### Intel - EP4CE15F17I8LN Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Product Status                 | Active                                                    |

|--------------------------------|-----------------------------------------------------------|

| Number of LABs/CLBs            | 963                                                       |

| Number of Logic Elements/Cells | 15408                                                     |

| Total RAM Bits                 | 516096                                                    |

| Number of I/O                  | 165                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 0.97V ~ 1.03V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 256-LBGA                                                  |

| Supplier Device Package        | 256-FBGA (17x17)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce15f17i8ln |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Address Clock Enable Support**

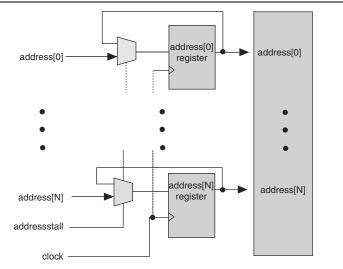

Cyclone IV devices M9K memory blocks support an active-low address clock enable, which holds the previous address value for as long as the addressstall signal is high (addressstall = '1'). When you configure M9K memory blocks in dual-port mode, each port has its own independent address clock enable.

Figure 3–2 shows an address clock enable block diagram. The address register output feeds back to its input using a multiplexer. The multiplexer output is selected by the address clock enable (addressstall) signal.

$\label{eq:Figure 3-2. Cyclone IV Devices Address Clock Enable Block Diagram$

The address clock enable is typically used to improve the effectiveness of cache memory applications during a cache-miss. The default value for the address clock enable signals is low.

| LFC[1] | LFC[0] | Setting (Decimal) |

|--------|--------|-------------------|

| 0      | 0      | 0                 |

| 0      | 1      | 1                 |

| 1      | 1      | 3                 |

| Table 5-10. | Loop Filter | <b>Control of Hig</b> | gh Frequenc | y Capacitor |

|-------------|-------------|-----------------------|-------------|-------------|

|-------------|-------------|-----------------------|-------------|-------------|

### **Bypassing a PLL Counter**

Bypassing a PLL counter results in a divide (N, C0 to C4 counters) factor of one.

Table 5–11 lists the settings for bypassing the counters in PLLs of Cyclone IV devices.

Table 5–11. PLL Counter Settings

|   | PLL Scan Chain Bits [08] Settings |   |   |   |       |                          |   | Description |                      |

|---|-----------------------------------|---|---|---|-------|--------------------------|---|-------------|----------------------|

|   | LSB                               |   |   |   | MSB   | Description              |   |             |                      |

| Х | Х                                 | Х | Х | Х | Х     | Х                        | Х | 1 (1)       | PLL counter bypassed |

| Х | ( X X X X X X X O                 |   |   |   | 0 (1) | PLL counter not bypassed |   |             |                      |

Note to Table 5–11:

(1) Bypass bit.

To bypass any of the PLL counters, set the bypass bit to 1. The values on the other bits are then ignored.

### **Dynamic Phase Shifting**

The dynamic phase shifting feature allows the output phase of individual PLL outputs to be dynamically adjusted relative to each other and the reference clock without sending serial data through the scan chain of the corresponding PLL. This feature simplifies the interface and allows you to quickly adjust t<sub>CO</sub> delays by changing output clock phase shift in real time. This is achieved by incrementing or decrementing the VCO phase-tap selection to a given C counter or to the M counter. The phase is shifted by 1/8 the VCO frequency at a time. The output clocks are active during this phase reconfiguration process.

Table 5–12 lists the control signals that are used for dynamic phase shifting.

Table 5–12. Dynamic Phase Shifting Control Signals (Part 1 of 2)

| Signal Name            | Description                                                                                                                                                                                                                        | Source                     | Destination                       |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|

| phasecounterselect[20] | Counter Select. Three bits decoded to select<br>either the M or one of the C counters for<br>phase adjustment. One address map to<br>select all C counters. This signal is registered<br>in the PLL on the rising edge of scanclk. | Logic array or I/O<br>pins | PLL<br>reconfiguration<br>circuit |

| phaseupdown            | Selects dynamic phase shift direction; $1 = UP$ ,<br>0 = DOWN. Signal is registered in the PLL on<br>the rising edge of scanclk.                                                                                                   | Logic array or I/O<br>pins | PLL<br>reconfiguration<br>circuit |

| phasestep              | Logic high enables dynamic phase shifting.                                                                                                                                                                                         | Logic array or I/O<br>pins | PLL<br>reconfiguration<br>circuit |

- "Pad Placement and DC Guidelines" on page 6–23

- "Clock Pins Functionality" on page 6–23

- "High-Speed I/O Interface" on page 6–24

- "High-Speed I/O Standards Support" on page 6–28

- "True Differential Output Buffer Feature" on page 6–35

- "High-Speed I/O Timing" on page 6–36

- "Design Guidelines" on page 6–37

- "Software Overview" on page 6–38

# **Cyclone IV I/O Elements**

Cyclone IV I/O elements (IOEs) contain a bidirectional I/O buffer and five registers for registering input, output, output-enable signals, and complete embedded bidirectional single-data rate transfer. I/O pins support various single-ended and differential I/O standards.

The IOE contains one input register, two output registers, and two output-enable (OE) registers. The two output registers and two OE registers are used for DDR applications. You can use input registers for fast setup times and output registers for fast clock-to-output times. Additionally, you can use OE registers for fast clock-to-output enable timing. You can use IOEs for input, output, or bidirectional data paths.

The CLKIN/REFCLK pins are powered by dedicated V<sub>CC\_CLKIN3A</sub>, V<sub>CC\_CLKIN3B</sub>, V<sub>CC\_CLKIN3B</sub>, v<sub>CC\_CLKIN8A</sub>, and V<sub>CC\_CLKIN8B</sub> power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for GPIO.

|                          |                            |                              |             | VCC_CLKIN Level |                  | I/O Pin Type  |            |                        |

|--------------------------|----------------------------|------------------------------|-------------|-----------------|------------------|---------------|------------|------------------------|

| I/O Standard             | I/O Standard HSSI Protocol |                              | Termination | Input           | Output           | Column<br>I/O | Row<br>I/O | Supported I/O<br>Banks |

| LVDS                     | All                        |                              | Off chip    | 2.5V            | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

| LVPECL                   | All                        | Differential<br>AC (Need     | Off chip    | 2.5V            | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

|                          | All                        | off chip<br>resistor to      | Off chip    | 2.5V            | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

| 1.2V, 1.5V,<br>3.3V PCML | All                        | restore<br>V <sub>CM</sub> ) | Off chip    | 2.5V            | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

|                          | All                        |                              | Off chip    | 2.5V            | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

| HCSL                     | PCIe                       | Differential<br>DC           | Off chip    | 2.5V            | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

Table 6–10. Cyclone IV GX HSSI REFCLK I/O Standard Support Using GPIO CLKIN Pins (1), (2)

Notes to Table 6-10:

(1) The EP4CGX15, EP4CGX22, and EP4CGX30 devices have two pairs of dedicated clock input pins in banks 3A and 8A for HSSI input reference clock. I/O banks 3B and 8B are not available in EP4CGX15, EP4CGX22, and EP4CGX30 devices.

(2) The EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices have four pairs of dedicated clock input pins in banks 3A, 3B, 8A, and 8B for HSSI input or single-ended clock input.

**To** For more information about the AC-coupled termination scheme for the HSSI reference clock, refer to the *Cyclone IV Transceivers Architecture* chapter.

## LVDS I/O Standard Support in Cyclone IV Devices

The LVDS I/O standard is a high-speed, low-voltage swing, low power, and GPIO interface standard. Cyclone IV devices meet the ANSI/TIA/EIA-644 standard with the following exceptions:

- The maximum differential output voltage (V<sub>OD</sub>) is increased to 600 mV. The maximum V<sub>OD</sub> for ANSI specification is 450 mV.

- The input voltage range is reduced to the range of 1.0 V to 1.6 V, 0.5 V to 1.85 V, or 0 V to 1.8 V based on different frequency ranges. The ANSI/TIA/EIA-644 specification supports an input voltage range of 0 V to 2.4 V.

- For LVDS I/O standard electrical specifications in Cyclone IV devices, refer to the *Cyclone IV Device Datasheet* chapter.

# **Configuration Scheme**

A configuration scheme with different configuration voltage standards is selected by driving the MSEL pins either high or low, as shown in Table 8–3, Table 8–4, and Table 8–5.

Hardwire the MSEL pins to V<sub>CCA</sub> or GND without pull-up or pull-down resistors to avoid problems detecting an incorrect configuration scheme. Do not drive the MSEL pins with a microprocessor or another device.

| Table 8–3. | Configuration Schemes for Cyclone IV GX Devices (EP4CGX15, EP4CGX22, and EP4CGX30 [except for F484 |

|------------|----------------------------------------------------------------------------------------------------|

| Package])  |                                                                                                    |

| Configuration Scheme                    | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|-----------------------------------------|-------|-------|-------|-----------|---------------------------------------------------|

|                                         | 1     | 0     | 1     | Fast      | 3.3                                               |

| AS                                      | 0     | 1     | 1     | Fast      | 3.0, 2.5                                          |

| AO                                      | 0     | 0     | 1     | Standard  | 3.3                                               |

|                                         | 0     | 1     | 0     | Standard  | 3.0, 2.5                                          |

|                                         | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| PS                                      | 1     | 1     | 0     | Fast      | 1.8, 1.5                                          |

|                                         | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                                     |

| JTAG-based configuration <sup>(2)</sup> | (3)   | (3)   | (3)   |           | _                                                 |

### Notes to Table 8-3:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to  $V_{CCA}$  or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

| Table 8-4. | <b>Configuration Schemes for Cyc</b> | lone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, |

|------------|--------------------------------------|-----------------------------------------------------------------|

| EP4CGX75   | , EP4CGX110, and EP4CGX150)          | (Part 1 of 2)                                                   |

| Configuration Scheme | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|----------------------|-------|-------|-------|-------|-----------|---------------------------------------------------|

|                      | 1     | 1     | 0     | 1     | Fast      | 3.3                                               |

| AS                   | 1     | 0     | 1     | 1     | Fast      | 3.0, 2.5                                          |

| AS                   | 1     | 0     | 0     | 1     | Standard  | 3.3                                               |

|                      | 1     | 0     | 1     | 0     | Standard  | 3.0, 2.5                                          |

|                      | 1     | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| PS                   | 1     | 1     | 1     | 0     | Fast      | 1.8, 1.5                                          |

| го                   | 1     | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                                     |

|                      | 0     | 0     | 0     | 0     | Standard  | 1.8, 1.5                                          |

|                      | 0     | 0     | 1     | 1     | Fast      | 3.3, 3.0, 2.5                                     |

| FPP                  | 0     | 1     | 0     | 0     | Fast      | 1.8, 1.5                                          |

| FPP                  | 0     | 0     | 0     | 1     | Standard  | 3.3, 3.0, 2.5                                     |

|                      | 0     | 0     | 1     | 0     | Standard  | 1.8, 1.5                                          |

## **Device Configuration Pins**

Table 8–18 through Table 8–21 describe the connections and functionality of all the configuration related pins on Cyclone IV devices. Table 8–18 and Table 8–19 list the device pin configuration for the Cyclone IV GX and Cyclone IV E, respectively.

Table 8–18. Configuration Pin Summary for Cyclone IV GX Devices

| Bank | Description        | Input/Output  | Dedicated | Powered By                     | <b>Configuration Mode</b> |

|------|--------------------|---------------|-----------|--------------------------------|---------------------------|

| 8    | Data[4:2]          | Input         | —         | V <sub>CCIO</sub>              | FPP                       |

| 3    | Data[7:5]          | Input         |           | V <sub>CCIO</sub>              | FPP                       |

| 9    | nCSO (2)           | Output        |           | V <sub>CCIO</sub>              | AS                        |

| 3    | CRC_ERROR          | Output        | —         | V <sub>CCIO</sub> /Pull-up (1) | Optional, all modes       |

| 9    | DATA[0] (2)        | Input         | Yes       | V <sub>CCIO</sub>              | PS, FPP, AS               |

| 9    | DATA [1] /ASDO (2) | Input         |           | V <sub>CCIO</sub>              | FPP                       |

| 9    | DATA[1]/ASDO (2)   | Output        |           | V <sub>CCIO</sub>              | AS                        |

| 3    | INIT_DONE          | Output        |           | Pull-up                        | Optional, all modes       |

| 3    | nSTATUS            | Bidirectional | Yes       | Pull-up                        | All modes                 |

| 9    | nCE                | Input         | Yes       | V <sub>CCIO</sub>              | All modes                 |

| 9    | 0                  | Input         | Yes       | V <sub>CCIO</sub>              | PS, FPP                   |

| 9    | DCLK (2)           | Output        | Output    |                                | AS                        |

| 3    | CONF_DONE          | Bidirectional | Yes       | Pull-up                        | All modes                 |

| 9    | TDI                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | TMS                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | TCK                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | nCONFIG            | Input         | Yes       | V <sub>CCIO</sub>              | All modes                 |

| 8    | CLKUSR             | Input         |           | V <sub>CCIO</sub>              | Optional                  |

| 3    | nCEO               | Output        |           | V <sub>CCIO</sub>              | Optional, all modes       |

| 3    | MSEL               | Input         | Yes       | V <sub>CCINT</sub>             | All modes                 |

| 9    | TDO                | Output        | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 6    | DEV_OE             | Input         | —         | V <sub>CCIO</sub>              | Optional                  |

| 6    | DEV_CLRn           | Input         | —         | V <sub>CCIO</sub>              | Optional                  |

Notes to Table 8-18:

(1) The CRC\_ERROR pin is a dedicated open-drain output or an optional user I/O pin. Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device and Pin Options dialog box. When using this pin, connect it to an external 10-kΩ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.

(2) To tri-state AS configuration pins in the AS configuration scheme, turn on the **Enable input tri-state on active configuration pins in user mode** option from the **Device and Pin Options** dialog box. This tri-states DCLK, nCSO, Data[0], and Data[1]/ASDO pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the **Enable input tri-state on active configuration pins in user mode** option and set the desired setting from the Dual-purpose Pins Setting menu.

| Bank | Description               | Input/Output | Dedicated | Powered By                            | <b>Configuration Mode</b> |

|------|---------------------------|--------------|-----------|---------------------------------------|---------------------------|

| 1    | nCSO (1)<br>FLASH_nCE (2) | Output       | _         | V <sub>CCIO</sub>                     | AS, AP                    |

| 6    | CRC_ERROR (3)             | Output       | —         | V <sub>CCIO</sub> /Pull-up <i>(4)</i> | Optional, all modes       |

|                  |                          | Configuration<br>Scheme Pin Type |                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------------|--------------------------|----------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                  |                          |                                  |                             | <ul> <li>Status output—the target Cyclone IV device drives the<br/>CONF_DONE pin low before and during configuration.<br/>After all the configuration data is received without error<br/>and the initialization cycle starts, the target device<br/>releases CONF_DONE.</li> <li>Status input _after all the data is received and</li> </ul>                                                                                                                                           |  |  |  |

| CONF_DONE        | N/A                      | All                              | Bidirectional<br>open-drain | <ul> <li>Status input—after all the data is received and<br/>CONF_DONE goes high, the target device initializes and<br/>enters user mode. The CONF_DONE pin must have an<br/>external 10-kΩ pull-up resistor in order for the device to<br/>initialize.</li> </ul>                                                                                                                                                                                                                     |  |  |  |

|                  |                          |                                  |                             | Driving CONF_DONE low after configuration and initialization does not affect the configured device. Do not connect bus holds or ADC to CONF_DONE pin.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| nCE              | N/A                      | All                              | Input                       | Active-low chip enable. The nCE pin activates the Cyclone IV device with a low signal to allow configuration. You must hold nCE pin low during configuration, initialization, and user-mode. In a single-device configuration, you must tie the nCE pin low. In a multi-device configuration, nCE of the first device is tied low while its nCEO pin is connected to nCE of the next device in the chain. You must hold the nCE pin low for successful JTAG programming of the device. |  |  |  |

|                  | N/A if<br>option is on.  |                                  | Output                      | Output that drives low when configuration is complete. In a single-device configuration, you can leave this pin floating or use it as a user I/O pin after configuration. In a multi-device configuration, this pin feeds the nCE pin of the next device. The nCEO of the last device in the chain is left floating or used as a user I/O pin after configuration.                                                                                                                     |  |  |  |

| nCEO             | I/O if option<br>is off. | All                              | open-drain                  | If you use the nCEO pin to feed the nCE pin of the next device, use an external 10-k $\Omega$ pull-up resistor to pull the nCEO pin high to the V <sub>CCIO</sub> voltage of its I/O bank to help the internal weak pull-up resistor.                                                                                                                                                                                                                                                  |  |  |  |

|                  |                          |                                  |                             | If you use the nCEO pin as a user I/O pin after configuration, set the state of the pin on the <b>Dual-Purpose Pin</b> settings.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| nCSO,            |                          |                                  |                             | Output control signal from the Cyclone IV device to the serial configuration device in AS mode that enables the configuration device. This pin functions as $nCSO$ in AS mode and $FLASH_nCE$ in AP mode.                                                                                                                                                                                                                                                                              |  |  |  |

| FLASH_nCE<br>(1) | I/O                      | AS, AP (2)                       | Output                      | Output control signal from the Cyclone IV device to the parallel flash in AP mode that enables the flash. Connects to the $CE\#$ pin on the Micron P30 or P33 flash. <sup>(2)</sup>                                                                                                                                                                                                                                                                                                    |  |  |  |

|                  |                          |                                  |                             | This pin has an internal pull-up resistor that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Table 8–20. De | edicated Configuration P | Pins on the Cyclone IV Device | (Part 2 of 4) |

|----------------|--------------------------|-------------------------------|---------------|

|----------------|--------------------------|-------------------------------|---------------|

### Table 8–28. Document Revision History (Part 2 of 2)

| Date          | Version    | Changes                                                                                                                                                                                                                                 |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |            | Updated for the Quartus II software 10.0 release:                                                                                                                                                                                       |

| July 2010     | 1.2        | <ul> <li>Updated "Power-On Reset (POR) Circuit", "Configuration and JTAG Pin I/O<br/>Requirements", and "Reset" sections.</li> </ul>                                                                                                    |

| -             |            | <ul> <li>Updated Figure 8–10.</li> </ul>                                                                                                                                                                                                |

|               |            | ■ Updated Table 8–16 and Table 8–17.                                                                                                                                                                                                    |

|               |            | Updated for the Quartus II software 9.1 SP1 release:                                                                                                                                                                                    |

|               |            | <ul> <li>Added "Overriding the Internal Oscillator" and "AP Configuration (Supported Flash<br/>Memories)" sections.</li> </ul>                                                                                                          |

|               |            | <ul> <li>Updated "JTAG Instructions" section.</li> </ul>                                                                                                                                                                                |

| February 2010 | y 2010 1.1 | ■ Added Table 8–6.                                                                                                                                                                                                                      |

|               |            | ■ Updated Table 8–2, Table 8–3, Table 8–4, Table 8–6, Table 8–11, Table 8–13, Table 8–14, Table 8–15, and Table 8–18.                                                                                                                   |

|               |            | <ul> <li>Updated Figure 8–4, Figure 8–5, Figure 8–6, Figure 8–13, Figure 8–14,<br/>Figure 8–15, Figure 8–17, Figure 8–18, Figure 8–23, Figure 8–24, Figure 8–25,<br/>Figure 8–26, Figure 8–27, Figure 8–28, and Figure 8–29.</li> </ul> |

| November 2009 | 1.0        | Initial release.                                                                                                                                                                                                                        |

Configuration error detection determines if the configuration data received through an external memory device is corrupted during configuration. To validate the configuration data, the Quartus<sup>®</sup> II software uses a function to calculate the CRC value for each configuration data frame and stores the frame-based CRC value in the configuration data as part of the configuration bit stream.

During configuration, Cyclone IV devices use the same methodology to calculate the CRC value based on the frame of data that is received and compares it against the frame CRC value in the data stream. Configuration continues until either the device detects an error or all the values are calculated.

In addition to the frame-based CRC value, the Quartus II software generates a 32-bit CRC value for the whole configuration bit stream. This 32-bit CRC value is stored in the 32-bit storage register at the end of the configuration and is used for user mode error detection that is discussed in "User Mode Error Detection".

## **User Mode Error Detection**

User mode error detection is available in Cyclone IV GX and Cyclone IV E devices with 1.2-V core voltage. Cyclone IV E devices with 1.0-V core voltage do not support user mode error detection.

Soft errors are changes in a configuration random-access memory (CRAM) bit state due to an ionizing particle. Cyclone IV devices have built-in error detection circuitry to detect data corruption by soft errors in the CRAM cells.

This error detection capability continuously computes the CRC of the configured CRAM bits based on the contents of the device and compares it with the pre-calculated CRC value obtained at the end of the configuration. If the CRCs match, there is no error in the current configuration CRAM bits. The process of error detection continues until the device is reset (by setting nCONFIG to low).

The Cyclone IV device error detection feature does not check memory blocks and I/O buffers. These device memory blocks support parity bits that are used to check the contents of memory blocks for any error. The I/O buffers are not verified during error detection because the configuration data uses flip-flops as storage elements that are more resistant to soft errors. Similar flip-flops are used to store the pre-calculated CRC and other error detection circuitry option bits.

The error detection circuitry in Cyclone IV devices uses a 32-bit CRC IEEE 802 standard and a 32-bit polynomial as the CRC generator. Therefore, a single 32-bit CRC calculation is performed by the device. If a soft error does not occur, the resulting 32-bit signature value is 0x00000000, that results in a 0 on the CRC\_ERROR output signal. If a soft error occurs in the device, the resulting signature value is non-zero and the CRC\_ERROR output signal is 1.

You can inject a soft error by changing the 32-bit CRC storage register in the CRC circuitry. After verifying the induced failure, you can restore the 32-bit CRC value to the correct CRC value with the same instruction and inserting the correct value.

Before updating it with a known bad value, Altera recommends reading out the correct value.

P

| Table 11–1. Power Supply Descriptions for the Cyclone IV GX Devices (Part 2 of 2) |

|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------|

| Power Supply Pin | Nominal Voltage Level (V) | Description                                |

|------------------|---------------------------|--------------------------------------------|

| VCCL_GXB         | 1.2                       | Transceiver PMA and auxiliary power supply |

Notes to Table 11-1:

(1) You must power up VCCA even if the phase-locked loop (PLL) is not used.

(2) I/O banks 3, 8, and 9 contain configuration pins. You can only power up the  $V_{CCIO}$  level of I/O banks 3 and 9 to 1.5 V, 1.8 V, 2.5 V, 3.0 V, or 3.3 V. For Fast Passive Parallel (FPP) configuration mode, you must power up the  $V_{CCIO}$  level of I/O bank 8 to 1.5 V, 1.8 V, 2.5 V, 3.0 V, or 3.3 V.

(3) All device packages of EP4CGX15, EP4CGX22, and device package F169 and F324 of EP4CGX30 devices have two VCC\_CLKIN dedicated clock input I/O located at Banks 3A and 8A. Device package F484 of EP4CGX30, all device packages of EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices have four VCC\_CLKIN dedicated clock input I/O bank located at banks 3A, 3B, 8A, and 8B.

(4) You must set VCC\_CLKIN to 2.5V if the CLKIN is used as a high-speed serial interface (HSSI) transceiver refclk. When not used as a transceiver refclk, VCC\_CLKIN supports 1.2 V/ 1.5 V/ 1.8 V/ 2.5 V/ 3.0 V/ 3.3V voltages.

| Power Supply Pin | Nominal Voltage Level (V)    | Description               |  |  |

|------------------|------------------------------|---------------------------|--|--|

| VCCINT           | 1.0, 1.2                     | Core voltage power supply |  |  |

| VCCA (1)         | 2.5                          | PLL analog power supply   |  |  |

| VCCD_PLL         | 1.0, 1.2                     | PLL digital power supply  |  |  |

| VCCIO (2)        | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | I/O banks power supply    |  |  |

Table 11–2. Power Supply Descriptions for the Cyclone IV E Devices

#### Notes to Table 11-2:

(1) You must power up VCCA even if the PLL is not used.

(2) I/O banks 1, 6, 7, and 8 contain configuration pins.

# **Hot-Socketing Specifications**

Cyclone IV devices are hot-socketing compliant without the need for any external components or special design requirements. Hot-socketing support in Cyclone IV devices has the following advantages:

- You can drive the device before power up without damaging the device.

- I/O pins remain tri-stated during power up. The device does not drive out before or during power-up. Therefore, it does not affect other buses in operation.

### **Devices Driven Before Power-Up**

You can drive signals into regular Cyclone IV E I/O pins and transceiver Cyclone IV GX I/O pins before or during power up or power down without damaging the device. Cyclone IV devices support any power-up or power-down sequence to simplify system-level designs.

### I/O Pins Remain Tri-stated During Power-Up

The output buffers of Cyclone IV devices are turned off during system power up or power down. Cyclone IV devices do not drive out until the device is configured and working in recommended operating conditions. The I/O pins are tri-stated until the device enters user mode.

# Cyclone IV Device Handbook,

# Volume 2

101 Innovation Drive San Jose, CA 95134 www.altera.com

CYIV-5V2-1.9

Table 1–9 lists the high- and low-speed clock sources for each channel.

| able 1–9. High- and Low-Speed Clock Sources for Each Channel in Non-Bonded Channel Configuration |

|--------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------|

| Dookono          | Troposius Plack   | Transceiver Channel | High- and Low-Spe | ed Clocks Sources            |  |

|------------------|-------------------|---------------------|-------------------|------------------------------|--|

| Package          | Transceiver Block | Transceiver Gnannei | Option 1          | Option 2                     |  |

| F324 and smaller | GXBL0             | All channels        | MPLL_1            | MPLL_2                       |  |

|                  | GXBL0             | Channels 0, 1       | MPLL_5/GPLL_1     | MPLL_6                       |  |

| F484 and larger  | GYBLU             | Channels 2, 3       | MPLL_5            | MPLL_6/MPLL_7 <sup>(1)</sup> |  |

| 1404 anu larger  | GXBL1 (1)         | Channels 0, 1       | MPLL_7/MPLL_6     | MPLL_8                       |  |

|                  | GYRTI (.)         | Channels 2, 3       | MPLL_7            | MPLL_8/GPLL_2                |  |

### Note to Table 1–9:

(1)  $\tt MPLL_7$  and <code>GXBL1</code> are not applicable for transceivers in F484 package

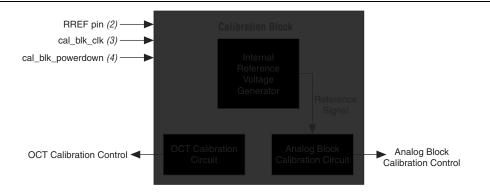

The calibration block internally generates a constant internal reference voltage, independent of PVT variations and uses this voltage and the external reference resistor on the RREF pin to generate constant reference currents. The OCT calibration circuit calibrates the OCT resistors present in the transceiver channels. Figure 1–41 shows the calibration block diagram.

### Notes to Figure 1-41:

- (1) All transceiver channels use the same calibration block clock and power down signals.

- (2) Connect a 2 k $\Omega$  (tolerance max ± 1%) external resistor to the RREF pin to ground. The RREF resistor connection in the board must be free from any external noise.

- (3) Supports up to 125 MHz clock frequency. Use either dedicated global clock or divide-down logic from the FPGA fabric to generate a slow clock on the local clock routing.

- (4) The calibration block restarts the calibration process following deassertion of the cal\_blk\_powerdown signal.

# **PCI-Express Hard IP Block**

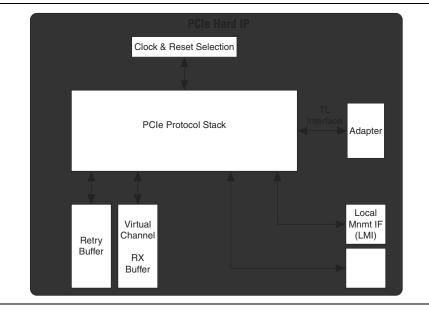

Figure 1–42 shows the block diagram of the PCIe hard IP block implementing the PHY MAC, Data Link Layer, and Transaction Layer for PCIe interfaces. The PIPE interface is used as the interface between the transceiver and the hard IP block.

Figure 1–42. PCI Express Hard IP High-Level Block Diagram

- 4. For the receiver operation, after deassertion of busy signal, wait for two parallel clock cycles to deassert the rx analogreset signal.

- 5. Wait for the rx\_freqlocked signal from each channel to go high. The rx\_freqlocked signal of each channel may go high at different times (indicated by the slashed pattern at marker 7).

- 6. In a bonded channel group, when the rx\_freqlocked signals of all the channels has gone high, from that point onwards, wait for at least t<sub>LTD\_Auto</sub> time for the receiver parallel clock to be stable, then deassert the rx\_digitalreset signal (marker 8). At this point, all the receivers are ready for data traffic.

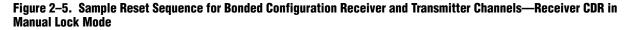

### **Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode**

This configuration contains both a transmitter and receiver channel. When the receiver CDR is in manual lock mode, use the reset sequence shown in Figure 2–5.

### Notes to Figure 2-5:

- (1) For t<sub>LTD Manual</sub> duration, refer to the Cyclone IV Device Datasheet chapter.

- (2) The number of rx\_locktorefclk [n] and rx\_locktodata [n] signals depend on the number of channels configured. n=number of channels.

- (3) For  $t_{LTR\_LTD\_Manual}$  duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (4) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

There are three methods that you can use to dynamically reconfigure the PMA controls of a transceiver channel:

- "Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels" on page 3–14

- "Method 2: Writing the Same Control Signals to Control All the Transceiver Channels" on page 3–16

- "Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same Time" on page 3–19

# Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels

Enable the logical\_channel\_address port by selecting the **Use** '**logical\_channel\_address' port** option on the **Analog controls** tab. This method is applicable only for a design where the dynamic reconfiguration controller controls more than one channel.

You can additionally reconfigure either the receiver portion, transmitter portion, or both the receiver and transmitter portions of the transceiver channel by setting the corresponding value on the rx\_tx\_duplex\_sel input port. For more information, refer to Table 3–2 on page 3–4.

### **Connecting the PMA Control Ports**

The selected PMA control ports remain fixed in width, regardless of the number of channels controlled by the ALTGX\_RECONFIG instance:

- tx\_vodctrl and tx\_vodctrl\_out are fixed to 3 bits

- tx preemp and tx preemp out are fixed to 5 bits

- rx\_eqdcgain and rx\_eqdcgain\_out are fixed to 2 bits

- rx\_eqctrl and rx\_eqctrl\_out are fixed to 4 bits

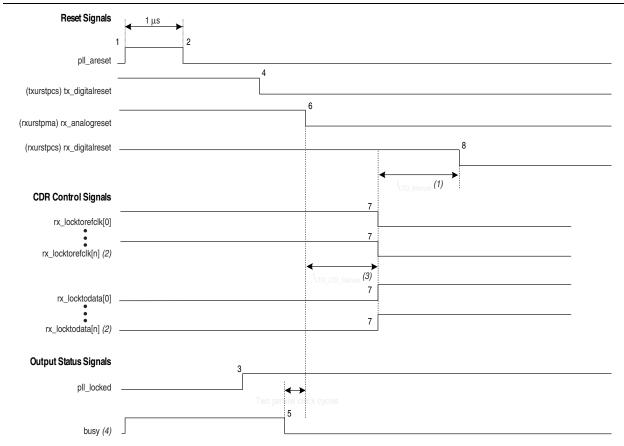

### Write Transaction

To complete a write transaction, perform the following steps:

- Set the selected PMA control ports to the desired settings (for example, tx\_vodctrl = 3'b001).

- 2. Set the logical\_channel\_address input port to the logical channel address of the transceiver channel whose PMA controls you want to reconfigure.

- 3. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 4. Ensure that the busy signal is low before you start a write transaction.

- 5. Assert the write\_all signal for one reconfig\_clk clock cycle.

The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

Figure 3–4 shows the write transaction waveform for Method 1.

### Figure 3-4. Write Transaction Waveform—Use 'logical\_channel\_address port' Option

#### Notes to Figure 3-4:

- (1) In this waveform example, you are writing to only the transmitter portion of the channel.

- (2) In this waveform example, the number of channels connected to the dynamic reconfiguration controller is four. Therefore, the

- logical\_channel\_address port is 2 bits wide.

#### **Read Transaction**

For example, to read the existing  $V_{OD}$  values from the transmit  $V_{OD}$  control registers of the transmitter portion of a specific channel controlled by the ALTGX\_RECONFIG instance, perform the following steps:

- Set the logical\_channel\_address input port to the logical channel address of the transceiver channel whose PMA controls you want to read (for example, tx\_vodctrl\_out).

- 2. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are read from the transceiver channel.

- 3. Ensure that the busy signal is low before you start a read transaction.

- 4. Assert the read signal for one reconfig\_clk clock cycle. This initiates the read transaction.

The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy reading the PMA control values. When the read transaction has completed, the busy signal goes low. The data\_valid signal is asserted to indicate that the data available at the read control signal is valid.

### **Control and Status Signals for Channel Reconfiguration**

The various control and status signals involved in the Channel Reconfiguration mode are as follows. Refer to "Dynamic Reconfiguration Controller Port List" on page 3–4 for the descriptions of the control and status signals.

The following are the input control signals:

- logical\_channel\_address[n..0]

- reset\_reconfig\_address

- reconfig\_reset

- reconfig\_mode\_sel[2..0]

- write\_all

The following are output status signals:

- reconfig\_address\_en

- reconfig\_address\_out[5..0]

- channel\_reconfig\_done

- busy

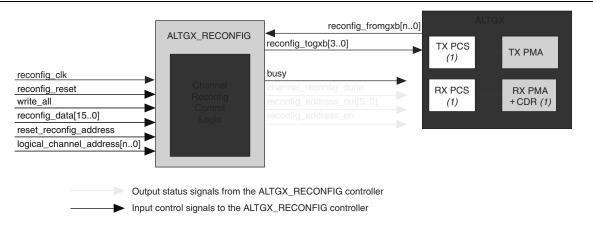

The ALTGX\_RECONFIG connection to the ALTGX instances when set in channel reconfiguration mode are as follows. For the port information, refer to "Dynamic Reconfiguration Controller Port List" on page 3–4.

Figure 3–10 shows the connection for channel reconfiguration mode.

### Figure 3–10. ALTGX and ALTGX\_RECONFIG Connection for Channel Reconfiguration Mode

### Note to Figure 3–10:

(1) This block can be reconfigured in channel reconfiguration mode.

Example 1–1 shows how to calculate the change of 50- $\Omega$  I/O impedance from 25°C at 3.0 V to 85°C at 3.15 V.

Example 1–1. Impedance Change

$$\begin{split} \Delta R_V &= (3.15-3) \times 1000 \times -0.026 = -3.83 \\ \Delta R_T &= (85-25) \times 0.262 = 15.72 \\ \text{Because } \Delta R_V \text{ is negative,} \\ MF_V &= 1 \ / \ (3.83/100 + 1) = 0.963 \\ \text{Because } \Delta R_T \text{ is positive,} \\ MF_T &= 15.72/100 + 1 = 1.157 \\ MF &= 0.963 \times 1.157 = 1.114 \\ R_{\text{final}} &= 50 \times 1.114 = 55.71 \ \Omega \end{split}$$

### **Pin Capacitance**

Table 1–11 lists the pin capacitance for Cyclone IV devices.

| Table 1–11. Pin Capacitance for Cyclone IV Devices <sup>(1)</sup> |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

| Symbol              | Parameter                                                                                                            | Typical –<br>Quad Flat<br>Pack<br>(QFP) | Typical –<br>Quad Flat<br>No Leads<br>(QFN) | Typical –<br>Ball-Grid<br>Array<br>(BGA) | Unit |

|---------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------|------------------------------------------|------|

| C <sub>IOTB</sub>   | Input capacitance on top and bottom I/O pins                                                                         | 7                                       | 7                                           | 6                                        | рF   |

| C <sub>IOLR</sub>   | Input capacitance on right I/O pins                                                                                  | 7                                       | 7                                           | 5                                        | pF   |

| $C_{LVDSLR}$        | Input capacitance on right I/O pins with dedicated LVDS output                                                       | 8                                       | 8                                           | 7                                        | рF   |

| C <sub>VREFLR</sub> | Input capacitance on right dual-purpose ${\tt VREF}$ pin when used as $V_{\sf REF}$ or user I/O pin                  | 21                                      | 21                                          | 21                                       | pF   |

| C <sub>VREFTB</sub> | Input capacitance on top and bottom dual-purpose $\mathtt{VREF}$ pin when used as $V_{\textrm{REF}}$ or user I/O pin | 23 <i>(3</i> )                          | 23                                          | 23                                       | pF   |

| C <sub>CLKTB</sub>  | Input capacitance on top and bottom dedicated clock input pins                                                       | 7                                       | 7                                           | 6                                        | pF   |

| C <sub>CLKLR</sub>  | Input capacitance on right dedicated clock input pins                                                                | 6                                       | 6                                           | 5                                        | pF   |

Notes to Table 1-11:

(1) The pin capacitance applies to FBGA, UBGA, and MBGA packages.

(2) When you use the vref pin as a regular input or output, you can expect a reduced performance of toggle rate and  $t_{CO}$  because of higher pin capacitance.

(3)  $C_{VREFTB}$  for the EP4CE22 device is 30 pF.

| Symbol                                       | Parameter                                                                                                                            | Min | Тур     | Max  | Unit              |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|-------------------|

| t <sub>dlock</sub>                           | Time required to lock dynamically (after switchover,<br>reconfiguring any non-post-scale counters/delays or<br>areset is deasserted) | _   | _       | 1    | ms                |

| t <sub>outjitter_period_dedclk</sub> (6)     | Dedicated clock output period jitter $F_{OUT} \ge 100 \text{ MHz}$                                                                   | _   | _       | 300  | ps                |

|                                              | F <sub>OUT</sub> < 100 MHz                                                                                                           | —   |         | 30   | mUI               |

| t <sub>outjitter_ccj_dedclk</sub> <i>(6)</i> | Dedicated clock output cycle-to-cycle jitter $F_{OUT} \ge 100 \text{ MHz}$                                                           | _   | _       | 300  | ps                |

|                                              | F <sub>OUT</sub> < 100 MHz                                                                                                           | _   | _       | 30   | mUI               |

| t <sub>outjitter_period_10</sub> <i>(6)</i>  | Regular I/O period jitter<br>F <sub>OUT</sub> ≥ 100 MHz                                                                              | _   | _       | 650  | ps                |

|                                              | F <sub>OUT</sub> < 100 MHz                                                                                                           | _   | —       | 75   | mUI               |

| t <sub>outjitter_ccj_io</sub> <i>(6)</i>     | Regular I/O cycle-to-cycle jitter $F_{OUT} \ge 100 \text{ MHz}$                                                                      | _   | _       | 650  | ps                |

|                                              | F <sub>OUT</sub> < 100 MHz                                                                                                           | —   | _       | 75   | mUI               |

| t <sub>PLL_PSERR</sub>                       | Accuracy of PLL phase shift                                                                                                          | —   | _       | ±50  | ps                |

| t <sub>ARESET</sub>                          | Minimum pulse width on areset signal.                                                                                                | 10  | _       | _    | ns                |

| t <sub>CONFIGPLL</sub>                       | Time required to reconfigure scan chains for PLLs                                                                                    | _   | 3.5 (7) |      | SCANCLK<br>cycles |

| f <sub>scanclk</sub>                         | scanclk frequency                                                                                                                    | _   | _       | 100  | MHz               |

| t <sub>casc_outjitter_period_dedclk</sub>    | Period jitter for dedicated clock output in cascaded PLLs ( $F_{OUT} \ge 100 \text{ MHz}$ )                                          | _   | _       | 425  | ps                |

| (8), (9)                                     | Period jitter for dedicated clock output in cascaded PLLs ( $F_{OUT}$ < 100 MHz)                                                     | _   |         | 42.5 | mUI               |

| Table 1-25. | PLL Specifications | for Cyclone IV Devices | <b>5</b> (1), (2) | (Part 2 of 2) |

|-------------|--------------------|------------------------|-------------------|---------------|

|-------------|--------------------|------------------------|-------------------|---------------|

### Notes to Table 1-25:

- (1) This table is applicable for general purpose PLLs and multipurpose PLLs.

- (2) You must connect  $V_{CCD PLL}$  to  $V_{CCINT}$  through the decoupling capacitor and ferrite bead.

- (3) This parameter is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

- (4) The V<sub>C0</sub> frequency reported by the Quartus II software in the PLL Summary section of the compilation report takes into consideration the V<sub>C0</sub> post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the f<sub>VC0</sub> specification.

- (5) A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source that is less than 200 ps.

- (6) Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.9999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL when an input jitter of 30 ps is applied.

- (7) With 100-MHz scanclk frequency.

(8) The cascaded PLLs specification is applicable only with the following conditions:

- $\blacksquare \quad Upstream \ PLL 0.59 \ MHz \leq Upstream \ PLL \ bandwidth < 1 \ MHz$

- Downstream PLL—Downstream PLL bandwidth > 2 MHz

- (9) PLL cascading is not supported for transceiver applications.

• For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to *Section III: System Performance Specifications* of the *External Memory Interface Handbook*.

Table 1-37 lists the memory output clock jitter specifications for Cyclone IV devices.

Table 1–37. Memory Output Clock Jitter Specifications for Cyclone IV Devices (1), (2)

| Parameter                    | Symbol                 | Min  | Max | Unit |

|------------------------------|------------------------|------|-----|------|

| Clock period jitter          | t <sub>JIT(per)</sub>  | -125 | 125 | ps   |

| Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -200 | 200 | ps   |

| Duty cycle jitter            | t <sub>JIT(duty)</sub> | -150 | 150 | ps   |

#### Notes to Table 1-37:

- (1) Memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2 standard.

- (2) The clock jitter specification applies to memory output clock pins generated using DDIO circuits clocked by a PLL output routed on a global clock (GCLK) network.

### **Duty Cycle Distortion Specifications**

Table 1–38 lists the worst case duty cycle distortion for Cyclone IV devices.

Table 1–38. Duty Cycle Distortion on Cyclone IV Devices I/O Pins (1), (2), (3)

| Symbol            | C6  |     | C7, 17 |     | C8, I8L, A7 |     | C9L |     | Unit |

|-------------------|-----|-----|--------|-----|-------------|-----|-----|-----|------|

| Symbol            | Min | Max | Min    | Max | Min         | Max | Min | Max | Unit |

| Output Duty Cycle | 45  | 55  | 45     | 55  | 45          | 55  | 45  | 55  | %    |

Notes to Table 1-38:

(1) The duty cycle distortion specification applies to clock outputs from the PLLs, global clock tree, and IOE driving the dedicated and general purpose I/O pins.

(2) Cyclone IV devices meet the specified duty cycle distortion at the maximum output toggle rate for each combination of I/O standard and current strength.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

### **OCT Calibration Timing Specification**

Table 1–39 lists the duration of calibration for series OCT with calibration at device power-up for Cyclone IV devices.

# Table 1–39. Timing Specification for Series OCT with Calibration at Device Power-Up for Cyclone IV Devices $^{(1)}$

| Symbol              | Description                                                   | Maximum | Units |  |

|---------------------|---------------------------------------------------------------|---------|-------|--|

| t <sub>octcal</sub> | Duration of series OCT with<br>calibration at device power-up | 20      | μs    |  |

### Note to Table 1-39:

(1) OCT calibration takes place after device configuration and before entering user mode.