### Intel - EP4CE15F23C8L Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 963                                                      |

| Number of Logic Elements/Cells | 15408                                                    |

| Total RAM Bits                 | 516096                                                   |

| Number of I/O                  | 343                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce15f23c8l |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Read or Write Clock Mode**

Cyclone IV devices M9K memory blocks can implement read or write clock mode for FIFO and simple dual-port memories. In this mode, a write clock controls the data inputs, write address, and wren registers. Similarly, a read clock controls the data outputs, read address, and rden registers. M9K memory blocks support independent clock enables for both the read and write clocks.

When using read or write mode, if you perform a simultaneous read or write to the same address location, the output read data is unknown. If you require the output data to be a known value, use either single-clock mode, input clock mode, or output clock mode and choose the appropriate read-during-write behavior in the MegaWizard Plug-In Manager.

# **Single-Clock Mode**

Cyclone IV devices M9K memory blocks can implement single-clock mode for FIFO, ROM, true dual-port, simple dual-port, and single-port memories. In this mode, you can control all registers of the M9K memory block with a single clock together with clock enable.

# **Design Considerations**

This section describes designing with M9K memory blocks.

# **Read-During-Write Operations**

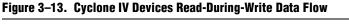

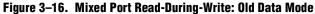

"Same-Port Read-During-Write Mode" on page 3–16 and "Mixed-Port Read-During-Write Mode" on page 3–16 describe the functionality of the various RAM configurations when reading from an address during a write operation at that same address.

There are two read-during-write data flows: same-port and mixed-port. Figure 3–13 shows the difference between these flows.

In this mode, you also have two output choices: **Old Data** mode or **Don't Care** mode. In **Old Data** mode, a read-during-write operation to different ports causes the RAM outputs to reflect the old data at that address location. In **Don't Care** mode, the same operation results in a "Don't Care" or unknown value on the RAM outputs.

**To** For more information about how to implement the desired behavior, refer to the *RAM Megafunction User Guide*.

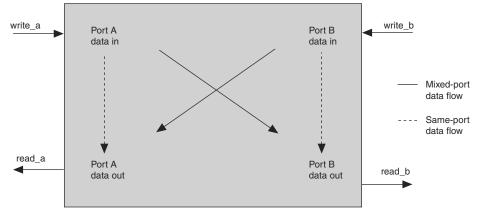

Figure 3–16 shows a sample functional waveform of mixed port read-during-write behavior for **Old Data** mode. In **Don't Care** mode, the old data is replaced with "Don't Care".

For mixed-port read-during-write operation with dual clocks, the relationship between the clocks determines the output behavior of the memory. If you use the same clock for the two clocks, the output is the old data from the address location. However, if you use different clocks, the output is unknown during the mixed-port read-during-write operation. This unknown value may be the old or new data at the address location, depending on whether the read happens before or after the write.

# **Conflict Resolution**

When you are using M9K memory blocks in true dual-port mode, it is possible to attempt two write operations to the same memory location (address). Because there is no conflict resolution circuitry built into M9K memory blocks, this results in unknown data being written to that location. Therefore, you must implement conflict-resolution logic external to the M9K memory block.

# **Clock Switchover**

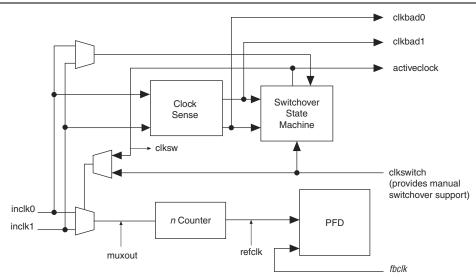

The clock switchover feature allows the PLL to switch between two reference input clocks. Use this feature for clock redundancy or for a dual-clock domain application, such as a system that turns on the redundant clock if the previous clock stops running. Your design can automatically perform clock switchover when the clock is no longer toggling, or based on the user control signal, clkswitch.

## **Automatic Clock Switchover**

PLLs of Cyclone IV devices support a fully configurable clock switchover capability.

When the current reference clock is not present, the clock-sense block automatically switches to the backup clock for PLL reference. The clock switchover circuit also sends out three status signals—clkbad0, clkbad1, and activeclock—from the PLL to implement a custom switchover circuit. You can select a clock source at the backup clock by connecting it to the inclk1 port of the PLL in your design.

Figure 5–17 shows the block diagram of the switchover circuit built into the PLL.

### Figure 5–17. Automatic Clock Switchover Circuit

There are two ways to use the clock switchover feature:

- Use the switchover circuitry for switching from inclk0 to inclk1 running at the same frequency. For example, in applications that require a redundant clock with the same frequency as the reference clock, the switchover state machine generates a signal that controls the multiplexer select input shown in Figure 5–17. In this case, inclk1 becomes the reference clock for the PLL. This automatic switchover can switch back and forth between the inclk0 and inclk1 clocks any number of times, when one of the two clocks fails and the other clock is available.

- Use the clkswitch input for user- or system-controlled switch conditions. This is possible for same-frequency switchover or to switch between inputs of different frequencies. For example, if inclk0 is 66 MHz and inclk1 is 200 MHz, you must control the switchover because the automatic clock-sense circuitry cannot monitor primary and secondary clock frequencies with a frequency difference of more than

- Low time count = 1 cycle

- rselodd = 1 effectively equals:

- High time count = 1.5 cycles

- Low time count = 1.5 cycles

- Duty cycle = (1.5/3)% high time count and (1.5/3)% low time count

### **Scan Chain Description**

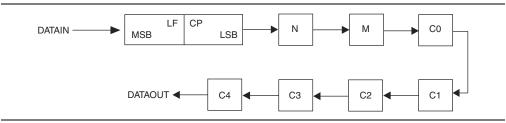

Cyclone IV PLLs have a 144-bit scan chain.

Table 5–7 lists the number of bits for each component of the PLL.

| Table 5-7. | Cyclone IV | PLL Reprogramming Bits |

|------------|------------|------------------------|

|------------|------------|------------------------|

| Block Name                 |         | Number of Bits |       |

|----------------------------|---------|----------------|-------|

| DIUCK NAIIIE               | Counter | Other          | Total |

| C4 <sup>(1)</sup>          | 16      | 2 (2)          | 18    |

| C3                         | 16      | 2 (2)          | 18    |

| C2                         | 16      | 2 (2)          | 18    |

| C1                         | 16      | 2 (2)          | 18    |

| C0                         | 16      | 2 (2)          | 18    |

| М                          | 16      | 2 (2)          | 18    |

| Ν                          | 16      | 2 (2)          | 18    |

| Charge Pump                | 9       | 0              | 9     |

| Loop Filter <sup>(3)</sup> | 9       | 0              | 9     |

| Total number of bits       |         |                | 144   |

### Notes to Table 5-7:

(1) LSB bit for C4 low-count value is the first bit shifted into the scan chain.

- (2) These two control bits include <code>rbypass</code>, for bypassing the counter, and <code>rselodd</code>, to select the output clock duty cycle.

- (3) MSB bit for loop filter is the last bit shifted into the scan chain.

Figure 5–24 shows the scan chain order of the PLL components.

Figure 5–24. PLL Component Scan Chain Order

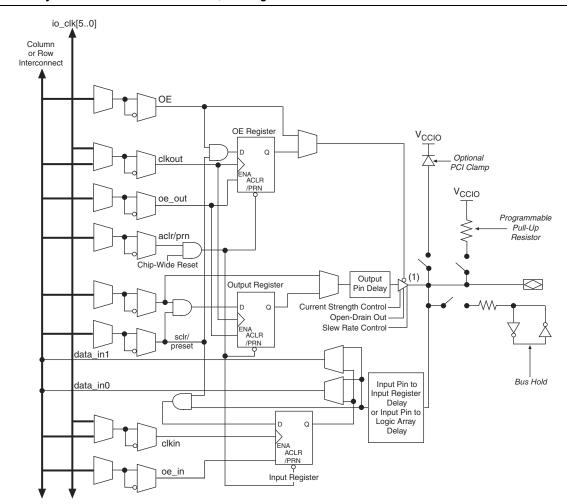

Figure 6–1 shows the Cyclone IV devices IOE structure for single data rate (SDR) operation.

#### Figure 6-1. Cyclone IV IOEs in a Bidirectional I/O Configuration for SDR Mode

#### Note to Figure 6–1:

(1) Tri-state control is not available for outputs configured with true differential I/O standards.

# **I/O Element Features**

The Cyclone IV IOE offers a range of programmable features for an I/O pin. These features increase the flexibility of I/O utilization and provide a way to reduce the usage of external discrete components, such as pull-up resistors and diodes.

## **Programmable Current Strength**

The output buffer for each Cyclone IV I/O pin has a programmable current strength control for certain I/O standards.

The LVTTL, LVCMOS, SSTL-2 Class I and II, SSTL-18 Class I and II, HSTL-18 Class I and II, HSTL-15 Class I and II, and HSTL-12 Class I and II I/O standards have several levels of current strength that you can control.

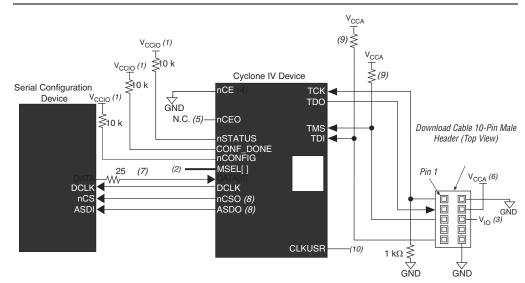

If you configure a master device with an SFL design, the master device enters user mode even though the slave devices in the multiple device chain are not being configured. The master device enters user mode with a SFL design even though the CONF\_DONE signal is externally held low by the other slave devices in chain. Figure 8–29 shows the JTAG configuration of a single Cyclone IV device with a SFL design.

### Notes to Figure 8-29:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL for AS configuration schemes, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (3) Pin 6 of the header is a V<sub>10</sub> reference voltage for the MasterBlaster output driver. The V<sub>10</sub> must match the V<sub>CCA</sub> of the device. For this value, refer to the *MasterBlaster Serial/USB Communications Cable User Guide*. When using the ByteBlasterMV download cable, this pin is a no connect. When using USB-Blaster, ByteBlaster II, and EthernetBlaster cables, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) You must connect the nCE pin to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (6) Power up the V<sub>CC</sub> of the EthernetBlaster, ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5- V V<sub>CCA</sub> supply. Third-party programmers must switch to 2.5 V. Pin 4 of the header is a V<sub>CC</sub> power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the *MasterBlaster Serial/USB Communications Cable User Guide*.

- (7) Connect the series resistor at the near end of the serial configuration device.

- (8) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA[1] pin in AP and FPP modes.

- (9) Resistor value can vary from 1 k $\Omega$  to 10 k $\Omega$ .

- (10) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

### **ISP of the Configuration Device**

In the second stage, the SFL design in the master device allows you to write the configuration data for the device chain into the serial configuration device with the Cyclone IV device JTAG interface. The JTAG interface sends the programming data for the serial configuration device to the Cyclone IV device first. The Cyclone IV device then uses the ASMI pins to send the data to the serial configuration device.

Table 8–21 lists the optional configuration pins. If you do not enable these optional configuration pins in the Quartus II software, they are available as general-purpose user I/O pins. Therefore, during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

| Pin Name  | User Mode                                     | Pin Type             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-----------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKUSR    | N/A if option is on.                          | Input                | Optional user-supplied clock input synchronizes the initialization of one or more devices. This pin is enabled by turning on the <b>Enable user-supplied start-up clock (CLKUSR)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLRUSK    | I/O if option is off.                         | mput                 | In AS configuration for Cyclone IV GX devices, you can use this pin as an external clock source to generate the DCLK by changing the clock source option in the Quartus II software in the <b>Configuration</b> tab of the <b>Device and Pin Options</b> dialog box.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INIT_DONE | N/A if option is on.<br>I/O if option is off. | Output<br>open-drain | Status pin is used to indicate when the device has initialized and<br>is in user-mode. When nCONFIG is low, the INIT_DONE pin is<br>tri-stated and pulled high due to an external 10-k $\Omega$ pull-up<br>resistor during the beginning of configuration. After the option<br>bit to enable INIT_DONE is programmed into the device (during<br>the first frame of configuration data), the INIT_DONE pin goes<br>low. When initialization is complete, the INIT_DONE pin is<br>released and pulled high and the device enters user mode.<br>Thus, the monitoring circuitry must be able to detect a low-to-<br>high transition. This pin is enabled by turning on the <b>Enable</b><br><b>INIT_DONE output</b> option in the Quartus II software. |

|           |                                               |                      | The functionality of this pin changes if the <b>Enable OCT_DONE</b> option is enabled in the Quartus II software. This option controls whether the INIT_DONE signal is gated by the OCT_DONE signal, which indicates the power-up on-chip termination (OCT) calibration is complete. If this option is turned off, the INIT_DONE signal is not gated by the OCT_DONE signal.                                                                                                                                                                                                                                                                                                                                                                       |

| DEV_OE    | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as programmed. This pin is enabled by turning on the <b>Enable device-wide output enable (DEV_OE)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DEV_CLRn  | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all clears on all device<br>registers. When this pin is driven low, all registers are cleared;<br>when this pin is driven high, all registers behave as<br>programmed. You can enable this pin by turning on the <b>Enable</b><br><b>device-wide reset (DEV_CLRn)</b> option in the Quartus II<br>software.                                                                                                                                                                                                                                                                                                                                                                                               |

Table 8–21. Optional Configuration Pins

# **Document Revision History**

Table 9–8 lists the revision history for this chapter.

| Table 9–8. Docum | ent Revision | History |

|------------------|--------------|---------|

|------------------|--------------|---------|

| Date          | Version | Changes                                                                                                                                                                                                                  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2013      | 1.3     | Updated "CRC_ERROR Pin Type" in Table 9–2.                                                                                                                                                                               |

| October 2012  | 1.2     | Updated Table 9–2.                                                                                                                                                                                                       |

| February 2010 | 1.1     | <ul> <li>Updated for the Quartus II software version 9.1 SP1 release:</li> <li>Updated "Configuration Error Detection" section.</li> <li>Updated Table 9–6.</li> <li>Added Cyclone IV E devices in Table 9–6.</li> </ul> |

| November 2009 | 1.0     | Initial release.                                                                                                                                                                                                         |

# Cyclone IV Device Handbook,

# Volume 2

101 Innovation Drive San Jose, CA 95134 www.altera.com

CYIV-5V2-1.9

# **Section I. Transceivers**

This section provides a complete overview of all features relating to the Cyclone<sup>®</sup> IV device transceivers. This section includes the following chapters:

- Chapter 1, Cyclone IV Transceivers Architecture

- Chapter 2, Cyclone IV Reset Control and Power Down

- Chapter 3, Cyclone IV Dynamic Reconfiguration

# **Revision History**

Refer to the chapter for its own specific revision history. For information about when the chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

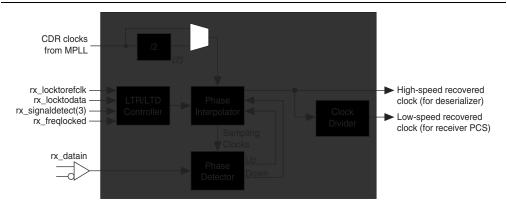

# **Clock Data Recovery**

Each receiver channel has an independent CDR unit to recover the clock from the incoming serial data stream. The high-speed recovered clock is used to clock the deserializer for serial-to-parallel conversion of the received input data, and low-speed recovered clock to clock the receiver PCS blocks. Figure 1–15 illustrates the CDR unit block diagram.

#### Notes to Figure 1-15:

- (1) Optional RX local divider for CDR clocks from multipurpose PLL is only available in each CDR unit for EP4CGX30 (F484 package), EP4CGX50, and EP4CGX75 devices. This block is used with the transceiver dynamic reconfiguration feature. For more information, refer to the Cyclone IV Dynamic Reconfiguration chapter and AN 609: Implementing Dynamic Reconfiguration in Cyclone IV GX Devices.

- (2) CDR state transition in automatic lock mode is not dependent on rx\_signaldetect signal, except when configured in PCI Express (PIPE) mode only.

Each CDR unit gets the reference clock from one of the two multipurpose phase-locked loops (PLLs) adjacent to the transceiver block. The CDR works by tracking the incoming data with a phase detector and finding the optimum sampling clock phase from the phase interpolator unit. The CDR operations are controlled by the LTR/LTD controller block, where the CDR may operate in the following states:

- Lock-to-reference (LTR) state—phase detector disabled and CDR ignores incoming data

- Lock-to-data (LTD) state—phase detector enabled and CDR tracks incoming data to find the optimum sampling clock phase

State transitions are supported with automatic lock mode and manual lock mode.

### **Automatic Lock Mode**

Upon receiver power-up and reset cycle, the CDR is put into LTR state. Transition to the LTD state is performed automatically when both of the following conditions are met:

- Signal detection circuitry indicates the presence of valid signal levels at the receiver input buffer. This condition is valid for PCI Express (PIPE) mode only. CDR transitions are not dependent on signal detection circuitry in other modes.

- The recovered clock is within the configured part per million (ppm) frequency threshold setting with respect to the CDR clocks from multipurpose PLL.

In configuration with rate match FIFO, the transmitter datapath clocking is identical to Transmitter Only operation as shown in Figure 1–38. In each bonded receiver channel, the CDR unit recovers the clock from serial received data and generates the high- and low-speed recovered clock for each bonded channel. The high-speed recovered clock feeds the channel's deserializer, and low-speed recovered clock is forwarded to receiver PCS. The individual low-speed recovered clock feeds to the following blocks in the receiver PCS:

- word aligner

- write clock of rate match FIFO

The common bonded low-speed clock that is used in all bonded transmitter PCS datapaths feeds the following blocks in each bonded receiver PCS:

- read clock of rate match FIFO

- 8B/10B decoder

- write clock of byte deserializer

- byte ordering

- write clock of RX phase compensation FIFO

When the byte deserializer is enabled, the common bonded low-speed clock frequency is halved before feeding to the write clock of RX phase compensation FIFO. The common bonded low-speed clock is available in FPGA fabric as coreclkout port, which can be used in FPGA fabric to send transmitter data and control signals, and capture receiver data and status signals from the bonded channels.

# **FPGA Fabric-Transceiver Interface Clocking**

The FPGA fabric-transceiver interface clocks consists of clock signals from the FPGA fabric to the transceiver blocks, and from the transceiver blocks to the FPGA fabric. These clock resources use the global clock networks (GCLK) in the FPGA core.

For information about the GCLK resources in the Cyclone IV GX devices, refer to *Clock Networks and PLLs in Cyclone IV Devices* chapter.

Table 1–11 lists the FPGA fabric-transceiver interface clocks.

Table 1–11. FPGA Fabric-Transceiver Interface Clocks (Part 1 of 2)

| Clock Name                                   | Clock Description                                                 | Interface Direction        |  |  |  |  |  |

|----------------------------------------------|-------------------------------------------------------------------|----------------------------|--|--|--|--|--|

| tx_clkout                                    | Phase compensation FIFO clock                                     | Transceiver to FPGA fabric |  |  |  |  |  |

| rx_clkout                                    | Phase compensation FIFO clock                                     | Transceiver to FPGA fabric |  |  |  |  |  |

| coreclkout                                   | Phase compensation FIFO clock                                     | Transceiver to FPGA fabric |  |  |  |  |  |

| fixed_clk                                    | 125MHz receiver detect clock in PIPE<br>mode                      | FPGA fabric to transceiver |  |  |  |  |  |

| reconfig_clk <sup>(1)</sup> , <sup>(2)</sup> | Transceiver dynamic reconfiguration and offset cancellation clock | FPGA fabric to transceiver |  |  |  |  |  |

- 2. After the PLL is reset, wait for the pll\_locked signal to go high (marker 4) indicating that the PLL is locked to the input reference clock. After the assertion of the pll\_locked signal, deassert the tx\_digitalreset signal (marker 5).

- 3. Wait at least five parallel clock cycles after the pll\_locked signal is asserted to deassert the rx\_analogreset signal (marker 6).

- 4. When the rx\_freqlocked signal goes high (marker 7), from that point onwards, wait for at least t<sub>LTD\_Auto</sub> time, then deassert the rx\_digitalreset signal (marker 8). At this point, the receiver is ready for data traffic.

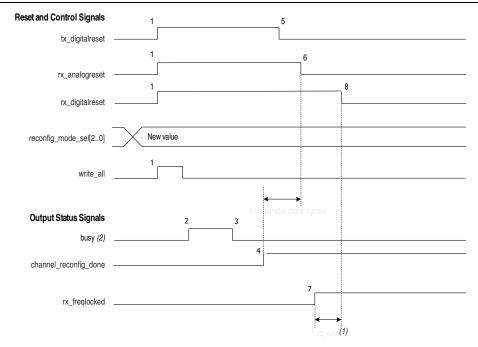

# **Reset Sequence in Channel Reconfiguration Mode**

Use the example reset sequence shown in Figure 2–12 when you are using the dynamic reconfiguration controller to change the PCS settings of the transceiver channel. In this example, the dynamic reconfiguration is used to dynamically reconfigure the transceiver channel configured in Basic ×1 mode with receiver CDR in automatic lock mode.

# Figure 2–12. Reset Sequence When Using the Dynamic Reconfiguration Controller to Change the PCS Settings of the Transceiver Channel

#### Notes to Figure 2-12:

- (1) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–12, perform the following reset procedure when using the dynamic reconfiguration controller to change the configuration of the transceiver channel:

- After power up and establishing that the transceiver is operating as desired, write the desired new value in the appropriate registers (including reconfig\_mode\_sel[2:0]) and subsequently assert the write\_all signal (marker 1) to initiate the dynamic reconfiguration.

- **\*** For more information, refer to the *Cyclone IV Dynamic Reconfiguration* chapter.

- 2. Assert the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals.

- 3. As soon as write\_all is asserted, the dynamic reconfiguration controller starts to execute its operation. This is indicated by the assertion of the busy signal (marker 2).

- 4. Wait for the assertion of the channel\_reconfig\_done signal (marker 4) that indicates the completion of dynamic reconfiguration in this mode.

- 5. Deassert the tx\_digitalreset signal (marker 5). This signal must be deasserted after assertion of the channel\_reconfig\_done signal (marker 4) and before the deassertion of the rx\_analogreset signal (marker 6).

- Wait for at least five parallel clock cycles after assertion of the channel\_reconfig\_done signal (marker 4) to deassert the rx\_analogreset signal (marker 6).

- Lastly, wait for the rx\_freqlocked signal to go high. After rx\_freqlocked goes high (marker 7), wait for t<sub>LTD\_Auto</sub> to deassert the rx\_digitalreset signal (marker 8). At this point, the receiver is ready for data traffic.

# **Power Down**

The Quartus II software automatically selects the power-down channel feature, which takes effect when you configure the Cyclone IV GX device. All unused transceiver channels and blocks are powered down to reduce overall power consumption. The gxb\_powerdown signal is an optional transceiver block signal. It powers down all transceiver channels and all functional blocks in the transceiver block. The minimum pulse width for this signal is 1 µs. After power up, if you use the gxb\_powerdown signal for a minimum of 1 µs. Lastly, follow the sequence shown in Figure 2–13.

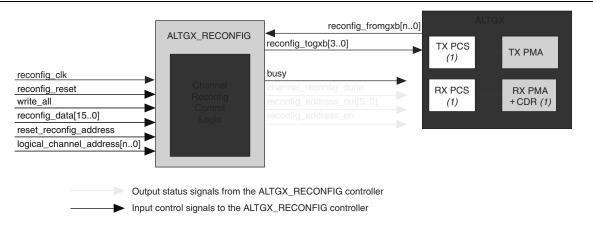

### **Control and Status Signals for Channel Reconfiguration**

The various control and status signals involved in the Channel Reconfiguration mode are as follows. Refer to "Dynamic Reconfiguration Controller Port List" on page 3–4 for the descriptions of the control and status signals.

The following are the input control signals:

- logical\_channel\_address[n..0]

- reset\_reconfig\_address

- reconfig\_reset

- reconfig\_mode\_sel[2..0]

- write\_all

The following are output status signals:

- reconfig\_address\_en

- reconfig\_address\_out[5..0]

- channel\_reconfig\_done

- busy

The ALTGX\_RECONFIG connection to the ALTGX instances when set in channel reconfiguration mode are as follows. For the port information, refer to "Dynamic Reconfiguration Controller Port List" on page 3–4.

Figure 3–10 shows the connection for channel reconfiguration mode.

### Figure 3–10. ALTGX and ALTGX\_RECONFIG Connection for Channel Reconfiguration Mode

### Note to Figure 3–10:

(1) This block can be reconfigured in channel reconfiguration mode.

| Visual Cue                               | Meaning                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input. The suffix n denotes an active-low signal. For example, resetn.                 |

| Courier type                             | Indicates command line commands and anything that must be typed exactly as it appears. For example, c:\qdesigns\tutorial\chiptrip.gdf.                                                 |

|                                          | Also indicates sections of an actual file, such as a Report File, references to parts of files (for example, the AHDL keyword SUBDESIGN), and logic function names (for example, TRI). |

| 4                                        | An angled arrow instructs you to press the Enter key.                                                                                                                                  |

| 1., 2., 3., and<br>a., b., c., and so on | Numbered steps indicate a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                          |

|                                          | Bullets indicate a list of items when the sequence of the items is not important.                                                                                                      |

| IP                                       | The hand points to information that requires special attention.                                                                                                                        |

| ?                                        | The question mark directs you to a software help system with related information.                                                                                                      |

| ••                                       | The feet direct you to another document or website with related information.                                                                                                           |

| <b>I</b> , <b>™</b> I                    | The multimedia icon directs you to a related multimedia presentation.                                                                                                                  |

| CAUTION                                  | A caution calls attention to a condition or possible situation that can damage or destroy the product or your work.                                                                    |

| VARNING                                  | A warning calls attention to a condition or possible situation that can cause you injury.                                                                                              |

|                                          | The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents.                 |

# **DC Characteristics**

This section lists the I/O leakage current, pin capacitance, on-chip termination (OCT) tolerance, and bus hold specifications for Cyclone IV devices.

## **Supply Current**

The device supply current requirement is the minimum current drawn from the power supply pins that can be used as a reference for power size planning. Use the Excel-based early power estimator (EPE) to get the supply current estimates for your design because these currents vary greatly with the resources used. Table 1–6 lists the I/O pin leakage current for Cyclone IV devices.

Table 1–6. I/O Pin Leakage Current for Cyclone IV Devices (1), (2)

| Symbol          | Parameter                            | Conditions                                 | Device | Min | Тур | Max | Unit |

|-----------------|--------------------------------------|--------------------------------------------|--------|-----|-----|-----|------|

| I <sub>I</sub>  | Input pin leakage current            | $V_I = 0 V \text{ to } V_{\text{CCIOMAX}}$ | —      | -10 | —   | 10  | μA   |

| I <sub>OZ</sub> | Tristated I/O pin leakage<br>current | $V_0 = 0 V$ to $V_{CCIOMAX}$               | _      | -10 | _   | 10  | μA   |

Notes to Table 1-6:

(1) This value is specified for normal device operation. The value varies during device power-up. This applies for all V<sub>CCI0</sub> settings (3.3, 3.0, 2.5, 1.8, 1.5, and 1.2 V).

(2) The 10  $\mu$ A I/O leakage current limit is applicable when the internal clamping diode is off. A higher current can be observed when the diode is on.

### **Bus Hold**

The bus hold retains the last valid logic state after the source driving it either enters the high impedance state or is removed. Each I/O pin has an option to enable bus hold in user mode. Bus hold is always disabled in configuration mode.

Table 1–7 lists bus hold specifications for Cyclone IV devices.

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 1 of 2)<sup>(1)</sup>

|                                            |                                                | V <sub>CCI0</sub> (V) |      |     |      |     |      |     |      |     |      |     |      |      |

|--------------------------------------------|------------------------------------------------|-----------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                  | Condition                                      | 1.2                   |      | 1   | 1.5  |     | 1.8  |     | 2.5  |     | .0   | 3.3 |      | Unit |

|                                            |                                                | Min                   | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus hold<br>low,<br>sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 8                     | _    | 12  | _    | 30  | _    | 50  | _    | 70  | _    | 70  | _    | μА   |

| Bus hold<br>high,<br>sustaining<br>current | V <sub>IN</sub> < V <sub>IL</sub><br>(minimum) | -8                    | _    | -12 | _    | -30 | _    | -50 | _    | -70 | _    | -70 | _    | μА   |

| Bus hold<br>low,<br>overdrive<br>current   | $0 V < V_{IN} < V_{CCIO}$                      | _                     | 125  |     | 175  | _   | 200  | _   | 300  | _   | 500  | _   | 500  | μА   |

| Bus hold<br>high,<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |                       | -125 | _   | -175 | _   | -200 | _   | -300 |     | -500 | _   | -500 | μА   |

**\*** For more information about receiver input and transmitter output waveforms, and for other differential I/O standards, refer to the *I/O Features in Cyclone IV Devices* chapter.

Table 1–18. Differential SSTL I/O Standard Specifications for Cyclone IV Devices (1)

| I/O Standard           | V     | V <sub>ccio</sub> (V) |       | V <sub>Swing(DC)</sub> (V) |                   | V <sub>X(AC)</sub> (V)          |     |                                 | V <sub>Swi</sub> | ng(AC)<br><b>V)</b>   | V <sub>ox</sub>                 | V <sub>OX(AC)</sub> (V) |                                 |

|------------------------|-------|-----------------------|-------|----------------------------|-------------------|---------------------------------|-----|---------------------------------|------------------|-----------------------|---------------------------------|-------------------------|---------------------------------|

|                        | Min   | Тур                   | Max   | Min                        | Max               | Min                             | Тур | Max                             | Min              | Max                   | Min                             | Тур                     | Max                             |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                   | 2.625 | 0.36                       | V <sub>CCIO</sub> | $V_{CCIO}/2 - 0.2$              | _   | V <sub>CCI0</sub> /2<br>+ 0.2   | 0.7              | V <sub>CCI</sub><br>0 | V <sub>CCIO</sub> /2 –<br>0.125 |                         | V <sub>CCI0</sub> /2<br>+ 0.125 |

| SSTL-18<br>Class I, II | 1.7   | 1.8                   | 1.90  | 0.25                       | V <sub>CCIO</sub> | V <sub>CCIO</sub> /2 –<br>0.175 | _   | V <sub>CCI0</sub> /2<br>+ 0.175 | 0.5              | V <sub>CCI</sub><br>0 | V <sub>CCIO</sub> /2 –<br>0.125 | _                       | V <sub>CCI0</sub> /2<br>+ 0.125 |

Note to Table 1-18:

(1) Differential SSTL requires a V<sub>REF</sub> input.

Table 1–19. Differential HSTL I/O Standard Specifications for Cyclone IV Devices <sup>(1)</sup>

| I/O Standard           | V <sub>CCIO</sub> (V) |     |       | V <sub>DIF(DC)</sub> (V) |                   | V <sub>X(AC)</sub> (V) |     |                             | V <sub>CM(DC)</sub> (V)     |     |                             |         | <sub>F(AC)</sub> (V)        |

|------------------------|-----------------------|-----|-------|--------------------------|-------------------|------------------------|-----|-----------------------------|-----------------------------|-----|-----------------------------|---------|-----------------------------|

|                        | andard Min Typ Max    |     | Max   | Min                      | Max               | Min                    | Тур | Max                         | Min                         | Тур | Max                         | Mi<br>n | Max                         |

| HSTL-18<br>Class I, II | 1.71                  | 1.8 | 1.89  | 0.2                      |                   | 0.85                   | _   | 0.95                        | 0.85                        | _   | 0.95                        | 0.4     | —                           |

| HSTL-15<br>Class I, II | 1.425                 | 1.5 | 1.575 | 0.2                      | _                 | 0.71                   | _   | 0.79                        | 0.71                        | _   | 0.79                        | 0.4     | _                           |

| HSTL-12<br>Class I, II | 1.14                  | 1.2 | 1.26  | 0.16                     | V <sub>CCIO</sub> | $0.48 \times V_{CCIO}$ | _   | 0.52 x<br>V <sub>CCI0</sub> | 0.48 x<br>V <sub>CCIO</sub> | _   | 0.52 x<br>V <sub>CCI0</sub> | 0.3     | 0.48 x<br>V <sub>CCI0</sub> |

Note to Table 1-19:

(1) Differential HSTL requires a V<sub>REF</sub> input.

Table 1–20. Differential I/O Standard Specifications for Cyclone IV Devices <sup>(1)</sup> (Part 1 of 2)

| I/O Standard                          | V <sub>CCIO</sub> (V) |     |       | V <sub>ID</sub> (mV) |     | V <sub>ICM</sub> (V) <sup>(2)</sup> |                                                                                                       |      | V <sub>OD</sub> (mV) <sup>(3)</sup> |     |     | V <sub>0S</sub> (V) <sup>(3)</sup> |      |       |

|---------------------------------------|-----------------------|-----|-------|----------------------|-----|-------------------------------------|-------------------------------------------------------------------------------------------------------|------|-------------------------------------|-----|-----|------------------------------------|------|-------|

| iju stanuaru                          | Min                   | Тур | Max   | Min                  | Max | Min                                 | Condition                                                                                             | Max  | Min                                 | Тур | Max | Min                                | Тур  | Max   |

|                                       |                       |     |       |                      |     | 0.05                                | $D_{MAX} \leq 500 \; Mbps$                                                                            | 1.80 |                                     |     |     |                                    |      |       |

| LVPECL<br>(Row I/Os)<br>(6)           | 2.375                 | 2.5 | 2.625 | 100                  | _   | 0.55                                | $\begin{array}{l} 500 \text{ Mbps} \leq \text{ D}_{\text{MAX}} \\ \leq 700 \text{ Mbps} \end{array}$  | 1.80 | _                                   | —   | _   | _                                  | _    | _     |

| .,                                    |                       |     |       |                      |     | 1.05                                | D <sub>MAX</sub> > 700 Mbps                                                                           | 1.55 |                                     |     |     |                                    |      |       |

|                                       |                       |     |       |                      |     | 0.05                                | $D_{MAX} \leq ~500~Mbps$                                                                              | 1.80 |                                     |     |     |                                    |      |       |

| LVPECL<br>(Column<br>I/Os) <i>(6)</i> | 2.375                 | 2.5 | 2.625 | 100                  |     | 0.55                                | $\begin{array}{l} 500 \text{ Mbps} \leq \text{D}_{\text{MAX}} \\ \leq 700 \text{ Mbps} \end{array}$   | 1.80 | _                                   | _   | _   | _                                  | _    | _     |

| 1/03/                                 |                       |     |       |                      |     | 1.05                                | D <sub>MAX</sub> > 700 Mbps                                                                           | 1.55 |                                     | I   |     |                                    |      |       |

| LVDS (Row<br>I/Os)                    | 2.375                 | 2.5 | 2.625 | 100                  |     | 0.05                                | $D_{MAX} \leq  500 \; Mbps$                                                                           | 1.80 | 247                                 |     | 600 | 1.125                              | 1.25 | 1.375 |

|                                       |                       |     |       |                      |     | 0.55                                | $\begin{array}{l} 500 \text{ Mbps} \leq \text{D}_{\text{MAX}} \\ \leq \ 700 \text{ Mbps} \end{array}$ | 1.80 |                                     |     |     |                                    |      |       |

|                                       |                       |     |       |                      |     | 1.05                                | D <sub>MAX</sub> > 700 Mbps                                                                           | 1.55 |                                     |     |     |                                    |      |       |

| Device    | Performance |       |     |                    |                           |       |                           |    |        |  |  |  |

|-----------|-------------|-------|-----|--------------------|---------------------------|-------|---------------------------|----|--------|--|--|--|

| Device    | C6          | C7    | C8  | C8L <sup>(1)</sup> | <b>C9L</b> <sup>(1)</sup> | 17    | <b>18L</b> <sup>(1)</sup> | A7 | – Unit |  |  |  |

| EP4CE55   | 500         | 437.5 | 402 | 362                | 265                       | 437.5 | 362                       | —  | MHz    |  |  |  |

| EP4CE75   | 500         | 437.5 | 402 | 362                | 265                       | 437.5 | 362                       | —  | MHz    |  |  |  |

| EP4CE115  | _           | 437.5 | 402 | 362                | 265                       | 437.5 | 362                       | —  | MHz    |  |  |  |

| EP4CGX15  | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |  |  |  |

| EP4CGX22  | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |  |  |  |

| EP4CGX30  | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |  |  |  |

| EP4CGX50  | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |  |  |  |

| EP4CGX75  | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |  |  |  |

| EP4CGX110 | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |  |  |  |

| EP4CGX150 | 500         | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |  |  |  |

Table 1–24. Clock Tree Performance for Cyclone IV Devices (Part 2 of 2)

### Note to Table 1-24:

(1) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades.

### **PLL Specifications**

Table 1–25 lists the PLL specifications for Cyclone IV devices when operating in the commercial junction temperature range (0°C to 85°C), the industrial junction temperature range (–40°C to 100°C), the extended industrial junction temperature range (–40°C to 125°C), and the automotive junction temperature range (–40°C to 125°C). For more information about the PLL block, refer to "Glossary" on page 1–37.

Table 1–25. PLL Specifications for Cyclone IV Devices <sup>(1), (2)</sup> (Part 1 of 2)

| Symbol                                                      | Parameter                                                       | Min | Тур | Max   | Unit |

|-------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|-------|------|

|                                                             | Input clock frequency (-6, -7, -8 speed grades)                 | 5   | —   | 472.5 | MHz  |

| f <sub>IN</sub> <i>(3)</i>                                  | Input clock frequency (–8L speed grade)                         | 5   |     | 362   | MHz  |

|                                                             | Input clock frequency (–9L speed grade)                         | 5   |     | 265   | MHz  |

| f <sub>INPFD</sub>                                          | PFD input frequency                                             | 5   |     | 325   | MHz  |

| f <sub>VCO</sub> (4)                                        | PLL internal VCO operating range                                | 600 | —   | 1300  | MHz  |

| f <sub>INDUTY</sub>                                         | Input clock duty cycle                                          | 40  |     | 60    | %    |

| t <sub>injitter_CCJ</sub> (5)                               | Input clock cycle-to-cycle jitter $F_{REF} \ge 100 \text{ MHz}$ |     | _   | 0.15  | UI   |

|                                                             | F <sub>REF</sub> < 100 MHz                                      |     |     | ±750  | ps   |

| f <sub>OUT_EXT</sub> (external clock output) <sup>(3)</sup> | PLL output frequency                                            | _   | _   | 472.5 | MHz  |

|                                                             | PLL output frequency (-6 speed grade)                           |     |     | 472.5 | MHz  |

|                                                             | PLL output frequency (-7 speed grade)                           | _   |     | 450   | MHz  |

| f <sub>OUT</sub> (to global clock)                          | PLL output frequency (-8 speed grade)                           |     |     | 402.5 | MHz  |

|                                                             | PLL output frequency (-8L speed grade)                          |     | —   | 362   | MHz  |

|                                                             | PLL output frequency (-9L speed grade)                          | _   |     | 265   | MHz  |

| t <sub>outduty</sub>                                        | Duty cycle for external clock output (when set to 50%)          | 45  | 50  | 55    | %    |

| t <sub>LOCK</sub>                                           | Time required to lock from end of device configuration          | —   | —   | 1     | ms   |

# **Document Revision History**

Table 1–47 lists the revision history for this chapter.

| Date          | Version | Changes                                                                                                                                                                                                                                          |  |  |  |  |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| December 2016 | 2.1     | Added note to Table 1–9 and Table 1–10.                                                                                                                                                                                                          |  |  |  |  |  |

| March 2016    | 2.0     | Updated note (5) in Table 1–21 to remove support for the N148 package.                                                                                                                                                                           |  |  |  |  |  |

| October 2014  | 4.0     | Updated maximum value for V <sub>CCD_PLL</sub> in Table 1–1.                                                                                                                                                                                     |  |  |  |  |  |

| October 2014  | 1.9     | Removed extended temperature note in Table 1–3.                                                                                                                                                                                                  |  |  |  |  |  |

| December 2013 | 1.8     | Updated Table 1–21 by adding Note (15).                                                                                                                                                                                                          |  |  |  |  |  |

| May 2013      | 1.7     | Updated Table 1–15 by adding Note (4).                                                                                                                                                                                                           |  |  |  |  |  |

|               |         | ■ Updated the maximum value for V <sub>I</sub> , V <sub>CCD_PLL</sub> , V <sub>CCIO</sub> , V <sub>CC_CLKIN</sub> , V <sub>CCH_GXB</sub> , and V <sub>CCA_GXB</sub><br>Table 1–1.                                                                |  |  |  |  |  |

|               |         | ■ Updated Table 1–11 and Table 1–22.                                                                                                                                                                                                             |  |  |  |  |  |

| October 2012  | 1.6     | <ul> <li>Updated Table 1–21 to include peak-to-peak differential input voltage for the<br/>Cyclone IV GX transceiver input reference clock.</li> </ul>                                                                                           |  |  |  |  |  |

|               |         | ■ Updated Table 1–29 to include the typical DCLK value.                                                                                                                                                                                          |  |  |  |  |  |

|               |         | <ul> <li>Updated the minimum f<sub>HSCLK</sub> value in Table 1–31, Table 1–32, Table 1–33,<br/>Table 1–34, and Table 1–35.</li> </ul>                                                                                                           |  |  |  |  |  |

|               | 1.5     | <ul> <li>Updated "Maximum Allowed Overshoot or Undershoot Voltage", "Operating<br/>Conditions", and "PLL Specifications" sections.</li> </ul>                                                                                                    |  |  |  |  |  |

| November 2011 |         | <ul> <li>Updated Table 1–2, Table 1–3, Table 1–4, Table 1–5, Table 1–8, Table 1–9,<br/>Table 1–15, Table 1–18, Table 1–19, and Table 1–21.</li> </ul>                                                                                            |  |  |  |  |  |

|               |         | ■ Updated Figure 1–1.                                                                                                                                                                                                                            |  |  |  |  |  |

|               | 1.4     | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                                                                                                                    |  |  |  |  |  |

| December 2010 |         | ■ Updated Table 1–21 and Table 1–25.                                                                                                                                                                                                             |  |  |  |  |  |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                                                                                                                            |  |  |  |  |  |

|               |         | Updated for the Quartus II software version 10.0 release:                                                                                                                                                                                        |  |  |  |  |  |

|               | 1.3     | ■ Updated Table 1–3, Table 1–4, Table 1–21, Table 1–25, Table 1–28, Table 1–30, Table 1–40, Table 1–41, Table 1–42, Table 1–43, Table 1–44, and Table 1–45.                                                                                      |  |  |  |  |  |

| July 2010     |         | ■ Updated Figure 1–2 and Figure 1–3.                                                                                                                                                                                                             |  |  |  |  |  |

|               |         | <ul> <li>Removed SW Requirement and TCCS for Cyclone IV Devices tables.</li> </ul>                                                                                                                                                               |  |  |  |  |  |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                                                                                                                            |  |  |  |  |  |

|               | 1.2     | Updated to include automotive devices:                                                                                                                                                                                                           |  |  |  |  |  |

| March 2010    |         | <ul> <li>Updated the "Operating Conditions" and "PLL Specifications" sections.</li> </ul>                                                                                                                                                        |  |  |  |  |  |

|               |         | <ul> <li>Updated Table 1–1, Table 1–8, Table 1–9, Table 1–21, Table 1–26, Table 1–27,<br/>Table 1–31, Table 1–32, Table 1–33, Table 1–34, Table 1–35, Table 1–36,<br/>Table 1–37, Table 1–38, Table 1–40, Table 1–42, and Table 1–43.</li> </ul> |  |  |  |  |  |

|               |         | <ul> <li>Added Table 1–5 to include ESD for Cyclone IV devices GPIOs and HSSI I/Os.</li> </ul>                                                                                                                                                   |  |  |  |  |  |

|               |         | <ul> <li>Added Table 1–44 and Table 1–45 to include IOE programmable delay for<br/>Cyclone IV E 1.2 V core voltage devices.</li> </ul>                                                                                                           |  |  |  |  |  |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                                                                                                                            |  |  |  |  |  |