### Intel - EP4CE15F23C9L Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 963                                                      |

| Number of Logic Elements/Cells | 15408                                                    |

| Total RAM Bits                 | 516096                                                   |

| Number of I/O                  | 343                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce15f23c9l |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Differential HSTL I/O Standard Support in Cyclone IV Devices |      |

|--------------------------------------------------------------|------|

| True Differential Output Buffer Feature                      |      |

| Programmable Pre-Emphasis                                    | 6–35 |

| High-Speed I/O Timing                                        |      |

| Design Guidelines                                            |      |

| Differential Pad Placement Guidelines                        |      |

| Board Design Considerations                                  |      |

| Software Overview                                            |      |

| Document Revision History                                    |      |

|                                                              |      |

### **Chapter 7. External Memory Interfaces in Cyclone IV Devices**

| Cyclone IV Devices Memory Interfaces Pin Support      | 7–2  |

|-------------------------------------------------------|------|

| Data and Data Clock/Strobe Pins                       | 7–2  |

| Optional Parity, DM, and Error Correction Coding Pins | 7–11 |

| Address and Control/Command Pins                      | 7–12 |

| Memory Clock Pins                                     | 7–12 |

| Cyclone IV Devices Memory Interfaces Features         | 7–12 |

| DDR Input Registers                                   | 7–12 |

| DDR Output Registers                                  | 7–14 |

| OCT with Calibration                                  | 7–15 |

| PLL                                                   | 7–15 |

| Document Revision History                             | 7–16 |

## Section III. System Integration

### Chapter 8. Configuration and Remote System Upgrades in Cyclone IV Devices

| Configuration                                                                          |                 |

|----------------------------------------------------------------------------------------|-----------------|

| Configuration Features                                                                 |                 |

| Configuration Data Decompression                                                       |                 |

| Configuration Requirement                                                              |                 |

| Power-On Reset (POR) Circuit                                                           |                 |

| Configuration File Size                                                                |                 |

| Configuration and JTAG Pin I/O Requirements                                            |                 |

| Configuration Process                                                                  |                 |

| Power Up                                                                               |                 |

| Reset                                                                                  |                 |

| Configuration                                                                          |                 |

| Configuration Error                                                                    |                 |

| Initialization                                                                         |                 |

| User Mode                                                                              |                 |

| Configuration Scheme                                                                   |                 |

| AS Configuration (Serial Configuration Devices)                                        |                 |

| Single-Device AS Configuration                                                         |                 |

| Multi-Device AS Configuration                                                          |                 |

| Configuring Multiple Cyclone IV Devices with the Same Design                           |                 |

| Guidelines for Connecting a Serial Configuration Device to Cyclone IV Devices for 8–18 | an AS Interface |

| Programming Serial Configuration Devices                                               |                 |

| AP Configuration (Supported Flash Memories)                                            |                 |

| AP Configuration Supported Flash Memories                                              |                 |

| Single-Device AP Configuration                                                         |                 |

| Multi-Device AP Configuration                                                          |                 |

| Byte-Wide Multi-Device AP Configuration                                                |                 |

|                                                                                        |                 |

# **Logic Array Blocks**

Logic array blocks (LABs) contain groups of LEs.

### Topology

Each LAB consists of the following features:

- 16 LEs

- LAB control signals

- LE carry chains

- Register chains

- Local interconnect

The local interconnect transfers signals between LEs in the same LAB. Register chain connections transfer the output of one LE register to the adjacent LE register in an LAB. The Quartus II Compiler places associated logic in an LAB or adjacent LABs, allowing the use of local and register chain connections for performance and area efficiency.

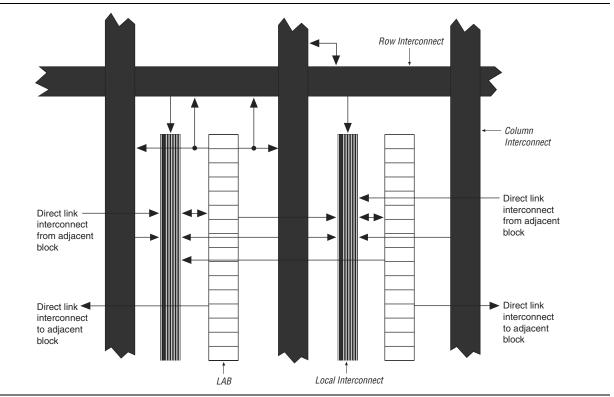

Figure 2–4 shows the LAB structure for Cyclone IV devices.

Figure 2–4. Cyclone IV Device LAB Structure

### **LAB Interconnects**

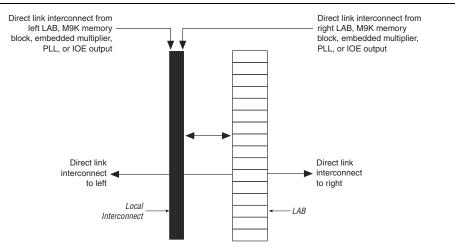

The LAB local interconnect is driven by column and row interconnects and LE outputs in the same LAB. Neighboring LABs, phase-locked loops (PLLs), M9K RAM blocks, and embedded multipliers from the left and right can also drive the local interconnect of a LAB through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive up to 48 LEs through fast local and direct link interconnects.

Figure 2–5 shows the direct link connection.

#### Figure 2–5. Cyclone IV Device Direct Link Connection

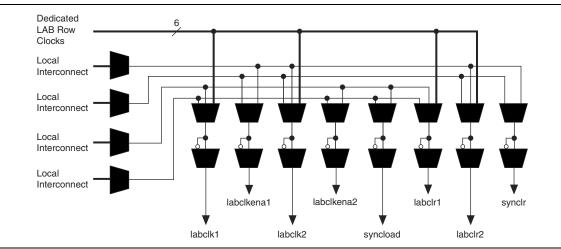

# LAB Control Signals

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include:

- Two clocks

- Two clock enables

- Two asynchronous clears

- One synchronous clear

- One synchronous load

You can use up to eight control signals at a time. Register packing and synchronous load cannot be used simultaneously.

Each LAB can have up to four non-global control signals. You can use additional LAB control signals as long as they are global signals.

Synchronous clear and load signals are useful for implementing counters and other functions. The synchronous clear and synchronous load signals are LAB-wide signals that affect all registers in the LAB.

Each LAB can use two clocks and two clock enable signals. The clock and clock enable signals of each LAB are linked. For example, any LE in a particular LAB using the labclk1 signal also uses the labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. Deasserting the clock enable signal turns off the LAB-wide clock.

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack interconnect inherent low skew allows clock and control signal distribution in addition to data distribution.

Figure 2–6 shows the LAB control signal generation circuit.

Figure 2–6. Cyclone IV Device LAB-Wide Control Signals

LAB-wide signals control the logic for the clear signal of the register. The LE directly supports an asynchronous clear function. Each LAB supports up to two asynchronous clear signals (labclr1 and labclr2).

A LAB-wide asynchronous load signal to control the logic for the preset signal of the register is not available. The register preset is achieved with a NOT gate push-back technique. Cyclone IV devices only support either a preset or asynchronous clear signal.

In addition to the clear port, Cyclone IV devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

# **Document Revision History**

Table 2–1 shows the revision history for this chapter.

Table 2-1. Document Revision History

| Date          | Version | Changes          |

|---------------|---------|------------------|

| November 2009 | 1.0     | Initial release. |

In this mode, the activeclock signal mirrors the clkswitch signal. As both blocks are still functional during the manual switch, neither clkbad signals go high. Because the switchover circuit is positive edge-sensitive, the falling edge of the clkswitch signal does not cause the circuit to switch back from inclk1 to inclk0. When the clkswitch signal goes high again, the process repeats. The clkswitch signal and the automatic switch only works depending on the availability of the clock that is switched to. If the clock is unavailable, the state machine waits until the clock is available.

When CLKSWITCH = 1, it overrides the automatic switch-over function. As long as clkswitch signal is high, further switch-over action is blocked.

|               | • |

|---------------|---|

| inclk0        |   |

| inclk1        |   |

| muxout        |   |

| clkswitch _   |   |

| activeclock _ |   |

| clkbad0 -     |   |

| clkbad1 -     |   |

#### Figure 5–19. Clock Switchover Using the clkswitch Control (1)

#### Note to Figure 5–19:

(1) Both inclk0 and inclk1 must be running when the clkswitch signal goes high to start a manual clock switchover event.

### **Manual Clock Switchover**

PLLs of Cyclone IV devices support manual switchover, in which the clkswitch signal controls whether inclk0 or inclk1 is the input clock to the PLL. The characteristics of a manual switchover are similar to the manual override feature in an automatic clock switchover, in which the switchover circuit is edge-sensitive. When the clkswitch signal goes high, the switchover sequence starts. The falling edge of the clkswitch signal does not cause the circuit to switch back to the previous input clock.

• For more information about PLL software support in the Quartus II software, refer to the *ALTPLL Megafunction User Guide*.

#### Guidelines

Use the following guidelines to design with clock switchover in PLLs:

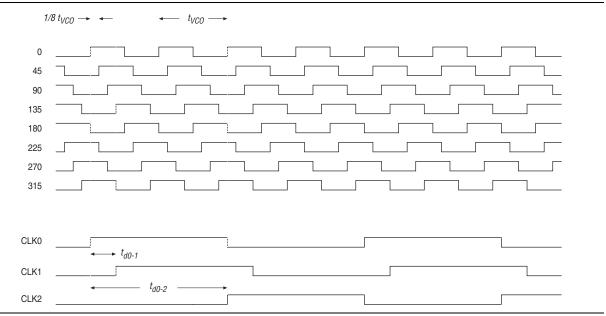

Clock loss detection and automatic clock switchover require the inclk0 and inclk1 frequencies be within 20% of each other. Failing to meet this requirement causes the clkbad0 and clkbad1 signals to function improperly. Figure 5–21 shows an example of phase shift insertion using fine resolution through VCO phase taps method. The eight phases from the VCO are shown and labeled for reference. In this example, CLK0 is based on 0° phase from the VCO and has the C value for the counter set to one. The CLK1 signal is divided by four, two VCO clocks for high time and two VCO clocks for low time. CLK1 is based on the 135° phase tap from the VCO and has the C value for the counter set to one. The CLK1 signal is also divided by four. In this case, the two clocks are offset by 3  $\Phi_{\rm fine}$ . CLK2 is based on the 0° phase from the VCO but has the C value for the counter set to three. This creates a delay of two  $\Phi_{\rm coarse}$  (two complete VCO periods).

You can use the coarse and fine phase shifts to implement clock delays in Cyclone IV devices.

Cyclone IV devices support dynamic phase shifting of VCO phase taps only. The phase shift is configurable for any number of times. Each phase shift takes about one scanclk cycle, allowing you to implement large phase shifts quickly.

# **PLL Cascading**

Cyclone IV devices allow cascading between general purpose PLLs and multipurpose PLLs in normal or direct mode through the GCLK network. If your design cascades PLLs, the source (upstream) PLL must have a low-bandwidth setting, while the destination (downstream) PLL must have a high-bandwidth setting.

PLL\_6 and PLL7 have upstream cascading capability only.

PLL cascading is not supported when used in transceiver applications.

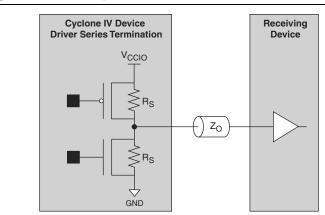

Figure 6–4 shows the single-ended I/O standards for OCT without calibration. The  $R_S$  shown is the intrinsic transistor impedance.

All I/O banks and I/O pins support impedance matching and series termination. Dedicated configuration pins and JTAG pins do not support impedance matching or series termination.

$R_S$  OCT is supported on any I/O bank.  $V_{CCIO}$  and  $V_{REF}$  must be compatible for all I/O pins to enable  $R_S$  OCT in a given I/O bank. I/O standards that support different  $R_S$  values can reside in the same I/O bank as long as their  $V_{CCIO}$  and  $V_{REF}$  do not conflict.

Impedance matching is implemented using the capabilities of the output driver and is subject to a certain degree of variation, depending on the process, voltage, and temperature.

For more information about tolerance specification, refer to the *Cyclone IV Device Datasheet* chapter.

# I/O Standards

Cyclone IV devices support multiple single-ended and differential I/O standards. Cyclone IV devices support 3.3-, 3.0-, 2.5-, 1.8-, 1.5-, and 1.2-V I/O standards.

Table 6–3 summarizes I/O standards supported by Cyclone IV devices and which I/O pins support them.

| Table 6–3. Cyclone IV Devices Supported I/O Standards and Constraints (Part |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

|                                         |              |                     | V <sub>ccio</sub> Level (in V) |        | Column I/O Pins |         |                     | Row I/O Pins <sup>(1)</sup> |                  |

|-----------------------------------------|--------------|---------------------|--------------------------------|--------|-----------------|---------|---------------------|-----------------------------|------------------|

| I/O Standard                            | Туре         | Standard<br>Support | Input                          | Output | CLK,<br>DQS     | PLL_OUT | User<br>I/O<br>Pins | CLK,<br>DQS                 | User I/O<br>Pins |

| 3.3-V LVTTL,<br>3.3-V LVCMOS <i>(2)</i> | Single-ended | JESD8-B             | 3.3/3.0/2.5<br><i>(3)</i>      | 3.3    | $\checkmark$    | ~       | $\checkmark$        | ~                           | ~                |

| 3.0-V LVTTL,<br>3.0-V LVCMOS <i>(2)</i> | Single-ended | JESD8-B             | 3.3/3.0/2.5<br><i>(3)</i>      | 3.0    | >               | ~       | $\checkmark$        | ~                           | ~                |

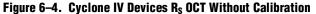

## **LVPECL I/O Support in Cyclone IV Devices**

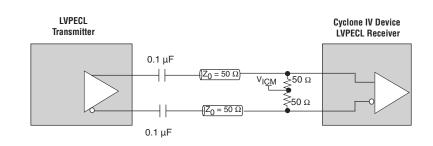

The LVPECL I/O standard is a differential interface standard that requires a 2.5-V  $V_{CCIO}$ . This standard is used in applications involving video graphics, telecommunications, data communications, and clock distribution. Cyclone IV devices support the LVPECL input standard at the dedicated clock input pins only. The LVPECL receiver requires an external 100- $\Omega$  termination resistor between the two signals at the input buffer.

For the LVPECL I/O standard electrical specification, refer to the Cyclone IV Device Datasheet chapter.

AC coupling is required when the LVPECL common mode voltage of the output buffer is higher than the Cyclone IV devices LVPECL input common mode voltage.

Figure 6–18 shows the AC-coupled termination scheme. The  $50-\Omega$  resistors used at the receiver are external to the device. DC-coupled LVPECL is supported if the LVPECL output common mode voltage is in the Cyclone IV devices LVPECL input buffer specification (refer to Figure 6–19).

#### Figure 6–18. LVPECL AC-Coupled Termination (1)

#### Note to Figure 6–18:

(1) The LVPECL AC-coupled termination is applicable only when an Altera FPGA transmitter is used.

Figure 6–19 shows the LVPECL DC-coupled termination.

#### Figure 6–19. LVPECL DC-Coupled Termination (1)

#### Note to Figure 6–19:

(1) The LVPECL DC-coupled termination is applicable only when an Altera FPGA transmitter is used.

# Table 8–4. Configuration Schemes for Cyclone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150) (Part 2 of 2)

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) $^{(1)}$ |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------|

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   | _         | _                                           |

#### Notes to Table 8-4:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to  $V_{CCA}$  or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

> Smaller Cyclone IV E devices or package options (E144 and F256 packages) do not have the MSEL[3] pin. The AS Fast POR configuration scheme at 3.0- or 2.5-V configuration voltage standard and the AP configuration scheme are not supported in Cyclone IV E devices without the MSEL[3] pin. To configure these devices with other supported configuration schemes, select MSEL[2..0] pins according to the MSEL settings in Table 8–5.

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------------|

|                              | 1     | 1     | 0     | 1     | Fast      | 3.3                                               |

| AS                           | 0     | 1     | 0     | 0     | Fast      | 3.0, 2.5                                          |

|                              | 0     | 0     | 1     | 0     | Standard  | 3.3                                               |

|                              | 0     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 0     | 1     | 0     | 1     | Fast      | 3.3                                               |

|                              | 0     | 1     | 1     | 0     | Fast      | 1.8                                               |

| AP                           | 0     | 1     | 1     | 1     | Standard  | 3.3                                               |

|                              | 1     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 1     | 0     | 0     | 0     | Standard  | 1.8                                               |

| PS                           | 1     | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| 15                           | 0     | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                                     |

| FPP                          | 1     | 1     | 1     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| 111                          | 1     | 1     | 1     | 1     | Fast      | 1.8, 1.5                                          |

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   |           | _                                                 |

Table 8–5. Configuration Schemes for Cyclone IV E Devices

#### Notes to Table 8-5:

(1) Configuration voltage standard applied to the V<sub>CCIO</sub> supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to V<sub>CCA</sub> or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

- The divisor value divides the frequency of the configuration oscillator output clock. This output clock is used as the clock source for the error detection process.

- 8. Click OK.

#### Figure 9–2. Enabling the Error Detection CRC Feature in the Quartus II Software

### **Accessing Error Detection Block Through User Logic**

The error detection circuit stores the computed 32-bit CRC signature in a 32-bit register, which is read out by user logic from the core. The cycloneiv\_crcblock primitive is a WYSIWYG component used to establish the interface from the user logic to the error detection circuit. The cycloneiv\_crcblock primitive atom contains the input and output ports that must be included in the atom. To access the logic array, the cycloneiv\_crcblock WYSIWYG atom must be inserted into your design.

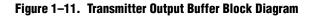

### **Transmitter Output Buffer**

Figure 1–11 shows the transmitter output buffer block diagram.

#### Note to Figure 1-11:

(1) Receiver detect function is specific for PCIe protocol implementation only. For more information, refer to "PCI Express (PIPE) Mode" on page 1–52.

The Cyclone IV GX transmitter output buffers support the **1.5-V PCML** I/O standard and are powered by VCCH\_GXB power pins with 2.5-V supply. The 2.5-V supply on VCCH\_GXB pins are regulated internally to 1.5-V for the transmitter output buffers. The transmitter output buffers support the following additional features:

- Programmable differential output voltage (V<sub>OD</sub>)—customizes the V<sub>OD</sub> up to 1200 mV to handle different trace lengths, various backplanes, and various receiver requirements.

- Programmable pre-emphasis—boosts high-frequency components in the transmitted signal to maximize the data eye opening at the far-end. The high-frequency components might be attenuated in the transmission media due to data-dependent jitter and intersymbol interference (ISI) effects. The requirement for pre-emphasis increases as the data rates through legacy backplanes increase.

- Programmable differential on-chip termination (OCT)—provides calibrated OCT at differential 100 Ω or 150 Ω with on-chip transmitter common mode voltage (V<sub>CM</sub>) at 0.65 V. V<sub>CM</sub> is tri-stated when you disable the OCT to use external termination.

- Disable OCT to use external termination if the link requires a 85  $\Omega$  termination, such as when you are interfacing with certain PCIe Gen1 or Gen2 capable devices.

- The Cyclone IV GX transmitter output buffers are current-mode drivers. The resulting V<sub>OD</sub> voltage is therefore a function of the transmitter termination value. For lists of supported V<sub>OD</sub> settings, refer to the *Cyclone IV Device Data Sheet*.

- Programmable equalization—boosts the high-frequency gain of the incoming signal up to 7 dB. This compensates for the low-pass filter effects of the transmission media. The amount of high-frequency gain required depends on the loss characteristics of the physical medium.

- Programmable DC gain—provides equal boost to incoming signal across the frequency spectrum with DC gain settings up to 6 dB.

- Programmable differential OCT—provides calibrated OCT at 100 Ω or 150 Ω with on-chip receiver common mode voltage at 0.82 V. The common mode voltage is tristated when you disable the OCT to use external termination.

- Offset cancellation—corrects the analog offset voltages that might exist from process variations between the positive and negative differential signals in the equalizer stage and CDR circuit.

- Signal detection—detects if the signal level present at the receiver input buffer is higher than the threshold with a built-in signal threshold detection circuitry. The circuitry has a hysteresis response that filters out any high-frequency ringing caused by ISI effects or high-frequency losses in the transmission medium. Detection is indicated by the assertion of the rx\_signaldetect signal. Signal detection is only supported when 8B/10B encoder/decoder block is enabled. When not supported, the rx\_signaldetect signal is forced high, bypassing the signal detection function.

- Disable OCT to use external termination if the link requires a 85  $\Omega$  termination, such as when you are interfacing with certain PCIe Gen1 or Gen2 capable devices.

- For specifications on programmable equalization and DC gain settings, refer to the *Cyclone IV Device Data Sheet*.

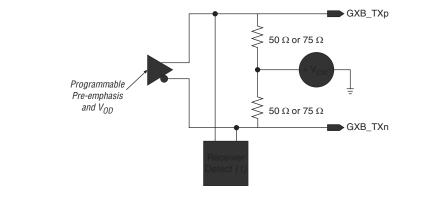

## **Rate Match FIFO**

In asynchronous systems, the upstream transmitter and local receiver can be clocked with independent reference clocks. Frequency differences in the order of a few hundred ppm can corrupt the data when latching from the recovered clock domain (the same clock domain as the upstream transmitter reference clock) to the local receiver reference clock domain. Figure 1–21 shows the rate match FIFO block diagram.

Figure 1–21. Rate Match FIFO Block Diagram

The rate match FIFO compensates for small clock frequency differences of up to  $\pm 300$  ppm (600 ppm total) between the upstream transmitter and the local receiver clocks by performing the following functions:

- Insert skip symbols when the local receiver reference clock frequency is greater than the upstream transmitter reference clock frequency

- Delete skip symbols when the local receiver reference clock frequency is less than the upstream transmitter reference clock frequency

The 20-word deep rate match FIFO and logics control insertion and deletion of skip symbols, depending on the ppm difference. The operation begins after the word aligner synchronization status (rx\_syncstatus) is asserted.

P

Rate match FIFO is only supported with 8B/10B encoded data and the word aligner in automatic synchronization state machine mode.

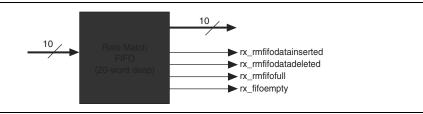

### **8B/10B Decoder**

The 8B/10B decoder receives 10-bit data and decodes it into an 8-bit data and a 1-bit control identifier. The decoder is compliant with Clause 36 of the IEEE 802.3 specification.

Figure 1–22 shows the 8B/10B decoder block diagram.

#### Figure 1–22. 8B/10B Decoder Block Diagram

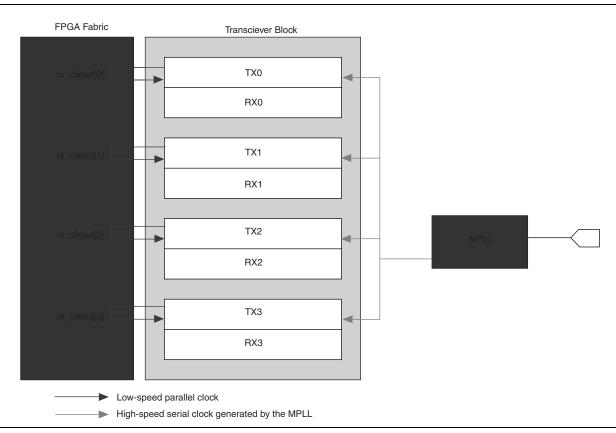

# **Transceiver Clocking Architecture**

The multipurpose PLLs and general-purpose PLLs located on the left side of the device generate the clocks required for the transceiver operation. The following sections describe the Cyclone IV GX transceiver clocking architecture:

- "Input Reference Clocking" on page 1–27

- "Transceiver Channel Datapath Clocking" on page 1–29

- "FPGA Fabric-Transceiver Interface Clocking" on page 1–43

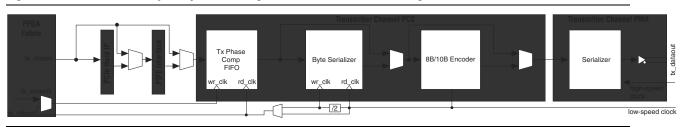

When the byte serializer is enabled, the low-speed clock frequency is halved before feeding into the read clock of TX phase compensation FIFO. The low-speed clock is available in the FPGA fabric as tx\_clkout port, which can be used in the FPGA fabric to send transmitter data and control signals.

Figure 1-33. Transmitter Only Datapath Clocking in Non-Bonded Channel Configuration

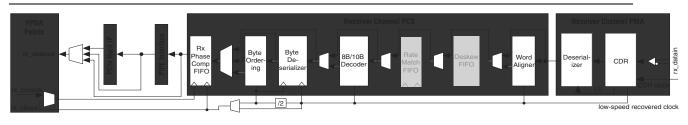

Figure 1–34 shows the datapath clocking in receiver only operation. In this mode, the receiver PCS supports configuration without the rate match FIFO. The CDR unit in the channel recovers the clock from the received serial data and generates the high-speed recovered clock for the deserializer, and low-speed recovered clock for forwarding to the receiver PCS. The low-speed recovered clock feeds to the following blocks in the receiver PCS:

- word aligner

- 8B/10B decoder

- write clock of byte deserializer

- byte ordering

- write clock of RX phase compensation FIFO

When the byte deserializer is enabled, the low-speed recovered clock frequency is halved before feeding into the write clock of the RX phase compensation FIFO. The low-speed recovered clock is available in the FPGA fabric as rx\_clkout port, which can be used in the FPGA fabric to capture receiver data and status signals.

Figure 1-34. Receiver Only Datapath Clocking without Rate Match FIFO in Non-Bonded Channel Configuration

Note to Figure 1-34:

(1) High-speed recovered clock.

When the transceiver is configured for transmitter and receiver operation in non-bonded channel configuration, the receiver PCS supports configuration with and without the rate match FIFO. The difference is only at the receiver datapath clocking. The transmitter datapath clocking is identical to transmitter only operation mode as shown in Figure 1–33.

| Block  | Port Name                       | Input/<br>Output          | Clock Domain                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|---------------------------------|---------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | rx_coreclk                      | Output                    | Clock signal                                                                   | Optional read clock port for the RX phase compensation FIFO.                                                                                                                                                                                                                                                                                                                                                   |

| RX PCS | rx_phase_comp_fifo<br>_error    | Output                    | Synchronous to tx_clkout<br>(non-bonded modes) or<br>coreclkout (bonded modes) | <ul><li>RX phase compensation FIFO full or empty indicator.</li><li>A high level indicates FIFO is either full or empty.</li></ul>                                                                                                                                                                                                                                                                             |

|        | rx_bitslipboundarys<br>electout | Output                    | Asynchronous signal.                                                           | <ul> <li>Indicate the number of bits slipped in the word aligner configured in manual alignment mode.</li> <li>Values range from 0 to 9.</li> </ul>                                                                                                                                                                                                                                                            |

|        | rx_datain                       | Input                     | N/A                                                                            | Receiver serial data input port.                                                                                                                                                                                                                                                                                                                                                                               |

|        | rx_freqlocked                   | -                         | Asynchronous signal                                                            | <ul> <li>Receiver CDR lock state indicator</li> <li>A high level indicates the CDR is in LTD state.</li> <li>A low level indicates the CDR is in LTR state.</li> </ul>                                                                                                                                                                                                                                         |

| RX PMA | rx_locktodata                   | Input Asynchronous signal |                                                                                | <ul> <li>Receiver CDR LTD state control signal</li> <li>A high level forces the CDR to LTD state</li> <li>When deasserted, the receiver CDR lock state depends on the rx_locktorefclk signal level.</li> </ul>                                                                                                                                                                                                 |

|        | rx_locktorefclk                 | Input                     | Asynchronous signal                                                            | <ul> <li>Receiver CDR LTR state control signal.</li> <li>The rx_locktorefclk and rx_locktodata signals control whether the receiver CDR states as follows: <ul> <li>[rx_locktodata:rx_locktorefclk]</li> <li>2'b00—receiver CDR is in automatic lock mode</li> <li>2b'01—receiver CDR is in manual lock mode (LTR state)</li> <li>2b'1x—receiver CDR is in manual lock mode (LTD state)</li> </ul> </li> </ul> |

|        | rx_signaldetect                 | Output                    | Asynchronous signal                                                            | <ul> <li>Signal threshold detect indicator.</li> <li>Available in Basic mode when 8B/10B encoder/decoder is used, and in PIPE mode.</li> <li>A high level indicates that the signal present at the receiver input buffer is above the programmed signal detection threshold value.</li> </ul>                                                                                                                  |

|        | rx_recovclkout                  | Output                    | Clock signal                                                                   | <ul> <li>CDR low-speed recovered clock</li> <li>Only available in the GIGE mode for applications such as Synchronous Ethernet.</li> </ul>                                                                                                                                                                                                                                                                      |

| Table 1–27. | <b>Receiver Ports in</b> | <b>ALTGX Megafunction</b> | for Cyclone IV GX | (Part 3 of 3) |

|-------------|--------------------------|---------------------------|-------------------|---------------|

|-------------|--------------------------|---------------------------|-------------------|---------------|

Table 2–2 lists the power-down signals available for each transceiver block.

Table 2–2.

Transceiver Block Power-Down Signals

| Signal        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               | Resets the transceiver PLL. The pll_areset signal is asserted in two conditions:                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| pll_areset    | <ul> <li>During reset sequence, the signal is asserted to reset the transceiver PLL. This signal is<br/>controlled by the user.</li> </ul>                                                                                                                                                                                                                                                                                                                                                               |  |  |

|               | <ul> <li>After the transceiver PLL is reconfigured, the signal is asserted high by the<br/>ALTPLL_RECONFIG controller. This signal is not controlled by the user.</li> </ul>                                                                                                                                                                                                                                                                                                                             |  |  |

| gxb_powerdown | Powers down the entire transceiver block. When this signal is asserted, this signal powers down the PCS and PMA in all the transceiver channels.                                                                                                                                                                                                                                                                                                                                                         |  |  |

|               | This signal operates independently from the other reset signals. This signal is common to the transceiver block.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| pll_locked    | A status signal. Indicates the status of the transmitter multipurpose PLLs or general purpose PLLs.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|               | <ul> <li>A high level—indicates the multipurpose PLL or general purpose PLL is locked to the<br/>incoming reference clock frequency.</li> </ul>                                                                                                                                                                                                                                                                                                                                                          |  |  |

|               | A status signal. Indicates the status of the receiver CDR lock mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| rx_freqlocked | A high level—the receiver is in lock-to-data mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|               | A low level—the receiver CDR is in lock-to-reference mode.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| busy          | A status signal. An output from the ALTGX_RECONFIG block indicates the status of the dynamic reconfiguration controller. This signal remains low for the first reconfig_clk clock cycle after power up. It then gets asserted from the second reconfig_clk clock cycle. Assertion on this signal indicates that the offset cancellation process is being executed on the receiver buffer as well as the receiver CDR. When this signal is deasserted, it indicates that offset cancellation is complete. |  |  |

|               | This busy signal is also used to indicate the dynamic reconfiguration duration such as in analog reconfiguration mode and channel reconfiguration mode.                                                                                                                                                                                                                                                                                                                                                  |  |  |

For more information about offset cancellation, refer to the *Cyclone IV Dynamic Reconfiguration* chapter.

IF If none of the channels is instantiated in a transceiver block, the Quartus<sup>®</sup> II software automatically powers down the entire transceiver block.

### **Blocks Affected by the Reset and Power-Down Signals**

Table 2–3 lists the blocks that are affected by specific reset and power-down signals.

| Table 2–3. | Blocks Affected by Reset and Power-Down Signals | (Part 1 of 2) |

|------------|-------------------------------------------------|---------------|

|------------|-------------------------------------------------|---------------|

| Transceiver Block                          | rx_digitalreset | rx_analogreset | tx_digitalreset | pll_areset   | gxb_powerdown |

|--------------------------------------------|-----------------|----------------|-----------------|--------------|---------------|

| multipurpose PLLs and general purpose PLLs | —               | _              | _               | $\checkmark$ | _             |

| Transmitter Phase<br>Compensation FIFO     | _               | _              | ~               | _            | ~             |

| Byte Serializer                            | _               |                | $\checkmark$    | _            | $\checkmark$  |

| 8B/10B Encoder                             | —               | —              | ~               |              | $\checkmark$  |

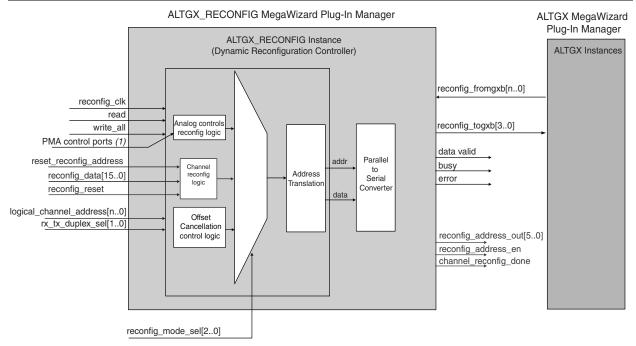

Figure 3–1 shows a conceptual view of the dynamic reconfiguration controller architecture. For a detailed description of the inputs and outputs of the ALTGX\_RECONFIG instance, refer to "Error Indication During Dynamic Reconfiguration" on page 3–36.

Figure 3–1. Dynamic Reconfiguration Controller

#### Note to Figure 3-1:

(1) The PMA control ports consist of the V<sub>OD</sub>, pre-emphasis, DC gain, and manual equalization controls.

C C

<sup>o</sup> Only PMA reconfiguration mode supports manual equalization controls.

You can use one ALTGX\_RECONFIG instance to control multiple transceiver blocks. However, you cannot use multiple ALTGX\_RECONFIG instances to control one transceiver block.

#### **Option 2: Use the Respective Channel Transmitter Core Clocks**

- Enable this option if you want the individual transmitter channel tx\_clkout signals to provide the write clock to their respective Transmit Phase Compensation FIFOs.

- This option is typically enabled when each transceiver channel is reconfigured to a different functional mode using channel reconfiguration.

Figure 3–12 shows how each transmitter channel's tx\_clkout signal provides a clock to the Transmit Phase Compensation FIFOs of the respective transceiver channels.

Figure 3–12. Option 2 for Transmitter Core Clocking (Channel Reconfiguration Mode)

Receiver core clocking refers to the clock that is used to read the parallel data from the Receiver Phase Compensation FIFO into the FPGA fabric. You can use one of the following clocks to read from the Receive Phase Compensation FIFO:

- rx\_coreclk—you can use a clock of the same frequency as rx\_clkout from the FPGA fabric to provide the read clock to the Receive Phase Compensation FIFO. If you use rx\_coreclk, it overrides the rx\_clkout options in the ALTGX MegaWizard Plug-In Manager.

- rx\_clkout—the Quartus II software automatically routes rx\_clkout to the FPGA fabric and back into the Receive Phase Compensation FIFO.

Table 1–29 lists the active configuration mode specifications for Cyclone IV devices.

| Programming Mode                    | DCLK Range | Typical DCLK | Unit |

|-------------------------------------|------------|--------------|------|

| Active Parallel (AP) <sup>(1)</sup> | 20 to 40   | 33           | MHz  |

| Active Serial (AS)                  | 20 to 40   | 33           | MHz  |

Table 1–29. Active Configuration Mode Specifications for Cyclone IV Devices

#### Note to Table 1-29:

(1) AP configuration mode is only supported for Cyclone IV E devices.

Table 1-30 lists the JTAG timing parameters and values for Cyclone IV devices.

Table 1–30. JTAG Timing Parameters for Cyclone IV Devices (1)

| Symbol                | Parameter                                                    | Min | Max | Unit |

|-----------------------|--------------------------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>      | TCK clock period                                             | 40  | —   | ns   |

| t <sub>JCH</sub>      | TCK clock high time                                          | 19  | _   | ns   |

| t <sub>JCL</sub>      | TCK clock low time                                           | 19  | _   | ns   |

| t <sub>JPSU_TDI</sub> | JTAG port setup time for TDI                                 | 1   | _   | ns   |

| t <sub>JPSU_TMS</sub> | JTAG port setup time for TMS                                 | 3   | _   | ns   |

| t <sub>JPH</sub>      | JTAG port hold time                                          | 10  | _   | ns   |

| t <sub>JPCO</sub>     | JTAG port clock to output <sup>(2), (3)</sup>                | —   | 15  | ns   |

| t <sub>JPZX</sub>     | JTAG port high impedance to valid output <sup>(2), (3)</sup> | —   | 15  | ns   |

| t <sub>JPXZ</sub>     | JTAG port valid output to high impedance $(2)$ , $(3)$       | —   | 15  | ns   |

| t <sub>JSSU</sub>     | Capture register setup time                                  | 5   | _   | ns   |

| t <sub>JSH</sub>      | Capture register hold time                                   | 10  | _   | ns   |

| t <sub>JSC0</sub>     | Update register clock to output                              | _   | 25  | ns   |

| t <sub>JSZX</sub>     | Update register high impedance to valid output               | _   | 25  | ns   |

| t <sub>JSXZ</sub>     | Update register valid output to high impedance               | —   | 25  | ns   |

#### Notes to Table 1-30:

(1) For more information about JTAG waveforms, refer to "JTAG Waveform" in "Glossary" on page 1-37.

- (2) The specification is shown for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 16 ns.

- (3) For EP4CGX22, EP4CGX30 (F324 and smaller package), EP4CGX110, and EP4CGX150 devices, the output time specification for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins is 16 ns. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 18 ns.

### **Periphery Performance**

This section describes periphery performance, including high-speed I/O and external memory interface.

I/O performance supports several system interfaces, such as the high-speed I/O interface, external memory interface, and the PCI/PCI-X bus interface. I/Os using the SSTL-18 Class I termination standard can achieve up to the stated DDR2 SDRAM interfacing speeds. I/Os using general-purpose I/O standards such as 3.3-, 3.0-, 2.5-, 1.8-, or 1.5-LVTTL/LVCMOS are capable of a typical 200 MHz interfacing frequency with a 10 pF load.