### Intel - EP4CE15M9C7N Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 963                                                     |

| Number of Logic Elements/Cells | 15408                                                   |

| Total RAM Bits                 | 516096                                                  |

| Number of I/O                  | 165                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 256-TFBGA                                               |

| Supplier Device Package        | 256-MBGA (9x9)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce15m9c7n |

|                                |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5. Clock Networks and PLLs in Cyclone IV Devices

This chapter describes the hierarchical clock networks and phase-locked loops (PLLs) with advanced features in the Cyclone<sup>®</sup> IV device family. It includes details about the ability to reconfigure the PLL counter clock frequency and phase shift in real time, allowing you to sweep PLL output frequencies and dynamically adjust the output clock phase shift.

The Quartus<sup>®</sup> II software enables the PLLs and their features without external devices.

This chapter contains the following sections:

- "Clock Networks" on page 5–1

- "PLLs in Cyclone IV Devices" on page 5–18

- "Cyclone IV PLL Hardware Overview" on page 5–20

- "Clock Feedback Modes" on page 5–23

- "Hardware Features" on page 5–26

- "Programmable Bandwidth" on page 5–32

- "Phase Shift Implementation" on page 5–32

- "PLL Cascading" on page 5–33

- "PLL Reconfiguration" on page 5–34

- "Spread-Spectrum Clocking" on page 5–41

- "PLL Specifications" on page 5–41

## **Clock Networks**

The Cyclone IV GX device provides up to 12 dedicated clock pins (CLK[15..4]) that can drive the global clocks (GCLKs). Cyclone IV GX devices support four dedicated clock pins on each side of the device except the left side. These clock pins can drive up to 30 GCLKs.

The Cyclone IV E device provides up to 15 dedicated clock pins (CLK[15..1]) that can drive up to 20 GCLKs. Cyclone IV E devices support three dedicated clock pins on the left side and four dedicated clock pins on the top, right, and bottom sides of the device except EP4CE6 and EP4CE10 devices. EP4CE6 and EP4CE10 devices only support three dedicated clock pins on the left side and four dedicated clock pins on the right side of the device.

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

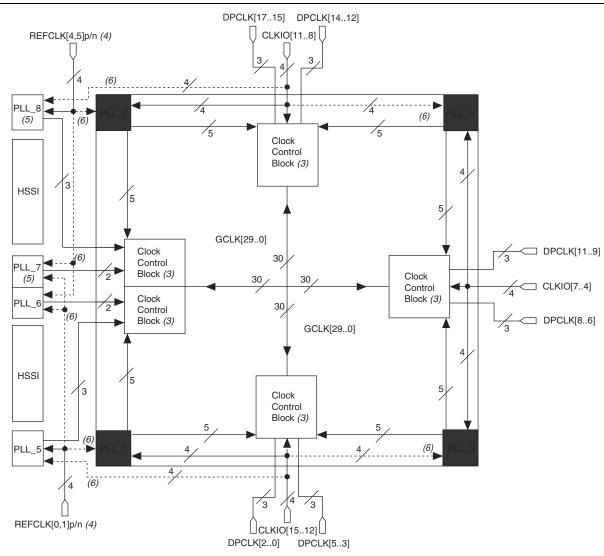

## Figure 5–3. Clock Networks and Clock Control Block Locations in EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices <sup>(1), (2)</sup>

### Notes to Figure 5-3:

- (1) The clock networks and clock control block locations in this figure apply to only the EP4CGX30 device in F484 package and all EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices.

- (2) PLL\_1, PLL\_2, PLL\_3, and PLL\_4 are general purpose PLLs while PLL\_5, PLL\_6, PLL\_7, and PLL\_8 are multipurpose PLLs.

- (3) There are 6 clock control blocks on the top, right and bottom sides of the device and 12 clock control blocks on the left side of the device.

- (4) REFCLK[0,1]p/n and REFCLK[4,5]p/n can only drive the general purpose PLLs and multipurpose PLLs on the left side of the device. These clock pins do not have access to the clock control blocks and GCLK networks. The REFCLK[4,5]p/n pins are not available in devices in F484 package.

- (5) Not available for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

- (6) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

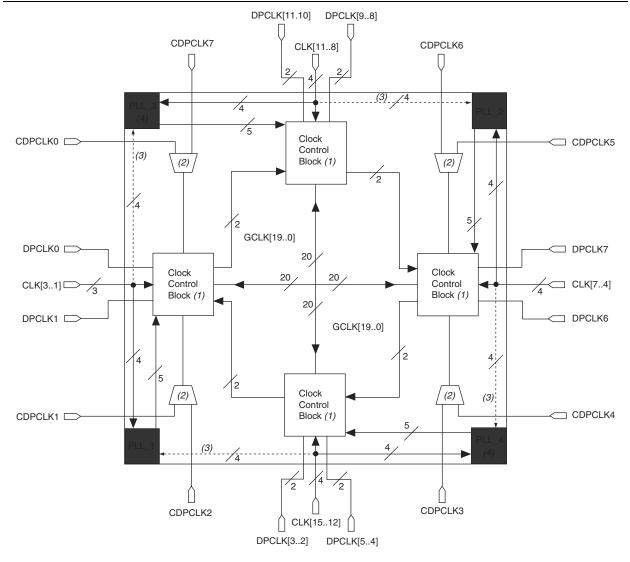

### Figure 5-4. Clock Networks and Clock Control Block Locations in Cyclone IV E Devices

### Notes to Figure 5-4:

- (1) There are five clock control blocks on each side.

- (2) Only one of the corner CDPCLK pins in each corner can feed the clock control block at a time. You can use the other CDPCLK pins as general-purpose I/O (GPIO) pins.

- (3) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

- (4)  $PLL_3$  and  $PLL_4$  are not available in EP4CE6 and EP4CE10 devices.

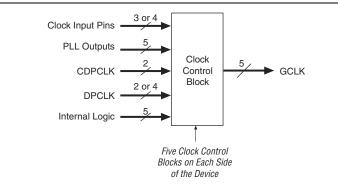

The inputs to the clock control blocks on each side of the Cyclone IV GX device must be chosen from among the following clock sources:

- Four clock input pins

- Ten PLL counter outputs (five from each adjacent PLLs)

- Two, four, or six DPCLK pins from the top, bottom, and right sides of the device

- Five signals from internal logic

Figure 5–6 shows a simplified version of the five clock control blocks on each side of the Cyclone IV E device periphery.

### Note to Figure 5–6:

(1) The left and right sides of the device have two DPCLK pins; the top and bottom of the device have four DPCLK pins.

### **GCLK Network Power Down**

You can disable a Cyclone IV device's GCLK (power down) using both static and dynamic approaches. In the static approach, configuration bits are set in the configuration file generated by the Quartus II software, which automatically disables unused GCLKs. The dynamic clock enable or disable feature allows internal logic to control clock enable or disable the GCLKs in Cyclone IV devices.

When a clock network is disabled, all the logic fed by the clock network is in an off-state, thereby reducing the overall power consumption of the device. This function is independent of the PLL and is applied directly on the clock network, as shown in Figure 5–1 on page 5–11.

You can set the input clock sources and the clkena signals for the GCLK multiplexers through the Quartus II software using the ALTCLKCTRL megafunction.

**For more information, refer to the** *ALTCLKCTRL Megafunction User Guide.*

### clkena Signals

Cyclone IV devices support clkena signals at the GCLK network level. This allows you to gate-off the clock even when a PLL is used. Upon re-enabling the output clock, the PLL does not need a resynchronization or re-lock period because the circuit gates off the clock at the clock network level. In addition, the PLL can remain locked independent of the clkena signals because the loop-related counters are not affected.

## **Programmable Bandwidth**

The PLL bandwidth is the measure of the PLL's ability to track the input clock and its associated jitter. PLLs of Cyclone IV devices provide advanced control of the PLL bandwidth using the programmable characteristics of the PLL loop, including loop filter and charge pump. The closed-loop gain 3-dB frequency in the PLL determines the PLL bandwidth. The bandwidth is approximately the unity gain point for open loop PLL response.

## **Phase Shift Implementation**

Phase shift is used to implement a robust solution for clock delays in Cyclone IV devices. Phase shift is implemented with a combination of the VCO phase output and the counter starting time. The VCO phase output and counter starting time are the most accurate methods of inserting delays, because they are based only on counter settings that are independent of process, voltage, and temperature.

You can phase shift the output clocks from the PLLs of Cyclone IV devices in one of two ways:

- Fine resolution using VCO phase taps

- Coarse resolution using counter starting time

Fine resolution phase shifts are implemented by allowing any of the output counters (C[4..0]) or the M counter to use any of the eight phases of the VCO as the reference clock. This allows you to adjust the delay time with a fine resolution.

Equation 5–1 shows the minimum delay time that you can insert using this method.

### Equation 5–1. Fine Resolution Phase Shift

$f_{\text{fine}} = \frac{T_{VCO}}{8} = \frac{1}{8f_{VCO}} = \frac{N}{8Mf_{REF}}$

in which  $f_{\text{REF}}$  is the input reference clock frequency.

For example, if  $f_{\text{REF}}$  is 100 MHz, N = 1, and M = 8, then  $f_{\text{VCO}}$  = 800 MHz, and  $\Phi_{\text{fine}}$  = 156.25 ps. The PLL operating frequency defines this phase shift, a value that depends on reference clock frequency and counter settings.

Coarse resolution phase shifts are implemented by delaying the start of the counters for a predetermined number of counter clocks. Equation 5–2 shows the coarse phase shift.

### Equation 5–2. Coarse Resolution Phase Shift

$\Phi_{\text{coarse}} = \frac{C-1}{f_{VCO}} = \frac{(C-1)N}{Mf_{REF}}$

*C* is the count value set for the counter delay time (this is the initial setting in the PLL usage section of the compilation report in the Quartus II software). If the initial value is 1,  $C - 1 = 0^{\circ}$  phase shift.

In Cyclone IV devices, DQS is used only during write mode in DDR2 and DDR SDRAM interfaces. Cyclone IV devices ignore DQS as the read-data strobe because the PHY internally generates the read capture clock for read mode. However, you must connect the DQS pin to the DQS signal in DDR2 and DDR SDRAM interfaces, or to the CQ signal in QDR II SRAM interfaces.

- Cyclone IV devices do not support differential strobe pins, which is an optional feature in the DDR2 SDRAM device.

- When you use the Altera Memory Controller MegaCore<sup>®</sup> function, the PHY is instantiated for you. For more information about the memory interface data path, refer to the *External Memory Interface Handbook*.

- ALTMEMPHY is a self-calibrating megafunction, enhanced to simplify the implementation of the read-data path in different memory interfaces. The auto-calibration feature of ALTMEMPHY provides ease-of-use by optimizing clock phases and frequencies across process, voltage, and temperature (PVT) variations. You can save on the global clock resources in Cyclone IV devices through the ALTMEMPHY megafunction because you are not required to route the DQS signals on the global clock buses (because DQS is ignored for read capture). Resynchronization issues do not arise because no transfer occurs from the memory domain clock (DQS) to the system domain for capturing data DQ.

All I/O banks in Cyclone IV devices can support DQ and DQS signals with DQ-bus modes of ×8, ×9, ×16, ×18, ×32, and ×36 except Cyclone IV GX devices that do not support left I/O bank interface. DDR2 and DDR SDRAM interfaces use ×8 mode DQS group regardless of the interface width. For a wider interface, you can use multiple ×8 DQ groups to achieve the desired width requirement.

In the ×9, ×18, and ×36 modes, a pair of complementary DQS pins (CQ and CQ#) drives up to 9, 18, or 36 DQ pins, respectively, in the group, to support one, two, or four parity bits and the corresponding data bits. The ×9, ×18, and ×36 modes support the QDR II memory interface. CQ# is the inverted read-clock signal that is connected to the complementary data strobe (DQS or CQ#) pin. You can use any unused DQ pins as regular user I/O pins if they are not used as memory interface signals.

For more information about unsupported DQS and DQ groups of the Cyclone IV transceivers that run at ≥2.97 Gbps data rate, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

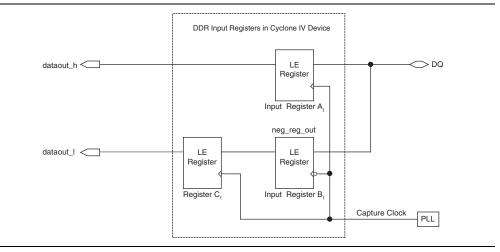

Figure 7–7 illustrates Cyclone IV DDR input registers.

Figure 7–7. Cyclone IV DDR Input Registers

These DDR input registers are implemented in the core of devices. The DDR data is first fed to two registers, input register  $A_I$  and input register  $B_I$ .

- Input register A<sub>I</sub> captures the DDR data present during the rising edge of the clock

- Input register B<sub>I</sub> captures the DDR data present during the falling edge of the clock

- Register C<sub>I</sub> aligns the data before it is synchronized with the system clock

The data from the DDR input register is fed to two registers, sync\_reg\_h and sync\_reg\_1, then the data is typically transferred to a FIFO block to synchronize the two data streams to the rising edge of the system clock. Because the read-capture clock is generated by the PLL, the read-data strobe signal (DQS or CQ) is not used during read operation in Cyclone IV devices; hence, postamble is not a concern in this case.

## Section III. System Integration

This section includes the following chapters:

- Chapter 8, Configuration and Remote System Upgrades in Cyclone IV Devices

- Chapter 9, SEU Mitigation in Cyclone IV Devices

- Chapter 10, JTAG Boundary-Scan Testing for Cyclone IV Devices

- Chapter 11, Power Requirements for Cyclone IV Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

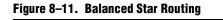

Figure 8–11 shows the recommended balanced star routing for multiple bus master interfaces to minimize signal integrity issues.

#### Notes to Figure 8-11:

- (1) Altera recommends that *M* does not exceed 6 inches, as listed in Table 8–11 on page 8–28.

- (2) Altera recommends using a balanced star routing. Keep the *N* length equal and as short as possible to minimize reflection noise from the transmission line. The *M* length is applicable for this setup.

### **Estimating AP Configuration Time**

AP configuration time is dominated by the time it takes to transfer data from the parallel flash to Cyclone IV E devices. This parallel interface is clocked by the Cyclone IV E DCLK output (generated from an internal oscillator). The DCLK minimum frequency when using the 40-MHz oscillator is 20 MHz (50 ns). In word-wide cascade programming, the DATA [15..0] bus transfers a 16-bit word and essentially cuts configuration time to approximately 1/16 of the AS configuration time. Equation 8–4 and Equation 8–5 show the configuration time calculations.

#### Equation 8-4.

Size  $\times \left(\frac{\text{maximum DCLK period}}{16 \text{ bits per DCLK cycle}}\right)$  = estimated maximum configuration time

Equation 8-5.

9,600,000 bits ×

$$\left(\frac{50 \text{ ns}}{16 \text{ bit}}\right)$$

= 30 ms

### Programming Serial Configuration Devices In-System with the JTAG Interface

Cyclone IV devices in a single- or multiple-device chain support in-system programming of a serial configuration device with the JTAG interface through the SFL design. The intelligent host or download cable of the board can use the four JTAG pins on the Cyclone IV device to program the serial configuration device in system, even if the host or download cable cannot access the configuration pins (DCLK, DATA, ASDI, and nCS pins).

The SFL design is a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the Cyclone IV device that uses their JTAG interface to access the EPCS JTAG Indirect Configuration Device Programming (.jic) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the SFL design.

In a multiple device chain, you must only configure the master device that controls the serial configuration device. Slave devices in the multiple device chain that are configured by the serial configuration device do not have to be configured when using this feature. To successfully use this feature, set the MSEL pins of the master device to select the AS configuration scheme (Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9). The serial configuration device in-system programming through the Cyclone IV device JTAG interface has three stages, which are described in the following sections:

- "Loading the SFL Design"

- "ISP of the Configuration Device" on page 8–56

- "Reconfiguration" on page 8–57

### Loading the SFL Design

The SFL design is a design inside the Cyclone IV device that bridges the JTAG interface and AS interface with glue logic.

The intelligent host uses the JTAG interface to configure the master device with a SFL design. The SFL design allows the master device to control the access of four serial configuration device pins, also known as the Active Serial Memory Interface (ASMI) pins, through the JTAG interface. The ASMI pins are serial clock input (DCLK), serial data output (DATA), AS data input (ASDI), and active-low chip select (nCS) pins.

## 11. Power Requirements for Cyclone IV Devices

### CYIV-51011-1.3

This chapter describes information about external power supply requirements, hot-socketing specifications, power-on reset (POR) requirements, and their implementation in Cyclone IV devices.

This chapter includes the following sections:

- "External Power Supply Requirements" on page 11–1

- "Hot-Socketing Specifications" on page 11–2

- "Hot-socketing Feature Implementation" on page 11–3

- "Power-On Reset Circuitry" on page 11–3

## **External Power Supply Requirements**

This section describes the different external power supplies required to power Cyclone IV devices. Table 11–1 and Table 11–2 list the descriptions of external power supply pins for Cyclone IV GX and Cyclone IV E devices, respectively.

**To** For power supply pin connection guidelines and power regulator sharing, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

| Power Supply Pin   | Nominal Voltage Level (V)    | Description                                                                                                       |  |  |  |  |  |

|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VCCINT             | 1.2                          | Core voltage, PCI Express (PCIe) hard IP block, and<br>transceiver physical coding sublayer (PCS) power<br>supply |  |  |  |  |  |

| VCCA (1)           | 2.5                          | PLL analog power supply                                                                                           |  |  |  |  |  |

| VCCD_PLL           | 1.2                          | PLL digital power supply                                                                                          |  |  |  |  |  |

| VCCIO (2)          | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | I/O banks power supply                                                                                            |  |  |  |  |  |

| VCC_CLKIN (3), (4) | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | Differential clock input pins power supply                                                                        |  |  |  |  |  |

| VCCH_GXB           | 2.5                          | Transceiver output (TX) buffer power supply                                                                       |  |  |  |  |  |

| VCCA_GXB           | 2.5                          | Transceiver physical medium attachment (PMA) and auxiliary power supply                                           |  |  |  |  |  |

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Section I. Transceivers**

This section provides a complete overview of all features relating to the Cyclone<sup>®</sup> IV device transceivers. This section includes the following chapters:

- Chapter 1, Cyclone IV Transceivers Architecture

- Chapter 2, Cyclone IV Reset Control and Power Down

- Chapter 3, Cyclone IV Dynamic Reconfiguration

## **Revision History**

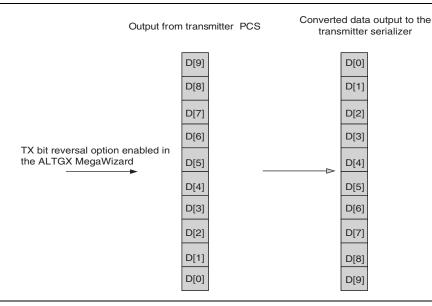

Refer to the chapter for its own specific revision history. For information about when the chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.  Bit reversal—reverses the transmit bit order from LSB-to-MSB (default) to MSB-to-LSB at the input to the serializer. For example, input data to serializer D[7..0] is rewired to D[0..7] for 8-bit data width, and D[9..0] is rewired to D[0..9] for 10-bit data width. Figure 1–10 shows the transmitter bit reversal feature.

Figure 1–10. Transmitter Bit Reversal Operation in Basic Single-Width Mode

- Input bit-flip—reverses the bit order at a byte level at the input of the transmitter phase compensation FIFO. For example, if the 16-bit parallel transmitter data at the tx\_datain port is '10111100 10101101' (16'hBCAD), selecting this option reverses the input data to the transmitter phase compensation FIFO to '00111101 10110101' (16'h3DB5).

- Bit-slip control—delays the data transmission by a number of specified bits to the serializer with the tx\_bitslipboundaryselect port. For usage details, refer to the "Transmit Bit-Slip Control" on page 1–76.

### Serializer

The serializer converts the low-speed parallel 8-bit or 10-bit data from the transmitter PCS to high-speed serial data for the transmitter output buffer. The serializer operates with a high-speed clock at half of the serial data rate. The serializer transmission sequence is LSB to MSB.

| <b>Functional Mode</b>   | Protocol                    | Key Feature                                                                               | Reference                                    |

|--------------------------|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------|

| Deterministic<br>Latency | Proprietary, CPRI,<br>OBSAI | TX PLL phase frequency detector (PFD) feedback, registered mode FIFO, TX bit-slip control | "Deterministic Latency<br>Mode" on page 1–73 |

| SDI                      | SDI                         | High-speed SERDES, CDR                                                                    | "SDI Mode" on<br>page 1–76                   |

Table 1–14. Transceiver Functional Modes for Protocol Implementation (Part 2 of 2)

### **Basic Mode**

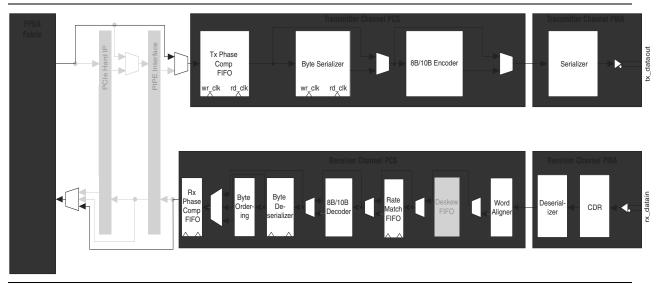

The Cyclone IV GX transceiver channel datapath is highly flexible in Basic mode to implement proprietary protocols. SATA, V-by-One, and Display Port protocol implementations in Cyclone IV GX transceiver are supported with Basic mode. Figure 1–44 shows the transceiver channel datapath supported in Basic mode.

Figure 1-44. Transceiver Channel Datapath in Basic Mode

In Serial RapidIO mode, the rate match FIFO compensates up to  $\pm 100$  ppm (200 ppm total) difference between the upstream transmitter and the local receiver reference clock.

Rate matcher is an optional block available for selection in Serial RapidIO mode. However, this block is not fully compliant to the SRIO specification. When enabled in the ALTGX MegaWizard Plug-In Manager, the default settings are:

- control pattern 1 = K28.5 with positive disparity

- skip pattern 1 = K29.7 with positive disparity

- control pattern 2 = K28.5 with negative disparity

- skip pattern 2 = K29.7 with negative disparity

When enabled, the rate match FIFO operation begins after the link is synchronized (indicated by assertion of rx\_syncstatus from the word aligner). When the rate matcher receives either of the two 10-bit control patterns followed by the respective 10-bit skip pattern, it inserts or deletes the 10-bit skip pattern as necessary to avoid the rate match FIFO from overflowing or under-running. The rate match FIFO can delete/insert a maximum of one skip pattern from a cluster.

The rate match FIFO may perform multiple insertion or deletion if the ppm difference is more than the allowable 200 ppm range. Ensure that the ppm difference in your system is less than 200 ppm.

### **XAUI Mode**

XAUI mode provides the bonded (×4) transceiver channel datapath configuration for XAUI protocol implementation. The Cyclone IV GX transceivers configured in XAUI mode provides the following functions:

- XGMII-to-PCS code conversion at transmitter datapath

- PCS-to-XGMII code conversion at receiver datapath

- channel deskewing of four lanes

- 8B/10B encoding and decoding

- IEEE P802.3ae-compliant synchronization state machine

- clock rate compensation

The XAUI is a self-managed interface to transparently extend the physical reach of the XGMII between the reconciliation sublayer and the PHY layer in the 10 Gbps LAN as shown in Figure 1–62. The XAUI interface consists of four lanes, each running at 3.125 Gbps with 8B/10B encoded data for a total of actual 10 Gbps data throughput. At the transmit side of the XAUI interface, the data and control characters are

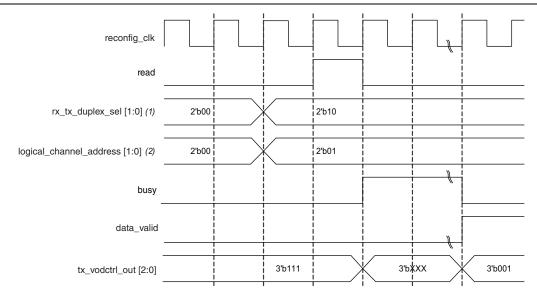

Figure 3–5 shows the read transaction waveform for Method 1.

Figure 3–5. Read Transaction Waveform—Use 'logical\_channel\_address port' Option

### Notes to Figure 3-5:

- (1) In this waveform example, you want to read from only the transmitter portion of the channel.

- (2) In this waveform example, the number of channels connected to the dynamic reconfiguration controller is four. Therefore, the logical channel address port is 2 bits wide.

Simultaneous write and read transactions are not allowed.

# Method 2: Writing the Same Control Signals to Control All the Transceiver Channels

This method does not require the logical\_channel\_address port. The PMA controls of all the transceiver channels connected to the ALTGX\_RECONFIG instance are reconfigured.

The **Use the same control signal for all the channels** option is available on the **Analog controls** tab of the ALTGX\_RECONFIG MegaWizard Plug-In Manager. If you enable this option, the width of the PMA control ports are fixed as follows:

### **PMA Control Ports Used in a Write Transaction**

- tx\_vodctrl is fixed to 3 bits

- tx preemp is fixed to 5 bits

- rx eqdcgain is fixed to 2 bits

- rx\_eqctrl is fixed to 4 bits

### **PMA Control Ports Used in a Read Transaction**

- tx\_vodctrl\_out is 3 bits per channel

- tx\_preemp\_out is 5 bits per channel

- rx eqdcgain out is 2 bits per channel

- rx\_eqctrl\_out is 4 bits per channel

For example, assume the number of channels controlled by the dynamic reconfiguration controller is two, tx\_vodctrl\_out is 6 bits wide.

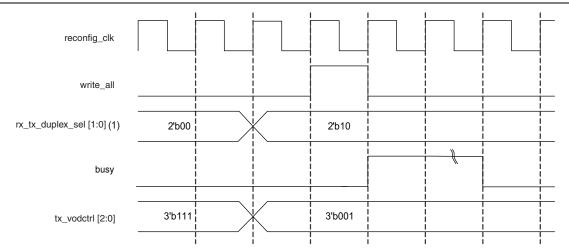

### Write Transaction

The value you set at the selected PMA control ports is written to all the transceiver channels connected to the ALTGX\_RECONFIG instance.

For example, assume you have enabled tx\_vodctrl in the ALTGX\_RECONFIG MegaWizard Plug-In Manager to reconfigure the V<sub>OD</sub> of the transceiver channels. To complete a write transaction to reconfigure the V<sub>OD</sub>, perform the following steps:

- 1. Before you initiate a write transaction, set the selected PMA control ports to the desired settings (for example, tx\_vodctrl = 3'b001).

- 2. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 3. Ensure that the busy signal is low before you start a write transaction.

- 4. Assert the write\_all signal for one reconfig\_clk clock cycle. This initiates the write transaction.

- 5. The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

Figure 3–6 shows the write transaction for Method 2.

### Figure 3–6. Write Transaction Waveform—Use the same control signal for all the channels Option

### Note to Figure 3-6:

(1) In this waveform example, you want to write to only the transmitter portion of the channel.

| Symbol                       | Modes | C6  |     |     |     | C7, 17 |     |     | C8, A7 |     |     | C8L, I8L |     |     | C9L |     |      | Unit |

|------------------------------|-------|-----|-----|-----|-----|--------|-----|-----|--------|-----|-----|----------|-----|-----|-----|-----|------|------|

|                              |       | Min | Тур | Max | Min | Тур    | Max | Min | Тур    | Max | Min | Тур      | Max | Min | Тур | Max | Unit |      |

| t <sub>LOCK</sub> <i>(2)</i> |       |     |     | 1   |     |        | 1   |     |        | 1   |     | _        | 1   |     |     | 1   | ms   |      |

### Table 1–32. Emulated RSDS\_E\_1R Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

Notes to Table 1-32:

(1) Emulated RSDS\_E\_1R transmitter is supported at the output pin of all I/O Banks of Cyclone IV E devices and I/O Banks 3, 4, 5, 6, 7, 8, and 9 of Cyclone IV GX devices.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                             | Madaa                                    |     | C6  |     |     | C7, I7 |       |     | C8, A7 |       |     | C8L, I | 8L    |     | Unit |       |      |

|------------------------------------|------------------------------------------|-----|-----|-----|-----|--------|-------|-----|--------|-------|-----|--------|-------|-----|------|-------|------|

| Symbol                             | Modes                                    | Min | Тур | Max | Min | Тур    | Max   | Min | Тур    | Max   | Min | Тур    | Max   | Min | Тур  | Max   | Unit |

|                                    | ×10                                      | 5   |     | 200 | 5   |        | 155.5 | 5   |        | 155.5 | 5   | —      | 155.5 | 5   |      | 132.5 | MHz  |

|                                    | ×8                                       | 5   |     | 200 | 5   | —      | 155.5 | 5   | —      | 155.5 | 5   | —      | 155.5 | 5   | _    | 132.5 | MHz  |

| f <sub>HSCLK</sub> (input<br>clock | ×7                                       | 5   | _   | 200 | 5   | _      | 155.5 | 5   | _      | 155.5 | 5   | —      | 155.5 | 5   | _    | 132.5 | MHz  |

| frequency)                         | ×4                                       | 5   |     | 200 | 5   | _      | 155.5 | 5   | _      | 155.5 | 5   | —      | 155.5 | 5   | _    | 132.5 | MHz  |

| ,                                  | ×2                                       | 5   |     | 200 | 5   | —      | 155.5 | 5   | —      | 155.5 | 5   | —      | 155.5 | 5   | _    | 132.5 | MHz  |

|                                    | ×1                                       | 5   | _   | 400 | 5   | _      | 311   | 5   | _      | 311   | 5   | —      | 311   | 5   | _    | 265   | MHz  |

|                                    | ×10                                      | 100 |     | 400 | 100 |        | 311   | 100 |        | 311   | 100 | _      | 311   | 100 |      | 265   | Mbps |

|                                    | ×8                                       | 80  |     | 400 | 80  | _      | 311   | 80  | —      | 311   | 80  | —      | 311   | 80  | _    | 265   | Mbps |

| Device<br>operation in             | ×7                                       | 70  | _   | 400 | 70  | _      | 311   | 70  | _      | 311   | 70  | —      | 311   | 70  | _    | 265   | Mbps |

| Mbps                               | ×4                                       | 40  |     | 400 | 40  |        | 311   | 40  |        | 311   | 40  | _      | 311   | 40  |      | 265   | Mbps |

|                                    | ×2                                       | 20  |     | 400 | 20  | _      | 311   | 20  | —      | 311   | 20  | —      | 311   | 20  | _    | 265   | Mbps |

|                                    | ×1                                       | 10  |     | 400 | 10  | _      | 311   | 10  | —      | 311   | 10  | —      | 311   | 10  | _    | 265   | Mbps |

| t <sub>DUTY</sub>                  | —                                        | 45  |     | 55  | 45  |        | 55    | 45  |        | 55    | 45  | _      | 55    | 45  |      | 55    | %    |

| TCCS                               | —                                        | —   |     | 200 | —   | _      | 200   | _   | —      | 200   | —   | —      | 200   | —   | _    | 200   | ps   |

| Output jitter<br>(peak to peak)    | —                                        | _   | _   | 500 | _   | _      | 500   | _   | _      | 550   | _   | _      | 600   | _   | _    | 700   | ps   |

| t <sub>RISE</sub>                  | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _   | 500    |       |     | 500    | _     | _   | 500    | _     | _   | 500  |       | ps   |

| t <sub>FALL</sub>                  | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _   | 500    | _     |     | 500    | _     | _   | 500    | _     | _   | 500  | _     | ps   |

| t <sub>LOCK</sub> (3)              | —                                        | —   | —   | 1   | —   | —      | 1     |     | —      | 1     | —   | _      | 1     | —   | —    | 1     | ms   |

Table 1–33. Mini-LVDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4)

Notes to Table 1-33:

(1) Applicable for true and emulated mini-LVDS transmitter.

(2) Cyclone IV E—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 1, 2, 5, and 6. Emulated mini-LVDS transmitter is supported at the output pin of all I/O banks.

Cyclone IV GY—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5.

Cyclone IV GX—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(3)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(4) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                          | Modes   | C6  |     | C7, | , 17 | C8, | A7  | C8L, | , 18L | C   | - Unit |      |

|---------------------------------|---------|-----|-----|-----|------|-----|-----|------|-------|-----|--------|------|

|                                 | INIOUES | Min | Max | Min | Max  | Min | Max | Min  | Max   | Min | Max    | UIII |

| t <sub>DUTY</sub>               | —       | 45  | 55  | 45  | 55   | 45  | 55  | 45   | 55    | 45  | 55     | %    |

| TCCS                            | —       | _   | 200 | —   | 200  | _   | 200 | _    | 200   | —   | 200    | ps   |

| Output jitter<br>(peak to peak) | _       |     | 500 | _   | 500  | _   | 550 | _    | 600   | _   | 700    | ps   |

| t <sub>LOCK</sub> (2)           | _       |     | 1   | _   | 1    |     | 1   | _    | 1     | _   | 1      | ms   |

### Table 1–35. Emulated LVDS Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

### Notes to Table 1-35:

(1) Cyclone IV E—emulated LVDS transmitter is supported at the output pin of all I/O Banks.

Cyclone IV GX—emulated LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Cumbel                    | Madaa | C   | 6     | C7, | , 17  | C8, | A7    | C8L | , 18L | CS  | )L  |      |

|---------------------------|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-----|------|

| Symbol                    | Modes | Min | Max   | Min | Max   | Min | Max   | Min | Max   | Min | Max | Unit |

|                           | ×10   | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

|                           | ×8    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

| f <sub>HSCLK</sub> (input | ×7    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

| clock<br>frequency)       | ×4    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

|                           | ×2    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

|                           | ×1    | 10  | 437.5 | 10  | 402.5 | 10  | 402.5 | 10  | 362   | 10  | 265 | MHz  |

|                           | ×10   | 100 | 875   | 100 | 740   | 100 | 640   | 100 | 640   | 100 | 500 | Mbps |

|                           | ×8    | 80  | 875   | 80  | 740   | 80  | 640   | 80  | 640   | 80  | 500 | Mbps |

| HSIODR                    | ×7    | 70  | 875   | 70  | 740   | 70  | 640   | 70  | 640   | 70  | 500 | Mbps |

| HOIDDA                    | ×4    | 40  | 875   | 40  | 740   | 40  | 640   | 40  | 640   | 40  | 500 | Mbps |

|                           | ×2    | 20  | 875   | 20  | 740   | 20  | 640   | 20  | 640   | 20  | 500 | Mbps |

|                           | ×1    | 10  | 437.5 | 10  | 402.5 | 10  | 402.5 | 10  | 362   | 10  | 265 | Mbps |

| SW                        | —     | _   | 400   | _   | 400   | _   | 400   | _   | 550   | _   | 640 | ps   |

| Input jitter<br>tolerance | _     | _   | 500   | _   | 500   | _   | 550   | _   | 600   | _   | 700 | ps   |

| t <sub>LOCK</sub> (2)     | —     | _   | 1     | —   | 1     | _   | 1     | —   | 1     | —   | 1   | ms   |

Table 1–36. LVDS Receiver Timing Specifications for Cyclone IV Devices (1), (3)

#### Notes to Table 1-36:

(1) Cyclone IV E—LVDS receiver is supported at all I/O Banks.

Cyclone IV GX—LVDS receiver is supported at I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

### **External Memory Interface Specifications**

The external memory interfaces for Cyclone IV devices are auto-calibrating and easy to implement.