Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 1395                                                     |

| Number of Logic Elements/Cells | 22320                                                    |

| Total RAM Bits                 | 608256                                                   |

| Number of I/O                  | 79                                                       |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 144-LQFP Exposed Pad                                     |

| Supplier Device Package        | 144-EQFP (20x20)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce22e22c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

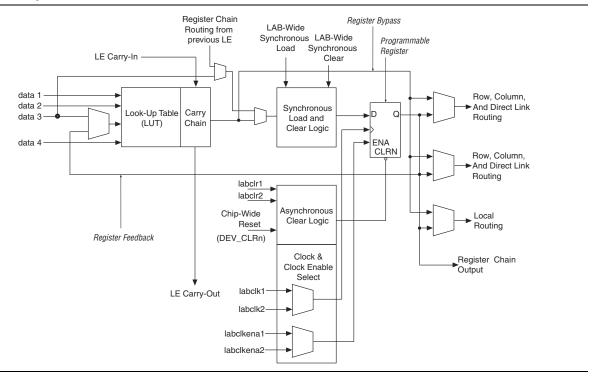

Figure 2–1 shows the LEs for Cyclone IV devices.

Figure 2–1. Cyclone IV Device LEs

## **LE Features**

You can configure the programmable register of each LE for D, T, JK, or SR flipflop operation. Each register has data, clock, clock enable, and clear inputs. Signals that use the global clock network, general-purpose I/O pins, or any internal logic can drive the clock and clear control signals of the register. Either general-purpose I/O pins or the internal logic can drive the clock enable. For combinational functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output independently drives these three outputs. Two LE outputs drive the column or row and direct link routing connections, while one LE drives the local interconnect resources. This allows the LUT to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the LUT for unrelated functions. The LAB-wide synchronous load control signal is not available when using register packing. For more information about the synchronous load control signal, refer to "LAB Control Signals" on page 2-6.

The register feedback mode allows the register output to feed back into the LUT of the same LE to ensure that the register is packed with its own fan-out LUT, providing another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

# 3. Memory Blocks in Cyclone IV Devices

#### CYIV-51003-1.1

Cyclone<sup>®</sup> IV devices feature embedded memory structures to address the on-chip memory needs of Altera<sup>®</sup> Cyclone IV device designs. The embedded memory structure consists of columns of M9K memory blocks that you can configure to provide various memory functions, such as RAM, shift registers, ROM, and FIFO buffers.

This chapter contains the following sections:

- "Memory Modes" on page 3–7

- "Clocking Modes" on page 3–14

- "Design Considerations" on page 3–15

## **Overview**

M9K blocks support the following features:

- 8,192 memory bits per block (9,216 bits per block including parity)

- Independent read-enable (rden) and write-enable (wren) signals for each port

- Packed mode in which the M9K memory block is split into two 4.5 K single-port RAMs

- Variable port configurations

- Single-port and simple dual-port modes support for all port widths

- True dual-port (one read and one write, two reads, or two writes) operation

- Byte enables for data input masking during writes

- Two clock-enable control signals for each port (port A and port B)

- Initialization file to pre-load memory content in RAM and ROM modes

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

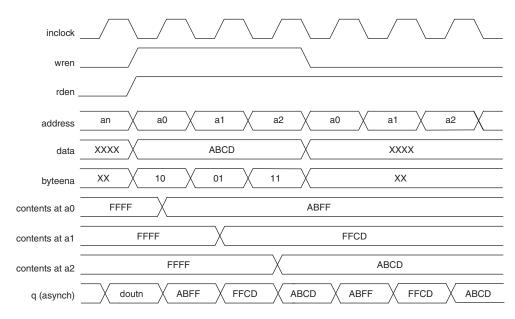

Figure 3–1 shows how the wren and byteena signals control the RAM operations.

Figure 3–1. Cyclone IV Devices byteena Functional Waveform (1)

#### Note to Figure 3-1:

(1) For this functional waveform, New Data mode is selected.

When a byteena bit is deasserted during a write cycle, the old data in the memory appears in the corresponding data-byte output. When a byteena bit is asserted during a write cycle, the corresponding data-byte output depends on the setting chosen in the Quartus<sup>®</sup> II software. The setting can either be the newly written data or the old data at that location.

Byte enables are only supported for True Dual-Port memory configurations when both the PortA and PortB data widths of the individual M9K memory blocks are multiples of 8 or 9 bits.

## **Packed Mode Support**

Cyclone IV devices M9K memory blocks support packed mode. You can implement two single-port memory blocks in a single block under the following conditions:

- Each of the two independent block sizes is less than or equal to half of the M9K block size. The maximum data width for each independent block is 18 bits wide.

- Each of the single-port memory blocks is configured in single-clock mode. For more information about packed mode support, refer to "Single-Port Mode" on page 3–8 and "Single-Clock Mode" on page 3–15.

Table 4–2 lists the sign of the multiplication results for the various operand sign representations. The results of the multiplication are signed if any one of the operands is a signed value.

Table 4–2. Multiplier Sign Representation

| Dat         | ta A        | Dat         | Result      |          |

|-------------|-------------|-------------|-------------|----------|

| signa Value | Logic Level | signb Value | Logic Level | nesuit   |

| Unsigned    | Low         | Unsigned    | Low         | Unsigned |

| Unsigned    | Low         | Signed      | High        | Signed   |

| Signed      | High        | Unsigned    | Low         | Signed   |

| Signed      | High        | Signed      | High        | Signed   |

Each embedded multiplier block has only one signa and one signb signal to control the sign representation of the input data to the block. If the embedded multiplier block has two 9 × 9 multipliers, the Data A input of both multipliers share the same signal, and the Data B input of both multipliers share the same signb signal. You can dynamically change the signa and signb signals to modify the sign representation of the input operands at run time. You can send the signa and signb signals through a dedicated input register. The multiplier offers full precision, regardless of the sign representation.

When the signa and signb signals are unused, the Quartus II software sets the multiplier to perform unsigned multiplication by default.

## **Output Registers**

You can register the embedded multiplier output with output registers in either 18- or 36-bit sections, depending on the operational mode of the multiplier. The following control signals are available for each output register in the embedded multiplier:

- clock

- clock enable

- asynchronous clear

All input and output registers in a single embedded multiplier are fed by the same clock, clock enable, and asynchronous clear signals.

# **Operational Modes**

You can use an embedded multiplier block in one of two operational modes, depending on the application needs:

- $\blacksquare$  One 18 × 18 multiplier

- Up to two  $9 \times 9$  independent multipliers

You can also use embedded multipliers of Cyclone IV devices to implement multiplier adder and multiplier accumulator functions, in which the multiplier portion of the function is implemented with embedded multipliers, and the adder or accumulator function is implemented in logic elements (LEs).

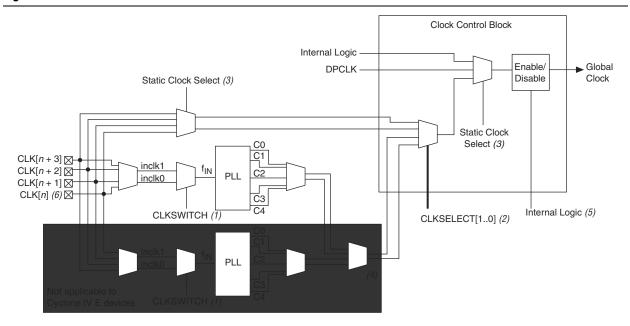

Figure 5–1 shows the clock control block.

Figure 5-1. Clock Control Block

#### Notes to Figure 5-1:

- (1) The clkswitch signal can either be set through the configuration file or dynamically set when using the manual PLL switchover feature. The output of the multiplexer is the input clock (f<sub>IN</sub>) for the PLL.

- (2) The clkselect[1..0] signals are fed by internal logic and are used to dynamically select the clock source for the GCLK when the device is in user mode.

- (3) The static clock select signals are set in the configuration file. Therefore, dynamic control when the device is in user mode is not feasible.

- (4) Two out of four PLL clock outputs are selected from adjacent PLLs to drive into the clock control block.

- (5) You can use internal logic to enable or disable the GCLK in user mode.

- (6) CLK[n] is not available on the left side of Cyclone IV E devices.

Each PLL generates five clock outputs through the c[4..0] counters. Two of these clocks can drive the GCLK through a clock control block, as shown in Figure 5–1.

For more information about how to use the clock control block in the Quartus II software, refer to the *ALTCLKCTRL Megafunction User Guide*.

## **Deterministic Latency Compensation Mode**

The deterministic latency mode compensates for the delay of the multipurpose PLLs through the clock network and serializer in Common Public Radio Interface (CPRI) applications. In this mode, the PLL PFD feedback path compensates the latency uncertainty in Tx dataout and Tx clkout paths relative to the reference clock.

## **Hardware Features**

Cyclone IV PLLs support several features for general-purpose clock management. This section discusses clock multiplication and division implementation, phase shifting implementations, and programmable duty cycles.

## **Clock Multiplication and Division**

Each Cyclone IV PLL provides clock synthesis for PLL output ports using M/(N\*post-scale counter) scaling factors. The input clock is divided by a pre-scale factor, N, and is then multiplied by the M feedback factor. The control loop drives the VCO to match  $f_{\rm IN}$  (M/N). Each output port has a unique post-scale counter that divides down the high-frequency VCO. For multiple PLL outputs with different frequencies, the VCO value is the least common multiple of the output frequencies that meets its frequency specifications. For example, if output frequencies required from one PLL are 33 and 66 MHz, the Quartus II software sets the VCO to 660 MHz (the least common multiple of 33 and 66 MHz in the VCO range). Then, the post-scale counters scale down the VCO frequency for each output port.

There is one pre-scale counter, N, and one multiply counter, M, per PLL, with a range of 1 to 512 for both M and N. The N counter does not use duty cycle control because the purpose of this counter is only to calculate frequency division. There are five generic post-scale counters per PLL that can feed GCLKs or external clock outputs. These post-scale counters range from 1 to 512 with a 50% duty cycle setting. The post-scale counters range from 1 to 256 with any non-50% duty cycle setting. The sum of the high/low count values chosen for a design selects the divide value for a given counter.

The Quartus II software automatically chooses the appropriate scaling factors according to the input frequency, multiplication, and division values entered into the ALTPLL megafunction.

Phase alignment between output counters is determined using the  $t_{PLL\_PSERR}$  specification.

# **High-Speed I/O Interface**

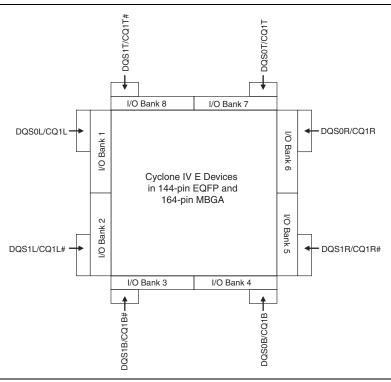

Cyclone IV E I/Os are separated into eight I/O banks, as shown in Figure 6–9 on page 6–17. Cyclone IV GX I/Os are separated into six user I/O banks with the left side of the device as the transceiver block, as shown in Figure 6–10 on page 6–18. Each bank has an independent power supply. True output drivers for LVDS, RSDS, mini-LVDS, and PPDS are on the right I/O banks. On the Cyclone IV E row I/O banks and the Cyclone IV GX right I/O banks, some of the differential pin pairs (p and n pins) of the true output drivers are not located on adjacent pins. In these cases, a power pin is located between the p and n pins. These I/O standards are also supported on all I/O banks using two single-ended output with the second output programmed as inverted, and an external resistor network. True input buffers for these I/O standards are supported on the top, bottom, and right I/O banks except for I/O bank 9.

# 7. External Memory Interfaces in Cyclone IV Devices

#### CYIV-51007-2.6

This chapter describes the memory interface pin support and the external memory interface features of Cyclone<sup>®</sup> IV devices.

In addition to an abundant supply of on-chip memory, Cyclone IV devices can easily interface with a broad range of external memory devices, including DDR2 SDRAM, DDR SDRAM, and QDR II SRAM. External memory devices are an important system component of a wide range of image processing, storage, communications, and general embedded applications.

Altera recommends that you construct all DDR2 or DDR SDRAM external memory interfaces using the Altera® ALTMEMPHY megafunction. You can implement the controller function using the Altera DDR2 or DDR SDRAM memory controllers, third-party controllers, or a custom controller for unique application needs. Cyclone IV devices support QDR II interfaces electrically, but Altera does not supply controller or physical layer (PHY) megafunctions for QDR II interfaces.

This chapter includes the following sections:

- "Cyclone IV Devices Memory Interfaces Pin Support" on page 7–2

- "Cyclone IV Devices Memory Interfaces Features" on page 7–12

- For more information about supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to the *External Memory Interface Handbook*.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 7–1 lists the number of DQS or DQ groups supported on each side of the Cyclone IV GX device.

Table 7-1. Cyclone IV GX Device DQS and DQ Bus Mode Support for Each Side of the Device

| Device               | Package          | Side       | Number<br>×8<br>Groups | Number<br>×9<br>Groups | Number<br>×16<br>Groups | Number<br>×18<br>Groups | Number<br>×32<br>Groups | Number<br>×36<br>Groups |

|----------------------|------------------|------------|------------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

|                      |                  | Right      | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

| EP4CGX15             | 169-pin FBGA     | Top (1)    | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|                      |                  | Bottom (2) | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|                      |                  | Right      | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|                      | 169-pin FBGA     | Top (1)    | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|                      |                  | Bottom (2) | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

| ED4CCV00             |                  | Right      | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

| EP4CGX22<br>EP4CGX30 | 324-pin FBGA     | Тор        | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

| EP4UGA3U             |                  | Bottom     | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|                      |                  | Right      | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      | 484-pin FBGA (3) | Тор        | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      |                  | Bottom     | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      | 484-pin FBGA     | Right      | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      |                  | Тор        | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

| EP4CGX50             |                  | Bottom     | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

| EP4CGX75             | 672-pin FBGA     | Right      | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      |                  | Тор        | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      |                  | Bottom     | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      |                  | Right      | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      | 484-pin FBGA     | Тор        | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      |                  | Bottom     | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

| EP4CGX110            |                  | Right      | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

| EP4CGX110            | 672-pin FBGA     | Тор        | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

| EF40UX13U            |                  | Bottom     | 4                      | 2                      | 2                       | 2                       | 1                       | 1                       |

|                      |                  | Right      | 6                      | 3                      | 2                       | 2                       | 1                       | 1                       |

|                      | 896-pin FBGA     | Тор        | 6                      | 3                      | 3                       | 3                       | 1                       | 1                       |

|                      |                  | Bottom     | 6                      | 3                      | 3                       | 3                       | 1                       | 1                       |

### Notes to Table 7-1:

<sup>(1)</sup> Some of the DQ pins can be used as RUP and RDN pins. You cannot use these groups if you are using these pins as RUP and RDN pins for OCT calibration

<sup>(2)</sup> Some of the DQ pins can be used as RUP pins while the DM pins can be used as RDN pins. You cannot use these groups if you are using the RUP and RDN pins for OCT calibration.

<sup>(3)</sup> Only available for EP4CGX30 device.

Figure 7–6 shows the location and numbering of the DQS, DQ, or CQ# pins in I/O banks of the Cyclone IV E device in the 144-pin EQFP and 164-pin MBGA packages.

Figure 7–6. DQS, CQ, or CQ# Pins for Cyclone IV E Devices in the 144-Pin EQFP and 164-pin MBGA Packages

In Cyclone IV devices, the  $\times 9$  mode uses the same DQ and DQS pins as the  $\times 8$  mode, and one additional DQ pin that serves as a regular I/O pin in the  $\times 8$  mode. The  $\times 18$  mode uses the same DQ and DQS pins as  $\times 16$  mode, with two additional DQ pins that serve as regular I/O pins in the  $\times 16$  mode. Similarly, the  $\times 36$  mode uses the same DQ and DQS pins as the  $\times 32$  mode, with four additional DQ pins that serve as regular I/O pins in the  $\times 32$  mode. When not used as DQ or DQS pins, the memory interface pins are available as regular I/O pins.

## **Optional Parity, DM, and Error Correction Coding Pins**

Cyclone IV devices support parity in  $\times 9$ ,  $\times 18$ , and  $\times 36$  modes. One parity bit is available per eight bits of data pins. You can use any of the DQ pins for parity in Cyclone IV devices because the parity pins are treated and configured similarly to DQ pins.

DM pins are only required when writing to DDR2 and DDR SDRAM devices. QDR II SRAM devices use the BWS# signal to select the byte to be written into memory. A low signal on the DM or BWS# pin indicates the write is valid. Driving the DM or BWS# pin high causes the memory to mask the DQ signals. Each group of DQS and DQ signals has one DM pin. Similar to the DQ output signals, the DM signals are clocked by the  $-90^{\circ}$  shifted clock.

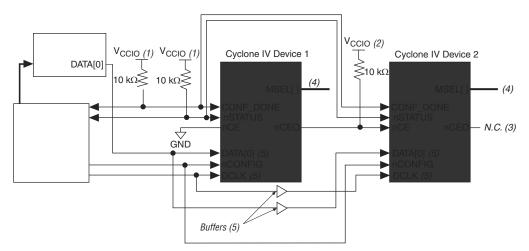

To ensure DCLK and DATA [0] are not left floating at the end of configuration, the MAX II device must drive them either high or low, whichever is convenient on your board. The DATA [0] pin is available as a user I/O pin after configuration. In the PS scheme, the DATA [0] pin is tri-stated by default in user mode and must be driven by the external host device. To change this default option in the Quartus II software, select the **Dual-Purpose Pins** tab of the **Device and Pin Options** dialog box.

The configuration clock (DCLK) speed must be below the specified system frequency to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

The external host device can also monitor CONF\_DONE and INIT\_DONE to ensure successful configuration. The CONF\_DONE pin must be monitored by the external device to detect errors and to determine when programming is complete. If all configuration data is sent, but CONF\_DONE or INIT\_DONE has not gone high, the external device must reconfigure the target device.

Figure 8–14 shows how to configure multiple devices using an external host device. This circuit is similar to the PS configuration circuit for a single device, except that Cyclone IV devices are cascaded for multi-device configuration.

Figure 8-14. Multi-Device PS Configuration Using an External Host

### Notes to Figure 8-14:

- (1) The pull-up resistor must be connected to a supply that provides an acceptable input signal for all devices in the chain. V<sub>CC</sub> must be high enough to meet the V<sub>IH</sub> specification of the I/O on the device and the external host.

- (2) Connect the pull-up resistor to the  $V_{\text{CCIO}}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

Table 8–20. Dedicated Configuration Pins on the Cyclone IV Device (Part 2 of 4)

| Pin Name  | User Mode                                           | Configuration<br>Scheme   | Pin Type                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|-----------------------------------------------------|---------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                                     | All                       |                             | ■ Status output—the target Cyclone IV device drives the CONF_DONE pin low before and during configuration. After all the configuration data is received without error and the initialization cycle starts, the target device releases CONF_DONE.                                                                                                                                                                                                                                       |

| CONF_DONE | N/A                                                 |                           | Bidirectional<br>open-drain | ■ Status input—after all the data is received and CONF_DONE goes high, the target device initializes and enters user mode. The CONF_DONE pin must have an external 10-kΩ pull-up resistor in order for the device to initialize.                                                                                                                                                                                                                                                       |

|           |                                                     |                           |                             | Driving CONF_DONE low after configuration and initialization does not affect the configured device. Do not connect bus holds or ADC to CONF_DONE pin.                                                                                                                                                                                                                                                                                                                                  |

| nCE       | N/A                                                 | All                       | Input                       | Active-low chip enable. The nCE pin activates the Cyclone IV device with a low signal to allow configuration. You must hold nCE pin low during configuration, initialization, and user-mode. In a single-device configuration, you must tie the nCE pin low. In a multi-device configuration, nCE of the first device is tied low while its nCEO pin is connected to nCE of the next device in the chain. You must hold the nCE pin low for successful JTAG programming of the device. |

|           | N/A if<br>option is on.<br>I/O if option<br>is off. | A11                       | Output<br>open-drain        | Output that drives low when configuration is complete. In a single-device configuration, you can leave this pin floating or use it as a user I/O pin after configuration. In a multidevice configuration, this pin feeds the nCE pin of the next device. The nCEO of the last device in the chain is left floating or used as a user I/O pin after configuration.                                                                                                                      |

| nCEO      |                                                     | option All                |                             | If you use the nCEO pin to feed the nCE pin of the next device, use an external 10-k $\Omega$ pull-up resistor to pull the nCEO pin high to the V <sub>CCIO</sub> voltage of its I/O bank to help the internal weak pull-up resistor.                                                                                                                                                                                                                                                  |

|           |                                                     |                           |                             | If you use the nCEO pin as a user I/O pin after configuration, set the state of the pin on the <b>Dual-Purpose Pin</b> settings.                                                                                                                                                                                                                                                                                                                                                       |

| nCSO,     |                                                     | I/O AS, AP <sup>(2)</sup> | Output                      | Output control signal from the Cyclone IV device to the serial configuration device in AS mode that enables the configuration device. This pin functions as nCso in AS mode and FLASH_nCE in AP mode.                                                                                                                                                                                                                                                                                  |

| FLASH_nCE | 1/0                                                 |                           |                             | Output control signal from the Cyclone IV device to the parallel flash in AP mode that enables the flash. Connects to the CE# pin on the Micron P30 or P33 flash. (2)                                                                                                                                                                                                                                                                                                                  |

|           |                                                     |                           |                             | This pin has an internal pull-up resistor that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                       |

May 2013 Altera Corporation Cyclone IV Device Handbook,

Table 8–20. Dedicated Configuration Pins on the Cyclone IV Device (Part 3 of 4)

| Pin Name             | User Mode | Configuration<br>Scheme       | Pin Type                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-----------|-------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | N/A       |                               | Input (PS,<br>FPP) (2)                                          | In PS and FPP configuration, DCLK is the clock input used to clock data from an external source into the target Cyclone IV device. Data is latched into the device on the rising edge of DCLK.                                                                                                                                                                                                                                                                           |

|                      |           |                               |                                                                 | In AS mode, DCLK is an output from the Cyclone IV device that provides timing for the configuration interface. It has an internal pull-up resistor (typically 25 k $\Omega$ ) that is always active.                                                                                                                                                                                                                                                                     |

| DCLK (1)             |           | PS, FPP, AS,<br>AP <i>(2)</i> | Output (AS,                                                     | In AP mode, DCLK is an output from the Cyclone IV E device that provides timing for the configuration interface. (2)                                                                                                                                                                                                                                                                                                                                                     |

|                      | I/O       |                               | AP)                                                             | In AS or AP configuration schemes, this pin is driven into an inactive state after configuration completes.  Alternatively, in active schemes, you can use this pin as a user I/O during user mode. In PS or FPP schemes that use a control host, you must drive DCLK either high or low, whichever is more convenient. In passive schemes, you cannot use DCLK as a user I/O in user mode. Toggling this pin after configuration does not affect the configured device. |

|                      | 1/0       | PS, FPP, AS,<br>AP (2)        | Input (PS,<br>FPP, AS).<br>Bidirectional<br>(AP) <sup>(2)</sup> | Data input. In serial configuration modes, bit-wide configuration data is presented to the target Cyclone IV device on the DATA [0] pin.                                                                                                                                                                                                                                                                                                                                 |

| DATA [0] <i>(1</i> ) |           |                               |                                                                 | In AS mode, DATA[0] has an internal pull-up resistor that is always active. After AS configuration, DATA[0] is a dedicated input pin with optional user control.                                                                                                                                                                                                                                                                                                         |

|                      |           |                               |                                                                 | After PS or FPP configuration, DATA[0] is available as a user I/O pin. The state of this pin depends on the <b>Dual-Purpose Pin</b> settings.                                                                                                                                                                                                                                                                                                                            |

|                      |           |                               |                                                                 | After AP configuration, DATA[0] is a dedicated bidirectional pin with optional user control. (2)                                                                                                                                                                                                                                                                                                                                                                         |

|                      |           |                               |                                                                 | The DATA[1] pin functions as the ASDO pin in AS mode.  Data input in non-AS mode. Control signal from the  Cyclone IV device to the serial configuration device in AS  mode used to read out configuration data.                                                                                                                                                                                                                                                         |

|                      |           |                               |                                                                 | In AS mode, DATA[1] has an internal pull-up resistor that is always active. After AS configuration, DATA[1] is a dedicated output pin with optional user control.                                                                                                                                                                                                                                                                                                        |

| DATA[1]/             | 1/0       | FPP, AS, AP                   | Input (FPP).<br>Output (AS).                                    | In a PS configuration scheme, DATA[1] functions as a user I/O pin during configuration, which means it is tri-stated.                                                                                                                                                                                                                                                                                                                                                    |

| ASDO (1)             | 1/0       | (2)                           | Bidirectional<br>(AP) (2)                                       | After FPP configuration, DATA [1] is available as a user I/O pin and the state of this pin depends on the <b>Dual-Purpose Pin</b> settings.                                                                                                                                                                                                                                                                                                                              |

|                      |           |                               |                                                                 | In an AP configuration scheme, for Cyclone IV E devices only, the byte-wide or word-wide configuration data is presented to the target Cyclone IV E device on DATA [70] or DATA [150], respectively. After AP configuration, DATA [1] is a dedicated bidirectional pin with optional user control. (2)                                                                                                                                                                   |

# 10. JTAG Boundary-Scan Testing for Cyclone IV Devices

#### CYIV-51010-1.3

This chapter describes the boundary-scan test (BST) features that are supported in Cyclone® IV devices. The features are similar to Cyclone III devices, unless stated in this chapter.

Cyclone IV devices (Cyclone IV E devices and Cyclone IV GX devices) support IEEE Std. 1149.1. Cyclone IV GX devices also support IEEE Std. 1149.6. The IEEE Std. 1149.6 (AC JTAG) is only supported on the high-speed serial interface (HSSI) transceivers in Cyclone IV GX devices. The purpose of IEEE Std. 1149.6 is to enable board-level connectivity checking between transmitters and receivers that are AC coupled.

This chapter includes the following sections:

- "IEEE Std. 1149.6 Boundary-Scan Register" on page 10–2

- "BST Operation Control" on page 10–3

- "I/O Voltage Support in a JTAG Chain" on page 10–5

- "Boundary-Scan Description Language Support" on page 10–6

- For more information about the JTAG instructions code with descriptions and IEEE Std.1149.1 BST guidelines, refer to the *IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone III Devices* chapter.

- For more information about the following topics, refer to *AN 39: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices*:

- IEEE Std. 1149.1 BST architecture and circuitry

- TAP controller state-machine

- Instruction mode

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Chapter Revision Dates**

The chapters in this document, Cyclone IV Device Handbook, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Cyclone IV Transceivers Architecture

Revised: February 2015 Part Number: CYIV-52001-3.7

Chapter 2. Cyclone IV Reset Control and Power Down

Revised: *September* 2014 Part Number: *CYIV-*52002-1.4

Chapter 3. Cyclone IV Dynamic Reconfiguration

Revised: *November 2011* Part Number: *CYIV-52003-2.1*

2.5

3.125

| Table 1 | Table 1–25. PRBS, High and Low Frequency Patterns, and Channel Settings (Part 2 of 2) |                     |                                  |                              |                                                                       |                                                                      |                                   |                              |                                                                       |                                                                      |

|---------|---------------------------------------------------------------------------------------|---------------------|----------------------------------|------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------|------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|

|         |                                                                                       | 8-bit Channel Width |                                  |                              | 10-bit Channel Width                                                  |                                                                      |                                   |                              |                                                                       |                                                                      |

| Patter  | ns                                                                                    | Polynomial          | Channel<br>Width<br>of<br>8 bits | Word<br>Alignment<br>Pattern | Maximum<br>Data Rate<br>(Gbps) for<br>F324 and<br>Smaller<br>Packages | Maximum<br>Data Rate<br>(Gbps) for<br>F484 and<br>Larger<br>Packages | Channel<br>Width<br>of<br>10-bits | Word<br>Alignment<br>Pattern | Maximum<br>Data Rate<br>(Gbps) for<br>F324 and<br>Smaller<br>Packages | Maximum<br>Data Rate<br>(Gbps) for<br>F484 and<br>Larger<br>Packages |

| Low     |                                                                                       |                     |                                  |                              |                                                                       |                                                                      |                                   |                              |                                                                       |                                                                      |

#### Notes to Table 1-25:

Frequency (2)

1111100000

- (1) Channel width refers to the What is the channel width? option in the General screen of the ALTGX MegaWizard Plug-In Manager. Based on the selection, an 8 or 10 bits wide pattern is generated as indicated by a Yes (Y) or No (N).

- (2) A verifier and associated rx bistdone and rx bisterr signals are not available for the specified patterns.

You can enable the serial loopback option to loop the generated PRBS patterns to the receiver channel for verifier to check the PRBS patterns. When the PRBS pattern is received, the rx bisterr and rx bistdone signals indicate the status of the verifier. After the word aligner restores the word boundary, the rx bistdone signal is driven high when the verifier receives a complete pattern cycle and remains asserted until it is reset using the rx digitalreset port. After the assertion of rx bistdone, the rx bisterr signal is asserted for a minimum of three rx clkout cycles when errors are detected in the data and deasserts if the following PRBS sequence contains no error. You can reset the PRBS pattern generator and verifier by asserting the tx\_digitalreset and rx\_digitalreset ports, respectively.

Table 1–27. Receiver Ports in ALTGX Megafunction for Cyclone IV GX (Part 1 of 3)

| Block  | Port Name                                                            | Input/<br>Output                                                                                                                                                                                                | Clock Domain                                                                                                                                                                                                | Description                                                                                                                                                                                                                                    |  |  |

|--------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RX PCS | rx_syncstatus                                                        | Output                                                                                                                                                                                                          | Synchronous to tx_clkout (non-bonded modes with rate match FIFO), rx_clkout (non-bonded modes without rate match FIFO), coreclkout (bonded modes), or rx_coreclk (when using the optional rx_coreclk input) | Word alignment synchronization status indicator. This signal passes through the RX Phase Compensation FIFO.  Not available in bit-slip mode                                                                                                    |  |  |

|        | rx_patternde tect  Output  bonded FIFO), r. modes v. corecll rx_core |                                                                                                                                                                                                                 | Synchronous to tx_clkout (non-bonded modes with rate match FIFO), rx_clkout (non-bonded modes without rate match FIFO), coreclkout (bonded modes), or rx_coreclk (when using the optional rx_coreclk input) | Indicates when the word alignment logic detects the alignment pattern in the current word boundary. This signal passes through the RX Phase Compensation FIFO.                                                                                 |  |  |

|        | rx_bitslip                                                           | Asynchronous signal. Minimum pulse width is two parallel clock cycles.                                                                                                                                          |                                                                                                                                                                                                             | Bit-slip control for the word aligner configured in bit-slip mode.  At every rising edge, word aligner slips one bit into the received data stream, effectively shifting the word boundary by one bit.                                         |  |  |

|        | rx_rlv                                                               | Output  Asynchronous signal. Driven for a minimum of two recovered clock cycles in configurations without byte serializer and a minimum of three recovered clock cycles in configurations with byte serializer. |                                                                                                                                                                                                             | Run-length violation indicator.  A high pulse indicates that the number of consecutive 1s or 0s in the received data stream exceeds the programmed run length violation threshold.                                                             |  |  |

|        | rx_invpolarity                                                       | Input                                                                                                                                                                                                           | Asynchronous signal. Minimum pulse width is two parallel clock cycles.                                                                                                                                      | Generic receiver polarity inversion control.  A high level to invert the polarity of every bit of the 8-or 10-bit data to the word aligner.                                                                                                    |  |  |

|        | rx_enapattern<br>align                                               | Input                                                                                                                                                                                                           | Asynchronous signal.                                                                                                                                                                                        | Controls the word aligner operation configured in manual alignment mode.                                                                                                                                                                       |  |  |

|        | rx_rmfifodata                                                        |                                                                                                                                                                                                                 | Synchronous to tx_clkout (non-bonded modes) or coreclkout (bonded modes)                                                                                                                                    | Rate match FIFO insertion status indicator.  • A high level indicates the rate match pattern byte is inserted to compensate for the ppm difference in the reference clock frequencies between the upstream transmitter and the local receiver. |  |  |

|        | rx_rmfifodata<br>deleted                                             | Output                                                                                                                                                                                                          | Synchronous to tx_clkout (non-bonded modes) or coreclkout (bonded modes)                                                                                                                                    | Rate match FIFO deletion status indicator.  • A high level indicates the rate match pattern byte is deleted to compensate for the ppm difference in the reference clock frequencies between the upstream transmitter and the local receiver.   |  |  |

Table 3-2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 5 of 7)

| Port Name                    | Input/<br>Output | Description                                                                                                                                                                                                                                                                                |                                                                                                                                         |                                             |  |  |  |

|------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|

|                              |                  | This is an optional pre-emphasis write control for the transmit buffer. Depending on what value you set at this input, the controller dynamically writes the value to the pre-emphasis control register of the transmit buffer.                                                            |                                                                                                                                         |                                             |  |  |  |

|                              |                  | The width of this signal is fixed to 5 bits if you enable either the <b>Use</b> 'logical_channel_address' port for Analog controls reconfiguration option of same control signal for all the channels option in the Analog controls screen the width of this signal is 5 bits per channel. |                                                                                                                                         |                                             |  |  |  |

|                              |                  | tx_preemp[40]                                                                                                                                                                                                                                                                              | Corresponding ALTGX instance settings                                                                                                   | Corresponding pre-<br>emphasis setting (mA) |  |  |  |

|                              |                  | 00000                                                                                                                                                                                                                                                                                      | 0                                                                                                                                       | Disabled                                    |  |  |  |

|                              |                  | 00001                                                                                                                                                                                                                                                                                      | 1                                                                                                                                       | 0.5                                         |  |  |  |

| tx preemp[40] (1)            | Input            | 00101                                                                                                                                                                                                                                                                                      | 5                                                                                                                                       | 1.0                                         |  |  |  |

| en_preep[10]                 | mput             | 01001                                                                                                                                                                                                                                                                                      | 9                                                                                                                                       | 1.5                                         |  |  |  |

|                              |                  | 01101                                                                                                                                                                                                                                                                                      | 13                                                                                                                                      | 2.0                                         |  |  |  |

|                              |                  | 10000                                                                                                                                                                                                                                                                                      | 16                                                                                                                                      | 2.375                                       |  |  |  |

|                              |                  | 10001                                                                                                                                                                                                                                                                                      | 17                                                                                                                                      | 2.5                                         |  |  |  |

|                              |                  | 10010                                                                                                                                                                                                                                                                                      | 18                                                                                                                                      | 2.625                                       |  |  |  |

|                              |                  | 10011                                                                                                                                                                                                                                                                                      | 19                                                                                                                                      | 2.75                                        |  |  |  |

|                              |                  | 10100                                                                                                                                                                                                                                                                                      | 20                                                                                                                                      | 2.875                                       |  |  |  |

|                              |                  | 10101                                                                                                                                                                                                                                                                                      | 21                                                                                                                                      | 3.0                                         |  |  |  |

|                              |                  | All other values => N/A                                                                                                                                                                                                                                                                    |                                                                                                                                         |                                             |  |  |  |

|                              |                  | This is an optional wr the PMA.                                                                                                                                                                                                                                                            | ite control to write an equalization                                                                                                    | control value for the receive side of       |  |  |  |

|                              |                  | 'logical_channel_ad<br>same control signal                                                                                                                                                                                                                                                 | nal is fixed to 4 bits if you enable of dress' port for Analog controls refor all the channels option in the all is 4 bits per channel. |                                             |  |  |  |

| rx_eqctrl[30] <sup>(1)</sup> | Input            | rx_eqctrl[30]                                                                                                                                                                                                                                                                              | Corresponding ALTGX instance                                                                                                            | settings                                    |  |  |  |

|                              |                  | 0001                                                                                                                                                                                                                                                                                       | Low                                                                                                                                     |                                             |  |  |  |

|                              |                  | 0101                                                                                                                                                                                                                                                                                       | Medium Low                                                                                                                              |                                             |  |  |  |

|                              |                  | 0100                                                                                                                                                                                                                                                                                       | Medium High                                                                                                                             |                                             |  |  |  |

|                              |                  | 0111                                                                                                                                                                                                                                                                                       | High                                                                                                                                    |                                             |  |  |  |

|                              |                  | All other values => N                                                                                                                                                                                                                                                                      | 'A                                                                                                                                      |                                             |  |  |  |

# 1. Cyclone IV Device Datasheet

#### CYIV-53001-2.1

This chapter describes the electrical and switching characteristics for Cyclone® IV devices. Electrical characteristics include operating conditions and power consumption. Switching characteristics include transceiver specifications, core, and periphery performance. This chapter also describes I/O timing, including programmable I/O element (IOE) delay and programmable output buffer delay.

This chapter includes the following sections:

- "Operating Conditions" on page 1–1

- "Power Consumption" on page 1–16

- "Switching Characteristics" on page 1–16

- "I/O Timing" on page 1–37

- "Glossary" on page 1–37

# **Operating Conditions**

When Cyclone IV devices are implemented in a system, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of Cyclone IV devices, you must consider the operating requirements described in this chapter.

Cyclone IV devices are offered in commercial, industrial, extended industrial and, automotive grades. Cyclone IV E devices offer –6 (fastest), –7, –8, –8L, and –9L speed grades for commercial devices, –8L speed grades for industrial devices, and –7 speed grade for extended industrial and automotive devices. Cyclone IV GX devices offer –6 (fastest), –7, and –8 speed grades for commercial devices and –7 speed grade for industrial devices.

In this chapter, a prefix associated with the operating temperature range is attached to the speed grades; commercial with a "C" prefix, industrial with an "I" prefix, and automotive with an "A" prefix. Therefore, commercial devices are indicated as C6, C7, C8, C8L, or C9L per respective speed grade. Industrial devices are indicated as I7, I8, or I8L. Automotive devices are indicated as A7.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.