# E·XFL

### Intel - EP4CE22E22C8L Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 1395                                                     |

| Number of Logic Elements/Cells | 22320                                                    |

| Total RAM Bits                 | 608256                                                   |

| Number of I/O                  | 79                                                       |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 144-LQFP Exposed Pad                                     |

| Supplier Device Package        | 144-EQFP (20x20)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce22e22c8l |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

In addition to the three general routing outputs, LEs in an LAB have register chain outputs, which allows registers in the same LAB to cascade together. The register chain output allows the LUTs to be used for combinational functions and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources.

## **LE Operating Modes**

Cyclone IV LEs operate in the following modes:

- Normal mode

- Arithmetic mode

The Quartus<sup>®</sup> II software automatically chooses the appropriate mode for common functions, such as counters, adders, subtractors, and arithmetic functions, in conjunction with parameterized functions such as the library of parameterized modules (LPM) functions. You can also create special-purpose functions that specify which LE operating mode to use for optimal performance, if required.

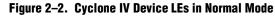

## **Normal Mode**

Normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (Figure 2–2). The Quartus II Compiler automatically selects the carry-in (cin) or the data3 signal as one of the inputs to the LUT. LEs in normal mode support packed registers and register feedback.

Figure 2–2 shows LEs in normal mode.

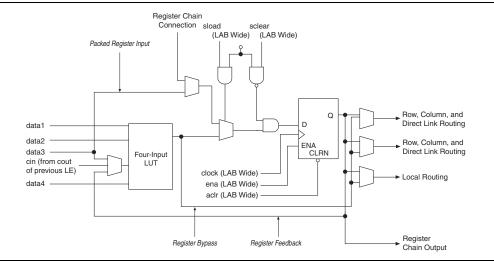

Figure 3–7 shows a timing waveform for read and write operations in single-port mode with unregistered outputs. Registering the outputs of the RAM simply delays the q output by one clock cycle.

Figure 3–7. Cyclone IV Devices Single-Port Mode Timing Waveform

## **Simple Dual-Port Mode**

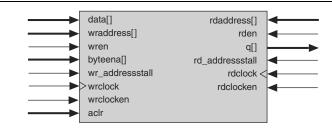

Simple dual-port mode supports simultaneous read and write operations to different locations. Figure 3–8 shows the simple dual-port memory configuration.

Figure 3–8. Cyclone IV Devices Simple Dual-Port Memory (1)

#### Note to Figure 3-8:

(1) Simple dual-port RAM supports input or output clock mode in addition to the read or write clock mode shown.

Cyclone IV devices M9K memory blocks support mixed-width configurations, allowing different read and write port widths. Table 3–3 lists mixed-width configurations.

Table 3–3.

Cyclone IV Devices M9K Block Mixed-Width Configurations (Simple Dual-Port Mode)

(Part 1 of 2)

| Dood Dort |              | Write Port   |              |              |              |              |          |          |          |  |  |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|----------|----------|----------|--|--|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 256 × 32     | 1024 × 9 | 512 × 18 | 256 × 36 |  |  |

| 8192 × 1  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _        |          | —        |  |  |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -        |          | —        |  |  |

| 2048 × 4  | ~            | ~            | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$ | _        | _        | —        |  |  |

| 1024 × 8  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _        | _        | —        |  |  |

For more information about the number of GCLK networks in each device density, refer to the *Cyclone IV FPGA Device Family Overview* chapter.

## **GCLK Network**

GCLKs drive throughout the entire device, feeding all device quadrants. All resources in the device (I/O elements, logic array blocks (LABs), dedicated multiplier blocks, and M9K memory blocks) can use GCLKs as clock sources. Use these clock network resources for control signals, such as clock enables and clears fed by an external pin. Internal logic can also drive GCLKs for internally generated GCLKs and asynchronous clears, clock enables, or other control signals with high fan-out.

Table 5–1, Table 5–2 on page 5–4, and Table 5–3 on page 5–7 list the connectivity of the clock sources to the GCLK networks.

Table 5-1. GCLK Network Connections for EP4CGX15, EP4CGX22, and EP4CGX30<sup>(1), (2)</sup> (Part 1 of 2)

| GCLK Network Clock            | GCLK Networks |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

|-------------------------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Sources                       | 0             | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           |

| CLK4/DIFFCLK_2n               |               | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            |

| CLK5/DIFFCLK_2p               |               | —            |              | —            |              | —            | $\checkmark$ | $\checkmark$ | —            | —            |              |              | —            |              |              |              |              | —            |              | —            |

| CLK6/DIFFCLK_3n               | _             | —            | —            | —            |              | —            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              | —            | —            |              | —            |              |              | —            |              | —            |

| CLK7/DIFFCLK_3p               |               | —            |              | —            |              | $\checkmark$ |              |              | $\checkmark$ |              |              |              | —            | _            |              | _            |              |              | —            | —            |

| CLK8/DIFFCLK_5n               |               | —            |              | _            |              | _            |              |              |              |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              |              |              |              | —            |

| CLK9/DIFFCLK_5p               | —             | —            |              | —            | —            | —            |              | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | _            |              | _            | —            | —            | —            | —            |

| CLK10/DIFFCLK_4n/RE<br>FCLK1n | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | ~            | _            | ~            | ~            | _            | _            | _            | _            | —            |

| CLK11/DIFFCLK_4p/RE<br>FCLK1p | _             | _            | _            |              |              | _            |              |              | _            | _            | ~            |              | _            | ~            |              | _            |              | _            |              | —            |

| CLK12/DIFFCLK_7p/RE<br>FCLK0p | _             |              | _            |              | _            | _            | _            | _            | _            | _            | _            | _            | _            |              | _            | $\checkmark$ | _            | ~            | _            | ~            |

| CLK13/DIFFCLK_7n/RE<br>FCLK0n | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            |              | ~            | ~            | _            | —            |

| CLK14/DIFFCLK_6p              |               | —            |              | —            |              | _            |              |              |              |              |              |              | —            | _            |              | _            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| CLK15/DIFFCLK_6n              |               | —            | —            | —            | _            | —            | —            | —            | —            |              |              | —            | —            | _            | —            | $\checkmark$ | _            | —            | $\checkmark$ | —            |

| PLL_1_C0                      | $\checkmark$  | _            |              | $\checkmark$ |              |              |              |              |              |              |              |              |              |              |              | >            |              |              | $\checkmark$ | —            |

| PLL_1_C1                      |               | <b>~</b>     | _            |              | >            | _            |              |              | _            | _            | _            |              | _            |              |              |              | >            | _            |              | $\checkmark$ |

| PLL_1_C2                      | $\checkmark$  | —            | $\checkmark$ | —            | _            | —            |              |              | —            | —            | —            |              | —            |              |              | >            | _            | $\checkmark$ | _            | —            |

| PLL_1_C3                      |               | <b>~</b>     | _            | $\checkmark$ |              | _            |              |              | _            | _            | _            |              | _            |              |              |              | >            | _            | >            | —            |

| PLL_1_C4                      |               | _            | $\checkmark$ |              | >            |              |              |              | _            |              |              |              |              |              |              |              |              | $\checkmark$ |              | $\checkmark$ |

| PLL_2_C0                      | $\checkmark$  | —            |              | $\checkmark$ |              |              |              |              |              |              | $\checkmark$ |              |              | $\checkmark$ |              | _            |              |              | —            | —            |

| PLL_2_C1                      |               | $\checkmark$ |              | —            | $\checkmark$ | —            |              |              | —            |              |              | $\checkmark$ | —            | _            | $\checkmark$ | _            | _            | —            | —            | —            |

| PLL_2_C2                      | $\checkmark$  | —            | $\checkmark$ |              |              |              |              |              |              |              | $\checkmark$ |              | $\checkmark$ | _            |              | _            |              |              | —            | —            |

| PLL_2_C3                      | —             | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | _            | >            | —            | —            | —            | —            | —            | —            |

| PLL_2_C4                      | _             | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            |              | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            |

| PLL_3_C0                      | —             | —            | —            | —            | _            | $\checkmark$ | —            | —            | ~            | —            | —            | —            | —            | _            | —            | >            | _            | —            | $\checkmark$ | —            |

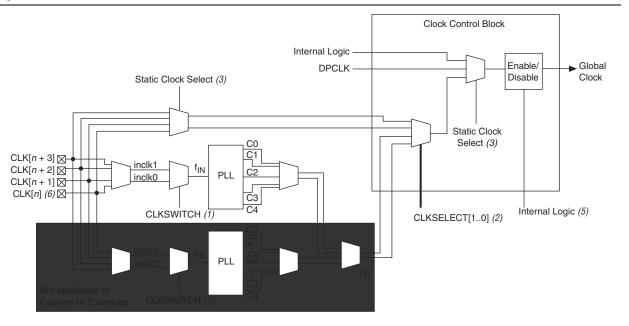

Figure 5–1 shows the clock control block.

#### Figure 5–1. Clock Control Block

#### Notes to Figure 5-1:

- (1) The clkswitch signal can either be set through the configuration file or dynamically set when using the manual PLL switchover feature. The output of the multiplexer is the input clock  $(f_{IN})$  for the PLL.

- (2) The clkselect[1..0] signals are fed by internal logic and are used to dynamically select the clock source for the GCLK when the device is in user mode.

- (3) The static clock select signals are set in the configuration file. Therefore, dynamic control when the device is in user mode is not feasible.

- (4) Two out of four PLL clock outputs are selected from adjacent PLLs to drive into the clock control block.

- (5) You can use internal logic to enable or disable the GCLK in user mode.

- (6) CLK [12] is not available on the left side of Cyclone IV E devices.

Each PLL generates five clock outputs through the c[4..0] counters. Two of these clocks can drive the GCLK through a clock control block, as shown in Figure 5–1.

For more information about how to use the clock control block in the Quartus II software, refer to the *ALTCLKCTRL Megafunction User Guide*.

| Signal Name | Description                                                                                                                                                                                                                                | Source                      | Destination                       |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------|--|

| scanclk     | Free running clock from core used in<br>combination with phasestep to enable or<br>disable dynamic phase shifting. Shared with<br>scanclk for dynamic reconfiguration.                                                                     | GCLK or I/O pins            | PLL<br>reconfiguration<br>circuit |  |

| phasedone   | When asserted, it indicates to core logic that<br>the phase adjustment is complete and PLL is<br>ready to act on a possible second adjustment<br>pulse. Asserts based on internal PLL timing.<br>De-asserts on the rising edge of scanclk. | PLL reconfiguration circuit | Logic array or<br>I/O pins        |  |

| Table 5-12. | <b>Dynamic Phase</b> | Shiftina | <b>Control Sign</b> | als ( | (Part 2 of 2) |

|-------------|----------------------|----------|---------------------|-------|---------------|

|             |                      | ••••••   | eenner ergn         |       |               |

Table 5–13 lists the PLL counter selection based on the corresponding PHASECOUNTERSELECT setting.

Table 5–13. Phase Counter Select Mapping

|     | phasecounterselec | t   | Calasia             |

|-----|-------------------|-----|---------------------|

| [2] | [1]               | [0] | Selects             |

| 0   | 0                 | 0   | All Output Counters |

| 0   | 0                 | 1   | M Counter           |

| 0   | 1                 | 0   | C0 Counter          |

| 0   | 1                 | 1   | C1 Counter          |

| 1   | 0                 | 0   | C2 Counter          |

| 1   | 0                 | 1   | C3 Counter          |

| 1   | 1                 | 0   | C4 Counter          |

To perform one dynamic phase-shift, follow these steps:

- 1. Set PHASEUPDOWN and PHASECOUNTERSELECT as required.

- 2. Assert PHASESTEP for at least two SCANCLK cycles. Each PHASESTEP pulse allows one phase shift.

- 3. Deassert PHASESTEP after PHASEDONE goes low.

- 4. Wait for PHASEDONE to go high.

- 5. Repeat steps 1 through 4 as many times as required to perform multiple phaseshifts.

<code>PHASEUPDOWN</code> and <code>PHASECOUNTERSELECT</code> signals are synchronous to <code>SCANCLK</code> and must meet the  $t_{su}$  and  $t_h$  requirements with respect to the <code>SCANCLK</code> edges.

You can repeat dynamic phase-shifting indefinitely. For example, in a design where the VCO frequency is set to 1,000 MHz and the output clock frequency is set to 100 MHz, performing 40 dynamic phase shifts (each one yields 125 ps phase shift) results in shifting the output clock by 180°, in other words, a phase shift of 5 ns.

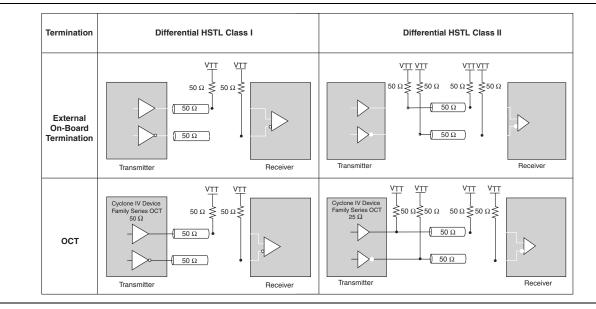

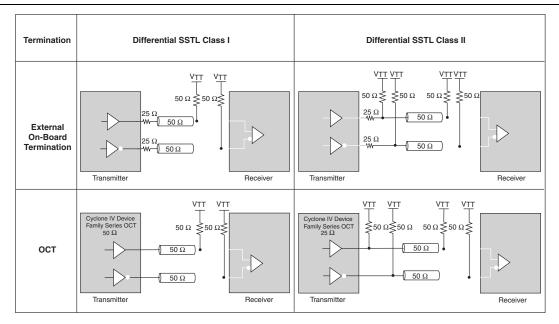

## **Differential I/O Standard Termination**

Differential I/O standards typically require a termination resistor between the two signals at the receiver. The termination resistor must match the differential load impedance of the bus (refer to Figure 6–7 and Figure 6–8).

Cyclone IV devices support differential SSTL-2 and SSTL-18, differential HSTL-18, HSTL-15, and HSTL-12, PPDS, LVDS, RSDS, mini-LVDS, and differential LVPECL.

Figure 6-7. Cyclone IV Devices Differential HSTL I/O Standard Class I and Class II Interface and Termination

Figure 6–8. Cyclone IV Devices Differential SSTL I/O Standard Class I and Class II Interface and Termination (1)

#### Note to Figure 6-8:

(1) Only Differential SSTL-2 I/O standard supports Class II output.

|               | Device    | Data Size (bits)          |

|---------------|-----------|---------------------------|

|               | EP4CGX15  | 3,805,568                 |

|               | EP4CGX22  | 7,600,040                 |

|               | EP4CGX30  | 7,600,040                 |

| Cyclone IV GX |           | 22,010,888 <sup>(1)</sup> |

|               | EP4CGX50  | 22,010,888                |

|               | EP4CGX75  | 22,010,888                |

|               | EP4CGX110 | 39,425,016                |

|               | EP4CGX150 | 39,425,016                |

#### Table 8-2. Uncompressed Raw Binary File (.rbf) Sizes for Cyclone IV Devices (Part 2 of 2)

Note to Table 8-2:

(1) Only for the F484 package.

Use the data in Table 8–2 to estimate the file size before design compilation. Different configuration file formats, such as Hexadecimal (.hex) or Tabular Text File (.ttf) formats, have different file sizes. However, for any specific version of the Quartus II software, any design targeted for the same device has the same uncompressed configuration file size. If you use compression, the file size varies after each compilation, because the compression ratio depends on the design.

• For more information about setting device configuration options or creating configuration files, refer to the *Software Settings* section in volume 2 of the *Configuration Handbook*.

### **Configuration and JTAG Pin I/O Requirements**

Cyclone IV devices are manufactured using the TSMC 60-nm low-k dielectric process. Although Cyclone IV devices use TSMC 2.5-V transistor technology in the I/O buffers, the devices are compatible and able to interface with 2.5, 3.0, and 3.3-V configuration voltage standards by following specific requirements.

All I/O inputs must maintain a maximum AC voltage of 4.1 V. When using a serial configuration device in an AS configuration scheme, you must connect a 25- $\Omega$  series resistor for the DATA[0] pin. When cascading the Cyclone IV device family in a multi-device configuration for AS, AP, FPP, and PS configuration schemes, you must connect the repeater buffers between the master and slave devices for the DATA and DCLK pins. When using the JTAG configuration scheme in a multi-device configuration, connect 25- $\Omega$  resistors on both ends of the TDO-TDI path if the TDO output driver is a non-Cyclone IV device.

The output resistance of the repeater buffers and the TDO path for all cases must fit the maximum overshoot equation shown in Equation 8–1.

Equation 8–1. <sup>(1)</sup>

$0.8Z_O \le R_E \le 1.8Z_O$

#### Note to Equation 8–1:

(1)  $Z_0$  is the transmission line impedance and  $R_E$  is the equivalent resistance of the output buffer.

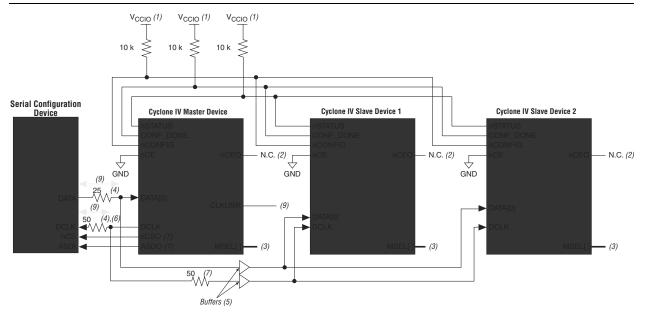

#### **Single SRAM Object File**

The second method configures both the master device and slave devices with the same **.sof**. The serial configuration device stores one copy of the **.sof**. You must set up one or more slave devices in the chain. All the slave devices must be set up in the same way (Figure 8–5).

#### Notes to Figure 8-5:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device of the Cyclone IV device in AS mode and the slave devices in PS mode. To connect the MSEL pins for the master device in AS mode and slave devices in PS mode, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) Connect the series resistor at the near end of the serial configuration device.

- (5) Connect the repeater buffers between the master and slave devices for DATA[0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (6) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

- (7) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (8) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- (9) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration device to the junction-split on both DCLK and Data0 line is 3.5 inches.

In this setup, all the Cyclone IV devices in the chain are connected for concurrent configuration. This reduces the AS configuration time because all the Cyclone IV devices are configured in one configuration cycle. Connect the nCE input pins of all the Cyclone IV devices to GND. You can either leave the nCEO output pins on all the Cyclone IV devices unconnected or use the nCEO output pins as normal user I/O pins. The DATA and DCLK pins are connected in parallel to all the Cyclone IV devices.

resistors.

Default read mode of the supported parallel flash memory and all writes to the parallel flash memory are asynchronous. Both the parallel flash families support a synchronous read mode, with data supplied on the positive edge of DCLK.

The serial clock (DCLK) generated by Cyclone IV E devices controls the entire configuration cycle and provides timing for the parallel interface.

### **Multi-Device AP Configuration**

You can configure multiple Cyclone IV E devices using a single parallel flash. You can cascade multiple Cyclone IV E devices using the chip-enable (nCE) and chip-enable-out (nCEO) pins. The first device in the chain must have its nCE pin connected to GND. You must connect its nCEO pin to the nCE pin of the next device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the nCEO signal high to its V<sub>CCIO</sub> level to help the internal weak pull-up resistor. When the first device captures all its configuration data from the bitstream, it drives the nCEO pin low, enabling the next device in the chain. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in the chain is a Cyclone IV E device. The nCONFIG, nSTATUS, CONF\_DONE, DCLK, DATA[15..8], and DATA[7..0] pins of each device in the chain are connected (Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27).

The first Cyclone IV E device in the chain, as shown in Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27, is the configuration master device and controls the configuration of the entire chain. You must connect its MSEL pins to select the AP configuration scheme. The remaining Cyclone IV E devices are used as configuration slaves. You must connect their MSEL pins to select the FPP configuration scheme. Any other Altera device that supports FPP configuration can also be part of the chain as a configuration slave.

The following are the configurations for the DATA[15..0] bus in a multi-device AP configuration:

- Byte-wide multi-device AP configuration

- Word-wide multi-device AP configuration

To ensure DCLK and DATA [0] are not left floating at the end of configuration, the MAX II device must drive them either high or low, whichever is convenient on your board. The DATA [0] pin is available as a user I/O pin after configuration. In the PS scheme, the DATA [0] pin is tri-stated by default in user mode and must be driven by the external host device. To change this default option in the Quartus II software, select the **Dual-Purpose Pins** tab of the **Device and Pin Options** dialog box.

The configuration clock (DCLK) speed must be below the specified system frequency to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

The external host device can also monitor CONF\_DONE and INIT\_DONE to ensure successful configuration. The CONF\_DONE pin must be monitored by the external device to detect errors and to determine when programming is complete. If all configuration data is sent, but CONF\_DONE or INIT\_DONE has not gone high, the external device must reconfigure the target device.

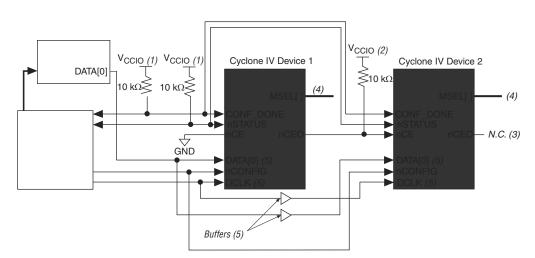

Figure 8–14 shows how to configure multiple devices using an external host device. This circuit is similar to the PS configuration circuit for a single device, except that Cyclone IV devices are cascaded for multi-device configuration.

#### Figure 8–14. Multi-Device PS Configuration Using an External Host

#### Notes to Figure 8-14:

- (1) The pull-up resistor must be connected to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  must be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

DCLK, DATA [7..0], and CONF\_DONE) are connected to every device in the chain. Configuration signals may require buffering to ensure signal integrity and prevent clock skew problems. Ensure that the DCLK and DATA lines are buffered. All devices initialize and enter user mode at the same time, because all device CONF\_DONE pins are tied together.

All nSTATUS and CONF\_DONE pins are tied together and if any device detects an error, configuration stops for the entire chain and the entire chain must be reconfigured. For example, if the first device flags an error on nSTATUS, it resets the chain by pulling its nSTATUS pin low. This behavior is similar to a single device detecting an error.

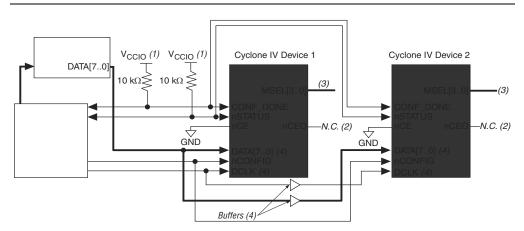

Figure 8–21 shows multi-device FPP configuration when both Cyclone IV devices are receiving the same configuration data. Configuration pins (nCONFIG, nSTATUS, DCLK, DATA[7..0], and CONF\_DONE) are connected to every device in the chain. Configuration signals may require buffering to ensure signal integrity and prevent clock skew problems. Ensure that the DCLK and DATA lines are buffered. Devices must be of the same density and package. All devices start and complete configuration at the same time.

## Figure 8–21. Multi-Device FPP Configuration Using an External Host When Both Devices Receive the Same Data

#### Notes to Figure 8-21:

- (1) You must connect the pull-up resistor to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  must be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

- (2) The nCEO pins of both devices are left unconnected or used as user I/O pins when configuring the same configuration data into multiple devices.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–4 on page 8–8 and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [7..0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

You can use a single configuration chain to configure Cyclone IV devices with other Altera devices that support FPP configuration. To ensure that all devices in the chain complete configuration at the same time or that an error flagged by one device starts reconfiguration in all devices, tie all the CONF DONE and nSTATUS pins together.

For more information about configuring multiple Altera devices in the same configuration chain, refer to *Configuring Mixed Altera FPGA Chains* in volume 2 of the *Configuration Handbook*.

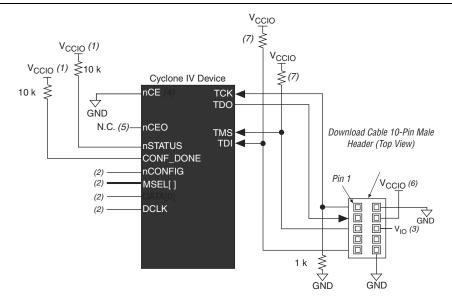

## Figure 8–24. JTAG Configuration of a Single Device Using a Download Cable (1.5-V or 1.8-V $V_{\text{CCIO}}$ Powering the JTAG Pins)

#### Notes to Figure 8-24:

- (1) Connect these pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the nCONFIG and MSEL pins to support a non-JTAG configuration scheme. If you only use JTAG configuration, connect the nCONFIG pin to logic-high and the MSEL pins to GND. In addition, pull DCLK and DATA[0] to either high or low, whichever is convenient on your board.

- (3) In the USB-Blaster and ByteBlaster II cables, this pin is connected to nCE when it is used for AS programming; otherwise it is a no connect.

- (4) The nCE must be connected to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (6) Power up the V<sub>CC</sub> of the EthernetBlaster, ByteBlaster II or USB-Blaster cable with supply from V<sub>CCI0</sub>. The Ethernet-Blaster, ByteBlaster II, and USB-Blaster cables do not support a target supply voltage of 1.2 V. For the target supply voltage value, refer to the *ByteBlaster II Download Cable User Guide*, the USB-Blaster Download Cable User Guide, and the EthernetBlaster Communications Cable User Guide.

- (7) Resistor value can vary from 1 k $\Omega$  to 10 k $\Omega$ .

To configure a single device in a JTAG chain, the programming software places all other devices in bypass mode. In bypass mode, devices pass programming data from the TDI pin to the TDO pin through a single bypass register without being affected internally. This scheme enables the programming software to program or verify the target device. Configuration data driven into the device appears on the TDO pin one clock cycle later.

The Quartus II software verifies successful JTAG configuration after completion. At the end of configuration, the software checks the state of CONF\_DONE through the JTAG port. When Quartus II generates a **.jam** for a multi-device chain, it contains instructions so that all the devices in the chain are initialized at the same time. If CONF\_DONE is not high, the Quartus II software indicates that configuration has failed. If CONF\_DONE is high, the software indicates that configuration was successful. After the configuration bitstream is serially sent using the JTAG TDI port, the TCK port clocks an additional clock cycles to perform device initialization.

Table 9–7 lists the input and output ports that you must include in the atom.

Table 9–7. CRC Block Input and Output Ports

| Port                                                             | Input/Output | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <crcblock_name></crcblock_name>                                  | Input        | Unique identifier for the CRC block, and represents any identifier name that is legal for the given description language (for example, Verilog HDL, VHDL, and AHDL). This field is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .clk(< <i>clock source</i> >                                     | Input        | This signal designates the clock input of this cell. All operations of this cell are with respect to the rising edge of the clock. Whether it is the loading of the data into the cell or data out of the cell, it always occurs on the rising edge. This port is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <pre>.shiftnld (<shiftnld source="">)</shiftnld></pre>           | Input        | This signal is an input into the error detection block. If shiftnld=1, the data is shifted from the internal shift register to the regout at each rising edge of clk. If shiftnld=0, the shift register parallel loads either the pre-calculated CRC value or the update register contents, depending on the ldsrc port input. To do this, the shiftnld must be driven low for at least two clock cycles. This port is required.                                                                                                                                                                                                                                                                                                                                                                                     |

| .ldsrc (< <i>ldsrc</i><br><i>source</i> >)                       | Input        | This signal is an input into the error detection block. If ldsrc=0, the pre-computed CRC register is selected for loading into the 32-bit shift register at the rising edge of clk when shiftnld=0. If ldsrc=1, the signature register (result of the CRC calculation) is selected for loading into the shift register at the rising edge of clk when shiftnld=0. This port is ignored when shiftnld=1. This port is required.                                                                                                                                                                                                                                                                                                                                                                                       |

| .crcerror ( <crcerror<br>indicator<br/>output&gt;)</crcerror<br> | Output       | This signal is the output of the cell that is synchronized to the internal oscillator of the device (80-MHz internal oscillator) and not to the clk port. It asserts high if the error block detects that a SRAM bit has flipped and the internal CRC computation has shown a difference with respect to the pre-computed value. You must connect this signal either to an output pin or a bidirectional pin. If it is connected to an output pin, you can only monitor the CRC_ERROR pin (the core cannot access this output). If the CRC_ERROR signal is used by core logic to read error detection logic, you must connect this signal to a BIDIR pin. The signal is fed to the core indirectly by feeding a BIDIR pin that has its output enable port connected to V <sub>CC</sub> (see Figure 9–3 on page 9–8). |

| .regout ( <registered<br>output&gt;)</registered<br>             | Output       | This signal is the output of the error detection shift register synchronized to the $clk$ port to be read by core logic. It shifts one bit at each cycle, so you should clock the $clk$ signal 31 cycles to read out the 32 bits of the shift register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## **Recovering from CRC Errors**

The system that the Altera FPGA resides in must control device reconfiguration. After detecting an error on the CRC\_ERROR pin, strobing the nCONFIG low directs the system to perform the reconfiguration at a time when it is safe for the system to reconfigure the FPGA.

When the data bit is rewritten with the correct value by reconfiguring the device, the device functions correctly.

While soft errors are uncommon in Altera devices, certain high-reliability applications might require a design to account for these errors.

| Document Revision History                                                    |                  |

|------------------------------------------------------------------------------|------------------|

| Chapter 3. Cyclone IV Dynamic Reconfiguration                                |                  |

| Glossary of Terms                                                            |                  |

| Dynamic Reconfiguration Controller Architecture                              |                  |

| Dynamic Reconfiguration Controller Port List                                 |                  |

| Offset Cancellation Feature                                                  |                  |

| Functional Simulation of the Offset Cancellation Process                     |                  |

| Dynamic Reconfiguration Modes                                                |                  |

| PMA Controls Reconfiguration Mode                                            |                  |

| Method 1: Using logical_channel_address to Reconfigure Specific Transceive   | er Channels 3–14 |

| Method 2: Writing the Same Control Signals to Control All the Transceiver C  | Channels 3–16    |

| Method 3: Writing Different Control Signals for all the Transceiver Channels | at the Same Time |

| 3–19                                                                         |                  |

| Transceiver Channel Reconfiguration Mode                                     |                  |

| Channel Interface Reconfiguration Mode                                       |                  |

| Data Rate Reconfiguration Mode Using RX Local Divider                        |                  |

| Control and Status Signals for Channel Reconfiguration                       |                  |

| PLL Reconfiguration Mode                                                     |                  |

| Error Indication During Dynamic Reconfiguration                              |                  |

| Functional Simulation of the Dynamic Reconfiguration Process                 |                  |

| Document Revision History                                                    |                  |

|                                                                              |                  |

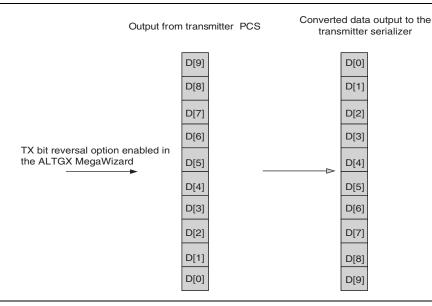

Bit reversal—reverses the transmit bit order from LSB-to-MSB (default) to MSB-to-LSB at the input to the serializer. For example, input data to serializer D[7..0] is rewired to D[0..7] for 8-bit data width, and D[9..0] is rewired to D[0..9] for 10-bit data width. Figure 1–10 shows the transmitter bit reversal feature.

Figure 1–10. Transmitter Bit Reversal Operation in Basic Single-Width Mode

- Input bit-flip—reverses the bit order at a byte level at the input of the transmitter phase compensation FIFO. For example, if the 16-bit parallel transmitter data at the tx\_datain port is '10111100 10101101' (16'hBCAD), selecting this option reverses the input data to the transmitter phase compensation FIFO to '00111101 10110101' (16'h3DB5).

- Bit-slip control—delays the data transmission by a number of specified bits to the serializer with the tx\_bitslipboundaryselect port. For usage details, refer to the "Transmit Bit-Slip Control" on page 1–76.

## Serializer

The serializer converts the low-speed parallel 8-bit or 10-bit data from the transmitter PCS to high-speed serial data for the transmitter output buffer. The serializer operates with a high-speed clock at half of the serial data rate. The serializer transmission sequence is LSB to MSB.

Table 1–4 lists the synchronization state machine parameters for the word aligner in this mode.

| Parameter                                                                       | Allowed Values |

|---------------------------------------------------------------------------------|----------------|

| Number of erroneous code groups received to lose synchronization                | 1–64           |

| Number of continuous good code groups received to reduce the error count by one | 1–256          |

Table 1–4.

Synchronization State Machine Parameters

After deassertion of the rx\_digitalreset signal in automatic synchronization state machine mode, the word aligner starts looking for the synchronization code groups, word alignment pattern or its complement in the received data stream. When the programmed number of valid synchronization code groups or ordered sets are received, the rx\_syncstatus signal is driven high to indicate that synchronization is acquired. The rx\_syncstatus signal is constantly driven high until the programmed number of erroneous code groups are received without receiving intermediate good groups; after which the rx\_syncstatus signal is driven low. The word aligner indicates loss of synchronization (rx\_syncstatus signal remains low) until the programmed number of valid synchronization code groups are received again.

In addition to restoring word boundaries, the word aligner supports the following features:

Programmable run length violation detection—detects consecutive 1s or 0s in the data stream, and asserts run length violation signal (rx\_rlv) when a preset run length threshold (maximum number of consecutive 1s or 0s) is detected. The rx\_rlv signal in each channel is clocked by its parallel recovered clock and is asserted for a minimum of two recovered clock cycles to ensure that the FPGA fabric clock can latch the rx\_rlv signal reliably because the FPGA fabric clock might have phase differences, ppm differences (in asynchronous systems), or both, with the recovered clock. Table 1–5 lists the run length violation circuit detection capabilities.

| Supported Data Width  | Detecto | Increment Step |          |

|-----------------------|---------|----------------|----------|

| Supporteu Data Wiutii | Minimum | Maximum        | Settings |

| 8-bit                 | 4       | 128            | 4        |

| 10-bit                | 5       | 160            | 5        |

Table 1–5. Run Length Violation Circuit Detection Capabilities

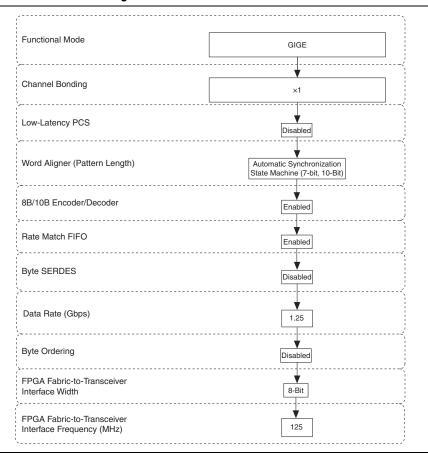

Figure 1–56 shows the transceiver configuration in GIGE mode.

Figure 1–56. Transceiver Configuration in GIGE Mode

When configured in GIGE mode, three encoded comma (/K28.5/) code groups are transmitted automatically after deassertion of tx\_digitalreset and before transmitting user data on the tx\_datain port. This could affect the synchronization state machine behavior at the receiver.

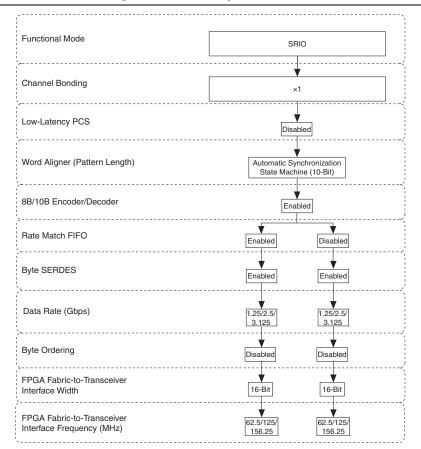

Depending on when you start transmitting the synchronization sequence, there could be an even or odd number of encoded data (/Dx.y/) code groups transmitted between the last of the three automatically sent /K28.5/ code groups and the first /K28.5/ code group of the synchronization sequence. If there is an even number of /Dx.y/ code groups received between these two /K28.5/ code groups, the first /K28.5/ code group of the synchronization sequence begins at an odd code group boundary. An IEEE802.3-compliant GIGE synchronization state machine treats this as an error condition and goes into the Loss-of-Sync state. Figure 1–61 shows the transceiver configuration in Serial RapidIO mode.

Figure 1–61. Transceiver Configuration in Serial RapidIO Mode

## **Lane Synchronization**

In Serial RapidIO mode, the word aligner is compliant to the SRIO Specification 1.3 and is configured in automatic synchronization state machine mode with the parameter settings as listed in Table 1–20.

Table 1–20. Synchronization State Machine Parameters <sup>(1)</sup>

| Parameter                                                                                 | Value |

|-------------------------------------------------------------------------------------------|-------|

| Number of valid synchronization (/K28.5/) code groups received to achieve synchronization | 127   |

| Number of erroneous code groups received to lose synchronization                          | 3     |

| Number of continuous good code groups received to reduce the error count by one           | 255   |

#### Note to Table 1-20:

(1) The word aligner supports 10-bit pattern lengths in SRIO mode.

## 3. Cyclone IV Dynamic Reconfiguration

Cyclone<sup>®</sup> IV GX transceivers allow you to dynamically reconfigure different portions of the transceivers without powering down any part of the device. This chapter describes and provides examples about the different modes available for dynamic reconfiguration.

You can use the ALTGX\_RECONFIG and ALTPLL\_RECONFIG controller instance to reconfigure the physical medium attachment (PMA) controls, physical coding sublayer (PCS), multipurpose phase locked loops (PLLs), and general purpose PLLs.

This chapter contains the following sections:

- "Glossary of Terms" on page 3–1

- "Dynamic Reconfiguration Controller Architecture" on page 3–2

- "Dynamic Reconfiguration Modes" on page 3–12

- "Error Indication During Dynamic Reconfiguration" on page 3–36

- "Functional Simulation of the Dynamic Reconfiguration Process" on page 3–37

## **Glossary of Terms**

Table 3–1 lists the terms used in this chapter:

| Table 3-1. | <b>Glossary</b> of | <b>Terms Used in</b> | this Chapter | (Part 1 of 2) |

|------------|--------------------|----------------------|--------------|---------------|

|------------|--------------------|----------------------|--------------|---------------|

| Term                       | Description                                                                                                                                                                                    |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ALTGX_RECONFIG Instance    | Dynamic reconfiguration controller instance generated by the ALTGX_RECONFIG MegaWizard <sup>™</sup> Plug-In Manager.                                                                           |  |  |

| ALTGX Instance             | Transceiver instance generated by the ALTGX MegaWizard Plug-In Manager.                                                                                                                        |  |  |

| ALTPLL_RECONFIG Instance   | Dynamic PLL reconfiguration controller instance generated by the ALTPLL_RECONFIG Megawizard Plug-In Manager                                                                                    |  |  |

| Logical Channel Addressing | Used whenever the concept of logical channel addressing is explained. This term does not refer to the logical_channel_address port available in the ALTGX_RECONFIG MegaWizard Plug-In Manager. |  |  |

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| FPGA Fabric-Transceiver Channel<br>Interface Description | Receive Signal Description (Based on Cyclone IV GX Supported FPGA<br>Fabric-Transceiver Channel Interface Widths)                                                       |  |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                          | Two 8-bit unencoded Data (rx_dataout)                                                                                                                                   |  |  |  |

|                                                          | rx_dataoutfull[7:0] - rx_dataout (LSByte) and                                                                                                                           |  |  |  |

|                                                          | rx_dataoutfull[23:16]-rx_dataout (MSByte)                                                                                                                               |  |  |  |

|                                                          | The following signals are used in 16-bit 8B/10B modes:                                                                                                                  |  |  |  |

|                                                          | Two Control Bits                                                                                                                                                        |  |  |  |

|                                                          | rx_dataoutfull[8] - rx_ctrldetect (LSB) and                                                                                                                             |  |  |  |

|                                                          | <pre>rx_dataoutfull[24]-rx_ctrldetect (MSB)</pre>                                                                                                                       |  |  |  |

|                                                          | Two Receiver Error Detect Bits                                                                                                                                          |  |  |  |

|                                                          | <pre>rx_dataoutfull[9] - rx_errdetect (LSB) and</pre>                                                                                                                   |  |  |  |

|                                                          | <pre>rx_dataoutfull[25]-rx_errdetect (MSB)</pre>                                                                                                                        |  |  |  |

|                                                          | Two Receiver Sync Status Bits                                                                                                                                           |  |  |  |

|                                                          | <pre>rx_dataoutfull [10] - rx_syncstatus (LSB) and</pre>                                                                                                                |  |  |  |

| 16-bit FPGA fabric-Transceiver                           | <pre>rx_dataoutfull[26] - rx_syncstatus (MSB)</pre>                                                                                                                     |  |  |  |

| Channel Interface with PCS-PMA set to 8/10 bits          | Two Receiver Disparity Error Bits                                                                                                                                       |  |  |  |

|                                                          | <pre>rx_dataoutfull [11] - rx_disperr (LSB) and</pre>                                                                                                                   |  |  |  |

|                                                          | <pre>rx_dataoutfull[27] - rx_disperr (MSB)</pre>                                                                                                                        |  |  |  |

|                                                          | Two Receiver Pattern Detect Bits                                                                                                                                        |  |  |  |

|                                                          | <pre>rx_dataoutfull[12] - rx_patterndetect (LSB) and</pre>                                                                                                              |  |  |  |

|                                                          | <pre>rx_dataoutfull[28] - rx_patterndetect (MSB)</pre>                                                                                                                  |  |  |  |

|                                                          | <pre>rx_dataoutfull[13] and rx_dataoutfull[29]: Rate Match FIFO deletion status<br/>indicator (rx_rmfifodatadeleted) in non-PCI Express (PIPE) functional modes</pre>   |  |  |  |

|                                                          | <pre>rx_dataoutfull[14] and rx_dataoutfull[30]: Rate Match FIFO insertion status<br/>indicator (rx_rmfifodatainserted) in non-PCI Express (PIPE) functional modes</pre> |  |  |  |

|                                                          | Two 2-bit PCI Express (PIPE) Functional Mode Status Bits                                                                                                                |  |  |  |

|                                                          | <pre>rx_dataoutfull[14:13] - rx_pipestatus (LSB) and rx_dataoutfull[30:29] -<br/>rx_pipestatus (MSB)</pre>                                                              |  |  |  |

|                                                          | <pre>rx_dataoutfull[15] and rx_dataoutfull[31]: 8B/10B running disparity indicator (rx_runningdisp)</pre>                                                               |  |  |  |

### Table 3–5. rx\_dataoutfull[31..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions (Part 2 of 3)