# E·XFL

#### Intel - EP4CE22E22C9L Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 1395                                                     |

| Number of Logic Elements/Cells | 22320                                                    |

| Total RAM Bits                 | 608256                                                   |

| Number of I/O                  | 79                                                       |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 144-LQFP Exposed Pad                                     |

| Supplier Device Package        | 144-EQFP (20x20)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce22e22c9l |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

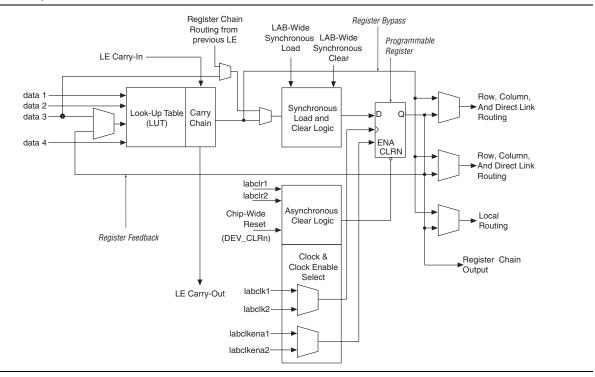

Figure 2–1 shows the LEs for Cyclone IV devices.

Figure 2–1. Cyclone IV Device LEs

### **LE Features**

You can configure the programmable register of each LE for D, T, JK, or SR flipflop operation. Each register has data, clock, clock enable, and clear inputs. Signals that use the global clock network, general-purpose I/O pins, or any internal logic can drive the clock and clear control signals of the register. Either general-purpose I/O pins or the internal logic can drive the clock enable. For combinational functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output independently drives these three outputs. Two LE outputs drive the column or row and direct link routing connections, while one LE drives the local interconnect resources. This allows the LUT to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the LUT for unrelated functions. The LAB-wide synchronous load control signal is not available when using register packing. For more information about the synchronous load control signal, refer to "LAB Control Signals" on page 2–6.

The register feedback mode allows the register output to feed back into the LUT of the same LE to ensure that the register is packed with its own fan-out LUT, providing another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

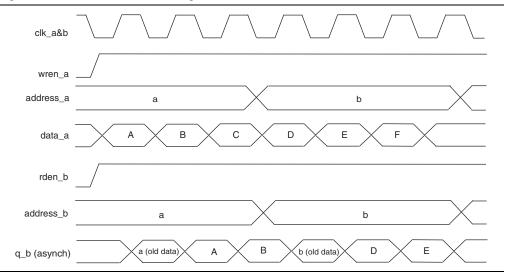

In this mode, you also have two output choices: **Old Data** mode or **Don't Care** mode. In **Old Data** mode, a read-during-write operation to different ports causes the RAM outputs to reflect the old data at that address location. In **Don't Care** mode, the same operation results in a "Don't Care" or unknown value on the RAM outputs.

**To** For more information about how to implement the desired behavior, refer to the *RAM Megafunction User Guide*.

Figure 3–16 shows a sample functional waveform of mixed port read-during-write behavior for **Old Data** mode. In **Don't Care** mode, the old data is replaced with "Don't Care".

For mixed-port read-during-write operation with dual clocks, the relationship between the clocks determines the output behavior of the memory. If you use the same clock for the two clocks, the output is the old data from the address location. However, if you use different clocks, the output is unknown during the mixed-port read-during-write operation. This unknown value may be the old or new data at the address location, depending on whether the read happens before or after the write.

### **Conflict Resolution**

When you are using M9K memory blocks in true dual-port mode, it is possible to attempt two write operations to the same memory location (address). Because there is no conflict resolution circuitry built into M9K memory blocks, this results in unknown data being written to that location. Therefore, you must implement conflict-resolution logic external to the M9K memory block.

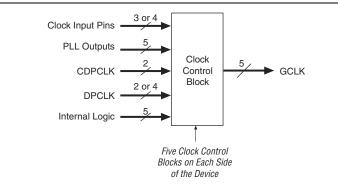

Figure 5–6 shows a simplified version of the five clock control blocks on each side of the Cyclone IV E device periphery.

#### Note to Figure 5–6:

(1) The left and right sides of the device have two DPCLK pins; the top and bottom of the device have four DPCLK pins.

### **GCLK Network Power Down**

You can disable a Cyclone IV device's GCLK (power down) using both static and dynamic approaches. In the static approach, configuration bits are set in the configuration file generated by the Quartus II software, which automatically disables unused GCLKs. The dynamic clock enable or disable feature allows internal logic to control clock enable or disable the GCLKs in Cyclone IV devices.

When a clock network is disabled, all the logic fed by the clock network is in an off-state, thereby reducing the overall power consumption of the device. This function is independent of the PLL and is applied directly on the clock network, as shown in Figure 5–1 on page 5–11.

You can set the input clock sources and the clkena signals for the GCLK multiplexers through the Quartus II software using the ALTCLKCTRL megafunction.

**For more information, refer to the** *ALTCLKCTRL Megafunction User Guide.*

### clkena Signals

Cyclone IV devices support clkena signals at the GCLK network level. This allows you to gate-off the clock even when a PLL is used. Upon re-enabling the output clock, the PLL does not need a resynchronization or re-lock period because the circuit gates off the clock at the clock network level. In addition, the PLL can remain locked independent of the clkena signals because the loop-related counters are not affected.

# **Clock Feedback Modes**

Cyclone IV PLLs support up to five different clock feedback modes. Each mode allows clock multiplication and division, phase shifting, and programmable duty cycle. For the supported feedback modes, refer to Table 5–5 on page 5–18 for Cyclone IV GX PLLs and Table 5–6 on page 5–19 for Cyclone IV E PLLs.

Input and output delays are fully compensated by the PLL only if you are using the dedicated clock input pins associated with a given PLL as the clock sources.

When driving the PLL using the GCLK network, the input and output delays may not be fully compensated in the Quartus II software.

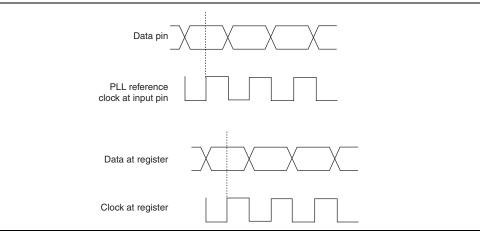

### Source-Synchronous Mode

If the data and clock arrive at the same time at the input pins, the phase relationship between the data and clock remains the same at the data and clock ports of any I/O element input register.

Figure 5–12 shows an example waveform of the data and clock in this mode. Use this mode for source-synchronous data transfers. Data and clock signals at the I/O element experience similar buffer delays as long as the same I/O standard is used.

Source-synchronous mode compensates for delay of the clock network used, including any difference in the delay between the following two paths:

- Data pin to I/O element register input

- Clock input pin to the PLL phase frequency detector (PFD) input

Set the input pin to the register delay chain in the I/O element to zero in the Quartus II software for all data pins clocked by a source-synchronous mode PLL. Also, all data pins must use the **PLL COMPENSATED logic** option in the Quartus II software.

### **Deterministic Latency Compensation Mode**

The deterministic latency mode compensates for the delay of the multipurpose PLLs through the clock network and serializer in Common Public Radio Interface (CPRI) applications. In this mode, the PLL PFD feedback path compensates the latency uncertainty in Tx dataout and Tx clkout paths relative to the reference clock.

### **Hardware Features**

Cyclone IV PLLs support several features for general-purpose clock management. This section discusses clock multiplication and division implementation, phase shifting implementations, and programmable duty cycles.

### **Clock Multiplication and Division**

Each Cyclone IV PLL provides clock synthesis for PLL output ports using  $M/(N^*post-scale \text{ counter})$  scaling factors. The input clock is divided by a pre-scale factor, N, and is then multiplied by the M feedback factor. The control loop drives the VCO to match  $f_{IN}$  (M/N). Each output port has a unique post-scale counter that divides down the high-frequency VCO. For multiple PLL outputs with different frequencies, the VCO value is the least common multiple of the output frequencies that meets its frequency specifications. For example, if output frequencies required from one PLL are 33 and 66 MHz, the Quartus II software sets the VCO to 660 MHz (the least common multiple of 33 and 66 MHz in the VCO range). Then, the post-scale counters scale down the VCO frequency for each output port.

There is one pre-scale counter, N, and one multiply counter, M, per PLL, with a range of 1 to 512 for both M and N. The N counter does not use duty cycle control because the purpose of this counter is only to calculate frequency division. There are five generic post-scale counters per PLL that can feed GCLKs or external clock outputs. These post-scale counters range from 1 to 512 with a 50% duty cycle setting. The post-scale counters range from 1 to 256 with any non-50% duty cycle setting. The sum of the high/low count values chosen for a design selects the divide value for a given counter.

The Quartus II software automatically chooses the appropriate scaling factors according to the input frequency, multiplication, and division values entered into the ALTPLL megafunction.

Phase alignment between output counters is determined using the t<sub>PLL\_PSERR</sub> specification.

- "Pad Placement and DC Guidelines" on page 6–23

- "Clock Pins Functionality" on page 6–23

- "High-Speed I/O Interface" on page 6–24

- "High-Speed I/O Standards Support" on page 6–28

- "True Differential Output Buffer Feature" on page 6–35

- "High-Speed I/O Timing" on page 6–36

- "Design Guidelines" on page 6–37

- "Software Overview" on page 6–38

### **Cyclone IV I/O Elements**

Cyclone IV I/O elements (IOEs) contain a bidirectional I/O buffer and five registers for registering input, output, output-enable signals, and complete embedded bidirectional single-data rate transfer. I/O pins support various single-ended and differential I/O standards.

The IOE contains one input register, two output registers, and two output-enable (OE) registers. The two output registers and two OE registers are used for DDR applications. You can use input registers for fast setup times and output registers for fast clock-to-output times. Additionally, you can use OE registers for fast clock-to-output enable timing. You can use IOEs for input, output, or bidirectional data paths.

# 7. External Memory Interfaces in Cyclone IV Devices

This chapter describes the memory interface pin support and the external memory interface features of Cyclone<sup>®</sup> IV devices.

In addition to an abundant supply of on-chip memory, Cyclone IV devices can easily interface with a broad range of external memory devices, including DDR2 SDRAM, DDR SDRAM, and QDR II SRAM. External memory devices are an important system component of a wide range of image processing, storage, communications, and general embedded applications.

Altera recommends that you construct all DDR2 or DDR SDRAM external memory interfaces using the Altera<sup>®</sup> ALTMEMPHY megafunction. You can implement the controller function using the Altera DDR2 or DDR SDRAM memory controllers, third-party controllers, or a custom controller for unique application needs. Cyclone IV devices support QDR II interfaces electrically, but Altera does not supply controller or physical layer (PHY) megafunctions for QDR II interfaces.

This chapter includes the following sections:

- "Cyclone IV Devices Memory Interfaces Pin Support" on page 7–2

- "Cyclone IV Devices Memory Interfaces Features" on page 7–12

- For more information about supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to the *External Memory Interface Handbook*.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

In Cyclone IV devices, DQS is used only during write mode in DDR2 and DDR SDRAM interfaces. Cyclone IV devices ignore DQS as the read-data strobe because the PHY internally generates the read capture clock for read mode. However, you must connect the DQS pin to the DQS signal in DDR2 and DDR SDRAM interfaces, or to the CQ signal in QDR II SRAM interfaces.

- Cyclone IV devices do not support differential strobe pins, which is an optional feature in the DDR2 SDRAM device.

- When you use the Altera Memory Controller MegaCore<sup>®</sup> function, the PHY is instantiated for you. For more information about the memory interface data path, refer to the *External Memory Interface Handbook*.

- ALTMEMPHY is a self-calibrating megafunction, enhanced to simplify the implementation of the read-data path in different memory interfaces. The auto-calibration feature of ALTMEMPHY provides ease-of-use by optimizing clock phases and frequencies across process, voltage, and temperature (PVT) variations. You can save on the global clock resources in Cyclone IV devices through the ALTMEMPHY megafunction because you are not required to route the DQS signals on the global clock buses (because DQS is ignored for read capture). Resynchronization issues do not arise because no transfer occurs from the memory domain clock (DQS) to the system domain for capturing data DQ.

All I/O banks in Cyclone IV devices can support DQ and DQS signals with DQ-bus modes of ×8, ×9, ×16, ×18, ×32, and ×36 except Cyclone IV GX devices that do not support left I/O bank interface. DDR2 and DDR SDRAM interfaces use ×8 mode DQS group regardless of the interface width. For a wider interface, you can use multiple ×8 DQ groups to achieve the desired width requirement.

In the ×9, ×18, and ×36 modes, a pair of complementary DQS pins (CQ and CQ#) drives up to 9, 18, or 36 DQ pins, respectively, in the group, to support one, two, or four parity bits and the corresponding data bits. The ×9, ×18, and ×36 modes support the QDR II memory interface. CQ# is the inverted read-clock signal that is connected to the complementary data strobe (DQS or CQ#) pin. You can use any unused DQ pins as regular user I/O pins if they are not used as memory interface signals.

For more information about unsupported DQS and DQ groups of the Cyclone IV transceivers that run at ≥2.97 Gbps data rate, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

In Cyclone IV devices, the DM pins are preassigned in the device pinouts. The Quartus II Fitter treats the DQ and DM pins in a DQS group equally for placement purposes. The preassigned DQ and DM pins are the preferred pins to use.

Some DDR2 SDRAM and DDR SDRAM devices support error correction coding (ECC), a method of detecting and automatically correcting errors in data transmission. In 72-bit DDR2 or DDR SDRAM, there are eight ECC pins and 64 data pins. Connect the DDR2 and DDR SDRAM ECC pins to a separate DQS or DQ group in Cyclone IV devices. The memory controller needs additional logic to encode and decode the ECC data.

### **Address and Control/Command Pins**

The address signals and the control or command signals are typically sent at a single data rate. You can use any of the user I/O pins on all I/O banks of Cyclone IV devices to generate the address and control or command signals to the memory device.

Cyclone IV devices do not support QDR II SRAM in the burst length of two.

### **Memory Clock Pins**

In DDR2 and DDR SDRAM memory interfaces, the memory clock signals (CK and CK#) are used to capture the address signals and the control or command signals. Similarly, QDR II SRAM devices use the write clocks (K and K#) to capture the address and command signals. The CK/CK# and K/K# signals are generated to resemble the write-data strobe using the DDIO registers in Cyclone IV devices.

CK/CK# pins must be placed on differential I/O pins (DIFFIO in Pin Planner) and in the same bank or on the same side as the data pins. You can use either side of the device for wraparound interfaces. As seen in the Pin Planner Pad View, CK0 cannot be located in the same row and column pad group as any of the interfacing DQ pins.

### **Cyclone IV Devices Memory Interfaces Features**

This section discusses Cyclone IV memory interfaces, including DDR input registers, DDR output registers, OCT, and phase-lock loops (PLLs).

### **DDR Input Registers**

The DDR input registers are implemented with three internal logic element (LE) registers for every DQ pin. These LE registers are located in the logic array block (LAB) adjacent to the DDR input pin.

For more information about Cyclone IV PLL, refer to the Clock Networks and PLLs in Cyclone IV Devices chapter.

# **Document Revision History**

Table 7–3 lists the revision history for this chapter.

| Date            | Version | Changes                                                                                                             |  |  |

|-----------------|---------|---------------------------------------------------------------------------------------------------------------------|--|--|

|                 |         | ■ Updated Table 7–1 to remove support for the N148 package.                                                         |  |  |

| March 2016      | 2.6     | ■ Updated note (1) in Figure 7–2 to remove support for the N148 package.                                            |  |  |

|                 |         | <ul> <li>Updated Figure 7–4 to remove support for the N148 package.</li> </ul>                                      |  |  |

| May 2013        | 2.5     | Updated Table 7–2 to add new device options and packages.                                                           |  |  |

| February 2013   | 2.4     | Updated Table 7–2 to add new device options and packages.                                                           |  |  |

| October 2012    | 2.3     | Updated Table 7–1 and Table 7–2.                                                                                    |  |  |

| December 2010 2 |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                       |  |  |

|                 | 2.2     | <ul> <li>Added Cyclone IV E new device package information.</li> </ul>                                              |  |  |

|                 |         | ■ Updated Table 7–2.                                                                                                |  |  |

|                 |         | <ul> <li>Minor text edits.</li> </ul>                                                                               |  |  |

| November 2010   | 2.1     | Updated "Data and Data Clock/Strobe Pins" section.                                                                  |  |  |

|                 |         | <ul> <li>Added Cyclone IV E devices information for the Quartus II software version 9.1 SP1<br/>release.</li> </ul> |  |  |

| February 2010   | 2.0     | ■ Updated Table 7–1.                                                                                                |  |  |

| -               |         | ■ Added Table 7–2.                                                                                                  |  |  |

|                 |         | ■ Added Figure 7–5 and Figure 7–6.                                                                                  |  |  |

Та

November 2009

1.0

Initial release.

| Device        |           | Data Size (bits)          |  |

|---------------|-----------|---------------------------|--|

|               | EP4CGX15  | 3,805,568                 |  |

|               | EP4CGX22  | 7,600,040                 |  |

|               | EP4CGX30  | 7,600,040                 |  |

| Cyclone IV GX |           | 22,010,888 <sup>(1)</sup> |  |

|               | EP4CGX50  | 22,010,888                |  |

|               | EP4CGX75  | 22,010,888                |  |

|               | EP4CGX110 | 39,425,016                |  |

|               | EP4CGX150 | 39,425,016                |  |

#### Table 8-2. Uncompressed Raw Binary File (.rbf) Sizes for Cyclone IV Devices (Part 2 of 2)

Note to Table 8-2:

(1) Only for the F484 package.

Use the data in Table 8–2 to estimate the file size before design compilation. Different configuration file formats, such as Hexadecimal (.hex) or Tabular Text File (.ttf) formats, have different file sizes. However, for any specific version of the Quartus II software, any design targeted for the same device has the same uncompressed configuration file size. If you use compression, the file size varies after each compilation, because the compression ratio depends on the design.

• For more information about setting device configuration options or creating configuration files, refer to the *Software Settings* section in volume 2 of the *Configuration Handbook*.

#### **Configuration and JTAG Pin I/O Requirements**

Cyclone IV devices are manufactured using the TSMC 60-nm low-k dielectric process. Although Cyclone IV devices use TSMC 2.5-V transistor technology in the I/O buffers, the devices are compatible and able to interface with 2.5, 3.0, and 3.3-V configuration voltage standards by following specific requirements.

All I/O inputs must maintain a maximum AC voltage of 4.1 V. When using a serial configuration device in an AS configuration scheme, you must connect a 25- $\Omega$  series resistor for the DATA[0] pin. When cascading the Cyclone IV device family in a multi-device configuration for AS, AP, FPP, and PS configuration schemes, you must connect the repeater buffers between the master and slave devices for the DATA and DCLK pins. When using the JTAG configuration scheme in a multi-device configuration, connect 25- $\Omega$  resistors on both ends of the TDO-TDI path if the TDO output driver is a non-Cyclone IV device.

The output resistance of the repeater buffers and the TDO path for all cases must fit the maximum overshoot equation shown in Equation 8–1.

Equation 8–1. <sup>(1)</sup>

$0.8Z_O \le R_E \le 1.8Z_O$

#### Note to Equation 8–1:

(1)  $Z_0$  is the transmission line impedance and  $R_E$  is the equivalent resistance of the output buffer.

For more information about the operation of the Micron P30 Parallel NOR and P33 Parallel NOR flash memories, search for the keyword "P30" or "P33" on the Micron website (www.micron.com) to obtain the P30 or P33 family datasheet.

#### **Single-Device AP Configuration**

The following groups of interface pins are supported in Micron P30 and P33 flash memories:

- Control pins

- Address pins

- Data pins

The following control signals are from the supported parallel flash memories:

- CLK

- active-low reset (RST#)

- active-low chip enable (CE#)

- active-low output enable (OE#)

- active-low address valid (ADV#)

- active-low write enable (WE#)

The supported parallel flash memories output a control signal (WAIT) to Cyclone IV E devices to indicate when synchronous data is ready on the data bus. Cyclone IV E devices have a 24-bit address bus connecting to the address bus (A[24:1]) of the flash memory. A 16-bit bidirectional data bus (DATA[15..0]) provides data transfer between the Cyclone IV E device and the flash memory.

The following control signals are from the Cyclone IV E device to flash memory:

- DCLK

- active-low hard rest (nRESET)

- active-low chip enable (FLASH\_nCE)

- active-low output enable for the DATA [15..0] bus and WAIT pin (nOE)

- active-low address valid signal and is used to write data into the flash (nAVD)

- active-low write enable and is used to write data into the flash (nWE)

#### **Programming Parallel Flash Memories**

Supported parallel flash memories are external non-volatile configuration devices. They are industry standard microprocessor flash memories. For more information about the supported families for the commodity parallel flash, refer to Table 8–10 on page 8–22.

Cyclone IV E devices in a single- or multiple-device chain support in-system programming of a parallel flash using the JTAG interface with the flash loader megafunction. The board intelligent host or download cable uses the four JTAG pins on Cyclone IV E devices to program the parallel flash in system, even if the host or download cable cannot access the configuration pins of the parallel flash.

**•** For more information about using the JTAG pins on Cyclone IV E devices to program the parallel flash in-system, refer to *AN* 478: Using FPGA-Based Parallel Flash Loader (*PFL*) with the Quartus II Software.

In the AP configuration scheme, the default configuration boot address is  $0 \times 010000$  when represented in 16-bit word addressing in the supported parallel flash memory (Figure 8–12). In the Quartus II software, the default configuration boot address is  $0 \times 020000$  because it is represented in 8-bit byte addressing. Cyclone IV E devices configure from word address  $0 \times 010000$ , which is equivalent to byte address  $0 \times 020000$ .

The Quartus II software uses byte addressing for the default configuration boot address. You must set the start address field to **0×020000**.

- External configuration reset (nCONFIG) assertion

- User watchdog timer time out

Table 8–24 lists the contents of the current state logic in the status register, when the remote system upgrade master state machine is in factory configuration or application configuration accessing the factory information or application information, respectively. The status register bit in Table 8–24 lists the bit positions in a 32-bit logic.

| Remote System Upgrade<br>Master State Machine | Status<br>Register Bit | Definition                            | Description                                                                                                                       |

|-----------------------------------------------|------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                               | 31:30                  | Master state machine<br>current state | The current state of the remote system upgrade master state machine                                                               |

| Factory information <sup>(1)</sup>            | 29:24                  | Reserved bits                         | Padding bits that are set to all 0's                                                                                              |

|                                               | 23:0                   | Boot address                          | The current 24-bit boot address that was used by the configuration scheme as the start address to load the current configuration. |

|                                               | 31:30                  | Master state machine<br>current state | The current state of the remote system upgrade master state machine                                                               |

| Application information 1 <sup>(2)</sup>      | 29                     | User watchdog timer<br>enable bit     | The current state of the user watchdog enable, which is active high                                                               |

|                                               | 28:0                   | User watchdog timer<br>time-out value | The current entire 29-bit watchdog time-out value.                                                                                |

|                                               | 31:30                  | Master state machine current state    | The current state of the remote system upgrade master state machine                                                               |

| Application information 2 (2)                 | 29:24                  | Reserved bits                         | Padding bits that are set to all 0's                                                                                              |

|                                               | 23:0                   | Boot address                          | The current 24-bit boot address that was used as the start address to load the current configuration                              |

#### Notes to Table 8-24:

(1) The remote system upgrade master state machine is in factory configuration.

(2) The remote system upgrade master state machine is in application configuration.

The previous two application configurations are available in the previous state registers (previous state register 1 and previous state register 2), but only for debugging purposes.

| Device    | Boundary-Scan Register Length |

|-----------|-------------------------------|

| EP4CGX75  | 1006                          |

| EP4CGX110 | 1495                          |

| EP4CGX150 | 1495                          |

| Table 10–1.         Boundary-Scan Register Length for Cyclone IV Devices (Part 2 of 2) |

|----------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------|

Note to Table 10-1:

(1) For the F484 package of the EP4CGX30 device, the boundary-scan register length is 1006.

Table 10–2 lists the IDCODE information for Cyclone IV devices.

| Table 10-2. | IDCODE Information for 32-Bit Cyclone IV Devices |

|-------------|--------------------------------------------------|

|-------------|--------------------------------------------------|

|              | IDCODE (32 Bits) <sup>(1)</sup>           |                     |                                    |                               |  |

|--------------|-------------------------------------------|---------------------|------------------------------------|-------------------------------|--|

| Device       | Version Part Number<br>(4 Bits) (16 Bits) |                     | Manufacturer Identity<br>(11 Bits) | LSB<br>(1 Bit) <sup>(2)</sup> |  |

| EP4CE6       | 0000                                      | 0010 0000 1111 0001 | 000 0110 1110                      | 1                             |  |

| EP4CE10      | 0000                                      | 0010 0000 1111 0001 | 000 0110 1110                      | 1                             |  |

| EP4CE15      | 0000                                      | 0010 0000 1111 0010 | 000 0110 1110                      | 1                             |  |

| EP4CE22      | 0000                                      | 0010 0000 1111 0011 | 000 0110 1110                      | 1                             |  |

| EP4CE30      | 0000                                      | 0010 0000 1111 0100 | 000 0110 1110                      | 1                             |  |

| EP4CE40      | 0000                                      | 0010 0000 1111 0100 | 000 0110 1110                      | 1                             |  |

| EP4CE55      | 0000                                      | 0010 0000 1111 0101 | 000 0110 1110                      | 1                             |  |

| EP4CE75      | 0000                                      | 0010 0000 1111 0110 | 000 0110 1110                      | 1                             |  |

| EP4CE115     | 0000                                      | 0010 0000 1111 0111 | 000 0110 1110                      | 1                             |  |

| EP4CGX15     | 0000                                      | 0010 1000 0000 0001 | 000 0110 1110                      | 1                             |  |

| EP4CGX22     | 0000                                      | 0010 1000 0001 0010 | 000 0110 1110                      | 1                             |  |

| EP4CGX30 (3) | 0000                                      | 0010 1000 0000 0010 | 000 0110 1110                      | 1                             |  |

| EP4CGX30 (4) | 0000                                      | 0010 1000 0010 0011 | 000 0110 1110                      | 1                             |  |

| EP4CGX50     | 0000                                      | 0010 1000 0001 0011 | 000 0110 1110                      | 1                             |  |

| EP4CGX75     | 0000                                      | 0010 1000 0000 0011 | 000 0110 1110                      | 1                             |  |

| EP4CGX110    | 0000                                      | 0010 1000 0001 0100 | 000 0110 1110                      | 1                             |  |

| EP4CGX150    | 0000                                      | 0010 1000 0000 0100 | 000 0110 1110                      | 1                             |  |

#### Notes to Table 10-2:

(1) The MSB is on the left.

(2) The IDCODE LSB is always 1.

(3) The IDCODE is applicable for all packages except for the F484 package.

(4) The IDCODE is applicable for the F484 package only.

IEEE Std.1149.6 mandates the addition of two new instructions: EXTEST\_PULSE and EXTEST\_TRAIN. These two instructions enable edge-detecting behavior on the signal path containing the AC pins.

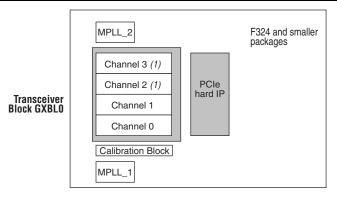

The Cyclone IV GX device includes a hard intellectual property (IP) implementation of the PCIe MegaCore<sup>®</sup> functions, supporting Gen1 ×1, ×2, and ×4 initial lane widths configured in the root port or endpoint mode. For more information, refer to "PCI-Express Hard IP Block" on page 1–46.

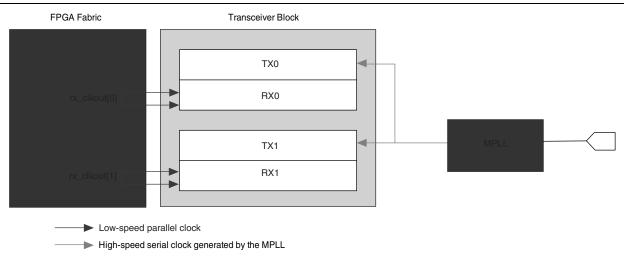

# **Transceiver Architecture**

Cyclone IV GX devices offer either one or two transceiver blocks per device, depending on the package. Each block consists of four full-duplex (transmitter and receiver) channels, located on the left side of the device (in a die-top view). Figure 1–1 and Figure 1–2 show the die-top view of the transceiver block and related resource locations in Cyclone IV GX devices.

#### Note to Figure 1–1:

(1) Channel 2 and Channel 3 are not available in the F169 and smaller packages.

Table 1–9 lists the high- and low-speed clock sources for each channel.

| able 1–9. High- and Low-Speed Clock Sources for Each Channel in Non-Bonded Channel Configuration |

|--------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------|

| Dookono          | Troposius Plack   | Transceiver Channel | High- and Low-Speed Clocks Sources |                              |

|------------------|-------------------|---------------------|------------------------------------|------------------------------|

| Package          | Transceiver Block |                     | Option 1                           | Option 2                     |

| F324 and smaller | GXBL0             | All channels        | MPLL_1                             | MPLL_2                       |

| F484 and larger  | GXBL0             | Channels 0, 1       | MPLL_5/GPLL_1                      | MPLL_6                       |

|                  |                   | Channels 2, 3       | MPLL_5                             | MPLL_6/MPLL_7 <sup>(1)</sup> |

|                  | GXBL1 (1)         | Channels 0, 1       | MPLL_7/MPLL_6                      | MPLL_8                       |

|                  |                   | Channels 2, 3       | MPLL_7                             | MPLL_8/GPLL_2                |

#### Note to Table 1–9:

(1)  $\tt MPLL_7$  and <code>GXBL1</code> are not applicable for transceivers in F484 package

Table 2–2 lists the power-down signals available for each transceiver block.

Table 2–2.

Transceiver Block Power-Down Signals

| Signal        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|               | Resets the transceiver PLL. The pll_areset signal is asserted in two conditions:                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| pll_areset    | <ul> <li>During reset sequence, the signal is asserted to reset the transceiver PLL. This signal is<br/>controlled by the user.</li> </ul>                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|               | <ul> <li>After the transceiver PLL is reconfigured, the signal is asserted high by the<br/>ALTPLL_RECONFIG controller. This signal is not controlled by the user.</li> </ul>                                                                                                                                                                                                                                                                                                                             |  |  |  |

| avb powerdowp | Powers down the entire transceiver block. When this signal is asserted, this signal powers down the PCS and PMA in all the transceiver channels.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| gxb_powerdown | This signal operates independently from the other reset signals. This signal is common to the transceiver block.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| pll_locked    | A status signal. Indicates the status of the transmitter multipurpose PLLs or general purpose PLLs.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|               | <ul> <li>A high level—indicates the multipurpose PLL or general purpose PLL is locked to the<br/>incoming reference clock frequency.</li> </ul>                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|               | A status signal. Indicates the status of the receiver CDR lock mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| rx_freqlocked | A high level—the receiver is in lock-to-data mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|               | A low level—the receiver CDR is in lock-to-reference mode.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| busy          | A status signal. An output from the ALTGX_RECONFIG block indicates the status of the dynamic reconfiguration controller. This signal remains low for the first reconfig_clk clock cycle after power up. It then gets asserted from the second reconfig_clk clock cycle. Assertion on this signal indicates that the offset cancellation process is being executed on the receiver buffer as well as the receiver CDR. When this signal is deasserted, it indicates that offset cancellation is complete. |  |  |  |

|               | This busy signal is also used to indicate the dynamic reconfiguration duration such as in analog reconfiguration mode and channel reconfiguration mode.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

For more information about offset cancellation, refer to the *Cyclone IV Dynamic Reconfiguration* chapter.

IF If none of the channels is instantiated in a transceiver block, the Quartus<sup>®</sup> II software automatically powers down the entire transceiver block.

### **Blocks Affected by the Reset and Power-Down Signals**

Table 2–3 lists the blocks that are affected by specific reset and power-down signals.

| Table 2–3. | Blocks Affected by Reset and Power-Down Signals | (Part 1 of 2) |

|------------|-------------------------------------------------|---------------|

|------------|-------------------------------------------------|---------------|

| Transceiver Block                          | rx_digitalreset | rx_analogreset | tx_digitalreset | pll_areset   | gxb_powerdown |

|--------------------------------------------|-----------------|----------------|-----------------|--------------|---------------|

| multipurpose PLLs and general purpose PLLs | —               | _              | _               | $\checkmark$ | _             |

| Transmitter Phase<br>Compensation FIFO     | _               | _              | ~               | _            | ~             |

| Byte Serializer                            | _               |                | $\checkmark$    | _            | $\checkmark$  |

| 8B/10B Encoder                             | —               | —              | ~               |              | $\checkmark$  |

#### **Option 3: Use the Respective Channel Receiver Core Clocks**

- Enable this option if you want the individual channel's rx\_clkout signal to provide the read clock to its respective Receive Phase Compensation FIFO.

- This option is typically enabled when the channel is reconfigured from a Basic or Protocol configuration with or without rate matching to another Basic or Protocol configuration with or without rate matching.

Figure 3–15 shows the respective rx\_clkout of each channel clocking the respective receiver channels of a transceiver block.

### **PLL Reconfiguration Mode**

Cyclone IV GX device support the PLL reconfiguration support through the ALTPLL\_RECONFIG MegaWizard. You can use this mode to reconfigure the multipurpose PLL or general purpose PLL used to clock the transceiver channel without affecting the remaining blocks of the channel. When you reconfigure the multipurpose PLL or general purpose PLL of a transceiver block to run at a different data rate, all the transceiver channels listening to this multipurpose PLL or general purpose PLL also get reconfigure the multipurpose PLL or general purpose PLL also get reconfigure the multipurpose PLL or general purpose to the new data rate. Channel settings are not affected. When you reconfigure the multipurpose PLL or general purpose PLL to support a different data rate, you must ensure that the functional mode of the transceiver channel supports the reconfigured data rate.

The PLL reconfiguration mode can be enabled by selecting the **Enable PLL Reconfiguration** option in the ALTGX MegaWizard under **Reconfiguration Setting** tab. For multipurpose PLL or general purpose PLL reconfiguration, **.mif** files are required to dynamically reconfigure the PLL setting in order to change the output frequency of the transceiver PLL to support different data rates. This chapter provides additional information about the document and Altera.

# **About this Handbook**

This handbook provides comprehensive information about the Altera<sup>®</sup> Cyclone<sup>®</sup> IV family of devices.

# **How to Contact Altera**

To locate the most up-to-date information about Altera products, refer to the following table.

| Contact <sup>(1)</sup>         | <b>Contact Method</b>           | Address                   |

|--------------------------------|---------------------------------|---------------------------|

| Technical support              | Website                         | www.altera.com/support    |

| Technical training             | Website www.altera.com/training |                           |

| recinical training             | Email                           | custrain@altera.com       |

| Product literature             | Website                         | www.altera.com/literature |

| Nontechnical support (general) | Email                           | nacomp@altera.com         |

| (software licensing)           | Email                           | authorization@altera.com  |

Note to Table:

(1) You can also contact your local Altera sales office or sales representative.

# **Typographic Conventions**

The following table shows the typographic conventions this document uses.

| Visual Cue                                | Meaning                                                                                                                                                                                                                       |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial Capital<br>Letters | Indicate command names, dialog box titles, dialog box options, and other GUI labels. For example, <b>Save As</b> dialog box. For GUI elements, capitalization matches the GUI.                                                |

| bold type                                 | Indicates directory names, project names, disk drive names, file names, file name extensions, software utility names, and GUI labels. For example, <b>\qdesigns</b> directory, <b>D:</b> drive, and <b>chiptrip.gdf</b> file. |

| Italic Type with Initial Capital Letters  | Indicate document titles. For example, Stratix IV Design Guidelines.                                                                                                                                                          |

|                                           | Indicates variables. For example, $n + 1$ .                                                                                                                                                                                   |

| italic type                               | Variable names are enclosed in angle brackets (< >). For example, <i><file name=""></file></i> and <i><project name="">.pof</project></i> file.                                                                               |

| Initial Capital Letters                   | Indicate keyboard keys and menu names. For example, the Delete key and the Options menu.                                                                                                                                      |

| "Subheading Title"                        | Quotation marks indicate references to sections in a document and titles of Quartus II Help topics. For example, "Typographic Conventions."                                                                                   |