## Intel - EP4CE22F17C6 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                  |

|--------------------------------|---------------------------------------------------------|

| Number of LABs/CLBs            | 1395                                                    |

| Number of Logic Elements/Cells | 22320                                                   |

| Total RAM Bits                 | 608256                                                  |

| Number of I/O                  | 153                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 256-LBGA                                                |

| Supplier Device Package        | 256-FBGA (17x17)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce22f17c6 |

|                                |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# I/O Features

Cyclone IV device I/O supports programmable bus hold, programmable pull-up resistors, programmable delay, programmable drive strength, programmable slew-rate control to optimize signal integrity, and hot socketing. Cyclone IV devices support calibrated on-chip series termination (Rs OCT) or driver impedance matching (Rs) for single-ended I/O standards. In Cyclone IV GX devices, the high-speed transceiver I/Os are located on the left side of the device. The top, bottom, and right sides can implement general-purpose user I/Os.

Table 1–8 lists the I/O standards that Cyclone IV devices support.

| Туре             | I/O Standard                                               |  |  |  |  |

|------------------|------------------------------------------------------------|--|--|--|--|

| Single-Ended I/O | LVTTL, LVCMOS, SSTL, HSTL, PCI, and PCI-X                  |  |  |  |  |

| Differential I/O | SSTL, HSTL, LVPECL, BLVDS, LVDS, mini-LVDS, RSDS, and PPDS |  |  |  |  |

Table 1–8. I/O Standards Support for the Cyclone IV Device Family

The LVDS SERDES is implemented in the core of the device using logic elements.

• For more information, refer to the *I/O Features in Cyclone IV Devices* chapter.

# **Clock Management**

Cyclone IV devices include up to 30 global clock (GCLK) networks and up to eight PLLs with five outputs per PLL to provide robust clock management and synthesis. You can dynamically reconfigure Cyclone IV device PLLs in user mode to change the clock frequency or phase.

Cyclone IV GX devices support two types of PLLs: multipurpose PLLs and generalpurpose PLLs:

- Use multipurpose PLLs for clocking the transceiver blocks. You can also use them for general-purpose clocking when they are not used for transceiver clocking.

- Use general purpose PLLs for general-purpose applications in the fabric and periphery, such as external memory interfaces. Some of the general purpose PLLs can support transceiver clocking.

**\*** For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

# **External Memory Interfaces**

Cyclone IV devices support SDR, DDR, DDR2 SDRAM, and QDRII SRAM interfaces on the top, bottom, and right sides of the device. Cyclone IV E devices also support these interfaces on the left side of the device. Interfaces may span two or more sides of the device to allow more flexible board design. The Altera® DDR SDRAM memory interface solution consists of a PHY interface and a memory controller. Altera supplies the PHY IP and you can use it in conjunction with your own custom memory controller or an Altera-provided memory controller. Cyclone IV devices support the use of error correction coding (ECC) bits on DDR and DDR2 SDRAM interfaces.

# 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices

#### CYIV-51002-1.0

This chapter contains feature definitions for logic elements (LEs) and logic array blocks (LABs). Details are provided on how LEs work, how LABs contain groups of LEs, and how LABs interface with the other blocks in Cyclone<sup>®</sup> IV devices.

# **Logic Elements**

Logic elements (LEs) are the smallest units of logic in the Cyclone IV device architecture. LEs are compact and provide advanced features with efficient logic usage. Each LE has the following features:

- A four-input look-up table (LUT), which can implement any function of four variables

- A programmable register

- A carry chain connection

- A register chain connection

- The ability to drive the following interconnects:

- Local

- Row

- Column

- Register chain

- Direct link

- Register packing support

- Register feedback support

Table 4–2 lists the sign of the multiplication results for the various operand sign representations. The results of the multiplication are signed if any one of the operands is a signed value.

| Data A      |             | Dat         | Result      |          |  |

|-------------|-------------|-------------|-------------|----------|--|

| signa Value | Logic Level | signb Value | Logic Level | nesuit   |  |

| Unsigned    | Low         | Unsigned    | Low         | Unsigned |  |

| Unsigned    | Low         | Signed      | High        | Signed   |  |

| Signed      | High        | Unsigned    | Low         | Signed   |  |

| Signed      | High        | Signed      | High        | Signed   |  |

Table 4–2. Multiplier Sign Representation

Each embedded multiplier block has only one signa and one signb signal to control the sign representation of the input data to the block. If the embedded multiplier block has two 9 × 9 multipliers, the Data A input of both multipliers share the same signa signal, and the Data B input of both multipliers share the same signb signal. You can dynamically change the signa and signb signals to modify the sign representation of the input operands at run time. You can send the signa and signb signals through a dedicated input register. The multiplier offers full precision, regardless of the sign representation.

# **Output Registers**

You can register the embedded multiplier output with output registers in either 18- or 36-bit sections, depending on the operational mode of the multiplier. The following control signals are available for each output register in the embedded multiplier:

- clock

- clock enable

- asynchronous clear

All input and output registers in a single embedded multiplier are fed by the same clock, clock enable, and asynchronous clear signals.

# **Operational Modes**

You can use an embedded multiplier block in one of two operational modes, depending on the application needs:

- One 18 × 18 multiplier

- Up to two 9 × 9 independent multipliers

You can also use embedded multipliers of Cyclone IV devices to implement multiplier adder and multiplier accumulator functions, in which the multiplier portion of the function is implemented with embedded multipliers, and the adder or accumulator function is implemented in logic elements (LEs).

When the signa and signb signals are unused, the Quartus II software sets the multiplier to perform unsigned multiplication by default.

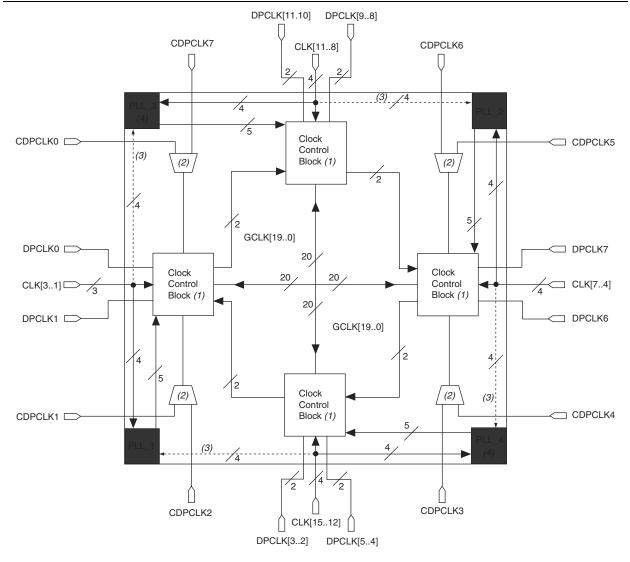

#### Figure 5-4. Clock Networks and Clock Control Block Locations in Cyclone IV E Devices

#### Notes to Figure 5-4:

- (1) There are five clock control blocks on each side.

- (2) Only one of the corner CDPCLK pins in each corner can feed the clock control block at a time. You can use the other CDPCLK pins as general-purpose I/O (GPIO) pins.

- (3) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

- (4)  $PLL_3$  and  $PLL_4$  are not available in EP4CE6 and EP4CE10 devices.

The inputs to the clock control blocks on each side of the Cyclone IV GX device must be chosen from among the following clock sources:

- Four clock input pins

- Ten PLL counter outputs (five from each adjacent PLLs)

- Two, four, or six DPCLK pins from the top, bottom, and right sides of the device

- Five signals from internal logic

20%. This feature is useful when clock sources can originate from multiple cards on the backplane, requiring a system-controlled switchover between frequencies of operation. Choose the secondary clock frequency so the VCO operates in the recommended frequency range. Also, set the M, N, and C counters accordingly to keep the VCO operating frequency in the recommended range.

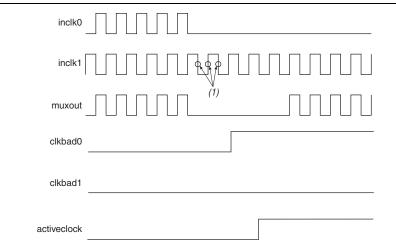

Figure 5–18 shows a waveform example of the switchover feature when using automatic loss of clock detection. Here, the inclk0 signal remains low. After the inclk0 signal remains low for approximately two clock cycles, the clock-sense circuitry drives the clkbad0 signal high. Also, because the reference clock signal is not toggling, the switchover state machine controls the multiplexer through the clksw signal to switch to inclk1.

#### Note to Figure 5–18:

(1) Switchover is enabled on the falling edge of inclk1 or inclk1, depending on which clock is available. In this figure, switchover is enabled on the falling edge of inclk1.

## **Manual Override**

If you are using the automatic switchover, you must switch input clocks with the manual override feature with the clkswitch input.

Figure 5–19 shows an example of a waveform illustrating the switchover feature when controlled by clkswitch. In this case, both clock sources are functional and inclk0 is selected as the reference clock. A low-to-high transition of the clkswitch signal starts the switchover sequence. The clkswitch signal must be high for at least three clock cycles (at least three of the longer clock period if inclk0 and inclk1 have different frequencies). On the falling edge of inclk0, the reference clock of the counter, muxout, is gated off to prevent any clock glitching. On the falling edge of inclk1, the reference clock multiplexer switches from inclk0 to inclk1 as the PLL reference, and the activeclock signal changes to indicate which clock is currently feeding the PLL.

# **High-Speed I/O Interface**

Cyclone IV E I/Os are separated into eight I/O banks, as shown in Figure 6–9 on page 6–17. Cyclone IV GX I/Os are separated into six user I/O banks with the left side of the device as the transceiver block, as shown in Figure 6–10 on page 6–18. Each bank has an independent power supply. True output drivers for LVDS, RSDS, mini-LVDS, and PPDS are on the right I/O banks. On the Cyclone IV E row I/O banks and the Cyclone IV GX right I/O banks, some of the differential pin pairs (p and n pins) of the true output drivers are not located on adjacent pins. In these cases, a power pin is located between the p and n pins. These I/O standards are also supported on all I/O banks using two single-ended output with the second output programmed as inverted, and an external resistor network. True input buffers for these I/O standards are supported on the top, bottom, and right I/O banks except for I/O bank 9.

# Power-On Reset (POR) Circuit

The POR circuit keeps the device in reset state until the power supply voltage levels have stabilized during device power up. After device power up, the device does not release nSTATUS until V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> (for I/O banks in which the configuration and JTAG pins reside) are above the POR trip point of the device. V<sub>CCINT</sub> and V<sub>CCA</sub> are monitored for brown-out conditions after device power up.

$V_{CCA}$  is the analog power to the phase-locked loop (PLL).

In some applications, it is necessary for a device to wake up very quickly to begin operation. Cyclone IV devices offer the fast POR time option to support fast wake-up time applications. The fast POR time option has stricter power-up requirements when compared with the standard POR time option. You can select either the fast option or the standard POR option with the MSEL pin settings.

- IF your system exceeds the fast or standard POR time, you must hold nCONFIG low until all the power supplies are stable.

- For more information about the POR specifications, refer to the *Cyclone IV Device Datasheet*.

- **To** For more information about the wake-up time and POR circuit, refer to the *Power Requirements for Cyclone IV Devices* chapter.

# **Configuration File Size**

Table 8–2 lists the approximate uncompressed configuration file sizes for Cyclone IV devices. To calculate the amount of storage space required for multiple device configurations, add the file size of each device together.

|              | Device   | Data Size (bits) |

|--------------|----------|------------------|

|              | EP4CE6   | 2,944,088        |

|              | EP4CE10  | 2,944,088        |

|              | EP4CE15  | 4,086,848        |

|              | EP4CE22  | 5,748,552        |

| Cyclone IV E | EP4CE30  | 9,534,304        |

|              | EP4CE40  | 9,534,304        |

|              | EP4CE55  | 14,889,560       |

|              | EP4CE75  | 19,965,752       |

|              | EP4CE115 | 28,571,696       |

Table 8–2. Uncompressed Raw Binary File (.rbf) Sizes for Cyclone IV Devices (Part 1 of 2)

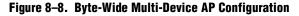

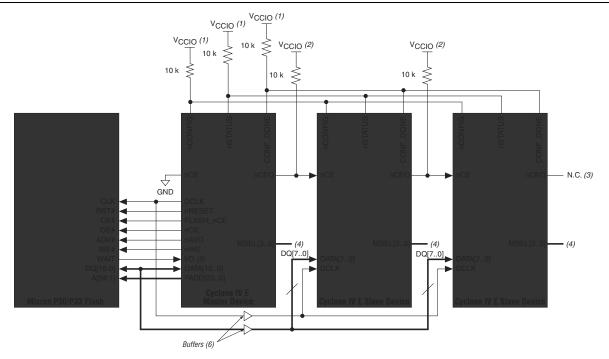

# **Byte-Wide Multi-Device AP Configuration**

The simpler method for multi-device AP configuration is the byte-wide multi-device AP configuration. In the byte-wide multi-device AP configuration, the LSB of the DATA [7..0] pin from the flash and master device (set to the AP configuration scheme) is connected to the slave devices set to the FPP configuration scheme, as shown in Figure 8–8.

#### Notes to Figure 8-8:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the V<sub>CCIO</sub> supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device in AP mode and the slave devices in FPP mode. To connect MSEL [3..0] for the master device in AP mode and the slave devices in FPP mode, refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

- (6) Connect the repeater buffers between the Cyclone IV E master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

## Word-Wide Multi-Device AP Configuration

The more efficient setup is one in which some of the slave devices are connected to the LSB of the DATA[7..0] and the remaining slave devices are connected to the MSB of the DATA[15..8]. In the word-wide multi-device AP configuration, the nCEO pin of the master device enables two separate daisy chains of slave devices, allowing both chains to be programmed concurrently, as shown in Figure 8–9.

The nSTATUS and CONF\_DONE pins on all target devices are connected together with external pull-up resistors, as shown in Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27. These pins are open-drain bidirectional pins on the devices. When the first device asserts nCEO (after receiving all its configuration data), it releases its CONF\_DONE pin. However, the subsequent devices in the chain keep this shared CONF\_DONE line low until they receive their configuration data. When all target devices in the chain receive their configuration data and release CONF\_DONE, the pull-up resistor drives a high level on this line and all devices simultaneously enter initialization mode.

# Guidelines for Connecting Parallel Flash to Cyclone IV E Devices for an AP Interface

For single- and multi-device AP configuration, the board trace length and loading between the supported parallel flash and Cyclone IV E devices must follow the recommendations listed in Table 8–11. These recommendations also apply to an AP configuration with multiple bus masters.

| Cyclone IV E AP Pins | Maximum Board Trace Length from<br>Cyclone IV E Device to Flash Device<br>(inches) | Maximum Board Load (pF) |

|----------------------|------------------------------------------------------------------------------------|-------------------------|

| DCLK                 | 6                                                                                  | 15                      |

| DATA[150]            | 6                                                                                  | 30                      |

| PADD[230]            | 6                                                                                  | 30                      |

| nRESET               | 6                                                                                  | 30                      |

| Flash_nCE            | 6                                                                                  | 30                      |

| nOE                  | 6                                                                                  | 30                      |

| nAVD                 | 6                                                                                  | 30                      |

| n₩E                  | 6                                                                                  | 30                      |

| I/O (1)              | 6                                                                                  | 30                      |

Table 8–11. Maximum Trace Length and Loading for AP Configuration

Note to Table 8-11:

(1) The AP configuration ignores the WAIT signal from the flash during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

## **Configuring With Multiple Bus Masters**

Similar to the AS configuration scheme, the AP configuration scheme supports multiple bus masters for the parallel flash. For another master to take control of the AP configuration bus, the master must assert nCONFIG low for at least 500 ns to reset the master Cyclone IV E device and override the weak 10-k $\Omega$  pull-down resistor on the nCE pin. This resets the master Cyclone IV E device then takes control of the AP configuration bus. The other master device then takes control of the AP configuration bus, then releases the nCE pin, and finally pulses nCONFIG low to restart the configuration.

In the AP configuration scheme, multiple masters share the parallel flash. Similar to the AS configuration scheme, the bus control is negotiated by the nCE pin.

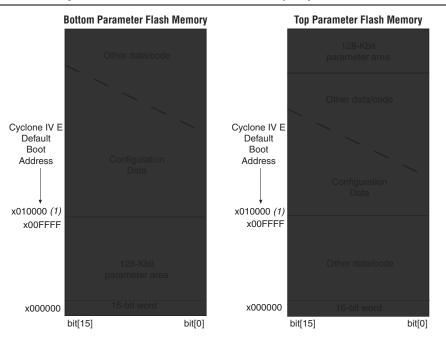

The default configuration boot address allows the system to use special parameter blocks in the flash memory map. Parameter blocks are at the top or bottom of the memory map. Figure 8–12 shows the configuration boot address in the AP configuration scheme. You can change the default configuration default boot address 0×010000 to any desired address using the APFC\_BOOT\_ADDR\_JTAG instruction. For more information about the APFC\_BOOT\_ADDR\_JTAG instruction, refer to "JTAG Instructions" on page 8–57.

#### Note to Figure 8-12:

(1) The default configuration boot address is x010000 when represented in 16-bit word addressing.

# **PS Configuration**

You can perform PS configuration on Cyclone IV devices with an external intelligent host, such as a MAX<sup>®</sup> II device, microprocessor with flash memory, or a download cable. In the PS scheme, an external host controls the configuration. Configuration data is clocked into the target Cyclone IV device through DATA[0] at each rising edge of DCLK.

If your system already contains a common flash interface (CFI) flash memory, you can use it for Cyclone IV device configuration storage as well. The MAX II PFL feature provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control the configuration from the flash memory device to the Cyclone IV device.

**Tor** For more information about the PFL, refer to *AN* 386: Using the Parallel Flash Loader with the Quartus II Software.

Cyclone IV devices do not support enhanced configuration devices for PS configuration.

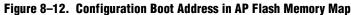

# **Transmitter Output Buffer**

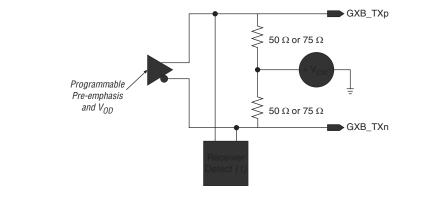

Figure 1–11 shows the transmitter output buffer block diagram.

#### Note to Figure 1-11:

(1) Receiver detect function is specific for PCIe protocol implementation only. For more information, refer to "PCI Express (PIPE) Mode" on page 1–52.

The Cyclone IV GX transmitter output buffers support the **1.5-V PCML** I/O standard and are powered by VCCH\_GXB power pins with 2.5-V supply. The 2.5-V supply on VCCH\_GXB pins are regulated internally to 1.5-V for the transmitter output buffers. The transmitter output buffers support the following additional features:

- Programmable differential output voltage (V<sub>OD</sub>)—customizes the V<sub>OD</sub> up to 1200 mV to handle different trace lengths, various backplanes, and various receiver requirements.

- Programmable pre-emphasis—boosts high-frequency components in the transmitted signal to maximize the data eye opening at the far-end. The high-frequency components might be attenuated in the transmission media due to data-dependent jitter and intersymbol interference (ISI) effects. The requirement for pre-emphasis increases as the data rates through legacy backplanes increase.

- Programmable differential on-chip termination (OCT)—provides calibrated OCT at differential 100 Ω or 150 Ω with on-chip transmitter common mode voltage (V<sub>CM</sub>) at 0.65 V. V<sub>CM</sub> is tri-stated when you disable the OCT to use external termination.

- Disable OCT to use external termination if the link requires a 85  $\Omega$  termination, such as when you are interfacing with certain PCIe Gen1 or Gen2 capable devices.

- The Cyclone IV GX transmitter output buffers are current-mode drivers. The resulting V<sub>OD</sub> voltage is therefore a function of the transmitter termination value. For lists of supported V<sub>OD</sub> settings, refer to the *Cyclone IV Device Data Sheet*.

## **Clock Rate Compensation**

In XAUI mode, the rate match FIFO compensates up to  $\pm 100$  ppm (200 ppm total) difference between the upstream transmitter and the local receiver reference clock. The XAUI protocol requires the transmitter to send /R/ (/K28.0/) code groups simultaneously on all four lanes (denoted as ||R|| column) during inter-packet gaps, adhering to rules listed in the IEEE P802.3ae specification.

The rate match operation begins after rx\_syncstatus and rx\_channelaligned are asserted. The rx\_syncstatus signal is from the word aligner, indicating that synchronization is acquired on all four channels, while rx\_channelaligned signal is from the deskew FIFO, indicating channel alignment.

The rate match FIFO looks for the ||R|| column (simultaneous /R/ code groups on all four channels) and deletes or inserts ||R|| columns to prevent the rate match FIFO from overflowing or under running. The rate match FIFO can insert or delete as many ||R|| columns as necessary to perform the rate match operation.

The rx\_rmfifodatadeleted and rx\_rmfifodatainserted flags that indicate rate match FIFO deletion and insertion events, respectively, are forwarded to the FPGA fabric. If an ||R|| column is deleted, the rx\_rmfifodeleted flag from each of the four channels goes high for one clock cycle per deleted ||R|| column. If an ||R|| column is inserted, the rx\_rmfifoinserted flag from each of the four channels goes high for one clock cycle per deleted ||R|| column. If an ||R|| column is inserted, the rx\_rmfifoinserted flag from each of the four channels goes high for one clock cycle per inserted ||R|| column.

The rate match FIFO does not insert or delete code groups automatically to overcome FIFO empty or full conditions. In this case, the rate match FIFO asserts the rx\_rmfifofull and rx\_rmfifoempty flags for at least three recovered clock cycles to indicate rate match FIFO full and empty conditions, respectively. You must then assert the rx\_digitalreset signal to reset the receiver PCS blocks.

# **Deterministic Latency Mode**

Deterministic Latency mode provides the transceiver configuration that allows no latency uncertainty in the datapath and features to strictly control latency variation. This mode supports non-bonded (×1) and bonded (×4) channel configurations, and is typically used to support CPRI and OBSAI protocols that require accurate delay measurements along the datapath. The Cyclone IV GX transceivers configured in Deterministic Latency mode provides the following features:

- registered mode phase compensation FIFO

- receive bit-slip indication

- transmit bit-slip control

- PLL PFD feedback

Figure 1–66 shows the transceiver channel datapath and clocking when configured in deterministic latency mode.

Note to Figure 1–66:

(1) High-speed recovered clock.

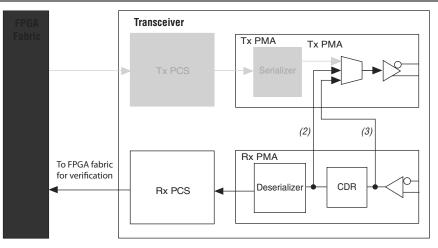

Figure 1–72 shows the two paths in reverse serial loopback mode.

Figure 1–72. Reverse Serial Loopback <sup>(1)</sup>

Notes to Figure 1-72:

- (1) Grayed-Out Blocks are Not Active in this mode.

- (2) Post-CDR reverse serial loopback path.

- (3) Pre-CDR reverse serial loopback path.

# **Self Test Modes**

Each transceiver channel in the Cyclone IV GX device contains modules for pattern generator and verifier. Using these built-in features, you can verify the functionality of the functional blocks in the transceiver channel without requiring user logic. The self test functionality is provided as an optional mechanism for debugging transceiver channels.

There are three types of supported pattern generators and verifiers:

- Built-in self test (BIST) incremental data generator and verifier—test the complete transmitter PCS and receiver PCS datapaths for bit errors with parallel loopback before the PMA blocks.

- Pseudo-random binary sequence (PRBS) generator and verifier—the PRBS generator and verifier interface with the serializer and deserializer in the PMA blocks. The advantage of using a PRBS data stream is that the randomness yields an environment that stresses the transmission medium. In the data stream, you can observe both random jitter and deterministic jitter using a time interval analyzer, bit error rate tester, or oscilloscope.

- High frequency and low frequency pattern generator—the high frequency patterns generate alternate ones and zeros and the low frequency patterns generate five ones and five zeroes. These patterns do not have a corresponding verifier.

The self-test features are only supported in Basic mode.

This solution may violate some of the protocol specific requirements. In such case, you can use Manual CDR lock option.

- For Manual CDR lock mode, rx\_freqlocked signal is not available. Upon detection of a dead link, take the following steps:

- a. Switch to LTR mode.

- b. Assert rx\_digitalreset.

- c. Wait for rx\_pll\_locked to go high.

- d. When you detect incoming data on the receive pins, switch to LTD mode.

- e. Wait for a duration of  $t_{LTD\_Manual}$ , which is the time taken to recover valid data after the rx\_locktodata signal is asserted in manual mode.

- f. De-assert rx\_digitalreset.

There are three methods that you can use to dynamically reconfigure the PMA controls of a transceiver channel:

- "Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels" on page 3–14

- "Method 2: Writing the Same Control Signals to Control All the Transceiver Channels" on page 3–16

- "Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same Time" on page 3–19

# Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels

Enable the logical\_channel\_address port by selecting the **Use** 'logical\_channel\_address' port option on the **Analog controls** tab. This method is applicable only for a design where the dynamic reconfiguration controller controls more than one channel.

You can additionally reconfigure either the receiver portion, transmitter portion, or both the receiver and transmitter portions of the transceiver channel by setting the corresponding value on the rx\_tx\_duplex\_sel input port. For more information, refer to Table 3–2 on page 3–4.

### **Connecting the PMA Control Ports**

The selected PMA control ports remain fixed in width, regardless of the number of channels controlled by the ALTGX\_RECONFIG instance:

- tx\_vodctrl and tx\_vodctrl\_out are fixed to 3 bits

- tx preemp and tx preemp out are fixed to 5 bits

- rx\_eqdcgain and rx\_eqdcgain\_out are fixed to 2 bits

- rx\_eqctrl and rx\_eqctrl\_out are fixed to 4 bits

#### Write Transaction

To complete a write transaction, perform the following steps:

- Set the selected PMA control ports to the desired settings (for example, tx\_vodctrl = 3'b001).

- 2. Set the logical\_channel\_address input port to the logical channel address of the transceiver channel whose PMA controls you want to reconfigure.

- 3. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 4. Ensure that the busy signal is low before you start a write transaction.

- 5. Assert the write\_all signal for one reconfig\_clk clock cycle.

The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

## Internal Weak Pull-Up and Weak Pull-Down Resistor

Table 1–12 lists the weak pull-up and pull-down resistor values for Cyclone IV devices.

Table 1–12. Internal Weak Pull-Up and Weak Pull-Down Resistor Values for Cyclone IV Devices (1)

| Symbol | Parameter                                                                                                                                                   | Conditions                                  | Min | Тур | Max | Unit |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

|        | Value of the I/O pin pull-up resistor<br>before and during configuration, as<br>well as user mode if you enable the<br>programmable pull-up resistor option | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (2), (3) | 7   | 25  | 41  | kΩ   |

|        |                                                                                                                                                             | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (2), (3) | 7   | 28  | 47  | kΩ   |

| R      |                                                                                                                                                             | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (2), (3) | 8   | 35  | 61  | kΩ   |

| R_pu   |                                                                                                                                                             | $V_{CCIO} = 1.8 \text{ V} \pm 5\%$ (2), (3) | 10  | 57  | 108 | kΩ   |

|        |                                                                                                                                                             | $V_{CCIO} = 1.5 \text{ V} \pm 5\%$ (2), (3) | 13  | 82  | 163 | kΩ   |

|        |                                                                                                                                                             | $V_{CCIO} = 1.2 \text{ V} \pm 5\%$ (2), (3) | 19  | 143 | 351 | kΩ   |

| R_PD   | Value of the I/O pin pull-down resistor before and during configuration                                                                                     | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (4)      | 6   | 19  | 30  | kΩ   |

|        |                                                                                                                                                             | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (4)      | 6   | 22  | 36  | kΩ   |

|        |                                                                                                                                                             | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (4)      | 6   | 25  | 43  | kΩ   |

|        |                                                                                                                                                             | $V_{CCIO} = 1.8 \text{ V} \pm 5\%$ (4)      | 7   | 35  | 71  | kΩ   |

|        |                                                                                                                                                             | $V_{CCIO} = 1.5 V \pm 5\%$ (4)              | 8   | 50  | 112 | kΩ   |

#### Notes to Table 1-12:

- (1) All I/O pins have an option to enable weak pull-up except the configuration, test, and JTAG pins. The weak pull-down feature is only available for JTAG TCK.

- (2) Pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (3)  $R_{PU} = (V_{CCIO} V_I)/I_{R_PU}$ Minimum condition: -40°C;  $V_{CCIO} = V_{CC} + 5\%$ ,  $V_I = V_{CC} + 5\% - 50$  mV; Typical condition: 25°C;  $V_{CCIO} = V_{CC}$ ,  $V_I = 0$  V; Maximum condition: 100°C;  $V_{CCIO} = V_{CC} - 5\%$ ,  $V_I = 0$  V; in which  $V_I$  refers to the input voltage at the I/O pin.

- $\begin{array}{ll} (4) & R_{\_PD} = V_I/I_{R\_PD} \\ & \text{Minimum condition:} -40^{\circ}\text{C}; \ V_{CCIO} = V_{CC} + 5\%, \ V_I = 50 \ \text{mV}; \\ & \text{Typical condition:} \ 25^{\circ}\text{C}; \ V_{CCIO} = V_{CC}, \ V_I = V_{CC} 5\%; \\ & \text{Maximum condition:} \ 100^{\circ}\text{C}; \ V_{CCIO} = V_{CC} 5\%, \ V_I = V_{CC} 5\%; \ \text{in which } V_I \ \text{refers to the input voltage at the I/O pin.} \end{array}$

## Hot-Socketing

Table 1–13 lists the hot-socketing specifications for Cyclone IV devices.

Table 1–13. Hot-Socketing Specifications for Cyclone IV Devices

| Symbol                  | Parameter                         | Maximum         |

|-------------------------|-----------------------------------|-----------------|

| I <sub>IOPIN(DC)</sub>  | DC current per I/O pin            | 300 μA          |

| I <sub>IOPIN(AC)</sub>  | AC current per I/O pin            | 8 mA <i>(1)</i> |

| I <sub>XCVRTX(DC)</sub> | DC current per transceiver TX pin | 100 mA          |

| I <sub>XCVRRX(DC)</sub> | DC current per transceiver RX pin | 50 mA           |

Note to Table 1-13:

(1) The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns, |IIOPIN| = C dv/dt, in which C is the I/O pin capacitance and dv/dt is the slew rate.

During hot-socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF.

### Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 4 of 4)

| Symbol/                                          | Conditions | C6  |                                    | C7, I7 |     | C8  |        |     | Unit |        |      |

|--------------------------------------------------|------------|-----|------------------------------------|--------|-----|-----|--------|-----|------|--------|------|

| Description                                      | Conultions | Min | Тур                                | Max    | Min | Тур | Max    | Min | Тур  | Max    | Unit |

| PLD-Transceiver Inte                             | rface      |     |                                    |        |     |     |        |     |      |        |      |

| Interface speed<br>(F324 and smaller<br>package) | _          | 25  | _                                  | 125    | 25  | _   | 125    | 25  | _    | 125    | MHz  |

| Interface speed<br>(F484 and larger<br>package)  | _          | 25  | _                                  | 156.25 | 25  | _   | 156.25 | 25  | _    | 156.25 | MHz  |

| Digital reset pulse width                        | _          |     | Minimum is 2 parallel clock cycles |        |     |     |        |     |      |        |      |

#### Notes to Table 1–21:

(1) This specification is valid for transmitter output jitter specification with a maximum total jitter value of 112 ps, typically for 3.125 Gbps SRIO and XAUI protocols.

(2) The minimum reconfig\_clk frequency is 2.5 MHz if the transceiver channel is configured in **Transmitter Only** mode. The minimum reconfig\_clk frequency is 37.5 MHz if the transceiver channel is configured in **Receiver Only** or **Receiver and Transmitter** mode.

(3) The device cannot tolerate prolonged operation at this absolute maximum.

- (4) The rate matcher supports only up to ±300 parts per million (ppm).

- (5) Supported for the F169 and F324 device packages only.

- (6) Supported for the F484, F672, and F896 device packages only. Pending device characterization.

- (7) To support CDR ppm tolerance greater than ±300 ppm, implement ppm detector in user logic and configure CDR to Manual Lock Mode.

- (8) Asynchronous spread-spectrum clocking is not supported.

- (9) For the EP4CGX30 (F484 package only), EP4CGX50, and EP4CGX75 devices, the CDR ppl tolerance is ±200 ppm.

- (10) Time taken until pll\_locked goes high after pll\_powerdown deasserts.

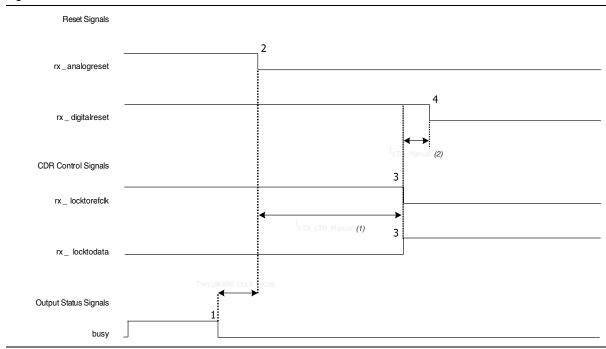

- (11) Time that the CDR must be kept in lock-to-reference mode after rx\_analogreset deasserts and before rx\_locktodata is asserted in manual mode.

(12) Time taken to recover valid data after the rx\_locktodata signal is asserted in manual mode (Figure 1-2), or after rx\_freqlocked signal goes high in automatic mode (Figure 1-3).

(13) Time taken to recover valid data after the rx\_locktodata signal is asserted in manual mode.

- (14) Time taken to recover valid data after the  $rx\_freqlocked$  signal goes high in automatic mode.

- (15) To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

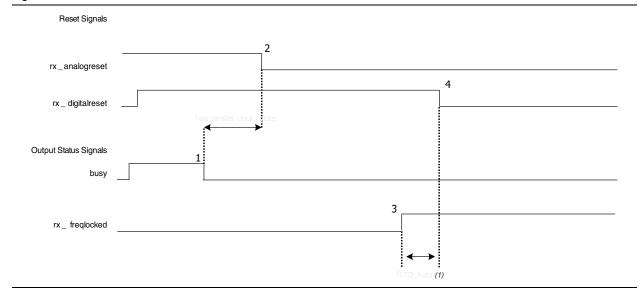

Figure 1–2 shows the lock time parameters in manual mode.

LTD = lock-to-data. LTR = lock-to-reference.

Figure 1–2. Lock Time Parameters for Manual Mode

Figure 1–3 shows the lock time parameters in automatic mode.

Figure 1–3. Lock Time Parameters for Automatic Mode

## Table 1-46. Glossary (Part 3 of 5)

| Letter | Term                                                   | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|--------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|        | R <sub>L</sub>                                         | Receiver differential input discrete resistor (external to Cyclone IV devices).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| R      | Receiver Input<br>Waveform                             | Receiver input waveform for LVDS and LVPECL differential standards:<br>Single-Ended Waveform<br>Positive Channel (p) = $V_{IH}$<br>Negative Channel (n) = $V_{IL}$<br>Ground<br>Differential Waveform (Mathematical Function of Positive & Negative Channel)<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$ |  |  |  |  |  |  |

|        | Receiver input<br>skew margin<br>(RSKM)                | High-speed I/O block: The total margin left after accounting for the sampling window and TCCS.<br>RSKM = (TUI – SW – TCCS) / 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| S      | Single-ended<br>voltage-<br>referenced I/O<br>Standard | VCCIO         VOH         VIH(DC)         VIH(DC)         VIH(DC)         VIL(QC)         VIL(QC)         VIL(QC)         VIL(QC)         VIL(AC)         VIL(AC)         VIL(AC)         VIL(AC)         VIL(AC)         VIL(AC)         VIL(AC)         Values. The AC values indicate the voltage levels at which the receiver must meet its timing specifications. The DC values indicate the voltage levels at which the final logic state of the receiver is unambiguously defined. After the receiver input crosses the AC value, the receiver changes to the new logic state. The new logic state is then maintained as long as the input stays beyond the DC threshold. This approach is intended to provide predictable receiver timing in the presence of input waveform <i>ringing</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|        | SW (Sampling<br>Window)                                | High-speed I/O block: The period of time during which the data must be valid to capture it correctly. The setup and hold times determine the ideal strobe position in the sampling window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |