#### Intel - EP4CE22F17C8N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 1395                                                     |

| Number of Logic Elements/Cells | 22320                                                    |

| Total RAM Bits                 | 608256                                                   |

| Number of I/O                  | 153                                                      |

| Number of Gates                |                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 256-LBGA                                                 |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce22f17c8n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Visual Cue                               | Meaning                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input. The suffix n denotes an active-low signal. For example, resetn.                 |

| Courier type                             | Indicates command line commands and anything that must be typed exactly as it appears. For example, c:\qdesigns\tutorial\chiptrip.gdf.                                                 |

|                                          | Also indicates sections of an actual file, such as a Report File, references to parts of files (for example, the AHDL keyword SUBDESIGN), and logic function names (for example, TRI). |

| 4                                        | An angled arrow instructs you to press the Enter key.                                                                                                                                  |

| 1., 2., 3., and<br>a., b., c., and so on | Numbered steps indicate a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                          |

|                                          | Bullets indicate a list of items when the sequence of the items is not important.                                                                                                      |

| IP                                       | The hand points to information that requires special attention.                                                                                                                        |

| ?                                        | The question mark directs you to a software help system with related information.                                                                                                      |

| ••                                       | The feet direct you to another document or website with related information.                                                                                                           |

| <b>I</b> ₹¶                              | The multimedia icon directs you to a related multimedia presentation.                                                                                                                  |

| CAUTION                                  | A caution calls attention to a condition or possible situation that can damage or destroy the product or your work.                                                                    |

| WARNING                                  | A warning calls attention to a condition or possible situation that can cause you injury.                                                                                              |

|                                          | The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents.                 |

# **Section I. Device Core**

This section provides a complete overview of all features relating to the Cyclone<sup>®</sup> IV device family, which is the most architecturally advanced, high-performance, low-power FPGA in the marketplace. This section includes the following chapters:

- Chapter 1, Cyclone IV FPGA Device Family Overview

- Chapter 2, Logic Elements and Logic Array Blocks in Cyclone IV Devices

- Chapter 3, Memory Blocks in Cyclone IV Devices

- Chapter 4, Embedded Multipliers in Cyclone IV Devices

- Chapter 5, Clock Networks and PLLs in Cyclone IV Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information about when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

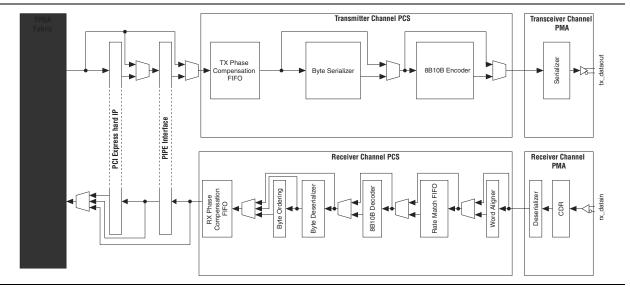

Figure 1–1 shows the structure of the Cyclone IV GX transceiver.

For more information, refer to the *Cyclone IV Transceivers Architecture* chapter.

## Hard IP for PCI Express (Cyclone IV GX Devices Only)

Cyclone IV GX devices incorporate a single hard IP block for ×1, ×2, or ×4 PCIe (PIPE) in each device. This hard IP block is a complete PCIe (PIPE) protocol solution that implements the PHY-MAC layer, Data Link Layer, and Transaction Layer functionality. The hard IP for the PCIe (PIPE) block supports root-port and end-point configurations. This pre-verified hard IP block reduces risk, design time, timing closure, and verification. You can configure the block with the Quartus II software's PCI Express Compiler, which guides you through the process step by step.

For more information, refer to the PCI Express Compiler User Guide.

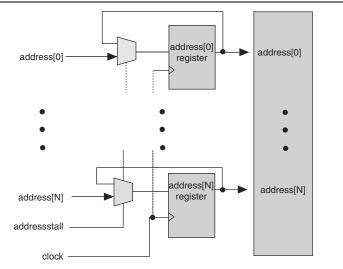

### **Address Clock Enable Support**

Cyclone IV devices M9K memory blocks support an active-low address clock enable, which holds the previous address value for as long as the addressstall signal is high (addressstall = '1'). When you configure M9K memory blocks in dual-port mode, each port has its own independent address clock enable.

Figure 3–2 shows an address clock enable block diagram. The address register output feeds back to its input using a multiplexer. The multiplexer output is selected by the address clock enable (addressstall) signal.

$\label{eq:Figure 3-2. Cyclone IV Devices Address Clock Enable Block Diagram$

The address clock enable is typically used to improve the effectiveness of cache memory applications during a cache-miss. The default value for the address clock enable signals is low.

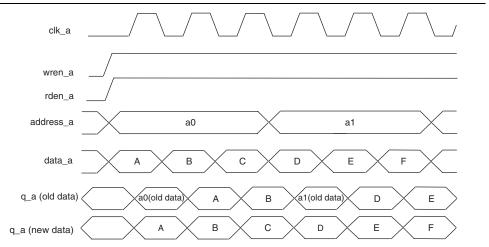

Figure 3–7 shows a timing waveform for read and write operations in single-port mode with unregistered outputs. Registering the outputs of the RAM simply delays the q output by one clock cycle.

Figure 3–7. Cyclone IV Devices Single-Port Mode Timing Waveform

### **Simple Dual-Port Mode**

Simple dual-port mode supports simultaneous read and write operations to different locations. Figure 3–8 shows the simple dual-port memory configuration.

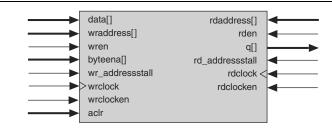

Figure 3–8. Cyclone IV Devices Simple Dual-Port Memory (1)

#### Note to Figure 3-8:

(1) Simple dual-port RAM supports input or output clock mode in addition to the read or write clock mode shown.

Cyclone IV devices M9K memory blocks support mixed-width configurations, allowing different read and write port widths. Table 3–3 lists mixed-width configurations.

Table 3–3.

Cyclone IV Devices M9K Block Mixed-Width Configurations (Simple Dual-Port Mode)

(Part 1 of 2)

| Dood Dort | Write Port   |              |              |              |              |              |          |          |          |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|----------|----------|----------|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 256 × 32     | 1024 × 9 | 512 × 18 | 256 × 36 |

| 8192 × 1  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _        |          | —        |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -        |          | —        |

| 2048 × 4  | ~            | ~            | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$ | _        | _        | —        |

| 1024 × 8  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _        | _        | —        |

In true dual-port mode, you can access any memory location at any time from either port A or port B. However, when accessing the same memory location from both ports, you must avoid possible write conflicts. When you attempt to write to the same address location from both ports at the same time, a write conflict happens. This results in unknown data being stored to that address location. There is no conflict resolution circuitry built into the Cyclone IV devices M9K memory blocks. You must handle address conflicts external to the RAM block.

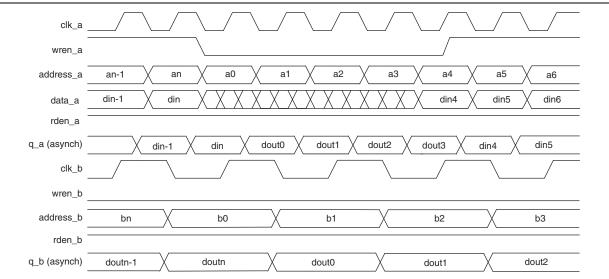

Figure 3–11 shows true dual-port timing waveforms for the write operation at port A and read operation at port B. Registering the outputs of the RAM simply delays the q outputs by one clock cycle.

Figure 3–11. Cyclone IV Devices True Dual-Port Timing Waveform

### **Shift Register Mode**

Cyclone IV devices M9K memory blocks can implement shift registers for digital signal processing (DSP) applications, such as finite impulse response (FIR) filters, pseudo-random number generators, multi-channel filtering, and auto-correlation and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flipflops that quickly exhaust many logic cells for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources.

The size of a ( $w \times m \times n$ ) shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n), and must be less than or equal to the maximum number of memory bits, which is 9,216 bits. In addition, the size of ( $w \times n$ ) must be less than or equal to the maximum width of the block, which is 36 bits. If you need a larger shift register, you can cascade the M9K memory blocks.

### **External Memory Interfacing**

Cyclone IV devices support I/O standards required to interface with a broad range of external memory interfaces, such as DDR SDRAM, DDR2 SDRAM, and QDR II SRAM.

For more information about Cyclone IV devices external memory interface support, refer to the *External Memory Interfaces in Cyclone IV Devices* chapter.

# **Pad Placement and DC Guidelines**

You can use the Quartus II software to validate your pad and pin placement.

### **Pad Placement**

Altera recommends that you create a Quartus II design, enter your device I/O assignments and compile your design to validate your pin placement. The Quartus II software checks your pin connections with respect to the I/O assignment and placement rules to ensure proper device operation. These rules depend on device density, package, I/O assignments, voltage assignments and other factors that are not fully described in this chapter.

For more information about how the Quartus II software checks I/O restrictions, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

### **DC Guidelines**

For the Quartus II software to automatically check for illegally placed pads according to the DC guidelines, set the DC current sink or source value to **Electromigration Current** assignment on each of the output pins that are connected to the external resistive load.

The programmable current strength setting has an impact on the amount of DC current that an output pin can source or sink. Determine if the current strength setting is sufficient for the external resistive load condition on the output pin.

## **Clock Pins Functionality**

Cyclone IV clock pins have multiple purposes, as per listed:

- CLK pins—Input support for single-ended and voltage-referenced standards. For I/O standard support, refer to Table 6–3 on page 6–11.

- DIFFCLK pins—Input support for differential standards. For I/O standard support, refer to Table 6–3 on page 6–11. When used as DIFFCLK pins, DC or AC coupling can be used depending on the interface requirements and external termination is required. For more information, refer to "High-Speed I/O Standards Support" on page 6–28.

- REFCLK pins—Input support for high speed differential reference clocks used by the transceivers in Cyclone IV GX devices. For I/O support, coupling, and termination requirements, refer to Table 6–10 on page 6–29.

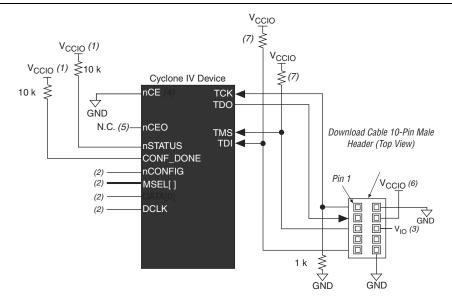

# Figure 8–24. JTAG Configuration of a Single Device Using a Download Cable (1.5-V or 1.8-V $V_{\text{CCIO}}$ Powering the JTAG Pins)

#### Notes to Figure 8-24:

- (1) Connect these pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the nCONFIG and MSEL pins to support a non-JTAG configuration scheme. If you only use JTAG configuration, connect the nCONFIG pin to logic-high and the MSEL pins to GND. In addition, pull DCLK and DATA[0] to either high or low, whichever is convenient on your board.

- (3) In the USB-Blaster and ByteBlaster II cables, this pin is connected to nCE when it is used for AS programming; otherwise it is a no connect.

- (4) The nCE must be connected to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (6) Power up the V<sub>CC</sub> of the EthernetBlaster, ByteBlaster II or USB-Blaster cable with supply from V<sub>CCI0</sub>. The Ethernet-Blaster, ByteBlaster II, and USB-Blaster cables do not support a target supply voltage of 1.2 V. For the target supply voltage value, refer to the *ByteBlaster II Download Cable User Guide*, the USB-Blaster Download Cable User Guide, and the EthernetBlaster Communications Cable User Guide.

- (7) Resistor value can vary from 1 k $\Omega$  to 10 k $\Omega$ .

To configure a single device in a JTAG chain, the programming software places all other devices in bypass mode. In bypass mode, devices pass programming data from the TDI pin to the TDO pin through a single bypass register without being affected internally. This scheme enables the programming software to program or verify the target device. Configuration data driven into the device appears on the TDO pin one clock cycle later.

The Quartus II software verifies successful JTAG configuration after completion. At the end of configuration, the software checks the state of CONF\_DONE through the JTAG port. When Quartus II generates a **.jam** for a multi-device chain, it contains instructions so that all the devices in the chain are initialized at the same time. If CONF\_DONE is not high, the Quartus II software indicates that configuration has failed. If CONF\_DONE is high, the software indicates that configuration was successful. After the configuration bitstream is serially sent using the JTAG TDI port, the TCK port clocks an additional clock cycles to perform device initialization.

- External configuration reset (nCONFIG) assertion

- User watchdog timer time out

Table 8–24 lists the contents of the current state logic in the status register, when the remote system upgrade master state machine is in factory configuration or application configuration accessing the factory information or application information, respectively. The status register bit in Table 8–24 lists the bit positions in a 32-bit logic.

| Remote System Upgrade<br>Master State Machine | Status<br>Register Bit | Definition                            | Description                                                                                                                       |  |

|-----------------------------------------------|------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

|                                               | 31:30                  | Master state machine<br>current state | The current state of the remote system upgrade master state machine                                                               |  |

| Factory information <sup>(1)</sup>            | 29:24                  | Reserved bits                         | Padding bits that are set to all 0's                                                                                              |  |

|                                               | 23:0                   | Boot address                          | The current 24-bit boot address that was used by the configuration scheme as the start address to load the current configuration. |  |

|                                               | 31:30                  | Master state machine current state    | The current state of the remote system upgrade master state machine                                                               |  |

| Application information 1 <sup>(2)</sup>      | 29                     | User watchdog timer<br>enable bit     | The current state of the user watchdog enable, which is active high                                                               |  |

|                                               | 28:0                   | User watchdog timer<br>time-out value | The current entire 29-bit watchdog time-out value.                                                                                |  |

|                                               | 31:30                  | Master state machine current state    | The current state of the remote system upgrade master state machine                                                               |  |

| Application information 2 (2)                 | 29:24                  | Reserved bits                         | Padding bits that are set to all 0's                                                                                              |  |

|                                               | 23:0                   | Boot address                          | The current 24-bit boot address that was used as the start address to load the current configuration                              |  |

#### Notes to Table 8-24:

(1) The remote system upgrade master state machine is in factory configuration.

(2) The remote system upgrade master state machine is in application configuration.

The previous two application configurations are available in the previous state registers (previous state register 1 and previous state register 2), but only for debugging purposes.

The remote system upgrade status register is updated by the dedicated error monitoring circuitry after an error condition, but before the factory configuration is loaded.

| <b>Reconfiguration Error/Trigger</b> | Control Register Setting In Remote Update |

|--------------------------------------|-------------------------------------------|

| nCONFIG reset                        | All bits are 0                            |

| nSTATUS <b>error</b>                 | All bits are 0                            |

| CORE triggered reconfiguration       | Update register                           |

| CRC error                            | All bits are 0                            |

| Wd time out                          | All bits are 0                            |

Table 8–26. Control Register Contents After an Error or Reconfiguration Trigger Condition

### **User Watchdog Timer**

The user watchdog timer prevents a faulty application configuration from indefinitely stalling the device. The system uses the timer to detect functional errors after an application configuration is successfully loaded into the Cyclone IV device.

The user watchdog timer is a counter that counts down from the initial value loaded into the remote system upgrade control register by the factory configuration. The counter is 29 bits wide and has a maximum count value of 2<sup>29</sup>. When specifying the user watchdog timer value, specify only the most significant 12 bits. The remote system upgrade circuitry appends 17'b1000 to form the 29-bits value for the watchdog timer. The granularity of the timer setting is 2<sup>17</sup> cycles. The cycle time is based on the frequency of the 10-MHz internal oscillator or CLKUSR (maximum frequency of 40 MHz).

Table 8–27 lists the operating range of the 10-MHz internal oscillator.

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5       | 6.5     | 10      | MHz  |

The user watchdog timer begins counting after the application configuration enters device user mode. This timer must be periodically reloaded or reset by the application configuration before the timer expires by asserting RU\_nRSTIMER. If the application configuration does not reload the user watchdog timer before the count expires, a time-out signal is generated by the remote system upgrade dedicated circuitry. The time-out signal tells the remote system upgrade circuitry to set the user watchdog timer status bit (Wd) in the remote system upgrade status register and reconfigures the device by loading the factory configuration.

To allow the remote system upgrade dedicated circuitry to reset the watchdog timer, you must assert the RU\_nRSTIMER signal active for a minimum of 250 ns. This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE megafunction high for a minimum of 250 ns.

Errors during configuration are detected by the CRC engine. Functional errors must not exist in the factory configuration because it is stored and validated during production and is never updated remotely.

# **Document Revision History**

Table 9–8 lists the revision history for this chapter.

| Table 9–8. Docum | ent Revision | History |

|------------------|--------------|---------|

|------------------|--------------|---------|

| Date          | Version | Changes                                                                                                                                                                                                                  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2013      | 1.3     | Updated "CRC_ERROR Pin Type" in Table 9–2.                                                                                                                                                                               |

| October 2012  | 1.2     | Updated Table 9–2.                                                                                                                                                                                                       |

| February 2010 | 1.1     | <ul> <li>Updated for the Quartus II software version 9.1 SP1 release:</li> <li>Updated "Configuration Error Detection" section.</li> <li>Updated Table 9–6.</li> <li>Added Cyclone IV E devices in Table 9–6.</li> </ul> |

| November 2009 | 1.0     | Initial release.                                                                                                                                                                                                         |

# **1. Cyclone IV Transceivers Architecture**

Cyclone<sup>®</sup> IV GX devices include up to eight full-duplex transceivers at serial data rates between 600 Mbps and 3.125 Gbps in a low-cost FPGA. Table 1–1 lists the supported Cyclone IV GX transceiver channel serial protocols.

| Protocol                                                     | Data Rate (Gbps)                  | F324 and smaller<br>packages | F484 and larger<br>packages |

|--------------------------------------------------------------|-----------------------------------|------------------------------|-----------------------------|

| PCI Express <sup>®</sup> (PCIe <sup>®</sup> ) <sup>(1)</sup> | 2.5                               | $\checkmark$                 | $\checkmark$                |

| Gbps Ethernet (GbE)                                          | 1.25                              | $\checkmark$                 | $\checkmark$                |

| Common Public Radio Interface (CPRI)                         | 0.6144, 1.2288, 2.4576, and 3.072 | <ul> <li>(2)</li> </ul>      | $\checkmark$                |

| OBSAI                                                        | 0.768, 1.536, and 3.072           | ✓ (2)                        | $\checkmark$                |

| XAUI                                                         | 3.125                             | —                            | $\checkmark$                |

| Carial digital interface (CDI)                               | HD-SDI at 1.485 and 1.4835        |                              | /                           |

| Serial digital interface (SDI)                               | 3G-SDI at 2.97 and 2.967          | —                            | $\checkmark$                |

| Serial RapidIO <sup>®</sup> (SRIO)                           | 1.25, 2.5, and 3.125              | —                            | $\checkmark$                |

| Serial Advanced Technology Attachment (SATA)                 | 1.5 and 3.0                       | —                            | $\checkmark$                |

| V-by-one                                                     | 3.125                             | —                            | $\checkmark$                |

| Display Port                                                 | 1.62 and 2.7                      | —                            | $\checkmark$                |

#### Notes to Table 1-1:

(1) Provides the physical interface for PCI Express (PIPE)-compliant interface that supports Gen1 ×1, ×2, and ×4 initial lane width configurations. When implementing ×1 or ×2 interface, remaining channels in the transceiver block are available to implement other protocols.

(2) Supports data rates up to 2.5 Gbps only.

You can implement these protocols through the ALTGX MegaWizard<sup>™</sup> Plug-In Manager, which also offers the highly flexible Basic functional mode to implement proprietary serial protocols at the following serial data rates:

- 600 Mbps to 2.5 Gbps for devices in F324 and smaller packages

- 600 Mbps to 3.125 Gbps for devices in F484 and larger packages

For descriptions of the ports available when instantiating a transceiver using the ALTGX megafunction, refer to "Transceiver Top-Level Port Lists" on page 1–85.

For more information about Cyclone IV transceivers that run at ≥2.97 Gbps data rate, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

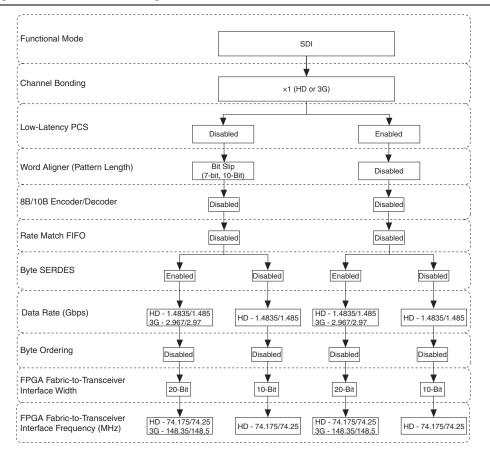

Figure 1–69 shows the transceiver configuration in SDI mode.

Figure 1–69. Transceiver Configuration in SDI Mode

Altera recommends driving rx\_bitslip port low in configuration where low-latency PCS is not enabled. In SDI systems, the word alignment and framing occurs after descrambling, which is implemented in the user logic. The word alignment therefore is not useful, and keeping rx\_bitslip port low avoids the word aligner from inserting bits in the received data stream.

# Loopback

Cyclone IV GX devices provide three loopback options that allow you to verify the operation of different functional blocks in the transceiver channel. The following loopback modes are available:

- reverse parallel loopback (available only for PIPE mode)

- serial loopback (available for all modes except PIPE mode)

- reverse serial loopback (available for all modes except XAUI mode)

In each loopback mode, all transmitter buffer and receiver buffer settings are available if the buffers are active, unless stated otherwise.

| Port Name                  | Input/<br>Output | Clock Domain        | Description                                                                                                                                                                                                                                                                                                     |

|----------------------------|------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fixedclk                   | Input            | Clock signal        | 125-MHz clock for receiver detect and offset cancellation only in PIPE mode.                                                                                                                                                                                                                                    |

|                            |                  |                     | Receiver detect or reverse parallel loopback control.                                                                                                                                                                                                                                                           |

| tx_detectrxloop            | Input            | Asynchronous signal | <ul> <li>A high level in the P1 power state and tx_forcelecidle<br/>signal asserted begins the receiver detection operation to determine<br/>if there is a valid receiver downstream. This signal must be<br/>deasserted when the pipephydonestatus signal indicates<br/>receiver detect completion.</li> </ul> |

|                            |                  |                     | <ul> <li>A high level in the P0 power state with the tx_forceelecidle<br/>signal deasserted dynamically configures the channel to support<br/>reverse parallel loopback mode.</li> </ul>                                                                                                                        |

|                            |                  |                     | Force the 8B/10B encoder to encode with negative running disparity.                                                                                                                                                                                                                                             |

| tx_forcedisp<br>compliance | Input            | Asynchronous signal | <ul> <li>Assert only when transmitting the first byte of the PIPE-compliance<br/>pattern to force the 8B/10B encoder with a negative running<br/>disparity.</li> </ul>                                                                                                                                          |

| pipe8b10binvpolarity       | Input            | Asynchronous signal | Invert the polarity of every bit of the 10-bit input to the 8B/10B decoder                                                                                                                                                                                                                                      |

|                            |                  |                     | PIPE power state control.                                                                                                                                                                                                                                                                                       |

|                            |                  |                     | <ul> <li>Signal is 2 bits wide and is encoded as follows:</li> </ul>                                                                                                                                                                                                                                            |

| powerdn                    | Input            | Asynchronous signal | <ul> <li>2'b00: P0 (Normal operation)</li> </ul>                                                                                                                                                                                                                                                                |

| powerun                    | mput             | Asynchionous signal | <ul> <li>2'b01: P0s (Low recovery time latency, low power state)</li> </ul>                                                                                                                                                                                                                                     |

|                            |                  |                     | <ul> <li>2'b10: P1 (Longer recovery time latency, lower power state)</li> </ul>                                                                                                                                                                                                                                 |

|                            |                  |                     | <ul> <li>2'b11: P2 (Lowest power state)</li> </ul>                                                                                                                                                                                                                                                              |

| pipedatavalid              | Output           | N/A                 | Valid data and control on the rx_dataout and rx_ctrldetect ports indicator.                                                                                                                                                                                                                                     |

|                            |                  |                     | PHY function completion indicator.                                                                                                                                                                                                                                                                              |

| pipephydone<br>status      | Output           | Asynchronous signal | <ul> <li>Asserted for one clock cycle to communicate completion of several<br/>PHY functions, such as power state transition and receiver<br/>detection.</li> </ul>                                                                                                                                             |

|                            |                  |                     | Electrical idle detected or inferred at the receiver indicator.                                                                                                                                                                                                                                                 |

| pipeelecidle               | Output           | Asynchronous signal | <ul> <li>When electrical idle inference is used, this signal is driven high<br/>when it infers an electrical idle condition</li> </ul>                                                                                                                                                                          |

|                            |                  |                     | <ul> <li>When electrical idle inference is not used, the<br/>rx_signaldetect signal is inverted and driven on this port.</li> </ul>                                                                                                                                                                             |

# Cyclone IV Device Handbook,

# Volume 3

101 Innovation Drive San Jose, CA 95134 www.altera.com

CYIV-5V3-2.1

| I/0                    |       | V <sub>ccio</sub> (V) | )     |                                                              | V <sub>REF</sub> (V)                                                                                                | V <sub>TT</sub> (V) <sup>(2)</sup>                                                                        |                            |                            |                         |  |  |

|------------------------|-------|-----------------------|-------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|-------------------------|--|--|

| Standard               | Min   | Тур                   | Max   | Min                                                          | Тур                                                                                                                 | Max                                                                                                       | Min                        | Тур                        | Max                     |  |  |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                   | 2.625 | 1.19                                                         | 1.25                                                                                                                | 1.31                                                                                                      | V <sub>REF</sub> –<br>0.04 | V <sub>REF</sub>           | V <sub>REF</sub> + 0.04 |  |  |

| SSTL-18<br>Class I, II | 1.7   | 1.8                   | 1.9   | 0.833                                                        | 0.9                                                                                                                 | 0.969                                                                                                     | V <sub>REF</sub> –<br>0.04 | V <sub>REF</sub>           | V <sub>REF</sub> + 0.04 |  |  |

| HSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.85                                                         | 0.9                                                                                                                 | 0.95                                                                                                      | 0.85                       | 0.9                        | 0.95                    |  |  |

| HSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.71                                                         | 0.75                                                                                                                | 0.79                                                                                                      | 0.71                       | 0.75                       | 0.79                    |  |  |

| HSTL-12<br>Class I, II | 1.14  | 1.2                   | 1.26  | 0.48 x V <sub>CCI0</sub> (3)<br>0.47 x V <sub>CCI0</sub> (4) | $\begin{array}{c} 0.5 \mbox{ x } V_{\rm CC10} \ \ {}^{(3)} \\ 0.5 \mbox{ x } V_{\rm CC10} \ \ {}^{(4)} \end{array}$ | $\begin{array}{l} 0.52 \times V_{\rm CCI0} \ {}^{(3)} \\ 0.53 \times V_{\rm CCI0} \ {}^{(4)} \end{array}$ | _                          | 0.5 x<br>V <sub>CCIO</sub> | _                       |  |  |

#### Notes to Table 1–16:

(1) For an explanation of terms used in Table 1–16, refer to "Glossary" on page 1–37.

(2)  $\,\,V_{TT}$  of the transmitting device must track  $V_{REF}$  of the receiving device.

(3) Value shown refers to DC input reference voltage,  $V_{\text{REF(DC)}}.$

(4) Value shown refers to AC input reference voltage,  $V_{REF(AC)}$ .

| Table 1–17. | Single-Ended SSTL and HSTI | . I/O Standards Signal S | pecifications for C | yclone IV Devices |

|-------------|----------------------------|--------------------------|---------------------|-------------------|

|-------------|----------------------------|--------------------------|---------------------|-------------------|

| I/O                 | VIL   | <sub>(DC)</sub> (V)         | VIII                        | I(DC) (V)                | VIL   | <sub>AC)</sub> (V)         | VIH                        | <sub>(AC)</sub> (V)         | V <sub>ol</sub> (V)         | V <sub>oh</sub> (V)         | I <sub>OL</sub> | I <sub>oh</sub> |

|---------------------|-------|-----------------------------|-----------------------------|--------------------------|-------|----------------------------|----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------|-----------------|

| Standard            | Min   | Max                         | Min                         | Max                      | Min   | Max                        | Max Min                    |                             | Max                         | Min                         | (mĀ)            | (mÅ)            |

| SSTL-2<br>Class I   | _     | V <sub>REF</sub> –<br>0.18  | V <sub>REF</sub> +<br>0.18  | _                        |       | V <sub>REF</sub> –<br>0.35 | V <sub>REF</sub> +<br>0.35 | _                           | V <sub>Π</sub> –<br>0.57    | V <sub>TT</sub> +<br>0.57   | 8.1             | -8.1            |

| SSTL-2<br>Class II  | _     | V <sub>REF</sub> –<br>0.18  | V <sub>REF</sub> +<br>0.18  | _                        | _     | V <sub>REF</sub> –<br>0.35 | V <sub>REF</sub> + 0.35    | _                           | V <sub>Π</sub> –<br>0.76    | V <sub>TT</sub> +<br>0.76   | 16.4            | -16.4           |

| SSTL-18<br>Class I  | _     | V <sub>REF</sub> –<br>0.125 | V <sub>REF</sub> +<br>0.125 | —                        | _     | V <sub>REF</sub> –<br>0.25 | V <sub>REF</sub> +<br>0.25 | _                           | V <sub>TT</sub> –<br>0.475  | V <sub>TT</sub> +<br>0.475  | 6.7             | -6.7            |

| SSTL-18<br>Class II | _     | V <sub>REF</sub> –<br>0.125 | V <sub>REF</sub> +<br>0.125 | —                        | _     | V <sub>REF</sub> –<br>0.25 | V <sub>REF</sub> +<br>0.25 | _                           | 0.28                        | V <sub>CCI0</sub> –<br>0.28 | 13.4            | -13.4           |

| HSTL-18<br>Class I  | _     | V <sub>REF</sub> –<br>0.1   | V <sub>REF</sub> + 0.1      | —                        | _     | V <sub>REF</sub> –<br>0.2  | V <sub>REF</sub> + 0.2     | _                           | 0.4                         | V <sub>CCI0</sub> –<br>0.4  | 8               | -8              |

| HSTL-18<br>Class II | _     | V <sub>REF</sub> –<br>0.1   | V <sub>REF</sub> + 0.1      | —                        | _     | V <sub>REF</sub> –<br>0.2  | V <sub>REF</sub> + 0.2     | _                           | 0.4                         | V <sub>CCIO</sub> –<br>0.4  | 16              | -16             |

| HSTL-15<br>Class I  | _     | V <sub>REF</sub> –<br>0.1   | V <sub>REF</sub> +<br>0.1   | _                        | _     | V <sub>REF</sub> –<br>0.2  | V <sub>REF</sub> + 0.2     | _                           | 0.4                         | V <sub>CCIO</sub> –<br>0.4  | 8               | -8              |

| HSTL-15<br>Class II | _     | V <sub>REF</sub> –<br>0.1   | V <sub>REF</sub> + 0.1      | —                        | _     | V <sub>REF</sub> –<br>0.2  | V <sub>REF</sub> + 0.2     | _                           | 0.4                         | V <sub>CCIO</sub> –<br>0.4  | 16              | -16             |

| HSTL-12<br>Class I  | -0.15 | V <sub>REF</sub> –<br>0.08  | V <sub>REF</sub> +<br>0.08  | V <sub>CCI0</sub> + 0.15 | -0.24 | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> +<br>0.15 | V <sub>CCI0</sub> + 0.24    | 0.25 ×<br>V <sub>CCI0</sub> | 0.75 ×<br>V <sub>CCI0</sub> | 8               | -8              |

| HSTL-12<br>Class II | -0.15 | V <sub>REF</sub> -<br>0.08  | V <sub>REF</sub> +<br>0.08  | V <sub>CCI0</sub> + 0.15 | -0.24 | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> +<br>0.15 | V <sub>CCI0</sub> +<br>0.24 | 0.25 ×<br>V <sub>CCI0</sub> | 0.75 ×<br>V <sub>CCIO</sub> | 14              | -14             |

| Device    |     |       |     | Perfor             | mance                     |       |                           |    |        |

|-----------|-----|-------|-----|--------------------|---------------------------|-------|---------------------------|----|--------|

| Device    | C6  | C7    | C8  | C8L <sup>(1)</sup> | <b>C9L</b> <sup>(1)</sup> | 17    | <b>18L</b> <sup>(1)</sup> | A7 | – Unit |

| EP4CE55   | 500 | 437.5 | 402 | 362                | 265                       | 437.5 | 362                       | —  | MHz    |

| EP4CE75   | 500 | 437.5 | 402 | 362                | 265                       | 437.5 | 362                       | —  | MHz    |

| EP4CE115  | _   | 437.5 | 402 | 362                | 265                       | 437.5 | 362                       | —  | MHz    |

| EP4CGX15  | 500 | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |

| EP4CGX22  | 500 | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |

| EP4CGX30  | 500 | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |

| EP4CGX50  | 500 | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |

| EP4CGX75  | 500 | 437.5 | 402 | _                  | —                         | 437.5 | _                         | —  | MHz    |

| EP4CGX110 | 500 | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |

| EP4CGX150 | 500 | 437.5 | 402 | —                  | —                         | 437.5 | —                         | —  | MHz    |

Table 1–24. Clock Tree Performance for Cyclone IV Devices (Part 2 of 2)

#### Note to Table 1-24:

(1) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades.

### **PLL Specifications**

Table 1–25 lists the PLL specifications for Cyclone IV devices when operating in the commercial junction temperature range (0°C to 85°C), the industrial junction temperature range (–40°C to 100°C), the extended industrial junction temperature range (–40°C to 125°C), and the automotive junction temperature range (–40°C to 125°C). For more information about the PLL block, refer to "Glossary" on page 1–37.

Table 1–25. PLL Specifications for Cyclone IV Devices <sup>(1), (2)</sup> (Part 1 of 2)

| Symbol                                                                                   | Parameter                                                          | Min | Тур | Max   | Unit |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|-------|------|

|                                                                                          | Input clock frequency (-6, -7, -8 speed grades)                    | 5   | —   | 472.5 | MHz  |

| f <sub>IN</sub> <i>(3)</i>                                                               | Input clock frequency (–8L speed grade)                            | 5   |     | 362   | MHz  |

|                                                                                          | Input clock frequency (–9L speed grade)                            | 5   |     | 265   | MHz  |

| f <sub>INPFD</sub>                                                                       | PFD input frequency                                                | 5   |     | 325   | MHz  |

| f <sub>VCO</sub> (4)                                                                     | PLL internal VCO operating range                                   | 600 | —   | 1300  | MHz  |

| f <sub>INDUTY</sub>                                                                      | Input clock duty cycle                                             | 40  |     | 60    | %    |

| t <sub>injitter CCJ</sub> (5)                                                            | Input clock cycle-to-cycle jitter<br>$F_{REF} \ge 100 \text{ MHz}$ |     | _   | 0.15  | UI   |

| INJITTER_CCJ <i>(5)</i><br>OUT_EXT (external clock                                       | F <sub>REF</sub> < 100 MHz                                         | _   |     | ±750  | ps   |

| f <sub>OUT_EXT</sub> (external clock output) <sup>(3)</sup>                              | PLL output frequency                                               | _   | _   | 472.5 | MHz  |

|                                                                                          | PLL output frequency (-6 speed grade)                              |     |     | 472.5 | MHz  |

|                                                                                          | PLL output frequency (-7 speed grade)                              | _   |     | 450   | MHz  |

| f <sub>OUT</sub> (to global clock)                                                       | PLL output frequency (-8 speed grade)                              | _   |     | 402.5 | MHz  |

|                                                                                          | PLL output frequency (-8L speed grade)                             | _   |     | 362   | MHz  |

| INPFD<br>VCO (4)<br>INDUTY<br>INJITTER_CCJ (5)<br>OUT_EXT (external clock<br>Dutput) (3) | PLL output frequency (-9L speed grade)                             | _   |     | 265   | MHz  |

| t <sub>outduty</sub>                                                                     | Duty cycle for external clock output (when set to 50%)             | 45  | 50  | 55    | %    |

| t <sub>LOCK</sub>                                                                        | Time required to lock from end of device configuration             | —   | —   | 1     | ms   |

Table 1–29 lists the active configuration mode specifications for Cyclone IV devices.

| Programming Mode                    | DCLK Range | Typical DCLK | Unit |

|-------------------------------------|------------|--------------|------|

| Active Parallel (AP) <sup>(1)</sup> | 20 to 40   | 33           | MHz  |

| Active Serial (AS)                  | 20 to 40   | 33           | MHz  |

Table 1–29. Active Configuration Mode Specifications for Cyclone IV Devices

#### Note to Table 1-29:

(1) AP configuration mode is only supported for Cyclone IV E devices.

Table 1-30 lists the JTAG timing parameters and values for Cyclone IV devices.

Table 1–30. JTAG Timing Parameters for Cyclone IV Devices (1)

| Symbol                | Parameter                                                    | Min | Max | Unit |

|-----------------------|--------------------------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>      | TCK clock period                                             | 40  | —   | ns   |

| t <sub>JCH</sub>      | TCK clock high time                                          | 19  | _   | ns   |

| t <sub>JCL</sub>      | TCK clock low time                                           | 19  | _   | ns   |

| t <sub>JPSU_TDI</sub> | JTAG port setup time for TDI                                 | 1   | _   | ns   |

| t <sub>JPSU_TMS</sub> | JTAG port setup time for TMS                                 | 3   | _   | ns   |

| t <sub>JPH</sub>      | JTAG port hold time                                          | 10  | _   | ns   |

| t <sub>JPC0</sub>     | JTAG port clock to output <sup>(2), (3)</sup>                |     | 15  | ns   |

| t <sub>JPZX</sub>     | JTAG port high impedance to valid output <sup>(2), (3)</sup> | —   | 15  | ns   |

| t <sub>JPXZ</sub>     | JTAG port valid output to high impedance $(2)$ , $(3)$       | —   | 15  | ns   |

| t <sub>JSSU</sub>     | Capture register setup time                                  | 5   | _   | ns   |

| t <sub>JSH</sub>      | Capture register hold time                                   | 10  | _   | ns   |

| t <sub>JSC0</sub>     | Update register clock to output                              |     | 25  | ns   |

| t <sub>JSZX</sub>     | Update register high impedance to valid output               |     | 25  | ns   |

| t <sub>JSXZ</sub>     | Update register valid output to high impedance               |     | 25  | ns   |

#### Notes to Table 1-30:

(1) For more information about JTAG waveforms, refer to "JTAG Waveform" in "Glossary" on page 1-37.

- (2) The specification is shown for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 16 ns.

- (3) For EP4CGX22, EP4CGX30 (F324 and smaller package), EP4CGX110, and EP4CGX150 devices, the output time specification for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins is 16 ns. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 18 ns.

### **Periphery Performance**

This section describes periphery performance, including high-speed I/O and external memory interface.

I/O performance supports several system interfaces, such as the high-speed I/O interface, external memory interface, and the PCI/PCI-X bus interface. I/Os using the SSTL-18 Class I termination standard can achieve up to the stated DDR2 SDRAM interfacing speeds. I/Os using general-purpose I/O standards such as 3.3-, 3.0-, 2.5-, 1.8-, or 1.5-LVTTL/LVCMOS are capable of a typical 200 MHz interfacing frequency with a 10 pF load.

- **\*** For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to *Section III: System Performance Specifications* of the *External Memory Interfaces Handbook*.

- Actual achievable frequency depends on design- and system-specific factors. Perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

### **High-Speed I/O Specifications**

Table 1–31 through Table 1–36 list the high-speed I/O timing for Cyclone IV devices. For definitions of high-speed timing specifications, refer to "Glossary" on page 1–37.

Table 1–31. RSDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4) (Part 1 of 2)

| 0 milest                                             |                                          |     | C6  |     |     | C7, I | 7     |     | C8, A | 7     |     | C8L, I | 8L    |     | Unit |       |      |

|------------------------------------------------------|------------------------------------------|-----|-----|-----|-----|-------|-------|-----|-------|-------|-----|--------|-------|-----|------|-------|------|

| Symbol                                               | Modes                                    | Min | Тур | Max | Min | Тур   | Max   | Min | Тур   | Max   | Min | Тур    | Max   | Min | Тур  | Max   | Unit |

|                                                      | ×10                                      | 5   |     | 180 | 5   |       | 155.5 | 5   |       | 155.5 | 5   |        | 155.5 | 5   |      | 132.5 | MHz  |

|                                                      | ×8                                       | 5   |     | 180 | 5   | —     | 155.5 | 5   |       | 155.5 | 5   |        | 155.5 | 5   | —    | 132.5 | MHz  |

| f <sub>HSCLK</sub><br>(input clock                   | ×7                                       | 5   |     | 180 | 5   |       | 155.5 | 5   |       | 155.5 | 5   |        | 155.5 | 5   |      | 132.5 | MHz  |

| (input clock frequency)                              | ×4                                       | 5   |     | 180 | 5   |       | 155.5 | 5   | _     | 155.5 | 5   |        | 155.5 | 5   |      | 132.5 | MHz  |

| 1 37                                                 | ×2                                       | 5   |     | 180 | 5   |       | 155.5 | 5   |       | 155.5 | 5   |        | 155.5 | 5   |      | 132.5 | MHz  |

|                                                      | ×1                                       | 5   |     | 360 | 5   |       | 311   | 5   | _     | 311   | 5   |        | 311   | 5   |      | 265   | MHz  |

|                                                      | ×10                                      | 100 |     | 360 | 100 |       | 311   | 100 | _     | 311   | 100 |        | 311   | 100 |      | 265   | Mbps |

| Device<br>operation in<br>Mbps                       | ×8                                       | 80  |     | 360 | 80  |       | 311   | 80  |       | 311   | 80  |        | 311   | 80  |      | 265   | Mbps |

|                                                      | ×7                                       | 70  | —   | 360 | 70  | —     | 311   | 70  |       | 311   | 70  | —      | 311   | 70  | —    | 265   | Mbps |

|                                                      | ×4                                       | 40  | —   | 360 | 40  | —     | 311   | 40  |       | 311   | 40  | —      | 311   | 40  | —    | 265   | Mbps |

|                                                      | ×2                                       | 20  |     | 360 | 20  |       | 311   | 20  | _     | 311   | 20  | —      | 311   | 20  | —    | 265   | Mbps |

|                                                      | ×1                                       | 10  | —   | 360 | 10  | —     | 311   | 10  |       | 311   | 10  | —      | 311   | 10  | —    | 265   | Mbps |

| t <sub>DUTY</sub>                                    | —                                        | 45  |     | 55  | 45  |       | 55    | 45  |       | 55    | 45  |        | 55    | 45  |      | 55    | %    |

| Transmitter<br>channel-to-<br>channel skew<br>(TCCS) | _                                        | _   | _   | 200 | _   | _     | 200   | _   | _     | 200   | _   | _      | 200   | _   | _    | 200   | ps   |

| Output jitter<br>(peak to peak)                      | _                                        | _   | _   | 500 | _   | _     | 500   | _   |       | 550   | _   | _      | 600   | _   | _    | 700   | ps   |

| t <sub>RISE</sub>                                    | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _   | 500   | _     | _   | 500   | _     | _   | 500    | _     | _   | 500  | _     | ps   |

| t <sub>FALL</sub>                                    | 20 – 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _   | 500   | _     | _   | 500   | _     | _   | 500    |       | _   | 500  |       | ps   |

| Symbol                       | Modes  | C6  |     |     | C7, I7 |     |     | C8, A7 |     |     | C8L, I8L |     |     | C9L |     |     | Unit |

|------------------------------|--------|-----|-----|-----|--------|-----|-----|--------|-----|-----|----------|-----|-----|-----|-----|-----|------|

|                              | WUUUUS | Min | Тур | Max | Min    | Тур | Max | Min    | Тур | Max | Min      | Тур | Max | Min | Тур | Max | Unit |

| t <sub>LOCK</sub> <i>(2)</i> |        |     |     | 1   |        |     | 1   | _      |     | 1   |          | _   | 1   |     |     | 1   | ms   |

#### Table 1–32. Emulated RSDS\_E\_1R Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

Notes to Table 1-32:

(1) Emulated RSDS\_E\_1R transmitter is supported at the output pin of all I/O Banks of Cyclone IV E devices and I/O Banks 3, 4, 5, 6, 7, 8, and 9 of Cyclone IV GX devices.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                                           | Modes                                    | C6  |     |     | C7, I7 |     |       | C8, A7 |     |       | C8L, 18L |     |       | C9L |     |       |      |

|--------------------------------------------------|------------------------------------------|-----|-----|-----|--------|-----|-------|--------|-----|-------|----------|-----|-------|-----|-----|-------|------|

|                                                  |                                          | Min | Тур | Max | Min    | Тур | Max   | Min    | Тур | Max   | Min      | Тур | Max   | Min | Тур | Max   | Unit |

| f <sub>HSCLK</sub> (input<br>clock<br>frequency) | ×10                                      | 5   |     | 200 | 5      |     | 155.5 | 5      |     | 155.5 | 5        | —   | 155.5 | 5   |     | 132.5 | MHz  |

|                                                  | ×8                                       | 5   |     | 200 | 5      | —   | 155.5 | 5      | —   | 155.5 | 5        | —   | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×7                                       | 5   | _   | 200 | 5      | _   | 155.5 | 5      | _   | 155.5 | 5        | —   | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×4                                       | 5   |     | 200 | 5      | _   | 155.5 | 5      | _   | 155.5 | 5        | —   | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×2                                       | 5   |     | 200 | 5      | —   | 155.5 | 5      | —   | 155.5 | 5        | —   | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×1                                       | 5   | _   | 400 | 5      | _   | 311   | 5      | _   | 311   | 5        | —   | 311   | 5   | _   | 265   | MHz  |

| Device<br>operation in<br>Mbps                   | ×10                                      | 100 |     | 400 | 100    |     | 311   | 100    |     | 311   | 100      | _   | 311   | 100 |     | 265   | Mbps |

|                                                  | ×8                                       | 80  |     | 400 | 80     | _   | 311   | 80     | —   | 311   | 80       | —   | 311   | 80  | _   | 265   | Mbps |

|                                                  | ×7                                       | 70  | _   | 400 | 70     | _   | 311   | 70     | _   | 311   | 70       | —   | 311   | 70  | _   | 265   | Mbps |

|                                                  | ×4                                       | 40  |     | 400 | 40     |     | 311   | 40     |     | 311   | 40       | _   | 311   | 40  |     | 265   | Mbps |

|                                                  | ×2                                       | 20  |     | 400 | 20     | _   | 311   | 20     | —   | 311   | 20       | —   | 311   | 20  | _   | 265   | Mbps |

|                                                  | ×1                                       | 10  |     | 400 | 10     | _   | 311   | 10     | —   | 311   | 10       | —   | 311   | 10  | _   | 265   | Mbps |

| t <sub>DUTY</sub>                                | —                                        | 45  |     | 55  | 45     |     | 55    | 45     |     | 55    | 45       | _   | 55    | 45  |     | 55    | %    |

| TCCS                                             | —                                        | —   |     | 200 | —      | _   | 200   | _      | —   | 200   | —        | —   | 200   | —   | _   | 200   | ps   |

| Output jitter<br>(peak to peak)                  | —                                        | _   | _   | 500 | _      | _   | 500   | _      | _   | 550   | _        | _   | 600   | _   | _   | 700   | ps   |

| t <sub>RISE</sub>                                | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _      | 500 |       |        | 500 | _     | _        | 500 | _     | _   | 500 |       | ps   |

| t <sub>FALL</sub>                                | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _      | 500 | _     |        | 500 | _     | _        | 500 |       | _   | 500 | _     | ps   |

| t <sub>LOCK</sub> (3)                            | —                                        | —   | —   | 1   | —      | —   | 1     |        | —   | 1     | —        | _   | 1     | —   | —   | 1     | ms   |

Table 1–33. Mini-LVDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4)

Notes to Table 1-33:

(1) Applicable for true and emulated mini-LVDS transmitter.

(2) Cyclone IV E—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 1, 2, 5, and 6. Emulated mini-LVDS transmitter is supported at the output pin of all I/O banks.

Cyclone IV GY—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5.

Cyclone IV GX—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(3)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(4) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.