### Intel - EP4CE22F17I8L Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 1395                                                     |

| Number of Logic Elements/Cells | 22320                                                    |

| Total RAM Bits                 | 608256                                                   |

| Number of I/O                  | 153                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 256-LBGA                                                 |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce22f17i8l |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Differential HSTL I/O Standard Support in Cyclone IV Devices | 6–35 |

|--------------------------------------------------------------|------|

| True Differential Output Buffer Feature                      |      |

| Programmable Pre-Emphasis                                    | 6–35 |

| High-Speed I/O Timing                                        |      |

| Design Guidelines                                            |      |

| Differential Pad Placement Guidelines                        | 6–37 |

| Board Design Considerations                                  |      |

| Software Overview                                            |      |

| Document Revision History                                    |      |

|                                                              |      |

## **Chapter 7. External Memory Interfaces in Cyclone IV Devices**

| Cyclone IV Devices Memory Interfaces Pin Support      | 7–2  |

|-------------------------------------------------------|------|

| Data and Data Clock/Strobe Pins                       | 7–2  |

| Optional Parity, DM, and Error Correction Coding Pins | 7–11 |

| Address and Control/Command Pins                      | 7–12 |

| Memory Clock Pins                                     | 7–12 |

| Cyclone IV Devices Memory Interfaces Features         | 7–12 |

| DDR Input Registers                                   | 7–12 |

| DDR Output Registers                                  | 7–14 |

| OCT with Calibration                                  | 7–15 |

| PLL                                                   | 7–15 |

| Document Revision History                             | 7–16 |

## Section III. System Integration

## Chapter 8. Configuration and Remote System Upgrades in Cyclone IV Devices

| Configuration                                                                          |                 |

|----------------------------------------------------------------------------------------|-----------------|

| Configuration Features                                                                 | 8–2             |

| Configuration Data Decompression                                                       | 8–2             |

| Configuration Requirement                                                              | 8–3             |

| Power-On Reset (POR) Circuit                                                           |                 |

| Configuration File Size                                                                | 8–4             |

| Configuration and JTAG Pin I/O Requirements                                            | 8–5             |

| Configuration Process                                                                  | 8–6             |

| Power Up                                                                               |                 |

| Reset                                                                                  | 8–6             |

| Configuration                                                                          | 8–6             |

| Configuration Error                                                                    | 8–7             |

| Initialization                                                                         | 8–7             |

| User Mode                                                                              | 8–7             |

| Configuration Scheme                                                                   | 8–8             |

| AS Configuration (Serial Configuration Devices)                                        | 8–10            |

| Single-Device AS Configuration                                                         | 8–10            |

| Multi-Device AS Configuration                                                          | 8–13            |

| Configuring Multiple Cyclone IV Devices with the Same Design                           | 8–14            |

| Guidelines for Connecting a Serial Configuration Device to Cyclone IV Devices for 8–18 | an AS Interface |

| Programming Serial Configuration Devices                                               | 8–19            |

| AP Configuration (Supported Flash Memories)                                            |                 |

| AP Configuration Supported Flash Memories                                              |                 |

| Single-Device AP Configuration                                                         |                 |

| Multi-Device AP Configuration                                                          |                 |

| Byte-Wide Multi-Device AP Configuration                                                |                 |

|                                                                                        |                 |

- Cyclone IV GX devices offer up to eight high-speed transceivers that provide:

- Data rates up to 3.125 Gbps

- 8B/10B encoder/decoder

- 8-bit or 10-bit physical media attachment (PMA) to physical coding sublayer (PCS) interface

- Byte serializer / deserializer (SERDES)

- Word aligner

- Rate matching FIFO

- TX bit slipper for Common Public Radio Interface (CPRI)

- Electrical idle

- Dynamic channel reconfiguration allowing you to change data rates and protocols on-the-fly

- Static equalization and pre-emphasis for superior signal integrity

- 150 mW per channel power consumption

- Flexible clocking structure to support multiple protocols in a single transceiver block

- Cyclone IV GX devices offer dedicated hard IP for PCI Express (PIPE) (PCIe) Gen 1:

- ×1, ×2, and ×4 lane configurations

- End-point and root-port configurations

- Up to 256-byte payload

- One virtual channel

- 2 KB retry buffer

- 4 KB receiver (Rx) buffer

- Cyclone IV GX devices offer a wide range of protocol support:

- PCIe (PIPE) Gen 1 ×1, ×2, and ×4 (2.5 Gbps)

- Gigabit Ethernet (1.25 Gbps)

- CPRI (up to 3.072 Gbps)

- XAUI (3.125 Gbps)

- Triple rate serial digital interface (SDI) (up to 2.97 Gbps)

- Serial RapidIO (3.125 Gbps)

- Basic mode (up to 3.125 Gbps)

- V-by-One (up to 3.0 Gbps)

- DisplayPort (2.7 Gbps)

- Serial Advanced Technology Attachment (SATA) (up to 3.0 Gbps)

- OBSAI (up to 3.072 Gbps)

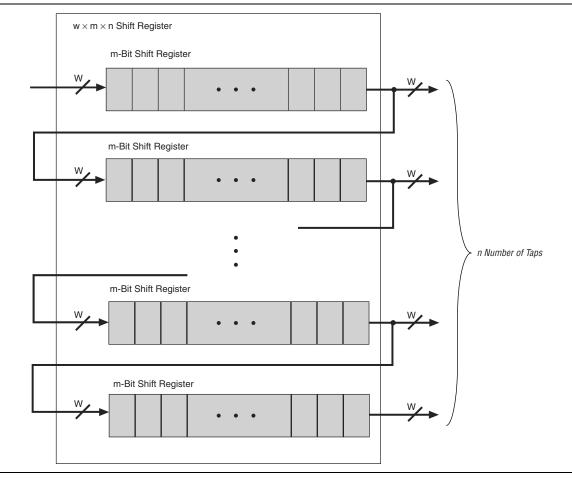

Figure 3–12 shows the Cyclone IV devices M9K memory block in shift register mode.

## **ROM Mode**

Cyclone IV devices M9K memory blocks support ROM mode. A **.mif** initializes the ROM contents of these blocks. The address lines of the ROM are registered. The outputs can be registered or unregistered. The ROM read operation is identical to the read operation in the single-port RAM configuration.

## **FIFO Buffer Mode**

Cyclone IV devices M9K memory blocks support single-clock or dual-clock FIFO buffers. Dual clock FIFO buffers are useful when transferring data from one clock domain to another clock domain. Cyclone IV devices M9K memory blocks do not support simultaneous read and write from an empty FIFO buffer.

**\*** For more information about FIFO buffers, refer to the *Single- and Dual-Clock FIFO Megafunction User Guide.*

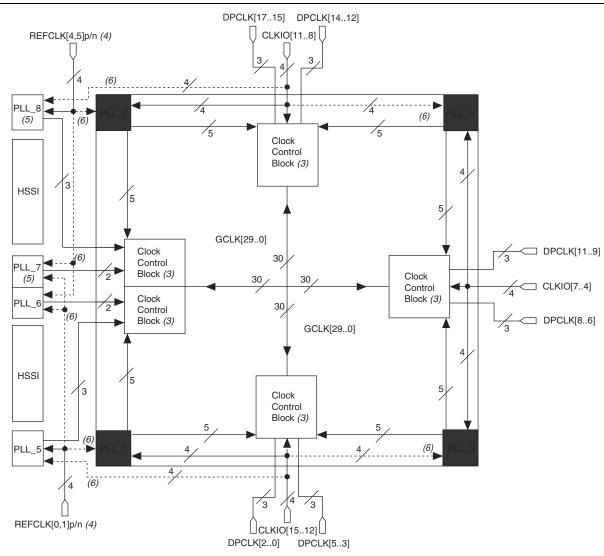

# Figure 5–3. Clock Networks and Clock Control Block Locations in EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices <sup>(1), (2)</sup>

### Notes to Figure 5-3:

- (1) The clock networks and clock control block locations in this figure apply to only the EP4CGX30 device in F484 package and all EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices.

- (2) PLL\_1, PLL\_2, PLL\_3, and PLL\_4 are general purpose PLLs while PLL\_5, PLL\_6, PLL\_7, and PLL\_8 are multipurpose PLLs.

- (3) There are 6 clock control blocks on the top, right and bottom sides of the device and 12 clock control blocks on the left side of the device.

- (4) REFCLK[0,1]p/n and REFCLK[4,5]p/n can only drive the general purpose PLLs and multipurpose PLLs on the left side of the device. These clock pins do not have access to the clock control blocks and GCLK networks. The REFCLK[4,5]p/n pins are not available in devices in F484 package.

- (5) Not available for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

- (6) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

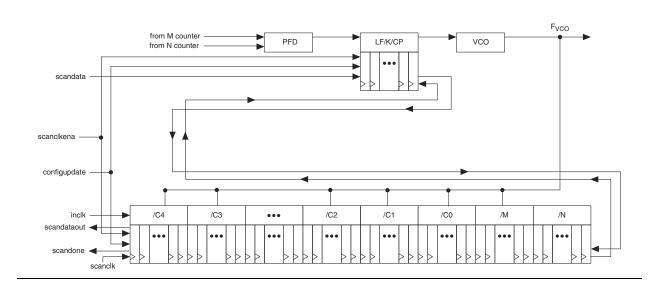

# **PLL Reconfiguration**

PLLs use several divide counters and different VCO phase taps to perform frequency synthesis and phase shifts. In PLLs of Cyclone IV devices, you can reconfigure both counter settings and phase shift the PLL output clock in real time. You can also change the charge pump and loop filter components, which dynamically affects PLL bandwidth. You can use these PLL components to update the output clock frequency, PLL bandwidth, and phase shift in real time, without reconfiguring the entire FPGA.

The ability to reconfigure the PLL in real time is useful in applications that might operate at multiple frequencies. It is also useful in prototyping environments, allowing you to sweep PLL output frequencies and adjust the output clock phase dynamically. For instance, a system generating test patterns is required to generate and send patterns at 75 or 150 MHz, depending on the requirements of the device under test. Reconfiguring PLL components in real time allows you to switch between two such output frequencies in a few microseconds.

You can also use this feature to adjust clock-to-out ( $t_{CO}$ ) delays in real time by changing the PLL output clock phase shift. This approach eliminates the need to regenerate a configuration file with the new PLL settings.

# **PLL Reconfiguration Hardware Implementation**

The following PLL components are configurable in real time:

- Pre-scale counter (N)

- Feedback counter (M)

- Post-scale output counters (C0-C4)

- Dynamically adjust the charge pump current (I<sub>CP</sub>) and loop filter components (R, C) to facilitate on-the-fly reconfiguration of the PLL bandwidth

Figure 5–22 shows how to adjust PLL counter settings dynamically by shifting their new settings into a serial shift register chain or scan chain. Serial data shifts to the scan chain via the scandataport, and shift registers are clocked by scanclk. The maximum scanclk frequency is 100 MHz. After shifting the last bit of data, asserting the configupdate signal for at least one scanclk clock cycle synchronously updates the PLL configuration bits with the data in the scan registers.

The counter settings are updated synchronously to the clock frequency of the individual counters. Therefore, not all counters update simultaneously.

To reconfigure the PLL counters, perform the following steps:

- 1. The scanclkena signal is asserted at least one scanclk cycle prior to shifting in the first bit of scandata (D0).

- 2. Serial data (scandata) is shifted into the scan chain on the second rising edge of scanclk.

- 3. After all 144 bits have been scanned into the scan chain, the scanclkena signal is de-asserted to prevent inadvertent shifting of bits in the scan chain.

- 4. The configupdate signal is asserted for one scanclk cycle to update the PLL counters with the contents of the scan chain.

- 5. The scandone signal goes high indicating that the PLL is being reconfigured. A falling edge indicates that the PLL counters have been updated with new settings.

- 6. Reset the PLL using the areset signal if you make any changes to the M, N, post-scale output C counters, or the I<sub>CP</sub>, R, C settings.

- 7. You can repeat steps 1 through 5 to reconfigure the PLL any number of times.

| Table 6–3. Cyclone IV                       |                        |                      |                           |           |              |              |                             |              |                  |  |  |  |

|---------------------------------------------|------------------------|----------------------|---------------------------|-----------|--------------|--------------|-----------------------------|--------------|------------------|--|--|--|

|                                             |                        |                      | V <sub>CCIO</sub> Leve    | el (in V) | 0            | column I/O P | Row I/O Pins <sup>(1)</sup> |              |                  |  |  |  |

| I/O Standard                                | Туре                   | Standard<br>Support  | Input                     | Output    | CLK,<br>DQS  | PLL_OUT      | User<br>I/O<br>Pins         | CLK,<br>DQS  | User I/O<br>Pins |  |  |  |

| 2.5-V LVTTL /<br>LVCMOS                     | Single-ended           | JESD8-5              | 3.3/3.0/2.5<br><i>(3)</i> | 2.5       | ~            | ~            | $\checkmark$                | ~            | ~                |  |  |  |

| 1.8-V LVTTL /<br>LVCMOS                     | Single-ended           | JESD8-7              | 1.8/1.5 <sup>(3)</sup>    | 1.8       | ~            | ~            | $\checkmark$                | ~            | ~                |  |  |  |

| 1.5-V LVCMOS                                | Single-ended           | JESD8-11             | 1.8/1.5 <sup>(3)</sup>    | 1.5       | $\checkmark$ | $\checkmark$ | $\checkmark$                | $\checkmark$ | $\checkmark$     |  |  |  |

| 1.2-V LVCMOS (4)                            | Single-ended           | JESD8-12A            | 1.2                       | 1.2       | $\checkmark$ | $\checkmark$ | $\checkmark$                | $\checkmark$ | $\checkmark$     |  |  |  |

| SSTL-2 Class I,<br>SSTL-2 Class II          | voltage-<br>referenced | JESD8-9A             | 2.5                       | 2.5       | ~            | ~            | $\checkmark$                | ~            | ~                |  |  |  |

| SSTL-18 Class I,<br>SSTL-18 Class II        | voltage-<br>referenced | JESD815              | 1.8                       | 1.8       | ~            | ~            | $\checkmark$                | ~            | ~                |  |  |  |

| HSTL-18 Class I,<br>HSTL-18 Class II        | voltage-<br>referenced | JESD8-6              | 1.8                       | 1.8       | ~            | ~            | $\checkmark$                | ~            | ~                |  |  |  |

| HSTL-15 Class I,<br>HSTL-15 Class II        | voltage-<br>referenced | JESD8-6              | 1.5                       | 1.5       | ~            | ~            | $\checkmark$                | ~            | ~                |  |  |  |

| HSTL-12 Class I                             | voltage-<br>referenced | JESD8-16A            | 1.2                       | 1.2       | ~            | ~            | $\checkmark$                | ~            | ~                |  |  |  |

| HSTL-12 Class II <sup>(9)</sup>             | voltage-<br>referenced | JESD8-16A            | 1.2                       | 1.2       | ~            | ~            | $\checkmark$                | _            | —                |  |  |  |

| PCI and PCI-X                               | Single-ended           | —                    | 3.0                       | 3.0       | $\checkmark$ | $\checkmark$ | $\checkmark$                | $\checkmark$ | $\checkmark$     |  |  |  |

| Differential SSTL-2<br>Class I or Class II  | Differential<br>(5)    | JESD8-9A             | <br>2.5                   | 2.5       | -<br>✓       | ✓<br>_       |                             | -<br>✓       |                  |  |  |  |

| Differential SSTL-18                        | Differential           |                      |                           | 1.8       | •<br>—       | ~            |                             | · -          |                  |  |  |  |

| Class I or Class II                         | (5)                    | JESD815              | 1.8                       |           | ~            |              |                             | ~            |                  |  |  |  |

| Differential HSTL-18                        | Differential           | 15050.0              | _                         | 1.8       | _            | ~            |                             | _            |                  |  |  |  |

| Class I or Class II                         | (5)                    | JESD8-6              | 1.8                       |           | ~            | —            | _                           | ~            |                  |  |  |  |

| Differential HSTL-15                        | Differential           |                      |                           | 1.5       | —            | ~            |                             | —            |                  |  |  |  |

| Class I or Class II                         | (5)                    | JESD8-6              | 1.5                       | —         | $\checkmark$ | —            |                             | $\checkmark$ | —                |  |  |  |

| Differential HSTL-12<br>Class I or Class II | Differential (5)       | JESD8-16A            | <br>1.2                   | 1.2       | -<br>~       | ✓<br>_       |                             | -<br>~       |                  |  |  |  |

| PPDS (6)                                    | Differential           |                      |                           | 2.5       | •<br>—       | ~            | $\checkmark$                | · -          | ~                |  |  |  |

| LVDS (10)                                   | Differential           | ANSI/TIA/<br>EIA-644 | 2.5                       | 2.5       | ~            | ~            | ~                           | ~            | ·<br>·           |  |  |  |

| RSDS and<br>mini-LVDS <sup>(6)</sup>        | Differential           | _                    | _                         | 2.5       | _            | ~            | ~                           | _            | ~                |  |  |  |

| BLVDS (8)                                   | Differential           | _                    | 2.5                       | 2.5       | —            | _            | $\checkmark$                | —            | ~                |  |  |  |

Table 6–3. Cyclone IV Devices Supported I/O Standards and Constraints (Part 2 of 3)

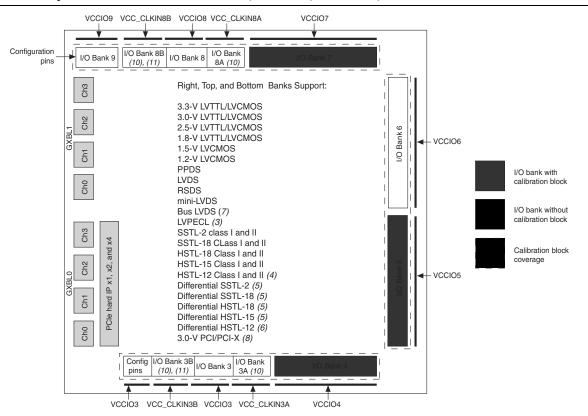

#### Figure 6–11. Cyclone IV GX I/O Banks for EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 <sup>(1), (2), (9)</sup>

#### Notes to Figure 6–11:

- (1) This is a top view of the silicon die. For exact pin locations, refer to the pin list and the Quartus II software.

- (2) True differential (PPDS, LVDS, mini-LVDS, and RSDS I/O standards) outputs are supported in row I/O banks 5 and 6 only. External resistors are needed for the differential outputs in column I/O banks.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The HSTL-12 Class II is supported in column I/O banks 4, 7, and 8.

- (5) The differential SSTL-18 and SSTL-2, differential HSTL-18, and HSTL-15 I/O standards are supported only on clock input pins and phase-locked loops (PLLs) output clock pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards.

- (6) The differential HSTL-12 I/O standard is only supported on clock input pins and PLL output clock pins. Differential HSTL-12 Class II is supported only in column I/O banks 4, 7, and 8.

- (7) BLVDS output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses the LVDS input buffer.

- (8) The PCI-X I/O standard does not meet the IV curve requirement at the linear region.

- (9) The OCT block is located in the shaded banks 4, 5, and 7.

- (10) The dedicated clock input I/O banks 3A, 3B, 8A, and 8B can be used either for HSSI input reference clock pins or clock input pins.

- (11) Single-ended clock input support is available for dedicated clock input I/O banks 3B and 8B.

## **External Memory Interfacing**

Cyclone IV devices support I/O standards required to interface with a broad range of external memory interfaces, such as DDR SDRAM, DDR2 SDRAM, and QDR II SRAM.

For more information about Cyclone IV devices external memory interface support, refer to the *External Memory Interfaces in Cyclone IV Devices* chapter.

# **Pad Placement and DC Guidelines**

You can use the Quartus II software to validate your pad and pin placement.

## **Pad Placement**

Altera recommends that you create a Quartus II design, enter your device I/O assignments and compile your design to validate your pin placement. The Quartus II software checks your pin connections with respect to the I/O assignment and placement rules to ensure proper device operation. These rules depend on device density, package, I/O assignments, voltage assignments and other factors that are not fully described in this chapter.

For more information about how the Quartus II software checks I/O restrictions, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

## **DC Guidelines**

For the Quartus II software to automatically check for illegally placed pads according to the DC guidelines, set the DC current sink or source value to **Electromigration Current** assignment on each of the output pins that are connected to the external resistive load.

The programmable current strength setting has an impact on the amount of DC current that an output pin can source or sink. Determine if the current strength setting is sufficient for the external resistive load condition on the output pin.

# **Clock Pins Functionality**

Cyclone IV clock pins have multiple purposes, as per listed:

- CLK pins—Input support for single-ended and voltage-referenced standards. For I/O standard support, refer to Table 6–3 on page 6–11.

- DIFFCLK pins—Input support for differential standards. For I/O standard support, refer to Table 6–3 on page 6–11. When used as DIFFCLK pins, DC or AC coupling can be used depending on the interface requirements and external termination is required. For more information, refer to "High-Speed I/O Standards Support" on page 6–28.

- REFCLK pins—Input support for high speed differential reference clocks used by the transceivers in Cyclone IV GX devices. For I/O support, coupling, and termination requirements, refer to Table 6–10 on page 6–29.

- 3. Click the **Configuration** tab.

- 4. Turn on Generate compressed bitstreams.

- 5. Click OK.

- 6. In the **Settings** dialog box, click **OK**.

You can enable compression when creating programming files from the **Convert Programming Files** dialog box. To enable compression, perform the following steps:

- 1. On the File menu, click Convert Programming Files.

- 2. Under **Output programming file**, select your desired file type from the **Programming file type** list.

- 3. If you select **Programmer Object File (.pof)**, you must specify the configuration device in the **Configuration device** list.

- 4. Under Input files to convert, select SOF Data.

- 5. Click Add File to browse to the Cyclone IV device SRAM object files (.sof).

- 6. In the **Convert Programming Files** dialog box, select the **.pof** you added to **SOF Data** and click **Properties**.

- 7. In the SOF File Properties dialog box, turn on the Compression option.

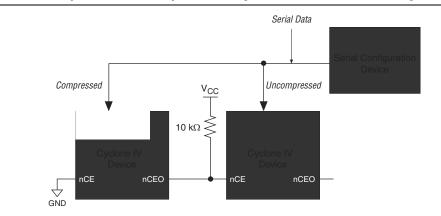

When multiple Cyclone IV devices are cascaded, you can selectively enable the compression feature for each device in the chain. Figure 8–1 shows a chain of two Cyclone IV devices. The first device has compression enabled and receives compressed bitstream from the configuration device. The second device has the compression feature disabled and receives uncompressed data. You can generate programming files for this setup in the **Convert Programming Files** dialog box.

Figure 8–1. Compressed and Uncompressed Configuration Data in the Same Configuration File

## **Configuration Requirement**

This section describes Cyclone IV device configuration requirement and includes the following topics:

- "Power-On Reset (POR) Circuit" on page 8–4

- "Configuration File Size" on page 8–4

- "Power Up" on page 8–6

# Table 8–4. Configuration Schemes for Cyclone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150) (Part 2 of 2)

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) $^{(1)}$ |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------|

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   | _         | _                                           |

### Notes to Table 8-4:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to  $V_{CCA}$  or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

> Smaller Cyclone IV E devices or package options (E144 and F256 packages) do not have the MSEL[3] pin. The AS Fast POR configuration scheme at 3.0- or 2.5-V configuration voltage standard and the AP configuration scheme are not supported in Cyclone IV E devices without the MSEL[3] pin. To configure these devices with other supported configuration schemes, select MSEL[2..0] pins according to the MSEL settings in Table 8–5.

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------------|

|                              | 1     | 1     | 0     | 1     | Fast      | 3.3                                               |

| AS                           | 0     | 1     | 0     | 0     | Fast      | 3.0, 2.5                                          |

|                              | 0     | 0     | 1     | 0     | Standard  | 3.3                                               |

|                              | 0     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 0     | 1     | 0     | 1     | Fast      | 3.3                                               |

|                              | 0     | 1     | 1     | 0     | Fast      | 1.8                                               |

| AP                           | 0     | 1     | 1     | 1     | Standard  | 3.3                                               |

|                              | 1     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 1     | 0     | 0     | 0     | Standard  | 1.8                                               |

| PS                           | 1     | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| 15                           | 0     | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                                     |

| FPP                          | 1     | 1     | 1     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| 111                          | 1     | 1     | 1     | 1     | Fast      | 1.8, 1.5                                          |

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   |           | _                                                 |

Table 8–5. Configuration Schemes for Cyclone IV E Devices

### Notes to Table 8-5:

(1) Configuration voltage standard applied to the V<sub>CCIO</sub> supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to V<sub>CCA</sub> or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

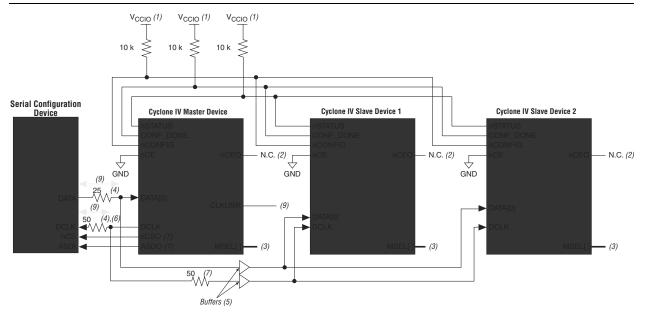

### **Single SRAM Object File**

The second method configures both the master device and slave devices with the same **.sof**. The serial configuration device stores one copy of the **.sof**. You must set up one or more slave devices in the chain. All the slave devices must be set up in the same way (Figure 8–5).

### Notes to Figure 8-5:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device of the Cyclone IV device in AS mode and the slave devices in PS mode. To connect the MSEL pins for the master device in AS mode and slave devices in PS mode, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) Connect the series resistor at the near end of the serial configuration device.

- (5) Connect the repeater buffers between the master and slave devices for DATA[0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (6) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

- (7) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (8) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- (9) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration device to the junction-split on both DCLK and Data0 line is 3.5 inches.

In this setup, all the Cyclone IV devices in the chain are connected for concurrent configuration. This reduces the AS configuration time because all the Cyclone IV devices are configured in one configuration cycle. Connect the nCE input pins of all the Cyclone IV devices to GND. You can either leave the nCEO output pins on all the Cyclone IV devices unconnected or use the nCEO output pins as normal user I/O pins. The DATA and DCLK pins are connected in parallel to all the Cyclone IV devices.

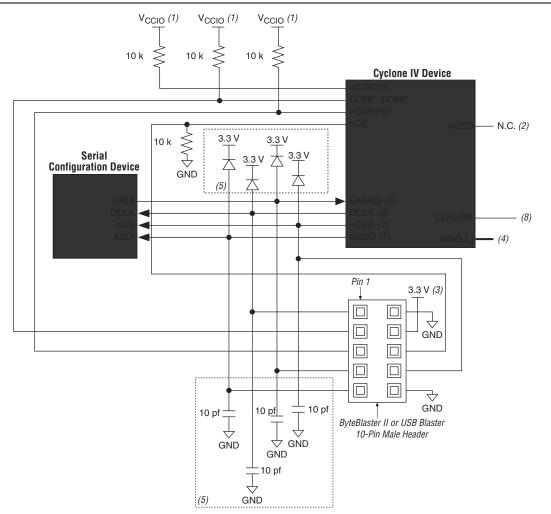

For more information about the USB-Blaster download cable, refer to the USB-Blaster *Download Cable User Guide*. For more information about the ByteBlaster II download cable, refer to the *ByteBlaster II Download Cable User Guide*.

Figure 8-6 shows the download cable connections to the serial configuration device.

### Notes to Figure 8-6:

- (1) Connect these pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (3) Power up the V<sub>CC</sub> of the ByteBlaster II or USB-Blaster download cable with the 3.3-V supply.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) The diodes and capacitors must be placed as close as possible to the Cyclone IV device. You must ensure that the diodes and capacitors maintain a maximum AC voltage of 4.1 V. The external diodes and capacitors are required to prevent damage to the Cyclone IV device AS configuration input pins due to possible overshoot when programming the serial configuration device with a download cable. Altera recommends using the Schottky diode, which has a relatively lower forward diode voltage (VF) than the switching and Zener diodes, for effective voltage clamping.

- (6) When cascading Cyclone IV devices in a multi-device AS configuration, connect the repeater buffers between the master and slave devices for DATA [0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (7) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (8) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

## **Remote System Upgrade Registers**

The remote system upgrade block contains a series of registers that stores the configuration addresses, watchdog timer settings, and status information. Table 8–22 lists these registers.

Table 8–22.

Remote System Upgrade Registers

| Register            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift<br>register   | This register is accessible by the logic array and allows the update, status, and control registers to be written<br>and sampled by user logic. Write access is enabled in remote update mode for factory configurations to allow<br>writing to the update register. Write access is disabled for all application configurations in remote update<br>mode.                                                                                                        |

| Control<br>register | This register contains the current configuration address, the user watchdog timer settings, one option bit for checking early CONF_DONE, and one option bit for selecting the internal oscillator as the startup state machine clock. During a read operation in an application configuration, this register is read into the shift register. When a reconfiguration cycle is started, the contents of the update register are written into the control register. |

| Update<br>register  | This register contains data similar to that in the control register. However, it can only be updated by the factory configuration by shifting data into the shift register and issuing an update operation. When a reconfiguration cycle is triggered by the factory configuration, the control register is updated with the contents of the update register. During a read in a factory configuration, this register is read into the shift register.            |

| Status<br>register  | This register is written by the remote system upgrade circuitry on every reconfiguration to record the cause of the reconfiguration. This information is used by the factory configuration to determine the appropriate action following a reconfiguration. During a capture cycle, this register is read into the shift register.                                                                                                                                |

The control and status registers of the remote system upgrade are clocked by the 10-MHz internal oscillator (the same oscillator that controls the user watchdog timer) or the CLKUSR. However, the shift and update registers of the remote system upgrade are clocked by the maximum frequency of 40-MHz user clock input (RU\_CLK). There is no minimum frequency for RU\_CLK.

### **Remote System Upgrade Control Register**

The remote system upgrade control register stores the application configuration address, the user watchdog timer settings, and option bits for a application configuration. In remote update mode for the AS configuration scheme, the control register address bits are set to all zeros (24'b0) at power up to load the AS factory configuration. In remote update mode for the AP configuration scheme, the control register address bits are set to 24'h010000 (24'b1 0000 0000 0000) at power up to load the AP default factory configuration. However, for the AP configuration scheme, you can change the default factory configuration address to any desired address using the APFC\_BOOT\_ADDR JTAG instruction. Additionally, a factory configuration in remote update mode has write access to this register. The PCIe protocol defines fast training sequences for bit and byte synchronization to transition from L0s to L0 (PIPE P0s to P0) power states. The PHY must acquire bit and byte synchronization when transitioning from L0s to L0 state between 16 ns to 4 µs. Each Cyclone IV GX receiver channel has built-in fast recovery circuit that allows the receiver to meet the requirement when enabled.

## **Electrical Idle Inference**

In PIPE mode, the Cyclone IV GX transceiver supports inferring the electrical idle condition at each receiver instead of detecting the electrical idle condition using analog circuitry, as defined in the version 2.0 of PCIe Base Specification. The inference is supported using rx\_elecidleinfersel[2..0] port, with valid driven values as listed in Table 1–17 in each link training and status state machine substate.

Table 1–17. Electrical Idle Inference Conditions

| rx_elecidleinfersel<br>[20] | Link Training and Status<br>State Machine State               | Description                                                                                       |

|-----------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 3'b100                      | LO                                                            | Absence of $\mathtt{update}\_\mathtt{FC}$ or alternatively skip ordered set in 128 $\mu s$ window |

| 3'b101                      | Recovery.RcvrCfg                                              | Absence of TS1 or TS2 ordered set in 1280 UI interval                                             |

| 3'b101                      | Recovery.Speed when<br>successful speed<br>negotiation = 1'b1 | Absence of TS1 or TS2 ordered set in 1280 UI interval                                             |

| 3'b110                      | Recovery.Speed when<br>successful speed<br>negotiation = 1'b0 | Absence of an exit from electrical idle in 2000 UI interval                                       |

| 3'b111                      | Loopback.Active (as slave)                                    | Absence of an exit from electrical idle in 128 $\mu s$ window                                     |

The electrical idle inference module drives the pipeelecidle signal high in each receiver channel when an electrical idle condition is inferred. The electrical idle inference module cannot detect electrical idle exit condition based on the reception of the electrical idle exit ordered set, as specified in the PCI Express (PIPE) Base Specification.

When enabled, the electrical idle inference block uses electrical idle ordered set detection from the fast recovery circuitry to drive the pipeelecidle signal.

## **Compliance Pattern Transmission**

In PIPE mode, the Cyclone IV GX transceiver supports compliance pattern transmission which requires the first /K28.5/ code group of the compliance pattern to be encoded with negative current disparity. This requirement is supported using a tx\_forcedispcompliance port that when driven with logic high, the transmitter data on the tx\_datain port is transmitted with negative current running disparity.

### **Receiver Only Channel—Receiver CDR in Manual Lock Mode**

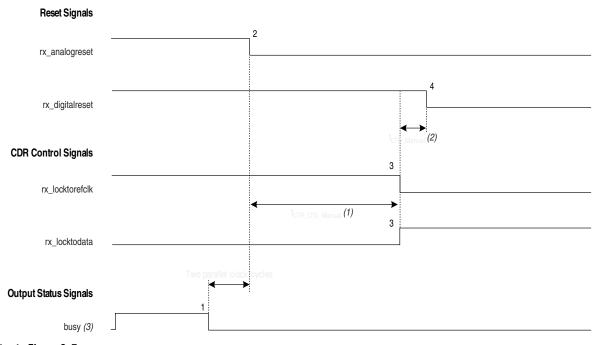

This configuration contains only a receiver channel. If you create a **Receiver Only** instance in the ALTGX MegaWizard Plug-In Manager with receiver CDR in manual lock mode, use the reset sequence shown in Figure 2–7.

Figure 2-7. Sample Reset Sequence of Receiver Only Channel—Receiver CDR in Manual Lock Mode

### Notes to Figure 2–7:

- (1) For t<sub>LTR LTD Manual</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) For  $t_{LTD Manual}$  duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (3) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–7, perform the following reset procedure for the receiver CDR in manual lock mode:

- 1. After power up, wait for the busy signal to be asserted.

- 2. Keep the rx\_digitalreset and rx\_locktorefclk signals asserted and the rx\_locktodata signal deasserted during this time period.

- 3. After deassertion of the busy signal (marker 1), wait for two parallel clock cycles to deassert the rx\_analogreset signal (marker 2). After rx\_analogreset deassert, rx\_pll\_locked will assert.

- 4. Wait for at least t<sub>LTR\_LTD\_Manual</sub>, then deassert the rx\_locktorefclk signal. At the same time, assert the rx\_locktodata signal (marker 3).

- 5. Deassert rx\_digital reset at least  $t_{\rm LTD\_Manual}$  (the time between markers 3 and 4) after asserting the rx\_locktodata signal. At this point, the receiver is ready to receive data.

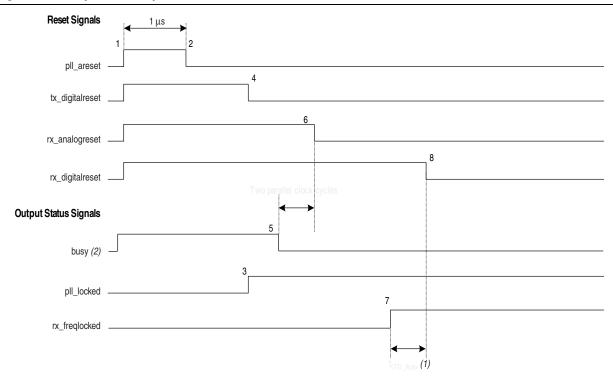

### **Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode**

This configuration contains both a transmitter and a receiver channel. If you create a **Receiver and Transmitter** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 2–8.

Figure 2–8. Sample Reset Sequence of Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

### Notes to Figure 2-8:

- (1) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–8, perform the following reset procedure for the receiver in CDR automatic lock mode:

- 1. After power up, assert pll\_areset for a minimum period of 1 µs (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals asserted during this time period. After you deassert the pll\_areset signal, the multipurpose PLL starts locking to the transmitter input reference clock.

- 3. After the multipurpose PLL locks, as indicated by the pll\_locked signal going high (marker 3), deassert tx\_digitalreset. For receiver operation, after deassertion of busy signal, wait for two parallel clock cycles to deassert the rx\_analogreset signal.

- 4. Wait for the rx freqlocked signal to go high (marker 7).

- 5. After the rx\_freqlocked signal goes high, wait for at least t<sub>LTD\_Auto</sub>, then deassert the rx\_digitalreset signal (marker 8). At this point, the transmitter and receiver are ready for data traffic.

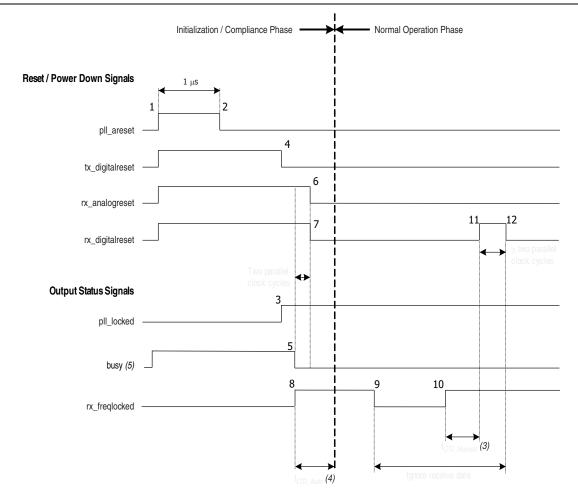

## **PCIe Functional Mode**

You can configure PCIe functional mode with or without the receiver clock rate compensation FIFO in the Cyclone IV GX device. The reset sequence remains the same whether or not you use the receiver clock rate compensation FIFO.

### **PCIe Reset Sequence**

The PCIe protocol consists of an initialization/compliance phase and a normal operation phase. The reset sequences for these two phases are described based on the timing diagram in Figure 2–10.

Figure 2–10. Reset Sequence of PCIe Functional Mode (1), (2)

### Notes to Figure 2–10:

- (1) This timing diagram is drawn based on the PCIe Gen  $1 \times 1$  mode.

- (2) For bonded PCIe Gen 1 ×2 and ×4 modes, there will be additional rx freqlocked [n] signal. n=number of channels.

- (3) For t<sub>LTD Manual</sub> duration, refer to the Cyclone IV Device Datasheet chapter.

- (4) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (5) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

|                                              | V <sub>CCI0</sub> (V) |     |       | V <sub>ID</sub> (mV) V <sub>IcM</sub> (V) <sup>(2)</sup> |     |      |                                                                                                       |      | Vo  | <sub>D</sub> (mV) | (3) | V <sub>0S</sub> (V) <sup>(3)</sup> |      |       |

|----------------------------------------------|-----------------------|-----|-------|----------------------------------------------------------|-----|------|-------------------------------------------------------------------------------------------------------|------|-----|-------------------|-----|------------------------------------|------|-------|

| I/O Standard                                 | Min                   | Тур | Max   | Min                                                      | Max | Min  | Min Condition Max N                                                                                   |      | Min | Тур               | Max | Min                                | Тур  | Max   |

|                                              |                       |     |       |                                                          |     | 0.05 | $D_{MAX} \leq 500 \text{ Mbps}$                                                                       | 1.80 |     |                   |     |                                    |      |       |

| LVDS<br>(Column<br>I/Os)                     | 2.375                 | 2.5 | 2.625 | 100                                                      | _   | 0.55 | $\begin{array}{l} 500 \text{ Mbps} \leq \text{D}_{\text{MAX}} \\ \leq \ 700 \text{ Mbps} \end{array}$ | 1.80 | 247 | —                 | 600 | 1.125                              | 1.25 | 1.375 |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,      |                       |     |       |                                                          |     | 1.05 | D <sub>MAX</sub> > 700 Mbps                                                                           | 1.55 |     |                   |     |                                    |      |       |

| BLVDS (Row<br>I/Os) <sup>(4)</sup>           | 2.375                 | 2.5 | 2.625 | 100                                                      | _   | _    | _                                                                                                     | _    | _   | _                 | _   | _                                  | _    | _     |

| BLVDS<br>(Column<br>I/Os) <sup>(4)</sup>     | 2.375                 | 2.5 | 2.625 | 100                                                      | _   | _    | _                                                                                                     | _    |     |                   | _   | _                                  | _    |       |

| mini-LVDS<br>(Row I/Os)<br>(5)               | 2.375                 | 2.5 | 2.625 | _                                                        | _   | _    | _                                                                                                     | _    | 300 | _                 | 600 | 1.0                                | 1.2  | 1.4   |

| mini-LVDS<br>(Column<br>I/Os) <sup>(5)</sup> | 2.375                 | 2.5 | 2.625 | _                                                        | _   | _    | _                                                                                                     | _    | 300 | _                 | 600 | 1.0                                | 1.2  | 1.4   |

| RSDS® (Row<br>I/Os) <sup>(5)</sup>           | 2.375                 | 2.5 | 2.625 | _                                                        | _   | _    | _                                                                                                     | _    | 100 | 200               | 600 | 0.5                                | 1.2  | 1.5   |

| RSDS<br>(Column<br>I/Os) <sup>(5)</sup>      | 2.375                 | 2.5 | 2.625 | _                                                        | _   | _    | _                                                                                                     | _    | 100 | 200               | 600 | 0.5                                | 1.2  | 1.5   |

| PPDS (Row<br>I/Os) <i>(</i> 5)               | 2.375                 | 2.5 | 2.625 | _                                                        | _   | _    | _                                                                                                     | _    | 100 | 200               | 600 | 0.5                                | 1.2  | 1.4   |

| PPDS<br>(Column<br>I/Os) <sup>(5)</sup>      | 2.375                 | 2.5 | 2.625 | _                                                        | _   |      | —                                                                                                     |      | 100 | 200               | 600 | 0.5                                | 1.2  | 1.4   |

### Notes to Table 1-20:

(1) For an explanation of terms used in Table 1–20, refer to "Glossary" on page 1–37.

(2)  $~V_{IN}$  range: 0 V  $\leq V_{IN} \leq$  1.85 V.

(3)  $R_L \mbox{ range: } 90 \leq \ R_L \leq \ 110 \ \Omega$  .

(4) There are no fixed  $V_{\rm IN},\,V_{\rm OD},$  and  $V_{\rm OS}$  specifications for BLVDS. They depend on the system topology.

(5) The Mini-LVDS, RSDS, and PPDS standards are only supported at the output pins.

(6) The LVPECL I/O standard is only supported on dedicated clock input pins. This I/O standard is not supported for output pins.