Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 1803                                                    |

| Number of Logic Elements/Cells | 28848                                                   |

| Total RAM Bits                 | 608256                                                  |

| Number of I/O                  | 532                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BGA                                                 |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce30f29c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

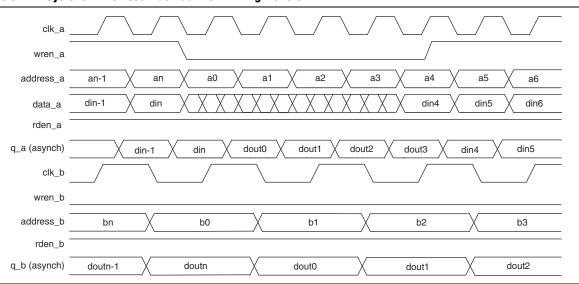

In true dual-port mode, you can access any memory location at any time from either port A or port B. However, when accessing the same memory location from both ports, you must avoid possible write conflicts. When you attempt to write to the same address location from both ports at the same time, a write conflict happens. This results in unknown data being stored to that address location. There is no conflict resolution circuitry built into the Cyclone IV devices M9K memory blocks. You must handle address conflicts external to the RAM block.

Figure 3–11 shows true dual-port timing waveforms for the write operation at port A and read operation at port B. Registering the outputs of the RAM simply delays the q outputs by one clock cycle.

Figure 3-11. Cyclone IV Devices True Dual-Port Timing Waveform

# **Shift Register Mode**

Cyclone IV devices M9K memory blocks can implement shift registers for digital signal processing (DSP) applications, such as finite impulse response (FIR) filters, pseudo-random number generators, multi-channel filtering, and auto-correlation and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flipflops that quickly exhaust many logic cells for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources.

The size of a  $(w \times m \times n)$  shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n), and must be less than or equal to the maximum number of memory bits, which is 9,216 bits. In addition, the size of  $(w \times n)$  must be less than or equal to the maximum width of the block, which is 36 bits. If you need a larger shift register, you can cascade the M9K memory blocks.

Table 5-3. GCLK Network Connections for Cyclone IV E Devices (1) (Part 2 of 3)

| GCLK Network Clock   |          |          |          |          |          |          |          |          | GC       | LK N     | etwo     | rks      |          |          |    |          |          |    |    |          |

|----------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----|----------|----------|----|----|----------|

| Sources              | 0        | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9        | 10       | 11       | 12       | 13       | 14 | 15       | 16       | 17 | 18 | 19       |

| CLK15/DIFFCLK_6p (2) | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | ~        | _        | _  | ~  | _        |

| PLL_1_C0 (3)         | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  |          | _        | _  | _  | _        |

| PLL_1_C1 (3)         | _        | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_1_C2 (3)         | <b>✓</b> | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_1_C3 (3)         | _        | <b>✓</b> | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_1_C4 (3)         | _        | _        | <b>✓</b> | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_2_C0 (3)         | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_2_C1 (3)         | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_2_C2 (3)         | _        | _        | _        | _        | _        | ✓        | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_2_C3 (3)         | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | <b>✓</b> | _        | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_2_C4 (3)         | _        | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | <b>✓</b> | _        | _        | _        | _        | _  | _        | _        | _  | _  | _        |

| PLL_3_C0             | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        | <b>✓</b> | _  | _        | _        | _  | _  | _        |

| PLL_3_C1             | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        | ✓  | _        | _        | _  | _  | _        |

| PLL_3_C2             | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | <b>✓</b> | _        | _  | _        | _        | _  | _  | _        |

| PLL_3_C3             | _        | _        | _        | _        |          | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | <b>✓</b> | _  | —        |          | _  | _  | _        |

| PLL_3_C4             | _        | _        | _        | _        |          | _        | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | ✓  | _        |          | _  | _  | _        |

| PLL_4_C0             | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | <b>✓</b> | _        | _  | ✓  | _        |

| PLL_4_C1             | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | _        | <b>✓</b> | _  | _  | <b>√</b> |

| PLL_4_C2             | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | ✓        | _        | ✓  | _  | _        |

| PLL_4_C3             | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | _        | ✓        | _  | ✓  | _        |

| PLL_4_C4             | _        | _        | _        | _        |          | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | _        |          | ✓  | _  | <b>√</b> |

| DPCLK0               | <b>✓</b> | _        | _        | _        |          | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  | _        |          | _  | _  | _        |

| DPCLK1               | _        | ~        | _        | _        |          | _        | _        | _        | _        | _        | _        | _        | _        | _        | _  |          |          | _  | _  | _        |

| DPCLK7 (4)           |          |          |          |          |          |          |          |          |          |          |          |          |          |          |    |          |          |    |    |          |

| CDPCLKO, or          | _        | _        | ~        | _        | _        | _        | _        | _        | _        | _        | _        | —        | _        | _        | _  | _        | _        | _  | _  |          |

| CDPCLK7 (2), (5)     |          |          |          |          |          |          |          |          |          |          |          |          |          |          |    |          |          |    |    |          |

Figure 5–21 shows an example of phase shift insertion using fine resolution through VCO phase taps method. The eight phases from the VCO are shown and labeled for reference. In this example, CLK0 is based on 0° phase from the VCO and has the C value for the counter set to one. The CLK1 signal is divided by four, two VCO clocks for high time and two VCO clocks for low time. CLK1 is based on the 135° phase tap from the VCO and has the C value for the counter set to one. The CLK1 signal is also divided by four. In this case, the two clocks are offset by 3  $\Phi_{\rm fine}$ . CLK2 is based on the 0° phase from the VCO but has the C value for the counter set to three. This creates a delay of two  $\Phi_{\rm coarse}$  (two complete VCO periods).

$1/8 t_{VCO} \rightarrow \qquad \qquad t_{VCO} \rightarrow \qquad t_{VCO} \rightarrow$

Figure 5-21. Delay Insertion Using VCO Phase Output and Counter Delay Time

You can use the coarse and fine phase shifts to implement clock delays in Cyclone IV devices.

Cyclone IV devices support dynamic phase shifting of VCO phase taps only. The phase shift is configurable for any number of times. Each phase shift takes about one scanclk cycle, allowing you to implement large phase shifts quickly.

# **PLL Cascading**

Cyclone IV devices allow cascading between general purpose PLLs and multipurpose PLLs in normal or direct mode through the GCLK network. If your design cascades PLLs, the source (upstream) PLL must have a low-bandwidth setting, while the destination (downstream) PLL must have a high-bandwidth setting.

PLL\_6 and PLL7 have upstream cascading capability only.

PLL cascading is not supported when used in transceiver applications.

## **External Memory Interfacing**

Cyclone IV devices support I/O standards required to interface with a broad range of external memory interfaces, such as DDR SDRAM, DDR2 SDRAM, and QDR II SRAM.

For more information about Cyclone IV devices external memory interface support, refer to the *External Memory Interfaces in Cyclone IV Devices* chapter.

# **Pad Placement and DC Guidelines**

You can use the Quartus II software to validate your pad and pin placement.

## **Pad Placement**

Altera recommends that you create a Quartus II design, enter your device I/O assignments and compile your design to validate your pin placement. The Quartus II software checks your pin connections with respect to the I/O assignment and placement rules to ensure proper device operation. These rules depend on device density, package, I/O assignments, voltage assignments and other factors that are not fully described in this chapter.

For more information about how the Quartus II software checks I/O restrictions, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

## **DC** Guidelines

For the Quartus II software to automatically check for illegally placed pads according to the DC guidelines, set the DC current sink or source value to **Electromigration Current** assignment on each of the output pins that are connected to the external resistive load.

The programmable current strength setting has an impact on the amount of DC current that an output pin can source or sink. Determine if the current strength setting is sufficient for the external resistive load condition on the output pin.

# **Clock Pins Functionality**

Cyclone IV clock pins have multiple purposes, as per listed:

- CLK pins—Input support for single-ended and voltage-referenced standards. For I/O standard support, refer to Table 6–3 on page 6–11.

- DIFFCLK pins—Input support for differential standards. For I/O standard support, refer to Table 6–3 on page 6–11. When used as DIFFCLK pins, DC or AC coupling can be used depending on the interface requirements and external termination is required. For more information, refer to "High-Speed I/O Standards Support" on page 6–28.

- REFCLK pins—Input support for high speed differential reference clocks used by the transceivers in Cyclone IV GX devices. For I/O support, coupling, and termination requirements, refer to Table 6–10 on page 6–29.

Table 6–8 and Table 6–9 summarize the total number of supported row and column differential channels in the Cyclone IV device family.

Table 6-8. Cyclone IV E I/O and Differential Channel Count

| Device                                       |          | EP4CE6   |          |          | EP4CE10  |          |          |          | 7.07.01  | E146E13  |          |          |          | EP4CE22  |          |          | EP4CE30  |          |          | 970      | Er46E40  |          |          | EP4CE55  |          |          | EP4CE75  |          | 37730743 | Er46E113 |

|----------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Numbers of Differential<br>Channels (1), (2) | 144-EQPF | 726-UBGA | 256-FBGA | 144-EQPF | S56-UBGA | 256-FBGA | 144-EQPF | 164-MBGA | 256-MBGA | S56-UBGA | 256-FBGA | 484-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 324-FBGA | 484-FBGA | 780-FBGA | 324-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-FBGA | 780-FBGA |

| User<br>I/O <i>(3)</i>                       | 91       | 179      | 179      | 91       | 179      | 179      | 81       | 89       | 165      | 165      | 165      | 343      | 79       | 153      | 153      | 193      | 328      | 532      | 193      | 328      | 328      | 532      | 324      | 324      | 374      | 292      | 292      | 426      | 280      | 528      |

| User I/O<br>Banks                            | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        |

| LVDS (4), (<br>6)                            | 8        | 23       | 23       | 8        | 23       | 23       | 6        | 8        | 21       | 21       | 21       | 67       | 7        | 20       | 20       | 30       | 60       | 112      | 30       | 60       | 60       | 112      | 62       | 62       | 70       | 54       | 54       | 79       | 50       | 103      |

| Emulated<br>LVDS (5), (<br>6)                | 13       | 43       | 43       | 13       | 43       | 43       | 12       | 13       | 32       | 32       | 32       | 70       | 10       | 32       | 32       | 38       | 64       | 112      | 38       | 64       | 64       | 112      | 70       | 70       | 90       | 56       | 56       | 99       | 53       | 127      |

#### Notes to Table 6-8:

- (1) User I/O pins are used as inputs or outputs; clock input pins are used as inputs only; clock output pins are used as output only.

- (2) For differential pad placement guidelines, refer to "Pad Placement" on page 6-23.

- (3) The I/O pin count includes all GPIOs, dedicated clock pins, and dual-purpose configuration pins. Dedicated configuration pins are not included in the pin count.

- (4) The true LVDS count includes all LVDS I/O pairs, differential clock input and clock output pins in row I/O banks 1, 2, 5, and 6.

- (5) The emulated LVDS count includes all LVDS I/O pairs, differential clock input and clock output pins in column I/O banks 3, 4, 7, and 8.

- (6) LVDS input and output buffers are sharing the same p and n pins. One LVDS I/O channel can only be either transmitter or receiver at a time.

Chapter 6: I/O Features in Cyclone IV Devices

High-Speed I/O Interface

# 7. External Memory Interfaces in Cyclone IV Devices

#### CYIV-51007-2.6

This chapter describes the memory interface pin support and the external memory interface features of Cyclone<sup>®</sup> IV devices.

In addition to an abundant supply of on-chip memory, Cyclone IV devices can easily interface with a broad range of external memory devices, including DDR2 SDRAM, DDR SDRAM, and QDR II SRAM. External memory devices are an important system component of a wide range of image processing, storage, communications, and general embedded applications.

Altera recommends that you construct all DDR2 or DDR SDRAM external memory interfaces using the Altera® ALTMEMPHY megafunction. You can implement the controller function using the Altera DDR2 or DDR SDRAM memory controllers, third-party controllers, or a custom controller for unique application needs. Cyclone IV devices support QDR II interfaces electrically, but Altera does not supply controller or physical layer (PHY) megafunctions for QDR II interfaces.

This chapter includes the following sections:

- "Cyclone IV Devices Memory Interfaces Pin Support" on page 7–2

- "Cyclone IV Devices Memory Interfaces Features" on page 7–12

- For more information about supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to the *External Memory Interface Handbook*.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 7–2. Cyclone IV E Device DQS and DQ Bus Mode Support for Each Side of the Device (Part 2 of 3)

| Device   | Package         | Side            | Number<br>×8<br>Groups | Number<br>×9<br>Groups | Number<br>×16<br>Groups | Number<br>×18<br>Groups | Number<br>×32<br>Groups | Number<br>×36<br>Groups |

|----------|-----------------|-----------------|------------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

|          |                 | Left            | 0                      | 0                      | 0                       | 0                       | _                       | _                       |

|          | 144-pin EQFP    | Right           | 0                      | 0                      | 0                       | 0                       | _                       | _                       |

|          | 144-pili EQFF   | Bottom (1), (3) | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|          |                 | Top (1), (4)    | 1                      | 0                      | 0                       | 0                       | _                       | _                       |

|          |                 | Left (1)        | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

| EP4CE22  | 256-pin UBGA    | Right (2)       | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

| EF4UEZZ  | 250-piii 0BGA   | Bottom          | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                 | Тор             | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                 | Left (1)        | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 256-pin FBGA    | Right (2)       | 1                      | 1                      | 0                       | 0                       | _                       | _                       |

|          | 250-piii 1 baA  | Bottom          | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                 | Тор             | 2                      | 2                      | 1                       | 1                       | _                       | _                       |

|          |                 | Left (1)        | 2                      | 2                      | 1                       | 1                       | 0                       | 0                       |

| EP4CE30  | 324-pin FBGA    | Right (2)       | 2                      | 2                      | 1                       | 1                       | 0                       | 0                       |

| LI 40L30 | 324-piii 1 buA  | Bottom          | 2                      | 2                      | 1                       | 1                       | 0                       | 0                       |

|          |                 | Тор             | 2                      | 2                      | 1                       | 1                       | 0                       | 0                       |

|          |                 | Left            | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|          | 484-pin FBGA    | Right           | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|          | 404-piii 1 baA  | Bottom          | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

| EP4CE30  |                 | Тор             | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

| EP4CE115 |                 | Left            | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|          | 780-pin FBGA    | Right           | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|          | 7 00-piii 1 bdA | Bottom          | 6                      | 6                      | 2                       | 2                       | 1                       | 1                       |

|          |                 | Тор             | 6                      | 6                      | 2                       | 2                       | 1                       | 1                       |

|          |                 | Left            | 2                      | 2                      | 1                       | 1                       | 0                       | 0                       |

| EP4CE40  | 324-nin FRGA    | Right           | 2                      | 2                      | 1                       | 1                       | 0                       | 0                       |

| L1 40L40 | 324-pin FBGA    | Bottom          | 2                      | 2                      | 1                       | 1                       | 0                       | 0                       |

|          |                 | Тор             | 2                      | 2                      | 1                       | 1                       | 0                       | 0                       |

| Table 1-2. C | ycione IV E Device | na and and and | woae Suppo | rt for Each S | Side of the D | evice (Pari | ( 3 OT 3) |

|--------------|--------------------|----------------|------------|---------------|---------------|-------------|-----------|

|              |                    |                | Number     | Number        | Number        | Number      | Number    |

| Device  | Package       | Side   | Number<br>×8<br>Groups | Number<br>×9<br>Groups | Number<br>×16<br>Groups | Number<br>×18<br>Groups | Number<br>×32<br>Groups | Number<br>×36<br>Groups |

|---------|---------------|--------|------------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

|         |               | Left   | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         | 484-pin UBGA  | Right  | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         | 404-piii UBGA | Bottom | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         |               | Тор    | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

| EP4CE40 |               | Left   | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

| EP4CE55 | 404 pin EDCA  | Right  | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

| EP4CE35 | 484-pin FBGA  | Bottom | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

| EF40E73 |               | Тор    | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         |               | Left   | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         | 780-pin FBGA  | Right  | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         |               | Bottom | 6                      | 6                      | 2                       | 2                       | 1                       | 1                       |

|         |               | Тор    | 6                      | 6                      | 2                       | 2                       | 1                       | 1                       |

#### Notes to Table 7-2:

- (1) Some of the DQ pins can be used as RUP and RDN pins. You cannot use these groups if you are using these pins as RUP and RDN pins for

- (2) Some of the DQ pins can be used as RUP pins while the DM pins can be used as RDN pins. You cannot use these groups if you are using the RUP and RDN pins for OCT calibration.

- (3) There is no DM pin support for these groups.

- (4) PLLCLKOUT3n and PLLCLKOUT3p pins are shared with the DQ or DM pins to gain ×8 DQ group. You cannot use these groups if you are using PLLCLKOUT3n and PLLCLKOUT3p.

For more information about device package outline, refer to the Device Packaging Specifications webpage.

DQS pins are listed in the Cyclone IV pin tables as DQSXY, in which X indicates the DQS grouping number and Y indicates whether the group is located on the top (T), bottom (B), or right (R) side of the device. Similarly, the corresponding DQ pins are marked as DQXY, in which the X denotes the DQ grouping number and Y denotes whether the group is located on the top (T), bottom (B), or right (R) side of the device. For example, DQS2T indicates a DQS pin belonging to group 2, located on the top side of the device. Similarly, the DQ pins belonging to that group is shown as DQ2T.

Each DQ group is associated with its corresponding DQS pins, as defined in the Cyclone IV pin tables. For example:

- For DDR2 or DDR SDRAM, ×8 DQ group DQ3B[7..0] pins are associated with the DQS3B pin (same 3B group index)

- For QDR II SRAM, ×9 Q read-data group DQ3T[8..0] pins are associated with DQS0T/CQ0T and DQS1T/CQ0T# pins (same 0T group index)

The Quartus<sup>®</sup> II software issues an error message if a DQ group is not placed properly with its associated DOS.

## Power-On Reset (POR) Circuit

The POR circuit keeps the device in reset state until the power supply voltage levels have stabilized during device power up. After device power up, the device does not release nSTATUS until  $V_{\rm CCINT}$ ,  $V_{\rm CCA}$ , and  $V_{\rm CCIO}$  (for I/O banks in which the configuration and JTAG pins reside) are above the POR trip point of the device.  $V_{\rm CCINT}$  and  $V_{\rm CCA}$  are monitored for brown-out conditions after device power up.

$V_{CCA}$  is the analog power to the phase-locked loop (PLL).

In some applications, it is necessary for a device to wake up very quickly to begin operation. Cyclone IV devices offer the fast POR time option to support fast wake-up time applications. The fast POR time option has stricter power-up requirements when compared with the standard POR time option. You can select either the fast option or the standard POR option with the MSEL pin settings.

- If your system exceeds the fast or standard POR time, you must hold nCONFIG low until all the power supplies are stable.

- For more information about the POR specifications, refer to the *Cyclone IV Device Datasheet*.

- For more information about the wake-up time and POR circuit, refer to the *Power Requirements for Cyclone IV Devices* chapter.

## **Configuration File Size**

Table 8–2 lists the approximate uncompressed configuration file sizes for Cyclone IV devices. To calculate the amount of storage space required for multiple device configurations, add the file size of each device together.

Table 8–2. Uncompressed Raw Binary File (.rbf) Sizes for Cyclone IV Devices (Part 1 of 2)

| <u>-</u>     | , , ,    | ,                |

|--------------|----------|------------------|

|              | Device   | Data Size (bits) |

|              | EP4CE6   | 2,944,088        |

|              | EP4CE10  | 2,944,088        |

|              | EP4CE15  | 4,086,848        |

|              | EP4CE22  | 5,748,552        |

| Cyclone IV E | EP4CE30  | 9,534,304        |

|              | EP4CE40  | 9,534,304        |

|              | EP4CE55  | 14,889,560       |

|              | EP4CE75  | 19,965,752       |

|              | EP4CE115 | 28,571,696       |

Table 8–8 provides the configuration time for AS configuration.

Table 8–8. AS Configuration Time for Cyclone IV Devices (1)

| Symbol          | Parameter            | Cyclone IV E | Cyclone IV GX | Unit |

|-----------------|----------------------|--------------|---------------|------|

| t <sub>SU</sub> | Setup time           | 10           | 8             | ns   |

| t <sub>H</sub>  | Hold time            | 0            | 0             | ns   |

| t <sub>co</sub> | Clock-to-output time | 4            | 4             | ns   |

#### Note to Table 8-8:

(1) For the AS configuration timing diagram, refer to the Serial Configuration (EPCS) Devices Datasheet.

Enabling compression reduces the amount of configuration data that is sent to the Cyclone IV device, which also reduces configuration time. On average, compression reduces configuration time by 50%.

## **Programming Serial Configuration Devices**

Serial configuration devices are non-volatile, flash memory-based devices. You can program these devices in-system with the USB-Blaster<sup>TM</sup> or ByteBlaster<sup>TM</sup> II download cables. Alternatively, you can program them with the Altera Programming Unit (APU), supported third-party programmers, or a microprocessor with the SRunner software driver.

You can perform in-system programming of serial configuration devices through the AS programming interface. During in-system programming, the download cable disables device access to the AS interface by driving the nCE pin high. Cyclone IV devices are also held in reset by a low level on nCONFIG. After programming is complete, the download cable releases nCE and nCONFIG, allowing the pull-down and pull-up resistors to drive  $\rm V_{CC}$  and GND, respectively.

To perform in-system programming of a serial configuration device through the AS programming interface, you must place the diodes and capacitors as close as possible to the Cyclone IV device. You must ensure that the diodes and capacitors maintain a maximum AC voltage of 4.1 V (Figure 8–6).

If you want to use the setup shown in Figure 8–6 to perform in-system programming of a serial configuration device and single- or multi-device AS configuration, you do not require a series resistor on the DATA line at the near end of the serial configuration device. The existing diodes and capacitors are sufficient.

Altera has developed the Serial FlashLoader (SFL), a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the Cyclone IV device that uses its JTAG interface to access the EPCS JIC (JTAG Indirect Configuration Device Programming) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the SFL design.

For more information about implementing the SFL with Cyclone IV devices, refer to AN 370: Using the Serial FlashLoader with the Quartus II Software.

May 2013 Altera Corporation

# **Document Revision History**

Table 9–8 lists the revision history for this chapter.

Table 9-8. Document Revision History

| Date          | Version | Changes                                                                                                                                                                      |  |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| May 2013      | 1.3     | Updated "CRC_ERROR Pin Type" in Table 9–2.                                                                                                                                   |  |

| October 2012  | 1.2     | Updated Table 9–2.                                                                                                                                                           |  |

| February 2010 | 1.1     | Updated for the Quartus II software version 9.1 SP1 release:  Updated "Configuration Error Detection" section.  Updated Table 9–6.  Added Cyclone IV E devices in Table 9–6. |  |

| November 2009 | 1.0     | Initial release.                                                                                                                                                             |  |

| Document Revision History                                                                  | 2–24 |

|--------------------------------------------------------------------------------------------|------|

| Chapter 3. Cyclone IV Dynamic Reconfiguration                                              |      |

| Glossary of Terms                                                                          | 3–1  |

| Dynamic Reconfiguration Controller Architecture                                            | 3–2  |

| Dynamic Reconfiguration Controller Port List                                               |      |

| Offset Cancellation Feature                                                                |      |

| Functional Simulation of the Offset Cancellation Process                                   |      |

| Dynamic Reconfiguration Modes                                                              | 3–12 |

| PMA Controls Reconfiguration Mode                                                          |      |

| Method 1: Using logical_channel_address to Reconfigure Specific Transceiver Channels       |      |

| Method 2: Writing the Same Control Signals to Control All the Transceiver Channels         |      |

| Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same T |      |

| 3–19                                                                                       |      |

| Transceiver Channel Reconfiguration Mode                                                   | 3–21 |

| Channel Interface Reconfiguration Mode                                                     |      |

| Data Rate Reconfiguration Mode Using RX Local Divider                                      |      |

| Control and Status Signals for Channel Reconfiguration                                     |      |

| PLL Reconfiguration Mode                                                                   |      |

| Error Indication During Dynamic Reconfiguration                                            |      |

| Functional Simulation of the Dynamic Reconfiguration Process                               |      |

| Document Revision History                                                                  |      |

Table 1–13. Automatic RX Phase Compensation FIFO Read Clock Selection (Part 2 of 2)

| Chann   | nel Configuration        | Quartus II Selection                                                                                                                                                                                        |

|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bonded  | With rate match FIFO (1) | coreclkout clock feeds the FIFO read clock for the bonded channels. coreclkout clock is the common bonded low-speed clock, which also feeds the FIFO read clock and transmitter PCS in the bonded channels. |

| Dollaca | Without rate match FIFO  | $rx\_clkout$ clock feeds the FIFO read clock. $rx\_clkout$ is forwarded through the receiver channel from low-speed recovered clock, which also feeds the FIFO write clock.                                 |

#### Note to Table 1-13:

(1) Configuration with rate match FIFO is supported in transmitter and receiver operation.

When using user-specified clock option, ensure that the clock feeding rx\_coreclk port has 0 ppm difference with the RX phase compensation FIFO write clock.

## **Calibration Block**

This block calibrates the OCT resistors and the analog portions of the transceiver blocks to ensure that the functionality is independent of process, voltage, and temperature (PVT) variations.

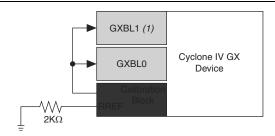

Figure 1–40 shows the location of the calibration block and how it is connected to the transceiver blocks.

Figure 1-40. Transceiver Calibration Blocks Location and Connection

#### Note to Figure 1-40:

(1) Transceiver block GXBL1 is only available for devices in F484 and larger packages.

## **Clock Frequency Compensation**

In Serial RapidIO mode, the rate match FIFO compensates up to ±100 ppm (200 ppm total) difference between the upstream transmitter and the local receiver reference clock.

Rate matcher is an optional block available for selection in Serial RapidIO mode. However, this block is not fully compliant to the SRIO specification. When enabled in the ALTGX MegaWizard Plug-In Manager, the default settings are:

- control pattern 1 = K28.5 with positive disparity

- $\blacksquare$  skip pattern 1 = K29.7 with positive disparity

- control pattern 2 = K28.5 with negative disparity

- skip pattern 2 = K29.7 with negative disparity

When enabled, the rate match FIFO operation begins after the link is synchronized (indicated by assertion of rx\_syncstatus from the word aligner). When the rate matcher receives either of the two 10-bit control patterns followed by the respective 10-bit skip pattern, it inserts or deletes the 10-bit skip pattern as necessary to avoid the rate match FIFO from overflowing or under-running. The rate match FIFO can delete/insert a maximum of one skip pattern from a cluster.

The rate match FIFO may perform multiple insertion or deletion if the ppm difference is more than the allowable 200 ppm range. Ensure that the ppm difference in your system is less than 200 ppm.

### **XAUI Mode**

XAUI mode provides the bonded (×4) transceiver channel datapath configuration for XAUI protocol implementation. The Cyclone IV GX transceivers configured in XAUI mode provides the following functions:

- XGMII-to-PCS code conversion at transmitter datapath

- PCS-to-XGMII code conversion at receiver datapath

- channel deskewing of four lanes

- 8B/10B encoding and decoding

- IEEE P802.3ae-compliant synchronization state machine

- clock rate compensation

The XAUI is a self-managed interface to transparently extend the physical reach of the XGMII between the reconciliation sublayer and the PHY layer in the 10 Gbps LAN as shown in Figure 1–62. The XAUI interface consists of four lanes, each running at 3.125 Gbps with 8B/10B encoded data for a total of actual 10 Gbps data throughput. At the transmit side of the XAUI interface, the data and control characters are

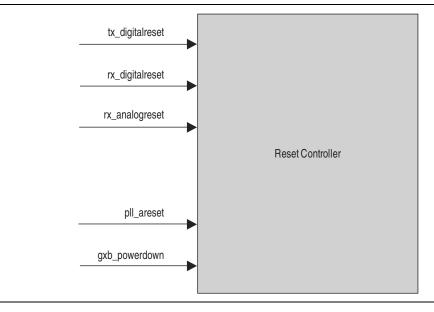

# 2. Cyclone IV Reset Control and Power Down

#### CYIV-52002-1.4

Cyclone<sup>®</sup> IV GX devices offer multiple reset signals to control transceiver channels independently. The ALTGX Transceiver MegaWizard<sup>™</sup> Plug-In Manager provides individual reset signals for each channel instantiated in your design. It also provides one power-down signal for each transceiver block.

This chapter includes the following sections:

- "User Reset and Power-Down Signals" on page 2–2

- "Transceiver Reset Sequences" on page 2–4

- "Dynamic Reconfiguration Reset Sequences" on page 2–19

- "Power Down" on page 2–21

- "Simulation Requirements" on page 2–22

- "Reference Information" on page 2–23

Figure 2–1 shows the reset control and power-down block for a Cyclone IV GX device.

Figure 2-1. Reset Control and Power-Down Block

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### **Transmitter Only Channel**

This configuration contains only a transmitter channel. If you create a **Transmitter Only** instance in the ALTGX MegaWizard Plug-In Manager, use the same reset sequence shown in Figure 2–3 on page 2–7.

#### Receiver Only Channel—Receiver CDR in Automatic Lock Mode

This configuration contains only a receiver channel. If you create a **Receiver Only** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 2–6.

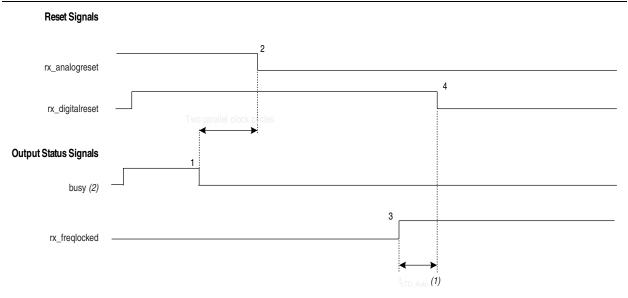

Figure 2–6. Sample Reset Sequence of Receiver Only Channel—Receiver CDR in Automatic Lock Mode

#### Notes to Figure 2-6:

- (1) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–6, perform the following reset procedure for the receiver in CDR automatic lock mode:

- 1. After power up, wait for the busy signal to be deasserted.

- 2. Keep the rx\_digitalreset and rx\_analogreset signals asserted during this time period.

- 3. After the busy signal is deasserted, wait for another two parallel clock cycles, then deassert the rx\_analogreset signal.

- 4. Wait for the rx freqlocked signal to go high.

- 5. When rx\_freqlocked goes high (marker 3), from that point onwards, wait for at least t<sub>LTD\_Auto</sub>, then de-assert the rx\_digitalreset signal (marker 4). At this point, the receiver is ready to receive data.

■ In PCIe mode simulation, you must assert the tx\_forceelecidle signal for at least one parallel clock cycle before transmitting normal data for correct simulation behavior.

# **Reference Information**

For more information about some useful reference terms used in this chapter, refer to the links listed in Table 2–7.

Table 2-7. Reference Information

| Terms Used in this Chapter              | Useful Reference Points |

|-----------------------------------------|-------------------------|

| Automatic Lock Mode                     | page 2–8                |

| Bonded channel configuration            | page 2–6                |

| busy                                    | page 2–3                |

| Dynamic Reconfiguration Reset Sequences | page 2–19               |

| gxb_powerdown                           | page 2–3                |

| LTD                                     | page 2–6                |

| LTR                                     | page 2–6                |

| Manual Lock Mode                        | page 2–9                |

| Non-Bonded channel configuration        | page 2–10               |

| PCIe                                    | page 2–17               |

| pll_locked                              | page 2–3                |

| pll_areset                              | page 2–3                |

| rx_analogreset                          | page 2–2                |

| rx_digitalreset                         | page 2–2                |

| rx_freqlocked                           | page 2–3                |

| tx_digitalreset                         | page 2–2                |

Table 3-2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 5 of 7)

| Port Name                    | Input/<br>Output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                           |          |  |  |  |  |  |  |               |                                       |

|------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|---------------|---------------------------------------|

| tx_preemp[40] (1)            |                  | This is an optional pre-emphasis write control for the transmit buffer. Depending on what value you set at this input, the controller dynamically writes the value to the pre-emphasis control register of the transmit buffer.  The width of this signal is fixed to 5 bits if you enable either the Use 'logical_channel_address' port for Analog controls reconfiguration option or the Use same control signal for all the channels option in the Analog controls screen. Otherwise, the width of this signal is 5 bits per channel. |                                                                                                           |          |  |  |  |  |  |  |               |                                       |

|                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                           |          |  |  |  |  |  |  | tx_preemp[40] | Corresponding ALTGX instance settings |

|                              |                  | 00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                         | Disabled |  |  |  |  |  |  |               |                                       |

|                              |                  | 00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                         | 0.5      |  |  |  |  |  |  |               |                                       |

|                              | Input            | 00101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                                                         | 1.0      |  |  |  |  |  |  |               |                                       |

|                              | mpat             | 01001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                                                         | 1.5      |  |  |  |  |  |  |               |                                       |

|                              |                  | 01101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13                                                                                                        | 2.0      |  |  |  |  |  |  |               |                                       |

|                              |                  | 10000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16                                                                                                        | 2.375    |  |  |  |  |  |  |               |                                       |

|                              |                  | 10001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17                                                                                                        | 2.5      |  |  |  |  |  |  |               |                                       |

|                              |                  | 10010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18                                                                                                        | 2.625    |  |  |  |  |  |  |               |                                       |

|                              |                  | 10011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19                                                                                                        | 2.75     |  |  |  |  |  |  |               |                                       |

|                              |                  | 10100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                                                                                        | 2.875    |  |  |  |  |  |  |               |                                       |

|                              |                  | 10101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                                                                                                        | 3.0      |  |  |  |  |  |  |               |                                       |

|                              |                  | All other values => N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |          |  |  |  |  |  |  |               |                                       |

|                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This is an optional write control to write an equalization control value for the receive side of the PMA. |          |  |  |  |  |  |  |               |                                       |

| rx_eqctr1[30] <sup>(1)</sup> |                  | The width of this signal is fixed to 4 bits if you enable either the <b>Use</b> 'logical_channel_address' port for Analog controls reconfiguration option or the <b>Use</b> same control signal for all the channels option in the Analog controls screen. Otherwise, the width of this signal is 4 bits per channel.                                                                                                                                                                                                                    |                                                                                                           |          |  |  |  |  |  |  |               |                                       |

|                              | Input            | rx_eqctrl [30] Corresponding ALTGX instance settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                           |          |  |  |  |  |  |  |               |                                       |

|                              |                  | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Low                                                                                                       |          |  |  |  |  |  |  |               |                                       |

|                              |                  | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Medium Low                                                                                                |          |  |  |  |  |  |  |               |                                       |

|                              |                  | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Medium High                                                                                               |          |  |  |  |  |  |  |               |                                       |

|                              |                  | 0111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High                                                                                                      |          |  |  |  |  |  |  |               |                                       |

|                              |                  | All other values => N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | /A                                                                                                        |          |  |  |  |  |  |  |               |                                       |

iv Contents

For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to Section III: System Performance Specifications of the External Memory Interfaces Handbook.

Actual achievable frequency depends on design- and system-specific factors. Perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

## **High-Speed I/O Specifications**

Table 1–31 through Table 1–36 list the high-speed I/O timing for Cyclone IV devices. For definitions of high-speed timing specifications, refer to "Glossary" on page 1–37.

Table 1–31. RSDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4) (Part 1 of 2)

| Symbol                                           | Modes                                    | C6  |     | C7, I7 |     | C8, A7 |       |     | C8L, I8L |       |     | C9L |       |     |     |       |      |

|--------------------------------------------------|------------------------------------------|-----|-----|--------|-----|--------|-------|-----|----------|-------|-----|-----|-------|-----|-----|-------|------|

|                                                  |                                          | Min | Тур | Max    | Min | Тур    | Max   | Min | Тур      | Max   | Min | Тур | Max   | Min | Тур | Max   | Unit |

| f <sub>HSCLK</sub><br>(input clock<br>frequency) | ×10                                      | 5   | _   | 180    | 5   | _      | 155.5 | 5   | _        | 155.5 | 5   |     | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×8                                       | 5   |     | 180    | 5   |        | 155.5 | 5   | _        | 155.5 | 5   |     | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×7                                       | 5   |     | 180    | 5   |        | 155.5 | 5   |          | 155.5 | 5   |     | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×4                                       | 5   |     | 180    | 5   |        | 155.5 | 5   |          | 155.5 | 5   |     | 155.5 | 5   | -   | 132.5 | MHz  |

|                                                  | ×2                                       | 5   | _   | 180    | 5   | _      | 155.5 | 5   |          | 155.5 | 5   |     | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×1                                       | 5   |     | 360    | 5   |        | 311   | 5   |          | 311   | 5   |     | 311   | 5   |     | 265   | MHz  |

| Device<br>operation in<br>Mbps                   | ×10                                      | 100 | _   | 360    | 100 | _      | 311   | 100 | _        | 311   | 100 | _   | 311   | 100 | _   | 265   | Mbps |

|                                                  | ×8                                       | 80  | _   | 360    | 80  |        | 311   | 80  | _        | 311   | 80  |     | 311   | 80  | _   | 265   | Mbps |

|                                                  | ×7                                       | 70  | _   | 360    | 70  |        | 311   | 70  | _        | 311   | 70  |     | 311   | 70  | _   | 265   | Mbps |

|                                                  | ×4                                       | 40  | _   | 360    | 40  | _      | 311   | 40  | _        | 311   | 40  | _   | 311   | 40  | _   | 265   | Mbps |

|                                                  | ×2                                       | 20  | _   | 360    | 20  |        | 311   | 20  | _        | 311   | 20  |     | 311   | 20  | _   | 265   | Mbps |

|                                                  | ×1                                       | 10  | _   | 360    | 10  |        | 311   | 10  | _        | 311   | 10  |     | 311   | 10  | _   | 265   | Mbps |

| t <sub>DUTY</sub>                                | _                                        | 45  |     | 55     | 45  |        | 55    | 45  | _        | 55    | 45  |     | 55    | 45  | _   | 55    | %    |

| Transmitter channel-to-channel skew (TCCS)       | _                                        | _   | _   | 200    | _   | _      | 200   | _   | _        | 200   | _   | _   | 200   | _   | _   | 200   | ps   |

| Output jitter<br>(peak to peak)                  | _                                        | _   | _   | 500    | _   | _      | 500   | _   | _        | 550   | _   | _   | 600   | _   | _   | 700   | ps   |

| t <sub>RISE</sub>                                | 20 – 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _      | _   | 500    | _     | _   | 500      | _     | _   | 500 | —     | _   | 500 | —     | ps   |

| t <sub>FALL</sub>                                | 20 – 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _      | _   | 500    | 1     |     | 500      | _     | _   | 500 | ı     | _   | 500 |       | ps   |