#### Intel - EP4CE30F29I8L Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 1803                                                     |

| Number of Logic Elements/Cells | 28848                                                    |

| Total RAM Bits                 | 608256                                                   |

| Number of I/O                  | 532                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 780-BGA                                                  |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce30f29i8l |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Manual Clock Switchover                     | 5–30 |

|---------------------------------------------|------|

| Guidelines                                  | 5–30 |

| Programmable Bandwidth                      | 5–32 |

| Phase Shift Implementation                  | 5–32 |

| PLL Cascading                               | 5–33 |

| PLL Reconfiguration                         | 5–34 |

| PLL Reconfiguration Hardware Implementation | 5–34 |

| Post-Scale Counters (C0 to C4)              | 5–36 |

| Scan Chain Description                      | 5–37 |

| Charge Pump and Loop Filter                 | 5–38 |

| Bypassing a PLL Counter                     | 5–39 |

| Dynamic Phase Shifting                      | 5–39 |

| Spread-Spectrum Clocking                    | 5–41 |

| PLL Specifications                          | 5–41 |

| Document Revision History                   | 5–42 |

## Section II. I/O Interfaces

| Chapter 6. I/O Features in Cyclone IV Devi |

|--------------------------------------------|

|--------------------------------------------|

| Cyclone IV I/O Elements                                              |      |

|----------------------------------------------------------------------|------|

| I/O Element Features                                                 |      |

| Programmable Current Strength                                        | 6–3  |

| Slew Rate Control                                                    | 6–4  |

| Open-Drain Output                                                    |      |

| Bus Hold                                                             |      |

| Programmable Pull-Up Resistor                                        |      |

| Programmable Delay                                                   |      |

| PCI-Clamp Diode                                                      |      |

| OCT Support                                                          |      |

| On-Chip Series Termination with Calibration                          |      |

| On-Chip Series Termination Without Calibration                       |      |

| I/O Standards                                                        |      |

| Termination Scheme for I/O Standards                                 |      |

| Voltage-Referenced I/O Standard Termination                          | 6–14 |

| Differential I/O Standard Termination                                |      |

| I/O Banks                                                            |      |

| High-Speed Differential Interfaces                                   |      |

| External Memory Interfacing                                          |      |

| Pad Placement and DC Guidelines                                      |      |

| Pad Placement                                                        |      |

| DC Guidelines                                                        |      |

| Clock Pins Functionality                                             |      |

| High-Speed I/O Interface                                             |      |

| High-Speed I/O Standards Support                                     |      |

| High Speed Serial Interface (HSSI) Input Reference Clock Support     |      |

| LVDS I/O Standard Support in Cyclone IV Devices                      | 6–29 |

| Designing with LVDS                                                  |      |

| BLVDS I/O Standard Support in Cyclone IV Devices                     |      |

| Designing with BLVDS                                                 |      |

| RSDS, Mini-LVDS, and PPDS I/O Standard Support in Cyclone IV Devices |      |

| Designing with RSDS, Mini-LVDS, and PPDS                             |      |

| LVPECL I/O Support in Cyclone IV Devices                             |      |

| Differential SSTL I/O Standard Support in Cyclone IV Devices         |      |

|                                                                      |      |

# **Cyclone IV Device Family Architecture**

This section describes Cyclone IV device architecture and contains the following topics:

- "FPGA Core Fabric"

- "I/O Features"

- "Clock Management"

- "External Memory Interfaces"

- "Configuration"

- "High-Speed Transceivers (Cyclone IV GX Devices Only)"

- "Hard IP for PCI Express (Cyclone IV GX Devices Only)"

### **FPGA Core Fabric**

Cyclone IV devices leverage the same core fabric as the very successful Cyclone series devices. The fabric consists of LEs, made of 4-input look up tables (LUTs), memory blocks, and multipliers.

Each Cyclone IV device M9K memory block provides 9 Kbits of embedded SRAM memory. You can configure the M9K blocks as single port, simple dual port, or true dual port RAM, as well as FIFO buffers or ROM. They can also be configured to implement any of the data widths in Table 1–7.

### Table 1–7. M9K Block Data Widths for Cyclone IV Device Family

| Mode                            | Data Width Configurations            |

|---------------------------------|--------------------------------------|

| Single port or simple dual port | ×1, ×2, ×4, ×8/9, ×16/18, and ×32/36 |

| True dual port                  | ×1, ×2, ×4, ×8/9, and ×16/18         |

The multiplier architecture in Cyclone IV devices is the same as in the existing Cyclone series devices. The embedded multiplier blocks can implement an 18 × 18 or two 9 × 9 multipliers in a single block. Altera offers a complete suite of DSP IP including finite impulse response (FIR), fast Fourier transform (FFT), and numerically controlled oscillator (NCO) functions for use with the multiplier blocks. The Quartus<sup>®</sup> II design software's DSP Builder tool integrates MathWorks Simulink and MATLAB design environments for a streamlined DSP design flow.

For more information, refer to the *Logic Elements and Logic Array Blocks in Cyclone IV Devices*, *Memory Blocks in Cyclone IV Devices*, and *Embedded Multipliers in Cyclone IV Devices* chapters.

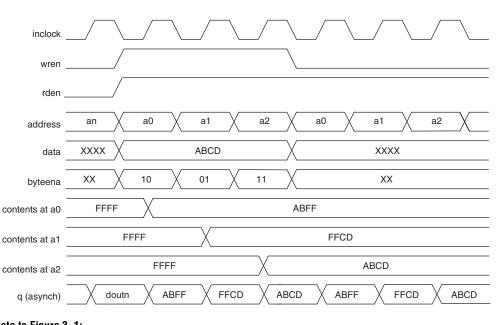

Figure 3–1 shows how the wren and byteena signals control the RAM operations.

Figure 3–1. Cyclone IV Devices byteena Functional Waveform <sup>(1)</sup>

When a byteena bit is deasserted during a write cycle, the old data in the memory appears in the corresponding data-byte output. When a byteena bit is asserted during a write cycle, the corresponding data-byte output depends on the setting chosen in the Quartus<sup>®</sup> II software. The setting can either be the newly written data or the old data at that location.

P

<sup>2</sup> Byte enables are only supported for True Dual-Port memory configurations when both the PortA and PortB data widths of the individual M9K memory blocks are multiples of 8 or 9 bits.

### **Packed Mode Support**

Cyclone IV devices M9K memory blocks support packed mode. You can implement two single-port memory blocks in a single block under the following conditions:

- Each of the two independent block sizes is less than or equal to half of the M9K block size. The maximum data width for each independent block is 18 bits wide.

- Each of the single-port memory blocks is configured in single-clock mode. For more information about packed mode support, refer to "Single-Port Mode" on page 3–8 and "Single-Clock Mode" on page 3–15.

Note to Figure 3-1:

<sup>(1)</sup> For this functional waveform, New Data mode is selected.

# **18-Bit Multipliers**

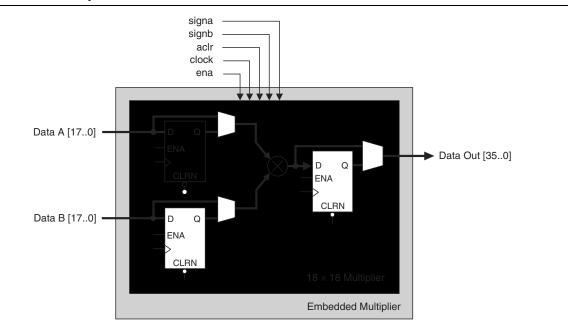

You can configure each embedded multiplier to support a single  $18 \times 18$  multiplier for input widths of 10 to 18 bits.

Figure 4–3 shows the embedded multiplier configured to support an 18-bit multiplier.

Figure 4–3. 18-Bit Multiplier Mode

All 18-bit multiplier inputs and results are independently sent through registers. The multiplier inputs can accept signed integers, unsigned integers, or a combination of both. Also, you can dynamically change the signa and signb signals and send these signals through dedicated input registers.

For more information about the number of GCLK networks in each device density, refer to the *Cyclone IV FPGA Device Family Overview* chapter.

## **GCLK Network**

GCLKs drive throughout the entire device, feeding all device quadrants. All resources in the device (I/O elements, logic array blocks (LABs), dedicated multiplier blocks, and M9K memory blocks) can use GCLKs as clock sources. Use these clock network resources for control signals, such as clock enables and clears fed by an external pin. Internal logic can also drive GCLKs for internally generated GCLKs and asynchronous clears, clock enables, or other control signals with high fan-out.

Table 5–1, Table 5–2 on page 5–4, and Table 5–3 on page 5–7 list the connectivity of the clock sources to the GCLK networks.

Table 5-1. GCLK Network Connections for EP4CGX15, EP4CGX22, and EP4CGX30<sup>(1), (2)</sup> (Part 1 of 2)

| GCLK Network Clock            |              | GCLK Networks |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

|-------------------------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Sources                       | 0            | 1             | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           |

| CLK4/DIFFCLK_2n               |              | —             | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            |

| CLK5/DIFFCLK_2p               |              | —             |              | —            |              | —            | $\checkmark$ | $\checkmark$ | —            | —            |              |              | —            |              |              |              |              | —            |              | —            |

| CLK6/DIFFCLK_3n               | _            | —             | —            | —            |              | —            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              | —            | —            |              | —            |              |              | —            |              | —            |

| CLK7/DIFFCLK_3p               |              | —             |              | —            |              | $\checkmark$ |              |              | $\checkmark$ |              |              |              | —            | _            |              | _            |              |              | —            | —            |

| CLK8/DIFFCLK_5n               |              | —             |              | _            |              |              |              |              |              |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              |              |              |              | —            |

| CLK9/DIFFCLK_5p               | —            | —             |              | —            | —            | —            |              | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | _            |              | _            | —            | —            | —            | —            |

| CLK10/DIFFCLK_4n/RE<br>FCLK1n | _            | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | ~            | _            | ~            | ~            | _            | _            | _            | _            | —            |

| CLK11/DIFFCLK_4p/RE<br>FCLK1p | _            | _             | _            |              |              | _            |              |              | _            | _            | ~            |              | _            | ~            |              | _            |              | _            |              | —            |

| CLK12/DIFFCLK_7p/RE<br>FCLK0p | _            |               | _            |              | _            | _            | _            | _            | _            | _            | _            | _            | _            |              | _            | $\checkmark$ | _            | ~            | _            | ~            |

| CLK13/DIFFCLK_7n/RE<br>FCLK0n | _            | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            |              | _            |              | ~            | ~            | _            | —            |

| CLK14/DIFFCLK_6p              |              | —             |              | —            |              | _            |              |              |              |              |              |              | —            | _            |              | _            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| CLK15/DIFFCLK_6n              |              | —             | —            | —            | _            | —            | —            |              | —            |              |              | —            | —            | _            | —            | $\checkmark$ | _            | —            | $\checkmark$ | —            |

| PLL_1_C0                      | $\checkmark$ | _             |              | $\checkmark$ |              |              |              |              |              |              |              |              |              |              |              | >            |              |              | $\checkmark$ | —            |

| PLL_1_C1                      |              | <b>~</b>      | _            |              | >            | _            |              |              | _            | _            | _            |              | _            |              |              |              | >            | _            |              | $\checkmark$ |

| PLL_1_C2                      | $\checkmark$ | —             | $\checkmark$ | —            | _            | —            |              |              | —            | —            | —            |              | —            |              |              | >            | _            | $\checkmark$ | _            | —            |

| PLL_1_C3                      |              | <b>~</b>      | _            | $\checkmark$ |              | _            |              |              | _            | _            | _            |              | _            |              |              |              | >            | _            | >            | —            |

| PLL_1_C4                      |              | _             | $\checkmark$ |              | >            |              |              |              | _            |              |              |              |              |              |              |              |              | $\checkmark$ |              | $\checkmark$ |

| PLL_2_C0                      | $\checkmark$ | —             |              | $\checkmark$ |              |              |              |              |              |              | $\checkmark$ |              |              | $\checkmark$ |              | _            |              |              | —            | —            |

| PLL_2_C1                      |              | $\checkmark$  |              | —            | $\checkmark$ | —            |              |              | —            |              |              | $\checkmark$ | —            | _            | $\checkmark$ | _            | _            | —            | —            | —            |

| PLL_2_C2                      | $\checkmark$ | —             | $\checkmark$ |              |              |              |              |              |              |              | $\checkmark$ |              | $\checkmark$ | _            |              | _            |              |              | —            | —            |

| PLL_2_C3                      | —            | $\checkmark$  | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | _            | >            | —            | —            | —            | —            | —            | —            |

| PLL_2_C4                      | _            | —             | $\checkmark$ | —            | $\checkmark$ | —            | —            |              | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            |

| PLL_3_C0                      | —            | —             | —            | —            | _            | $\checkmark$ | —            | —            | ~            | —            | —            | —            | —            | _            | —            | >            | _            | —            | $\checkmark$ | —            |

- When using manual clock switchover, the difference between inclk0 and inclk1 can be more than 20%. However, differences between the two clock sources (frequency, phase, or both) can cause the PLL to lose lock. Resetting the PLL ensures that the correct phase relationships are maintained between the input and output clocks.

- Both inclk0 and inclk1 must be running when the clkswitch signal goes high to start the manual clock switchover event. Failing to meet this requirement causes the clock switchover to malfunction.

- Applications that require a clock switchover feature and a small frequency drift must use a low-bandwidth PLL. When referencing input clock changes, the low-bandwidth PLL reacts slower than a high-bandwidth PLL. When the switchover happens, the low-bandwidth PLL propagates the stopping of the clock to the output slower than the high-bandwidth PLL. The low-bandwidth PLL filters out jitter on the reference clock. However, the low-bandwidth PLL also increases lock time.

- After a switchover occurs, there may be a finite resynchronization period for the PLL to lock onto a new clock. The exact amount of time it takes for the PLL to re-lock is dependent on the PLL configuration.

- If the phase relationship between the input clock to the PLL and output clock from the PLL is important in your design, assert areset for 10 ns after performing a clock switchover. Wait for the locked signal (or gated lock) to go high before re-enabling the output clocks from the PLL.

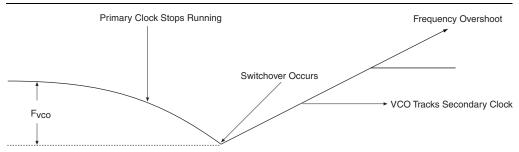

- Figure 5–20 shows how the VCO frequency gradually decreases when the primary clock is lost and then increases as the VCO locks on to the secondary clock. After the VCO locks on to the secondary clock, some overshoot can occur (an over-frequency condition) in the VCO frequency.

#### Figure 5–20. VCO Switchover Operating Frequency

Disable the system during switchover if the system is not tolerant to frequency variations during the PLL resynchronization period. You can use the clkbad0 and clkbad1 status signals to turn off the PFD (pfdena = 0) so the VCO maintains its last frequency. You can also use the switchover state machine to switch over to the secondary clock. Upon enabling the PFD, output clock enable signals (clkena) can disable clock outputs during the switchover and resynchronization period. After the lock indication is stable, the system can re-enable the output clock or clocks.

The CLKIN/REFCLK pins are powered by dedicated V<sub>CC\_CLKIN3A</sub>, V<sub>CC\_CLKIN3B</sub>, V<sub>CC\_CLKIN3B</sub>, v<sub>CC\_CLKIN8A</sub>, and V<sub>CC\_CLKIN8B</sub> power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for GPIO.

|                          |               |                              |             | VCC_C | LKIN Level       |               | l/0 Pin    | Туре                   |

|--------------------------|---------------|------------------------------|-------------|-------|------------------|---------------|------------|------------------------|

| I/O Standard H           | HSSI Protocol | Coupling                     | Termination | Input | Output           | Column<br>I/O | Row<br>I/O | Supported I/O<br>Banks |

| LVDS                     | All           |                              | Off chip    | 2.5V  | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

| LVPECL                   | All           | Differential<br>AC (Need     | Off chip    | 2.5V  | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

|                          | All           | off chip resistor to         | Off chip    | 2.5V  | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

| 1.2V, 1.5V,<br>3.3V PCML | All           | restore<br>V <sub>CM</sub> ) | Off chip    | 2.5V  | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

|                          | All           |                              | Off chip    | 2.5V  | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

| HCSL                     | PCIe          | Differential<br>DC           | Off chip    | 2.5V  | Not<br>supported | Yes           | No         | 3A, 3B, 8A, 8B         |

Table 6–10. Cyclone IV GX HSSI REFCLK I/O Standard Support Using GPIO CLKIN Pins (1), (2)

Notes to Table 6-10:

(1) The EP4CGX15, EP4CGX22, and EP4CGX30 devices have two pairs of dedicated clock input pins in banks 3A and 8A for HSSI input reference clock. I/O banks 3B and 8B are not available in EP4CGX15, EP4CGX22, and EP4CGX30 devices.

(2) The EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices have four pairs of dedicated clock input pins in banks 3A, 3B, 8A, and 8B for HSSI input or single-ended clock input.

**To** For more information about the AC-coupled termination scheme for the HSSI reference clock, refer to the *Cyclone IV Transceivers Architecture* chapter.

## LVDS I/O Standard Support in Cyclone IV Devices

The LVDS I/O standard is a high-speed, low-voltage swing, low power, and GPIO interface standard. Cyclone IV devices meet the ANSI/TIA/EIA-644 standard with the following exceptions:

- The maximum differential output voltage (V<sub>OD</sub>) is increased to 600 mV. The maximum V<sub>OD</sub> for ANSI specification is 450 mV.

- The input voltage range is reduced to the range of 1.0 V to 1.6 V, 0.5 V to 1.85 V, or 0 V to 1.8 V based on different frequency ranges. The ANSI/TIA/EIA-644 specification supports an input voltage range of 0 V to 2.4 V.

- For LVDS I/O standard electrical specifications in Cyclone IV devices, refer to the *Cyclone IV Device Datasheet* chapter.

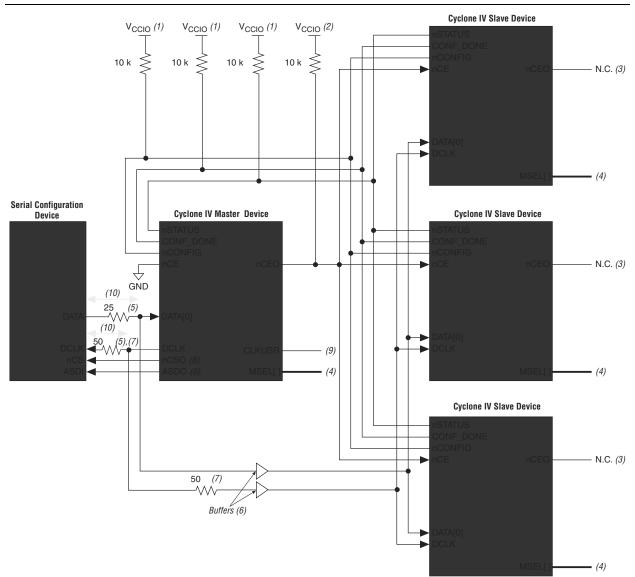

#### Figure 8-4. Multi-Device AS Configuration in Which Devices Receive the Same Data with Multiple .sof

#### Notes to Figure 8-4:

- (1) Connect the pull-up resistors to the V<sub>CCIO</sub> supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device in AS mode and the slave devices in PS mode. To connect the MSEL pins for the master device in AS mode and the slave devices in PS mode, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) Connect the series resistor at the near end of the serial configuration device.

- (6) Connect the repeater buffers between the master and slave devices for DATA[0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (7) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

- (8) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (9) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- (10) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration device to the junction-split on both DCLK and Data0 line is 3.5 inches.

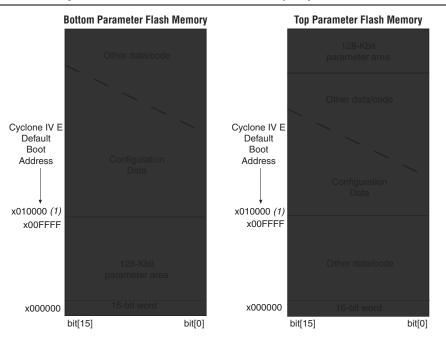

The default configuration boot address allows the system to use special parameter blocks in the flash memory map. Parameter blocks are at the top or bottom of the memory map. Figure 8–12 shows the configuration boot address in the AP configuration scheme. You can change the default configuration default boot address 0×010000 to any desired address using the APFC\_BOOT\_ADDR\_JTAG instruction. For more information about the APFC\_BOOT\_ADDR\_JTAG instruction, refer to "JTAG Instructions" on page 8–57.

#### Note to Figure 8-12:

(1) The default configuration boot address is x010000 when represented in 16-bit word addressing.

### **PS Configuration**

You can perform PS configuration on Cyclone IV devices with an external intelligent host, such as a MAX<sup>®</sup> II device, microprocessor with flash memory, or a download cable. In the PS scheme, an external host controls the configuration. Configuration data is clocked into the target Cyclone IV device through DATA[0] at each rising edge of DCLK.

If your system already contains a common flash interface (CFI) flash memory, you can use it for Cyclone IV device configuration storage as well. The MAX II PFL feature provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control the configuration from the flash memory device to the Cyclone IV device.

**Tor** For more information about the PFL, refer to *AN* 386: Using the Parallel Flash Loader with the Quartus II Software.

Cyclone IV devices do not support enhanced configuration devices for PS configuration.

### **PS Configuration Using an External Host**

In the PS configuration scheme, you can use an intelligent host such as a MAX II device or microprocessor that controls the transfer of configuration data from a storage device, such as flash memory, to the target Cyclone IV device. You can store the configuration data in **.rbf**, **.hex**, or **.ttf** format.

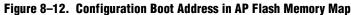

Figure 8–13 shows the configuration interface connections between a Cyclone IV device and an external host device for single-device configuration.

Figure 8–13. Single-Device PS Configuration Using an External Host

#### Notes to Figure 8-13:

- (1) Connect the pull-up resistor to a supply that provides an acceptable input signal for the device.  $V_{CC}$  must be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

- (2) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

To begin the configuration, the external host device must generate a low-to-high transition on the nCONFIG pin. When nSTATUS is pulled high, the external host device must place the configuration data one bit at a time on DATA[0]. If you use configuration data in **.rbf**, **.ttf**, or **.hex**, you must first send the LSB of each data byte. For example, if the **.rbf** contains the byte sequence 02 1B EE 01 FA, the serial bitstream you must send to the device is:

0100-0000 1101-1000 0111-0111 1000-0000 0101-1111

Cyclone IV devices receive configuration data on DATA[0] and the clock is received on DCLK. Data is latched into the device on the rising edge of DCLK. Data is continuously clocked into the target device until CONF\_DONE goes high and the device enters initialization state.

Two DCLK falling edges are required after CONF\_DONE goes high to begin the initialization of the device.

INIT\_DONE is released and pulled high when initialization is complete. The external host device must be able to detect this low-to-high transition which signals the device has entered user mode. When initialization is complete, the device enters user mode. In user mode, the user I/O pins no longer have weak pull-up resistors and function as assigned in your design.

| Table 11–1. Power Supply Descriptions for the Cyclone IV GX Devices (Part 2 of 2) |

|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------|

| Power Supply Pin | Nominal Voltage Level (V) | Description                                |

|------------------|---------------------------|--------------------------------------------|

| VCCL_GXB         | 1.2                       | Transceiver PMA and auxiliary power supply |

Notes to Table 11-1:

(1) You must power up VCCA even if the phase-locked loop (PLL) is not used.

(2) I/O banks 3, 8, and 9 contain configuration pins. You can only power up the  $V_{CCIO}$  level of I/O banks 3 and 9 to 1.5 V, 1.8 V, 2.5 V, 3.0 V, or 3.3 V. For Fast Passive Parallel (FPP) configuration mode, you must power up the  $V_{CCIO}$  level of I/O bank 8 to 1.5 V, 1.8 V, 2.5 V, 3.0 V, or 3.3 V.

(3) All device packages of EP4CGX15, EP4CGX22, and device package F169 and F324 of EP4CGX30 devices have two VCC\_CLKIN dedicated clock input I/O located at Banks 3A and 8A. Device package F484 of EP4CGX30, all device packages of EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices have four VCC\_CLKIN dedicated clock input I/O bank located at banks 3A, 3B, 8A, and 8B.

(4) You must set VCC\_CLKIN to 2.5V if the CLKIN is used as a high-speed serial interface (HSSI) transceiver refclk. When not used as a transceiver refclk, VCC\_CLKIN supports 1.2 V/ 1.5 V/ 1.8 V/ 2.5 V/ 3.0 V/ 3.3V voltages.

| Power Supply Pin | Nominal Voltage Level (V)    | Description               |

|------------------|------------------------------|---------------------------|

| VCCINT           | 1.0, 1.2                     | Core voltage power supply |

| VCCA (1)         | 2.5                          | PLL analog power supply   |

| VCCD_PLL         | 1.0, 1.2                     | PLL digital power supply  |

| VCCIO (2)        | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | I/O banks power supply    |

Table 11–2. Power Supply Descriptions for the Cyclone IV E Devices

#### Notes to Table 11-2:

(1) You must power up VCCA even if the PLL is not used.

(2) I/O banks 1, 6, 7, and 8 contain configuration pins.

# **Hot-Socketing Specifications**

Cyclone IV devices are hot-socketing compliant without the need for any external components or special design requirements. Hot-socketing support in Cyclone IV devices has the following advantages:

- You can drive the device before power up without damaging the device.

- I/O pins remain tri-stated during power up. The device does not drive out before or during power-up. Therefore, it does not affect other buses in operation.

### **Devices Driven Before Power-Up**

You can drive signals into regular Cyclone IV E I/O pins and transceiver Cyclone IV GX I/O pins before or during power up or power down without damaging the device. Cyclone IV devices support any power-up or power-down sequence to simplify system-level designs.

### I/O Pins Remain Tri-stated During Power-Up

The output buffers of Cyclone IV devices are turned off during system power up or power down. Cyclone IV devices do not drive out until the device is configured and working in recommended operating conditions. The I/O pins are tri-stated until the device enters user mode.

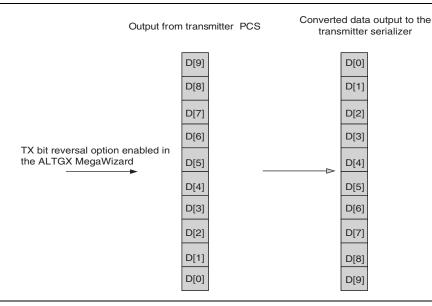

Bit reversal—reverses the transmit bit order from LSB-to-MSB (default) to MSB-to-LSB at the input to the serializer. For example, input data to serializer D[7..0] is rewired to D[0..7] for 8-bit data width, and D[9..0] is rewired to D[0..9] for 10-bit data width. Figure 1–10 shows the transmitter bit reversal feature.

Figure 1–10. Transmitter Bit Reversal Operation in Basic Single-Width Mode

- Input bit-flip—reverses the bit order at a byte level at the input of the transmitter phase compensation FIFO. For example, if the 16-bit parallel transmitter data at the tx\_datain port is '10111100 10101101' (16'hBCAD), selecting this option reverses the input data to the transmitter phase compensation FIFO to '00111101 10110101' (16'h3DB5).

- Bit-slip control—delays the data transmission by a number of specified bits to the serializer with the tx\_bitslipboundaryselect port. For usage details, refer to the "Transmit Bit-Slip Control" on page 1–76.

### Serializer

The serializer converts the low-speed parallel 8-bit or 10-bit data from the transmitter PCS to high-speed serial data for the transmitter output buffer. The serializer operates with a high-speed clock at half of the serial data rate. The serializer transmission sequence is LSB to MSB.

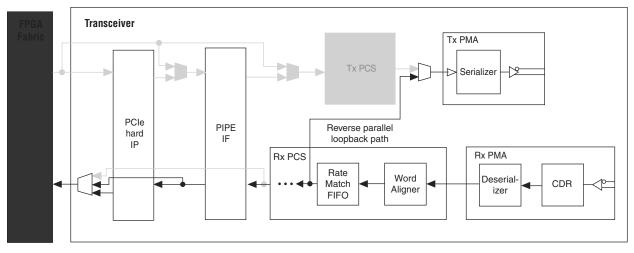

### **Reverse Parallel Loopback**

The reverse parallel loopback option is only available for PIPE mode. In this mode, the received serial data passes through the receiver CDR, deserializer, word aligner, and rate match FIFO before looping back to the transmitter serializer and transmitted out through the TX buffer, as shown in Figure 1–70. The received data is also available to the FPGA fabric. This loopback mode is compliant with version 2.00 of the *PHY Interface for the PCI Express Architecture* specification.

To enable the reverse parallel loopback mode, assert the tx\_detectrxloopback port in P0 power state.

Figure 1–70. PIPE Reverse Parallel Loopback Path (1)

Note to Figure 1–70: (1) Grayed-Out Blocks are Not Active in this mode.

## **Serial Loopback**

The serial loopback option is available for all functional modes except PIPE mode. In this mode, the data from the FPGA fabric passes through the transmitter channel and looped back to the receiver channel, bypassing the receiver buffer, as shown in Figure 1–71. The received data is available to the FPGA logic for verification. The receiver input buffer is not active in this mode. With this option, you can check the operation of all enabled PCS and PMA functional blocks in the transmitter and receiver channels.

The transmitter channel sends the data to both the serial output port and the receiver channel. The differential output voltage on the serial ports is based on the selected  $V_{OD}$  settings. The data is looped back to the receiver CDR and is retimed through different clock domains. You must provide an alignment pattern for the word aligner to enable the receiver channel to retrieve the byte boundary.

| Transceiver Block                        | rx_digitalreset | rx_analogreset | tx_digitalreset | pll_areset | gxb_powerdown |

|------------------------------------------|-----------------|----------------|-----------------|------------|---------------|

| Serializer                               | —               |                | $\checkmark$    |            | $\checkmark$  |

| Transmitter Buffer                       | —               |                | —               | _          | $\checkmark$  |

| Transmitter XAUI State<br>Machine        | —               | —              | ~               | _          | ~             |

| Receiver Buffer                          | —               |                | —               | _          | $\checkmark$  |

| Receiver CDR                             | —               | $\checkmark$   | —               | —          | $\checkmark$  |

| Receiver Deserializer                    | _               |                | —               |            | $\checkmark$  |

| Receiver Word Aligner                    | $\checkmark$    |                | —               | _          | $\checkmark$  |

| Receiver Deskew FIFO                     | $\checkmark$    |                | —               | —          | $\checkmark$  |

| Receiver Clock Rate<br>Compensation FIFO | ~               | _              | —               | _          | ~             |

| Receiver 8B/10B<br>Decoder               | ~               | _              | _               | _          | ~             |

| Receiver Byte<br>Deserializer            | ~               | _              | —               | _          | ~             |

| Receiver Byte Ordering                   | $\checkmark$    | —              | —               | —          | $\checkmark$  |

| Receiver Phase<br>Compensation FIFO      | ~               | _              | _               | _          | ~             |

| Receiver XAUI State<br>Machine           | ~               | —              | —               | _          | ~             |

| BIST Verifiers                           | $\checkmark$    | —              | —               | —          | $\checkmark$  |

Table 2–3. Blocks Affected by Reset and Power-Down Signals (Part 2 of 2)

# **Transceiver Reset Sequences**

You can configure transceiver channels in Cyclone IV GX devices in various configurations. In all functional modes except XAUI functional mode, transceiver channels can be either bonded or non-bonded. In XAUI functional mode, transceiver channels must be bonded. In PCI Express<sup>®</sup> (PCIe<sup>®</sup>) functional mode, transceiver channels can be either bonded or non-bonded and need to follow a specific reset sequence.

The two categories of reset sequences for Cyclone IV GX devices described in this chapter are:

- "All Supported Functional Modes Except the PCIe Functional Mode" on page 2–6—describes the reset sequences in bonded and non-bonded configurations.

- "PCIe Functional Mode" on page 2–17—describes the reset sequence for the initialization/compliance phase and the normal operation phase in PCIe functional modes.

# 3. Cyclone IV Dynamic Reconfiguration

Cyclone<sup>®</sup> IV GX transceivers allow you to dynamically reconfigure different portions of the transceivers without powering down any part of the device. This chapter describes and provides examples about the different modes available for dynamic reconfiguration.

You can use the ALTGX\_RECONFIG and ALTPLL\_RECONFIG controller instance to reconfigure the physical medium attachment (PMA) controls, physical coding sublayer (PCS), multipurpose phase locked loops (PLLs), and general purpose PLLs.

This chapter contains the following sections:

- "Glossary of Terms" on page 3–1

- "Dynamic Reconfiguration Controller Architecture" on page 3–2

- "Dynamic Reconfiguration Modes" on page 3–12

- "Error Indication During Dynamic Reconfiguration" on page 3–36

- "Functional Simulation of the Dynamic Reconfiguration Process" on page 3–37

# **Glossary of Terms**

Table 3–1 lists the terms used in this chapter:

| Table 3-1. | <b>Glossary</b> of | <b>Terms Used in</b> | this Chapter | (Part 1 of 2) |

|------------|--------------------|----------------------|--------------|---------------|

|------------|--------------------|----------------------|--------------|---------------|

| Term                                                                                   | Description                                                                                                                                                                                    |  |  |  |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ALTGX_RECONFIG Instance                                                                | Dynamic reconfiguration controller instance generated by the ALTGX_RECONFIG MegaWizard <sup>™</sup> Plug-In Manager.                                                                           |  |  |  |

| ALTGX Instance Transceiver instance generated by the ALTGX MegaWizard Plug-In Manager. |                                                                                                                                                                                                |  |  |  |

| ALTPLL_RECONFIG Instance                                                               | Dynamic PLL reconfiguration controller instance generated by the ALTPLL_RECONFIG Megawizard Plug-In Manager                                                                                    |  |  |  |

| Logical Channel Addressing                                                             | Used whenever the concept of logical channel addressing is explained. This term does not refer to the logical_channel_address port available in the ALTGX_RECONFIG MegaWizard Plug-In Manager. |  |  |  |

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

There are three methods that you can use to dynamically reconfigure the PMA controls of a transceiver channel:

- "Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels" on page 3–14

- "Method 2: Writing the Same Control Signals to Control All the Transceiver Channels" on page 3–16

- "Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same Time" on page 3–19

# Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels

Enable the logical\_channel\_address port by selecting the **Use** 'logical\_channel\_address' port option on the **Analog controls** tab. This method is applicable only for a design where the dynamic reconfiguration controller controls more than one channel.

You can additionally reconfigure either the receiver portion, transmitter portion, or both the receiver and transmitter portions of the transceiver channel by setting the corresponding value on the rx\_tx\_duplex\_sel input port. For more information, refer to Table 3–2 on page 3–4.

#### **Connecting the PMA Control Ports**

The selected PMA control ports remain fixed in width, regardless of the number of channels controlled by the ALTGX\_RECONFIG instance:

- tx\_vodctrl and tx\_vodctrl\_out are fixed to 3 bits

- tx preemp and tx preemp out are fixed to 5 bits

- rx\_eqdcgain and rx\_eqdcgain\_out are fixed to 2 bits

- rx\_eqctrl and rx\_eqctrl\_out are fixed to 4 bits

#### Write Transaction

To complete a write transaction, perform the following steps:

- Set the selected PMA control ports to the desired settings (for example, tx\_vodctrl = 3'b001).

- 2. Set the logical\_channel\_address input port to the logical channel address of the transceiver channel whose PMA controls you want to reconfigure.

- 3. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 4. Ensure that the busy signal is low before you start a write transaction.

- 5. Assert the write\_all signal for one reconfig\_clk clock cycle.

The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

# **DC Characteristics**

This section lists the I/O leakage current, pin capacitance, on-chip termination (OCT) tolerance, and bus hold specifications for Cyclone IV devices.

### **Supply Current**

The device supply current requirement is the minimum current drawn from the power supply pins that can be used as a reference for power size planning. Use the Excel-based early power estimator (EPE) to get the supply current estimates for your design because these currents vary greatly with the resources used. Table 1–6 lists the I/O pin leakage current for Cyclone IV devices.

Table 1–6. I/O Pin Leakage Current for Cyclone IV Devices (1), (2)

| Symbol          | Parameter                            | Conditions                                 | Device | Min | Тур | Max | Unit |

|-----------------|--------------------------------------|--------------------------------------------|--------|-----|-----|-----|------|

| I <sub>I</sub>  | Input pin leakage current            | $V_I = 0 V \text{ to } V_{\text{CCIOMAX}}$ | —      | -10 | _   | 10  | μA   |

| I <sub>OZ</sub> | Tristated I/O pin leakage<br>current | $V_0 = 0 V$ to $V_{CCIOMAX}$               | _      | -10 | _   | 10  | μA   |

Notes to Table 1-6:

(1) This value is specified for normal device operation. The value varies during device power-up. This applies for all V<sub>CCI0</sub> settings (3.3, 3.0, 2.5, 1.8, 1.5, and 1.2 V).

(2) The 10  $\mu$ A I/O leakage current limit is applicable when the internal clamping diode is off. A higher current can be observed when the diode is on.

### **Bus Hold**

The bus hold retains the last valid logic state after the source driving it either enters the high impedance state or is removed. Each I/O pin has an option to enable bus hold in user mode. Bus hold is always disabled in configuration mode.

Table 1–7 lists bus hold specifications for Cyclone IV devices.

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 1 of 2)<sup>(1)</sup>

|                                            |                                                | V <sub>CCI0</sub> (V) |      |     |      |     |      |     |      |     |      |     |      |      |

|--------------------------------------------|------------------------------------------------|-----------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                  | Condition                                      | 1.2                   |      | 1.5 |      | 1.8 |      | 2.5 |      | 3.0 |      | 3.3 |      | Unit |

|                                            |                                                | Min                   | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus hold<br>low,<br>sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 8                     | _    | 12  | _    | 30  | _    | 50  | _    | 70  | _    | 70  | _    | μА   |

| Bus hold<br>high,<br>sustaining<br>current | V <sub>IN</sub> < V <sub>IL</sub><br>(minimum) | -8                    | _    | -12 | _    | -30 | _    | -50 | _    | -70 | _    | -70 | _    | μА   |

| Bus hold<br>low,<br>overdrive<br>current   | $0 V < V_{IN} < V_{CCIO}$                      | _                     | 125  |     | 175  | _   | 200  | _   | 300  | _   | 500  | _   | 500  | μA   |

| Bus hold<br>high,<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |                       | -125 | _   | -175 |     | -200 |     | -300 |     | -500 |     | -500 | μА   |

| Symbol                                                 | Parameter                                                                                                                      |    | Тур     | Max  | Unit              |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----|---------|------|-------------------|

| t <sub>dlock</sub>                                     | Time required to lock dynamically (after switchover, reconfiguring any non-post-scale counters/delays or areset is deasserted) |    | _       | 1    | ms                |

| t <sub>outjitter_period_dedclk</sub> (6)               | Dedicated clock output period jitter $F_{OUT} \ge 100 \text{ MHz}$                                                             | _  | _       | 300  | ps                |

|                                                        | F <sub>OUT</sub> < 100 MHz                                                                                                     | _  | _       | 30   | mUI               |

| t <sub>outjitter_ccj_dedclk</sub> <i>(6)</i>           | Dedicated clock output cycle-to-cycle jitter $F_{OUT} \ge 100 \text{ MHz}$                                                     | _  | _       | 300  | ps                |

|                                                        | F <sub>OUT</sub> < 100 MHz                                                                                                     | _  | _       | 30   | mUI               |

| t <sub>outjitter_period_10</sub> (6)                   | Regular I/O period jitter<br>F <sub>OUT</sub> ≥ 100 MHz                                                                        | _  | _       | 650  | ps                |

|                                                        | F <sub>OUT</sub> < 100 MHz                                                                                                     | —  |         | 75   | mUI               |

| t <sub>outjitter_ccj_io</sub> <i>(6)</i>               | Regular I/O cycle-to-cycle jitter $F_{OUT} \ge 100 \text{ MHz}$                                                                | _  | _       | 650  | ps                |

|                                                        | F <sub>OUT</sub> < 100 MHz                                                                                                     | —  | _       | 75   | mUI               |

| t <sub>PLL_PSERR</sub>                                 | Accuracy of PLL phase shift                                                                                                    | —  |         | ±50  | ps                |

| t <sub>ARESET</sub>                                    | Minimum pulse width on areset signal.                                                                                          | 10 | _       |      | ns                |

| t <sub>CONFIGPLL</sub>                                 | Time required to reconfigure scan chains for PLLs                                                                              |    | 3.5 (7) |      | SCANCLK<br>cycles |

| f <sub>scanclk</sub>                                   | scanclk frequency                                                                                                              | _  | _       | 100  | MHz               |

| t <sub>CASC_OUTJ</sub> ITTER_PERIOD_DEDCLK<br>(8), (9) | Period jitter for dedicated clock output in cascaded PLLs ( $F_{OUT} \ge 100 \text{ MHz}$ )                                    | _  | _       | 425  | ps                |

|                                                        | Period jitter for dedicated clock output in cascaded PLLs ( $F_{OUT}$ < 100 MHz)                                               |    |         | 42.5 | mUI               |

| Table 1-25. | PLL Specifications | for Cyclone IV Devices | <b>5</b> (1), (2) | (Part 2 of 2) |

|-------------|--------------------|------------------------|-------------------|---------------|

|-------------|--------------------|------------------------|-------------------|---------------|

#### Notes to Table 1-25:

- (1) This table is applicable for general purpose PLLs and multipurpose PLLs.

- (2) You must connect  $V_{CCD PLL}$  to  $V_{CCINT}$  through the decoupling capacitor and ferrite bead.

- (3) This parameter is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

- (4) The V<sub>C0</sub> frequency reported by the Quartus II software in the PLL Summary section of the compilation report takes into consideration the V<sub>C0</sub> post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the f<sub>VC0</sub> specification.

- (5) A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source that is less than 200 ps.

- (6) Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.9999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL when an input jitter of 30 ps is applied.

- (7) With 100-MHz scanclk frequency.

(8) The cascaded PLLs specification is applicable only with the following conditions:

- $\blacksquare \quad Upstream \ PLL 0.59 \ MHz \leq Upstream \ PLL \ bandwidth < 1 \ MHz$

- Downstream PLL—Downstream PLL bandwidth > 2 MHz

- (9) PLL cascading is not supported for transceiver applications.