#### Intel - EP4CE40F29C8N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 2475                                                     |

| Number of Logic Elements/Cells | 39600                                                    |

| Total RAM Bits                 | 1161216                                                  |

| Number of I/O                  | 532                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BGA                                                  |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce40f29c8n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Visual Cue                               | Meaning                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input. The suffix n denotes an active-low signal. For example, resetn.                 |

| Courier type                             | Indicates command line commands and anything that must be typed exactly as it appears. For example, c:\qdesigns\tutorial\chiptrip.gdf.                                                 |

|                                          | Also indicates sections of an actual file, such as a Report File, references to parts of files (for example, the AHDL keyword SUBDESIGN), and logic function names (for example, TRI). |

| Ļ                                        | An angled arrow instructs you to press the Enter key.                                                                                                                                  |

| 1., 2., 3., and<br>a., b., c., and so on | Numbered steps indicate a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                          |

|                                          | Bullets indicate a list of items when the sequence of the items is not important.                                                                                                      |

| I                                        | The hand points to information that requires special attention.                                                                                                                        |

| ?                                        | The question mark directs you to a software help system with related information.                                                                                                      |

|                                          | The feet direct you to another document or website with related information.                                                                                                           |

| <b>I</b> , <b>™</b> I                    | The multimedia icon directs you to a related multimedia presentation.                                                                                                                  |

| CAUTION                                  | A caution calls attention to a condition or possible situation that can damage or destroy the product or your work.                                                                    |

| WARNING                                  | A warning calls attention to a condition or possible situation that can cause you injury.                                                                                              |

|                                          | The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents.                 |

- Up to 532 user I/Os

- LVDS interfaces up to 840 Mbps transmitter (Tx), 875 Mbps Rx

- Support for DDR2 SDRAM interfaces up to 200 MHz

- Support for QDRII SRAM and DDR SDRAM up to 167 MHz

- Up to eight phase-locked loops (PLLs) per device

- Offered in commercial and industrial temperature grades

### **Device Resources**

Table 1–1 lists Cyclone IV E device resources.

Table 1–1. Resources for the Cyclone IV E Device Family

| Resources                       | EP4CE6 | EP4CE10 | EP4CE15 | EP4CE22 | EP4CE30 | EP4CE40 | EP4CE55 | EP4CE75 | EP4CE115 |

|---------------------------------|--------|---------|---------|---------|---------|---------|---------|---------|----------|

| Logic elements (LEs)            | 6,272  | 10,320  | 15,408  | 22,320  | 28,848  | 39,600  | 55,856  | 75,408  | 114,480  |

| Embedded memory<br>(Kbits)      | 270    | 414     | 504     | 594     | 594     | 1,134   | 2,340   | 2,745   | 3,888    |

| Embedded 18 × 18<br>multipliers | 15     | 23      | 56      | 66      | 66      | 116     | 154     | 200     | 266      |

| General-purpose PLLs            | 2      | 2       | 4       | 4       | 4       | 4       | 4       | 4       | 4        |

| Global Clock Networks           | 10     | 10      | 20      | 20      | 20      | 20      | 20      | 20      | 20       |

| User I/O Banks                  | 8      | 8       | 8       | 8       | 8       | 8       | 8       | 8       | 8        |

| Maximum user I/O <sup>(1)</sup> | 179    | 179     | 343     | 153     | 532     | 532     | 374     | 426     | 528      |

#### Note to Table 1-1:

(1) The user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins are not included in the pin count.

### **Programmable Bandwidth**

The PLL bandwidth is the measure of the PLL's ability to track the input clock and its associated jitter. PLLs of Cyclone IV devices provide advanced control of the PLL bandwidth using the programmable characteristics of the PLL loop, including loop filter and charge pump. The closed-loop gain 3-dB frequency in the PLL determines the PLL bandwidth. The bandwidth is approximately the unity gain point for open loop PLL response.

### **Phase Shift Implementation**

Phase shift is used to implement a robust solution for clock delays in Cyclone IV devices. Phase shift is implemented with a combination of the VCO phase output and the counter starting time. The VCO phase output and counter starting time are the most accurate methods of inserting delays, because they are based only on counter settings that are independent of process, voltage, and temperature.

You can phase shift the output clocks from the PLLs of Cyclone IV devices in one of two ways:

- Fine resolution using VCO phase taps

- Coarse resolution using counter starting time

Fine resolution phase shifts are implemented by allowing any of the output counters (C[4..0]) or the M counter to use any of the eight phases of the VCO as the reference clock. This allows you to adjust the delay time with a fine resolution.

Equation 5–1 shows the minimum delay time that you can insert using this method.

#### Equation 5–1. Fine Resolution Phase Shift

$f_{\text{fine}} = \frac{T_{VCO}}{8} = \frac{1}{8f_{VCO}} = \frac{N}{8Mf_{REF}}$

in which  $f_{\text{REF}}$  is the input reference clock frequency.

For example, if  $f_{\text{REF}}$  is 100 MHz, N = 1, and M = 8, then  $f_{\text{VCO}}$  = 800 MHz, and  $\Phi_{\text{fine}}$  = 156.25 ps. The PLL operating frequency defines this phase shift, a value that depends on reference clock frequency and counter settings.

Coarse resolution phase shifts are implemented by delaying the start of the counters for a predetermined number of counter clocks. Equation 5–2 shows the coarse phase shift.

#### Equation 5–2. Coarse Resolution Phase Shift

$\Phi_{\text{coarse}} = \frac{C-1}{f_{VCO}} = \frac{(C-1)N}{Mf_{REF}}$

*C* is the count value set for the counter delay time (this is the initial setting in the PLL usage section of the compilation report in the Quartus II software). If the initial value is 1,  $C - 1 = 0^{\circ}$  phase shift.

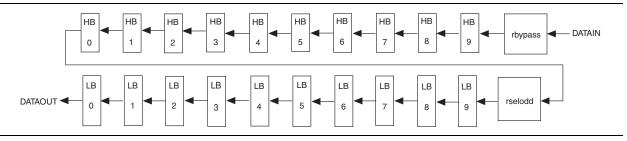

Figure 5–25 shows the scan chain bit order sequence for one PLL post-scale counter in PLLs of Cyclone IV devices.

#### Figure 5–25. Scan Chain Bit Order

### **Charge Pump and Loop Filter**

You can reconfigure the charge pump and loop filter settings to update the PLL bandwidth in real time. Table 5–8 through Table 5–10 list the possible settings for charge pump current ( $I_{CP}$ ), loop filter resistor (R), and capacitor (C) values for PLLs of Cyclone IV devices.

#### Table 5-8. Charge Pump Bit Control

| CP[2] | CP[1] | CP[0] | Setting (Decimal) |

|-------|-------|-------|-------------------|

| 0     | 0     | 0     | 0                 |

| 1     | 0     | 0     | 1                 |

| 1     | 1     | 0     | 3                 |

| 1     | 1     | 1     | 7                 |

#### Table 5–9. Loop Filter Resistor Value Control

| LFR[4] | LFR[3] | LFR[2] | LFR[1] | LFR[0] | Setting<br>(Decimal) |

|--------|--------|--------|--------|--------|----------------------|

| 0      | 0      | 0      | 0      | 0      | 0                    |

| 0      | 0      | 0      | 1      | 1      | 3                    |

| 0      | 0      | 1      | 0      | 0      | 4                    |

| 0      | 1      | 0      | 0      | 0      | 8                    |

| 1      | 0      | 0      | 0      | 0      | 16                   |

| 1      | 0      | 0      | 1      | 1      | 19                   |

| 1      | 0      | 1      | 0      | 0      | 20                   |

| 1      | 1      | 0      | 0      | 0      | 24                   |

| 1      | 1      | 0      | 1      | 1      | 27                   |

| 1      | 1      | 1      | 0      | 0      | 28                   |

| 1      | 1      | 1      | 1      | 0      | 30                   |

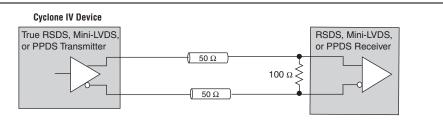

### **RSDS, Mini-LVDS, and PPDS I/O Standard Support in Cyclone IV Devices**

The RSDS, mini-LVDS, and PPDS I/O standards are used in chip-to-chip applications between the timing controller and the column drivers on the display panels such as LCD monitor panels and LCD televisions. Cyclone IV devices meet the National Semiconductor Corporation RSDS Interface Specification, Texas Instruments mini-LVDS Interface Specification, and National Semiconductor Corporation PPDS Interface Specification to support RSDS, mini-LVDS and PPDS output standards, respectively.

For Cyclone IV devices RSDS, mini-LVDS, and PPDS output electrical specifications, refer to the Cyclone IV Device Datasheet chapter.

For more information about the RSDS I/O standard, refer to the RSDS specification from the National Semiconductor website (www.national.com).

### **Designing with RSDS, Mini-LVDS, and PPDS**

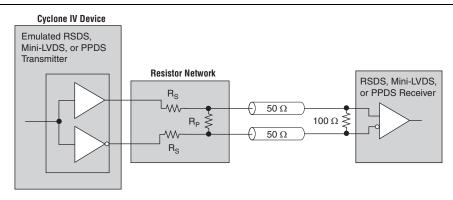

Cyclone IV I/O banks support RSDS, mini-LVDS, and PPDS output standards. The right I/O banks support true RSDS, mini-LVDS, and PPDS transmitters. On the top and bottom I/O banks, RSDS, mini-LVDS, and PPDS transmitters are supported using two single-ended output buffers with external resistors. The two single-ended output buffers are programmed to have opposite polarity.

Figure 6–15 shows an RSDS, mini-LVDS, or PPDS interface with a true output buffer.

# Figure 6–15. Cyclone IV Devices RSDS, Mini-LVDS, or PPDS Interface with True Output Buffer on the Right I/O Banks

Figure 6–16 shows an RSDS, mini-LVDS, or PPDS interface with two single-ended output buffers and external resistors.

# Figure 6–16. RSDS, Mini-LVDS, or PPDS Interface with External Resistor Network on the Top and Bottom I/O Banks (1)

You can begin reconfiguration by pulling the nCONFIG pin low. The nCONFIG pin must be low for at least 500 ns. When nCONFIG is pulled low, the Cyclone IV device is reset. The Cyclone IV device also pulls nSTATUS and CONF\_DONE low and all I/O pins are tri-stated. When nCONFIG returns to a logic-high level and nSTATUS is released by the Cyclone IV device, reconfiguration begins.

### **Configuration Error**

If an error occurs during configuration, Cyclone IV devices assert the nSTATUS signal low, indicating a data frame error and the CONF\_DONE signal stays low. If the **Auto-restart configuration after error** option (available in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box) is turned on, the Cyclone IV device releases nSTATUS after a reset time-out period (a maximum of 230  $\mu$ s), and retries configuration. If this option is turned off, the system must monitor nSTATUS for errors and then pulse nCONFIG low for at least 500 ns to restart configuration.

### Initialization

In Cyclone IV devices, the initialization clock source is either the internal oscillator or the optional CLKUSR pin. By default, the internal oscillator is the clock source for initialization. If you use the internal oscillator, the device provides itself with enough clock cycles for proper initialization. When using the internal oscillator, you do not have to send additional clock cycles from an external source to the CLKUSR pin during the initialization stage. Additionally, you can use the CLKUSR pin as a user I/O pin.

You also have the flexibility to synchronize initialization of multiple devices or to delay initialization with the **CLKUSR** option. The CLKUSR pin allows you to control when your device enters user mode for an indefinite amount of time. You can turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box. When you turn on the **Enable user supplied start-up clock option (CLKUSR)** option, the CLKUSR pin is the initialization clock source. Supplying a clock on the CLKUSR pin does not affect the configuration process. After the configuration data is accepted and CONF\_DONE goes high, Cyclone IV devices require 3,192 clock cycles to initialize properly and enter user mode.

If you use the optional CLKUSR pin and the nCONFIG pin is pulled low to restart configuration during device initialization, ensure that the CLKUSR pin continues to toggle when nSTATUS is low (a maximum of 230 µs).

### **User Mode**

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user mode with a low-to-high transition. The **Enable INIT\_DONE Output** option is available in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box. If you use the INIT\_DONE pin, it is high due to an external  $10-k\Omega$  pull-up resistor when nCONFIG is low and during the beginning of configuration. After the option bit to enable INIT\_DONE is programmed into the device (during the first frame of configuration data), the INIT\_DONE pin goes low. When initialization is complete, the INIT\_DONE pin is released and pulled high. This low-to-high transition signals that the device has entered user mode. In user mode, the user I/O pins function as assigned in your design and no longer have weak pull-up resistors.

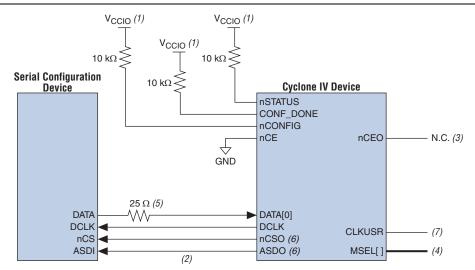

This four-pin interface connects to Cyclone IV device pins, as shown in Figure 8-2.

Figure 8–2. Single-Device AS Configuration

#### Notes to Figure 8-2:

- (1) Connect the pull-up resistors to the V<sub>CCIO</sub> supply of the bank in which the pin resides.

- (2) Cyclone IV devices use the ASDO-to-ASDI path to control the configuration device.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) Connect the series resistor at the near end of the serial configuration device.

- (6) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as the DATA [1] pin in AP and FPP modes.

- (7) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- To tri-state the configuration bus for AS configuration schemes, you must tie nCE high and nCONFIG low.

- The 25-Ω resistor at the near end of the serial configuration device for DATA[0] works to minimize the driver impedance mismatch with the board trace and reduce the overshoot seen at the Cyclone IV device DATA[0] input pin.

In the single-device AS configuration, the maximum board loading and board trace length between the supported serial configuration device and the Cyclone IV device must follow the recommendations in Table 8–7 on page 8–18.

The DCLK generated by the Cyclone IV device controls the entire configuration cycle and provides timing for the serial interface. Cyclone IV devices use an internal oscillator or an external clock source to generate the DCLK. For Cyclone IV E devices, you can use a 40-MHz internal oscillator to generate the DCLK and for Cyclone IV GX devices you can use a slow clock (20 MHz maximum) or a fast clock (40 MHz maximum) from the internal oscillator or an external clock from CLKUSR to generate the DCLK. There are some variations in the internal oscillator frequency because of the process, voltage, and temperature (PVT) conditions in Cyclone IV

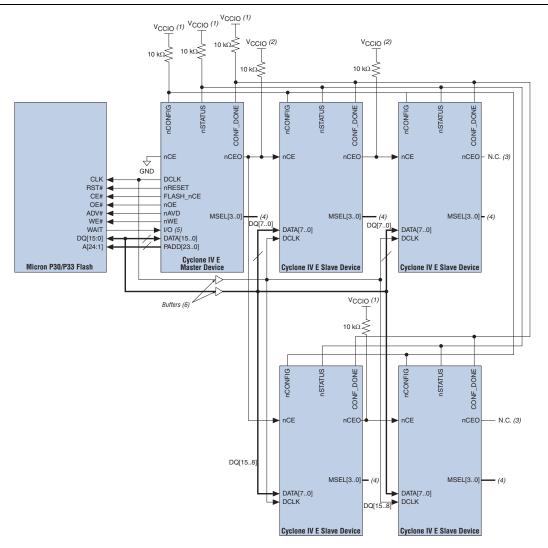

#### Notes to Figure 8-9:

- (1) Connect the pull-up resistors to the V<sub>CCIO</sub> supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device in AP mode and the slave devices in FPP mode. To connect MSEL [3..0] for the master device in AP mode and the slave devices in FPP mode, refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O pin to monitor the WAIT signal from the Micron P30 or P33 flash.

- (6) Connect the repeater buffers between the Cyclone IV E master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

In a multi-device AP configuration, the board trace length between the parallel flash and the master device must follow the recommendations listed in Table 8–11.

The nSTATUS and CONF\_DONE pins on all target devices are connected together with external pull-up resistors, as shown in Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27. These pins are open-drain bidirectional pins on the devices. When the first device asserts nCEO (after receiving all its configuration data), it releases its CONF\_DONE pin. However, the subsequent devices in the chain keep this shared CONF\_DONE line low until they receive their configuration data. When all target devices in the chain receive their configuration data and release CONF\_DONE, the pull-up resistor drives a high level on this line and all devices simultaneously enter initialization mode.

# Guidelines for Connecting Parallel Flash to Cyclone IV E Devices for an AP Interface

For single- and multi-device AP configuration, the board trace length and loading between the supported parallel flash and Cyclone IV E devices must follow the recommendations listed in Table 8–11. These recommendations also apply to an AP configuration with multiple bus masters.

| Cyclone IV E AP Pins | Maximum Board Trace Length from<br>Cyclone IV E Device to Flash Device<br>(inches) | Maximum Board Load (pF) |  |  |

|----------------------|------------------------------------------------------------------------------------|-------------------------|--|--|

| DCLK                 | 6                                                                                  | 15                      |  |  |

| DATA[150]            | 6                                                                                  | 30                      |  |  |

| PADD[230]            | 6                                                                                  | 30                      |  |  |

| nRESET               | 6                                                                                  | 30                      |  |  |

| Flash_nCE            | 6                                                                                  | 30                      |  |  |

| nOE                  | 6                                                                                  | 30                      |  |  |

| nAVD                 | 6                                                                                  | 30                      |  |  |

| nWE                  | 6                                                                                  | 30                      |  |  |

| I/O (1)              | 6                                                                                  | 30                      |  |  |

Table 8–11. Maximum Trace Length and Loading for AP Configuration

Note to Table 8-11:

(1) The AP configuration ignores the WAIT signal from the flash during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

### **Configuring With Multiple Bus Masters**

Similar to the AS configuration scheme, the AP configuration scheme supports multiple bus masters for the parallel flash. For another master to take control of the AP configuration bus, the master must assert nCONFIG low for at least 500 ns to reset the master Cyclone IV E device and override the weak 10-k $\Omega$  pull-down resistor on the nCE pin. This resets the master Cyclone IV E device then takes control of the AP configuration bus. The other master device then takes control of the AP configuration bus, then releases the nCE pin, and finally pulses nCONFIG low to restart the configuration.

In the AP configuration scheme, multiple masters share the parallel flash. Similar to the AS configuration scheme, the bus control is negotiated by the nCE pin.

| 0h-al               | Devenuetor                                                     | Mini                                         | mum                         | Max                 | imum                        | 11   |

|---------------------|----------------------------------------------------------------|----------------------------------------------|-----------------------------|---------------------|-----------------------------|------|

| Symbol              | Parameter                                                      | Cyclone IV <sup>(1)</sup>                    | Cyclone IV E <sup>(2)</sup> | Cyclone IV (1)      | Cyclone IV E <sup>(2)</sup> | Unit |

| t <sub>CF2ST1</sub> | nCONFIG high to<br>nSTATUS high                                | _                                            |                             | 23                  | μs                          |      |

| t <sub>CF2CK</sub>  | nCONFIG high to first rising edge on DCLK                      | 230                                          | (3)                         | -                   | _                           | μs   |

| t <sub>sт2СК</sub>  | nSTATUS high to first rising edge of DCLK                      | 2                                            | 2                           | -                   | _                           | μs   |

| t <sub>DH</sub>     | Data hold time after rising edge on DCLK                       | (                                            | )                           | -                   | ns                          |      |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode <sup>(5)</sup>                     | 30                                           | 00                          | 6                   | μs                          |      |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                               | 4 × maximum                                  | DCLK <b>period</b>          | -                   |                             |      |

| t <sub>cd2umc</sub> | CONF_DONE high to<br>user mode with<br><b>CLKUSR</b> option on | t <sub>CD2CU</sub> + (3,192 × CLKUSR period) |                             | 12 × CLKUSR period) |                             |      |

| t <sub>DSU</sub>    | Data setup time before rising edge on DCLK                     | 5 8                                          |                             | _                   | _                           | ns   |

| t <sub>CH</sub>     | DCLK high time                                                 | 3.2 6.4                                      |                             | 3.2 6.4 — —         |                             | ns   |

| t <sub>CL</sub>     | DCLK low time                                                  | 3.2 6.4                                      |                             |                     |                             | ns   |

| t <sub>CLK</sub>    | DCLK period                                                    | 7.5 15                                       |                             |                     |                             | ns   |

| f <sub>MAX</sub>    | DCLK frequency <sup>(6)</sup>                                  | —                                            | —                           | 133                 | 66                          | MHz  |

Notes to Table 8-12:

(1) Applicable for Cyclone IV GX and Cyclone IV E devices with 1.2-V core voltage.

(2) Applicable for Cyclone IV E devices with 1.0-V core voltage.

(3) This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

(4) This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

(5) The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for starting the device.

(6) Cyclone IV E devices with 1.0-V core voltage have slower F<sub>MAX</sub> when compared with Cyclone IV GX devices with 1.2-V core voltage.

### **PS Configuration Using a Download Cable**

In this section, the generic term "download cable" includes the Altera USB-Blaster USB port download cable, MasterBlaster<sup>™</sup> serial and USB communications cable, ByteBlaster II parallel port download cable, the ByteBlasterMV<sup>™</sup> parallel port download cable, and the EthernetBlaster communications cable.

In the PS configuration with a download cable, an intelligent host (such as a PC) transfers data from a storage device to the Cyclone IV device through the download cable.

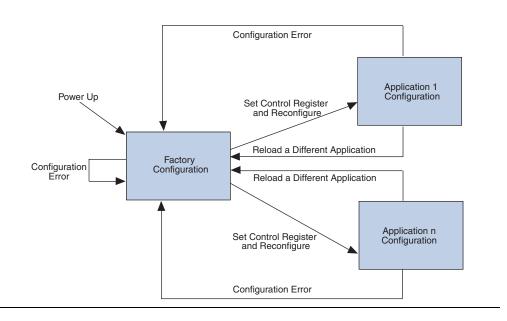

Figure 8–32 shows the transitions between the factory configuration and application configuration in remote update mode.

After power up or a configuration error, the factory configuration logic writes the remote system upgrade control register to specify the address of the application configuration to be loaded. The factory configuration also specifies whether or not to enable the user watchdog timer for the application configuration and, if enabled, specifies the timer setting.

Only valid application configurations designed for remote update mode include the logic to reset the timer in user mode. For more information about the user watchdog timer, refer to the "User Watchdog Timer" on page 8–79.

If there is an error while loading the application configuration, the remote system upgrade status register is written by the dedicated remote system upgrade circuitry of the Cyclone IV device to specify the cause of the reconfiguration.

The following actions cause the remote system upgrade status register to be written:

- nSTATUS driven low externally

- Internal cyclical redundancy check (CRC) error

- User watchdog timer time-out

- A configuration reset (logic array nCONFIG signal or external nCONFIG pin assertion)

The Cyclone IV device automatically loads the factory configuration when an error occurs. This user-designed factory configuration reads the remote system upgrade status register to determine the reason for reconfiguration. Then the factory configuration takes the appropriate error recovery steps and writes to the remote system upgrade control register to determine the next application configuration to be loaded.

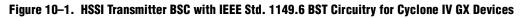

## IEEE Std. 1149.6 Boundary-Scan Register

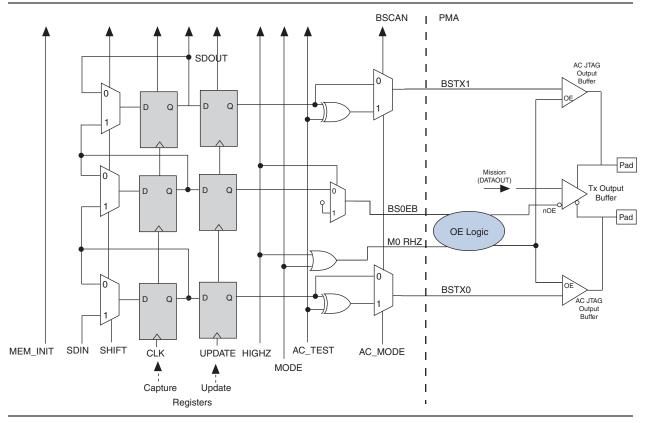

The boundary-scan cell (BSC) for HSSI transmitters ( $GXB_TX[p,n]$ ) and receivers ( $GXB_RX[p,n]$ ) in Cyclone IV GX devices are different from the BSCs for I/O pins.

Figure 10–1 shows the Cyclone IV GX HSSI transmitter boundary-scan cell.

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Visual Cue                               | Meaning                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input. The suffix n denotes an active-low signal. For example, resetn.                 |

| Courier type                             | Indicates command line commands and anything that must be typed exactly as it appears. For example, c:\qdesigns\tutorial\chiptrip.gdf.                                                 |

|                                          | Also indicates sections of an actual file, such as a Report File, references to parts of files (for example, the AHDL keyword SUBDESIGN), and logic function names (for example, TRI). |

| 4                                        | An angled arrow instructs you to press the Enter key.                                                                                                                                  |

| 1., 2., 3., and<br>a., b., c., and so on | Numbered steps indicate a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                          |

|                                          | Bullets indicate a list of items when the sequence of the items is not important.                                                                                                      |

| L.                                       | The hand points to information that requires special attention.                                                                                                                        |

| ?                                        | The question mark directs you to a software help system with related information.                                                                                                      |

|                                          | The feet direct you to another document or website with related information.                                                                                                           |

| <b>∄</b> ,∰∄                             | The multimedia icon directs you to a related multimedia presentation.                                                                                                                  |

| CAUTION                                  | A caution calls attention to a condition or possible situation that can damage or destroy the product or your work.                                                                    |

| WARNING                                  | A warning calls attention to a condition or possible situation that can cause you injury.                                                                                              |

|                                          | The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents.                 |

### **Receive Bit-Slip Indication**

The number of bits slipped in the word aligner for synchronization in manual alignment mode is provided with the rx\_bitslipboundaryselectout [4..0] signal. For example, if one bit is slipped in word aligner to achieve synchronization, the output on rx\_bitslipboundaryselectout [4..0] signal shows a value of 1 (5'00001). The information from this signal helps in latency calculation through the receiver as the number of bits slipped in the word aligner varies at each synchronization.

### **Transmit Bit-Slip Control**

The transmitter datapath supports bit-slip control to delay the serial data transmission by a number of specified bits in PCS with tx\_bitslipboundaryselect[4..0] port. With 8- or 10-bit channel width, the transmitter supports zero to nine bits of data slip. This feature helps to maintain a fixed round trip latency by compensating latency variation from word aligner when providing the appropriate values on tx\_bitslipboundaryselect[4..0] port based on values on rx\_bitslipboundaryselectout[4..0] signal.

### **PLL PFD feedback**

In Deterministic Latency mode, when transmitter input reference clock frequency is the same as the low-speed clock, the PLL that clocks the transceiver supports PFD feedback. When enabled, the PLL compensates for delay uncertainty in the low-speed clock (tx\_clkout in ×1 configuration or coreclkout in ×4 configuration) path relative to input reference and the transmitter datapath latency is fixed relative to the transmitter input reference clock.

### **SDI Mode**

SDI mode provides the non-bonded (×1) transceiver channel datapath configuration for HD- and 3G-SDI protocol implementations.

Cyclone IV GX transceivers configured in SDI mode provides the serialization and deserialization functions that supports the SDI data rates as listed in Table 1–24.

| SMPTE<br>Standard <sup>(1)</sup> | Configuration         | Data Rate (Mbps) | FPGA Fabric-to-<br>Transceiver Width | Byte SERDES Usage |

|----------------------------------|-----------------------|------------------|--------------------------------------|-------------------|

|                                  |                       | 1483.5           | 20-bit                               | Used              |

| 292M                             | High definition (HD)  | 1403.5           | 10-bit                               | Not used          |

| 292101                           |                       | 1485             | 20-bit                               | Used              |

|                                  |                       | 1405             | 10-bit                               | Not used          |

| 424M                             | Third concretion (20) | 2967             | 20-bit                               | Used              |

| 424101                           | Third-generation (3G) | 2970             | 20 <sup>-</sup> 011                  | 0380              |

Table 1–24. Supported SDI Data Rates

Note to Table 1-24:

(1) Society of Motion Picture and Television Engineers (SMPTE).

SDI functions such as scrambling/de-scrambling, framing, and cyclic redundancy check (CRC) must be implemented in the user logic.

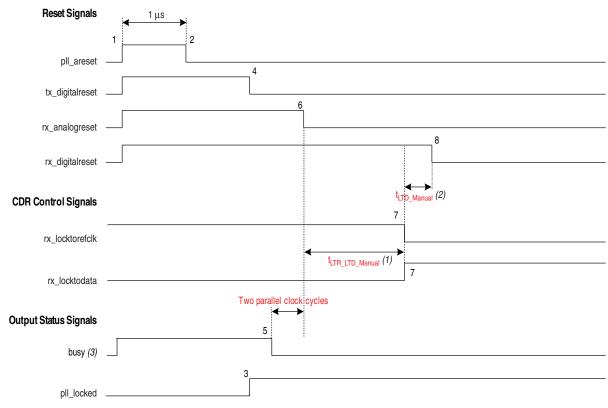

#### **Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode**

This configuration contains both a transmitter and receiver channel. If you create a **Receiver and Transmitter** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in manual lock mode, use the reset sequence shown in Figure 2–9.

Figure 2–9. Sample Reset Sequence of Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode

#### Notes to Figure 2–9:

- (1) For  $t_{LTR\_LTD\_Manual}$  duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) For t<sub>LTD Manual</sub> duration, refer to the Cyclone IV Device Datasheet chapter.

- (3) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–9, perform the following reset procedure for the receiver in manual lock mode:

- 1. After power up, assert pll\_areset for a minimum period of 1 µs (the time between markers 1 and 2).

- Keep the tx\_digitalreset, rx\_analogreset, rx\_digitalreset, and rx\_locktorefclk signals asserted and the rx\_locktodata signal deasserted during this time period. After you deassert the pll\_areset signal, the multipurpose PLL starts locking to the transmitter input reference clock.

- 3. After the multipurpose PLL locks, as indicated by the pll\_locked signal going high (marker 3), deassert tx\_digitalreset (marker 4). For receiver operation, after deassertion of busy signal (marker 5), wait for two parallel clock cycles to deassert the rx\_analogreset signal (marker 6). After rx\_analogreset deassert, rx pll locked will assert.

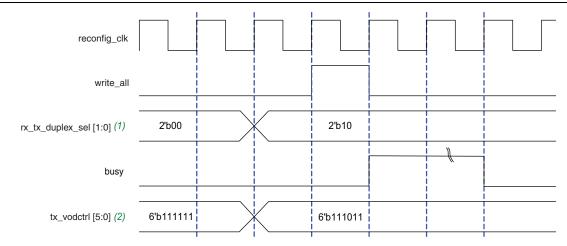

Figure 3–8 shows a write transaction waveform with the **Use the same control signal for all the channels** option disabled.

#### Notes to Figure 3-8:

- (1) In this waveform example, you want to write to only the transmitter portion of the channel.

- (2) In this waveform example, the number of channels controlled by the dynamic reconfiguration controller (the ALTGX\_RECONFIG instance) is two and that the tx\_vodctrl control port is enabled.

Simultaneous write and read transactions are not allowed.

#### **Read Transaction**

The read transaction in Method 3 is identical to that in Method 2. Refer to "Read Transaction" on page 3–18.

F

This is the slowest method. You have to write all the PMA settings for all channels even if you may only be changing one parameter on the channel. Altera recommends using the logical\_channel\_address method for time-critical applications.

For each method, you can additionally reconfigure the PMA setting of both transmitter and receiver portion, transmitter portion only, or receiver portion only of the transceiver channel. For more information, refer to "Dynamic Reconfiguration Controller Port List" on page 3–4. You can enable the rx\_tx\_duplex\_sel port by selecting the Use 'rx\_tx\_duplex\_sel' port to enable RX only, TX only or duplex reconfiguration option on the Error checks tab of the ALTGX\_RECONFIG MegaWizard Plug-In Manager.

Figure 3–9 shows the ALTGX\_RECONFIG connection to the ALTGX instances when set in analog reconfiguration mode. For the port information, refer to the "Dynamic Reconfiguration Controller Port List" on page 3–4.

For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to *Section III: System Performance Specifications* of the *External Memory Interface Handbook*.

Table 1–37 lists the memory output clock jitter specifications for Cyclone IV devices.

Table 1–37. Memory Output Clock Jitter Specifications for Cyclone IV Devices (1), (2)

| Parameter                    | Symbol                 | Min  | Max | Unit |

|------------------------------|------------------------|------|-----|------|

| Clock period jitter          | t <sub>JIT(per)</sub>  | -125 | 125 | ps   |

| Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -200 | 200 | ps   |

| Duty cycle jitter            | t <sub>JIT(duty)</sub> | -150 | 150 | ps   |

#### Notes to Table 1-37:

(1) Memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2 standard.

### **Duty Cycle Distortion Specifications**

Table 1–38 lists the worst case duty cycle distortion for Cyclone IV devices.

Table 1–38. Duty Cycle Distortion on Cyclone IV Devices I/O Pins (1), (2), (3)

| Symbol            | C6 C7, I7 |     | , 17 | C8, I8L, A7 |     | C9L |     | Unit |       |

|-------------------|-----------|-----|------|-------------|-----|-----|-----|------|-------|

|                   | Min       | Max | Min  | Max         | Min | Max | Min | Max  | UIIIL |

| Output Duty Cycle | 45        | 55  | 45   | 55          | 45  | 55  | 45  | 55   | %     |

Notes to Table 1-38:

(1) The duty cycle distortion specification applies to clock outputs from the PLLs, global clock tree, and IOE driving the dedicated and general purpose I/O pins.

(2) Cyclone IV devices meet the specified duty cycle distortion at the maximum output toggle rate for each combination of I/O standard and current strength.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

### **OCT Calibration Timing Specification**

Table 1–39 lists the duration of calibration for series OCT with calibration at device power-up for Cyclone IV devices.

# Table 1–39. Timing Specification for Series OCT with Calibration at Device Power-Up for Cyclone IV Devices $\,^{(1)}$

| Symbol              | Description                                                   | Maximum | Units |  |

|---------------------|---------------------------------------------------------------|---------|-------|--|

| t <sub>octcal</sub> | Duration of series OCT with<br>calibration at device power-up | 20      | μs    |  |

#### Note to Table 1-39:

(1) OCT calibration takes place after device configuration and before entering user mode.

1-33

<sup>(2)</sup> The clock jitter specification applies to memory output clock pins generated using DDIO circuits clocked by a PLL output routed on a global clock (GCLK) network.

Table 1–42 and Table 1–43 list the IOE programmable delay for Cyclone IV E 1.2 V core voltage devices.

|                                                                       |                                   | Number<br>of<br>Setting | Min<br>Offset | Max Offset  |       |       |             |       |       |       |       |    |

|-----------------------------------------------------------------------|-----------------------------------|-------------------------|---------------|-------------|-------|-------|-------------|-------|-------|-------|-------|----|

| Parameter                                                             | Paths<br>Affected                 |                         |               | Fast Corner |       |       | Slow Corner |       |       |       | Unit  |    |

|                                                                       |                                   |                         |               | C6          | 17    | A7    | C6          | C7    | C8    | 17    | A7    |    |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core  | 7                       | 0             | 1.314       | 1.211 | 1.211 | 2.177       | 2.340 | 2.433 | 2.388 | 2.508 | ns |

| Input delay from pin to input register                                | Pad to I/O<br>input register      | 8                       | 0             | 1.307       | 1.203 | 1.203 | 2.19        | 2.387 | 2.540 | 2.430 | 2.545 | ns |

| Delay from output<br>register to output pin                           | I/O output<br>register to<br>pad  | 2                       | 0             | 0.437       | 0.402 | 0.402 | 0.747       | 0.820 | 0.880 | 0.834 | 0.873 | ns |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock<br>network | 12                      | 0             | 0.693       | 0.665 | 0.665 | 1.200       | 1.379 | 1.532 | 1.393 | 1.441 | ns |

Notes to Table 1-42:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

| Parameter                                                             |                                   | Number<br>of<br>Setting | Min<br>Offset | Max Offset  |       |       |             |            |       |       |       |      |

|-----------------------------------------------------------------------|-----------------------------------|-------------------------|---------------|-------------|-------|-------|-------------|------------|-------|-------|-------|------|

|                                                                       | Paths<br>Affected                 |                         |               | Fast Corner |       |       | Slow Corner |            |       |       |       | Unit |

|                                                                       |                                   |                         |               | C6          | 17    | A7    | C6          | <b>C</b> 7 | C8    | 17    | A7    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core  | 7                       | 0             | 1.314       | 1.209 | 1.209 | 2.201       | 2.386      | 2.510 | 2.429 | 2.548 | ns   |

| Input delay from pin to input register                                | Pad to I/O<br>input register      | 8                       | 0             | 1.312       | 1.207 | 1.207 | 2.202       | 2.402      | 2.558 | 2.447 | 2.557 | ns   |

| Delay from output<br>register to output pin                           | I/O output<br>register to<br>pad  | 2                       | 0             | 0.458       | 0.419 | 0.419 | 0.783       | 0.861      | 0.924 | 0.875 | 0.915 | ns   |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock<br>network | 12                      | 0             | 0.686       | 0.657 | 0.657 | 1.185       | 1.360      | 1.506 | 1.376 | 1.422 | ns   |

Table 1–43. IOE Programmable Delay on Row Pins for Cyclone IV E 1.2 V Core Voltage Devices (1), (2)

#### Notes to Table 1-43:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.