### Intel - EP4CE40F29C9LN Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Detailo                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 2475                                                      |

| Number of Logic Elements/Cells | 39600                                                     |

| Total RAM Bits                 | 1161216                                                   |

| Number of I/O                  | 532                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 0.97V ~ 1.03V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 780-BGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce40f29c9ln |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Chapter 11. Power Requirements for Cyclone IV Devices

| External Power Supply Requirements         | 11–1 |

|--------------------------------------------|------|

| Hot-Socketing Specifications               |      |

| Devices Driven Before Power-Up             |      |

| I/O Pins Remain Tri-stated During Power-Up |      |

| Hot-socketing Feature Implementation       |      |

| Power-On Reset Circuitry                   |      |

| Document Revision History                  |      |

| Dood Dort | Write Port   |              |              |              |              |              |              |              |              |  |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 256 × 32     | 1024 × 9     | 512 × 18     | 256 × 36     |  |

| 512 × 16  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            |              | —            |  |

| 256 × 32  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            | _            | —            |  |

| 1024 × 9  | —            | _            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| 512 × 18  | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| 256 × 36  | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | ~            |  |

| Table 3-3. | Cyclone IV Devices M9K Block Mixed-Width Configurations (Simple Dual-Port Mode) | (Part 2 of 2) |

|------------|---------------------------------------------------------------------------------|---------------|

|------------|---------------------------------------------------------------------------------|---------------|

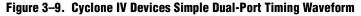

In simple dual-port mode, M9K memory blocks support separate wren and rden signals. You can save power by keeping the rden signal low (inactive) when not reading. Read-during-write operations to the same address can either output "Don't Care" data at that location or output "Old Data". To choose the desired behavior, set the **Read-During-Write** option to either **Don't Care** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about this behavior, refer to "Read-During-Write Operations" on page 3–15.

Figure 3–9 shows the timing waveform for read and write operations in simple dual-port mode with unregistered outputs. Registering the outputs of the RAM simply delays the q output by one clock cycle.

# **Document Revision History**

Table 5–14 lists the revision history for this chapter.

| Date          | Version | Changes                                                                                                                               |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| October 2012  | 2.4     | <ul> <li>Updated "Manual Override" and "PLL Cascading" sections.</li> </ul>                                                           |

|               | 2.4     | ■ Updated Figure 5–9.                                                                                                                 |

| November 2011 | 2.3     | <ul> <li>Updated the "Dynamic Phase Shifting" section.</li> </ul>                                                                     |

|               | 2.3     | <ul> <li>Updated Figure 5–26.</li> </ul>                                                                                              |

|               |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                         |

|               |         | ■ Updated Figure 5–3 and Figure 5–10.                                                                                                 |

| December 2010 | 2.2     | <ul> <li>Updated "GCLK Network Clock Source Generation", "PLLs in Cyclone IV Devices",<br/>and "Manual Override" sections.</li> </ul> |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                 |

|               |         | ■ Updated Figure 5–2, Figure 5–3, Figure 5–4, and Figure 5–10.                                                                        |

| July 2010     | 2.1     | ■ Updated Table 5–1, Table 5–2, and Table 5–5.                                                                                        |

|               |         | <ul> <li>Updated "Clock Feedback Modes" section.</li> </ul>                                                                           |

|               |         | <ul> <li>Added Cyclone IV E devices information for the Quartus II software version 9.1 SP1<br/>release.</li> </ul>                   |

|               |         | <ul> <li>Updated "Clock Networks" section.</li> </ul>                                                                                 |

| February 2010 | 2.0     | ■ Updated Table 5–1 and Table 5–2.                                                                                                    |

|               |         | ■ Added Table 5–3.                                                                                                                    |

|               |         | ■ Updated Figure 5–2, Figure 5–3, and Figure 5–9.                                                                                     |

|               |         | <ul> <li>Added Figure 5–4 and Figure 5–10.</li> </ul>                                                                                 |

| November 2009 | 1.0     | Initial release.                                                                                                                      |

- "FPP Configuration" on page 8–40

- "JTAG Configuration" on page 8–45

- "Device Configuration Pins" on page 8–62

## **Configuration Features**

Table 8–1 lists the configuration methods you can use in each configuration scheme.

Table 8–1. Configuration Features in Cyclone IV Devices

| <b>Configuration Scheme</b> | Configuration Method                  | Decompression | Remote System Upgrade <sup>(1)</sup> |  |

|-----------------------------|---------------------------------------|---------------|--------------------------------------|--|

| AS                          | Serial Configuration Device           | $\checkmark$  | $\checkmark$                         |  |

| AP                          | Supported Flash Memory <sup>(2)</sup> | —             | $\checkmark$                         |  |

| PS                          | External Host with Flash Memory       | $\checkmark$  | ✓ (3)                                |  |

|                             | Download Cable                        | $\checkmark$  | _                                    |  |

| FPP                         | External Host with Flash Memory       | —             | ✓ <sup>(3)</sup>                     |  |

| ITAC based configuration    | External Host with Flash Memory       | —             | —                                    |  |

| JTAG based configuration    | Download Cable                        | —             | _                                    |  |

### Notes to Table 8-1:

(1) Remote update mode is supported when you use the Remote System Upgrade feature. You can enable or disable remote update mode with an option setting in the Quartus® II software.

(2) For more information about the supported device families for the Micron commodity parallel flash, refer to Table 8–10 on page 8–22.

(3) Remote update mode is supported externally using the Parallel Flash Loader (PFL) with the Quartus II software.

### **Configuration Data Decompression**

Cyclone IV devices support configuration data decompression, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory and send the compressed bitstream to Cyclone IV devices. During configuration, Cyclone IV devices decompress the bitstream in real time and program the SRAM cells.

Compression may reduce the configuration bitstream size by 35 to 55%.

When you enable compression, the Quartus II software generates configuration files with compressed configuration data. This compressed file reduces the storage requirements in the configuration device or flash memory and decreases the time required to send the bitstream to the Cyclone IV device. The time required by a Cyclone IV device to decompress a configuration file is less than the time required to send the configuration data to the device. There are two methods for enabling compression for the Cyclone IV device bitstreams in the Quartus II software:

- Before design compilation (through the Compiler Settings menu)

- After design compilation (through the **Convert Programming Files** dialog box)

To enable compression in the compiler settings of the project in the Quartus II software, perform the following steps:

- 1. On the Assignments menu, click **Device**. The **Settings** dialog box appears.

- 2. Click Device and Pin Options. The Device and Pin Options dialog box appears.

four devices. During the first configuration cycle, the master device reads its configuration data from the serial configuration device while holding nCEO high. After completing its configuration cycle, the master device drives nCE low and sends the second copy of the configuration data to all three slave devices, configuring them simultaneously.

The advantage of the setup in Figure 8–4 is that you can have a different **.sof** for the master device. However, all the slave devices must be configured with the same **.sof**. You can either compress or uncompress the **.sof** in this configuration method.

You can still use this method if the master and slave devices use the same **.sof**.

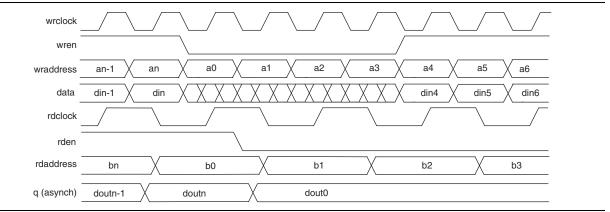

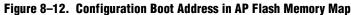

The default configuration boot address allows the system to use special parameter blocks in the flash memory map. Parameter blocks are at the top or bottom of the memory map. Figure 8–12 shows the configuration boot address in the AP configuration scheme. You can change the default configuration default boot address 0×010000 to any desired address using the APFC\_BOOT\_ADDR\_JTAG instruction. For more information about the APFC\_BOOT\_ADDR\_JTAG instruction, refer to "JTAG Instructions" on page 8–57.

#### Note to Figure 8-12:

(1) The default configuration boot address is x010000 when represented in 16-bit word addressing.

## **PS Configuration**

You can perform PS configuration on Cyclone IV devices with an external intelligent host, such as a MAX<sup>®</sup> II device, microprocessor with flash memory, or a download cable. In the PS scheme, an external host controls the configuration. Configuration data is clocked into the target Cyclone IV device through DATA[0] at each rising edge of DCLK.

If your system already contains a common flash interface (CFI) flash memory, you can use it for Cyclone IV device configuration storage as well. The MAX II PFL feature provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control the configuration from the flash memory device to the Cyclone IV device.

**Tor** For more information about the PFL, refer to *AN* 386: Using the Parallel Flash Loader with the Quartus II Software.

Cyclone IV devices do not support enhanced configuration devices for PS configuration.

To ensure DCLK and DATA [0] are not left floating at the end of configuration, the MAX II device must drive them either high or low, whichever is convenient on your board. The DATA [0] pin is available as a user I/O pin after configuration. In the PS scheme, the DATA [0] pin is tri-stated by default in user mode and must be driven by the external host device. To change this default option in the Quartus II software, select the **Dual-Purpose Pins** tab of the **Device and Pin Options** dialog box.

The configuration clock (DCLK) speed must be below the specified system frequency to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

The external host device can also monitor CONF\_DONE and INIT\_DONE to ensure successful configuration. The CONF\_DONE pin must be monitored by the external device to detect errors and to determine when programming is complete. If all configuration data is sent, but CONF\_DONE or INIT\_DONE has not gone high, the external device must reconfigure the target device.

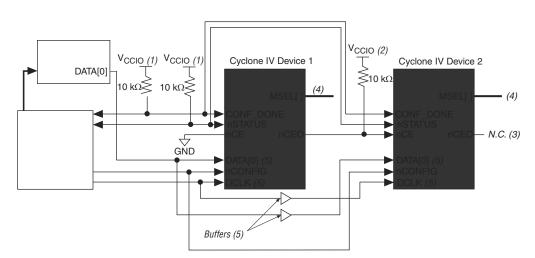

Figure 8–14 shows how to configure multiple devices using an external host device. This circuit is similar to the PS configuration circuit for a single device, except that Cyclone IV devices are cascaded for multi-device configuration.

### Figure 8–14. Multi-Device PS Configuration Using an External Host

#### Notes to Figure 8-14:

- (1) The pull-up resistor must be connected to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  must be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

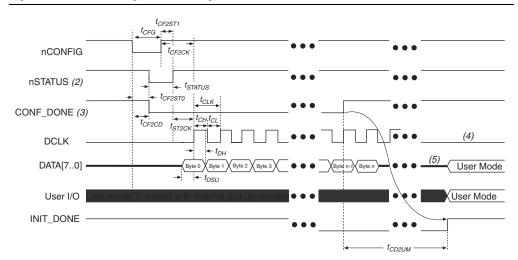

### **FPP Configuration Timing**

Figure 8–22 shows the timing waveform for the FPP configuration when using an external host.

### Notes to Figure 8-22:

- (1) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and  $CONF_DONE$  are at logic-high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (2) After power up, the Cyclone IV device holds  ${\tt nSTATUS}$  low during POR delay.

- (3) After power up, before and during configuration,  $CONF_DONE$  is low.

- (4) Do not leave DCLK floating after configuration. It must be driven high or low, whichever is more convenient.

- (5) DATA [7..0] is available as a user I/O pin after configuration; the state of the pin depends on the dual-purpose pin settings.

Table 8–13 lists the FPP configuration timing parameters for Cyclone IV devices.

Table 8–13. FPP Timing Parameters for Cyclone IV Devices (Part 1 of 2)

| 0hal                | Deventer                                        | Mini                      | mum                         | Maxin                     |                             |         |  |    |

|---------------------|-------------------------------------------------|---------------------------|-----------------------------|---------------------------|-----------------------------|---------|--|----|

| Symbol              | Parameter                                       | Cyclone IV <sup>(1)</sup> | Cyclone IV E <sup>(2)</sup> | Cyclone IV <sup>(1)</sup> | Cyclone IV E <sup>(2)</sup> | Unit    |  |    |

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low                    | _                         | -                           | 50                        | ns                          |         |  |    |

| t <sub>CF2ST0</sub> | nCONFIG <b>low to</b><br>nSTATUS <b>low</b>     | _                         | — 500                       |                           | 500                         |         |  |    |

| t <sub>CFG</sub>    | nCONFIG low pulse width                         | 500 —                     |                             |                           |                             | ns      |  |    |

| t <sub>status</sub> | nSTATUS low pulse width                         | 4                         | 5                           | 230 ( <sup>3</sup> )      |                             | μs      |  |    |

| t <sub>CF2ST1</sub> | nCONFIG high to<br>nSTATUS high                 | _                         |                             |                           |                             | 230 (4) |  | μs |

| t <sub>CF2CK</sub>  | nCONFIG high to<br>first rising edge on<br>DCLK | 230                       | (3)                         |                           |                             |         |  |    |

## **Device Configuration Pins**

Table 8–18 through Table 8–21 describe the connections and functionality of all the configuration related pins on Cyclone IV devices. Table 8–18 and Table 8–19 list the device pin configuration for the Cyclone IV GX and Cyclone IV E, respectively.

Table 8–18. Configuration Pin Summary for Cyclone IV GX Devices

| Bank | Description        | Input/Output  | Dedicated | Powered By                     | <b>Configuration Mode</b> |

|------|--------------------|---------------|-----------|--------------------------------|---------------------------|

| 8    | Data[4:2]          | Input         | —         | V <sub>CCIO</sub>              | FPP                       |

| 3    | Data[7:5]          | Input         |           | V <sub>CCIO</sub>              | FPP                       |

| 9    | nCSO (2)           | Output        |           | V <sub>CCIO</sub>              | AS                        |

| 3    | CRC_ERROR          | Output        | —         | V <sub>CCIO</sub> /Pull-up (1) | Optional, all modes       |

| 9    | DATA[0] (2)        | Input         | Yes       | V <sub>CCIO</sub>              | PS, FPP, AS               |

| 9    | DATA [1] /ASDO (2) | Input         |           | V <sub>CCIO</sub>              | FPP                       |

| 9    | DATA[1]/ASDO (2)   | Output        |           | V <sub>CCIO</sub>              | AS                        |

| 3    | INIT_DONE          | Output        |           | Pull-up                        | Optional, all modes       |

| 3    | nSTATUS            | Bidirectional | Yes       | Pull-up                        | All modes                 |

| 9    | nCE                | Input         | Yes       | V <sub>CCIO</sub>              | All modes                 |

| 9    | DCLK (2)           | are (2) Input | Yes       | V <sub>CCIO</sub>              | PS, FPP                   |

| 9    | DCLK (-)           | Output        | res       | V <sub>CCIO</sub>              | AS                        |

| 3    | CONF_DONE          | Bidirectional | Yes       | Pull-up                        | All modes                 |

| 9    | TDI                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | TMS                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | TCK                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | nCONFIG            | Input         | Yes       | V <sub>CCIO</sub>              | All modes                 |

| 8    | CLKUSR             | Input         |           | V <sub>CCIO</sub>              | Optional                  |

| 3    | nCEO               | Output        |           | V <sub>ccio</sub>              | Optional, all modes       |

| 3    | MSEL               | Input         | Yes       | V <sub>CCINT</sub>             | All modes                 |

| 9    | TDO                | Output        | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 6    | DEV_OE             | Input         | —         | V <sub>CCIO</sub>              | Optional                  |

| 6    | DEV_CLRn           | Input         | —         | V <sub>CCIO</sub>              | Optional                  |

Notes to Table 8-18:

(1) The CRC\_ERROR pin is a dedicated open-drain output or an optional user I/O pin. Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device and Pin Options dialog box. When using this pin, connect it to an external 10-kΩ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.

(2) To tri-state AS configuration pins in the AS configuration scheme, turn on the **Enable input tri-state on active configuration pins in user mode** option from the **Device and Pin Options** dialog box. This tri-states DCLK, nCSO, Data[0], and Data[1]/ASDO pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the **Enable input tri-state on active configuration pins in user mode** option and set the desired setting from the Dual-purpose Pins Setting menu.

| Bank | Description               | Input/Output | Dedicated | Powered By                            | <b>Configuration Mode</b> |

|------|---------------------------|--------------|-----------|---------------------------------------|---------------------------|

| 1    | nCSO (1)<br>FLASH_nCE (2) | Output       | —         | V <sub>CCIO</sub>                     | AS, AP                    |

| 6    | CRC_ERROR (3)             | Output       | —         | V <sub>CCIO</sub> /Pull-up <i>(4)</i> | Optional, all modes       |

# 9. SEU Mitigation in Cyclone IV Devices

This chapter describes the cyclical redundancy check (CRC) error detection feature in user mode and how to recover from soft errors.

Configuration error detection is supported in all Cyclone<sup>®</sup> IV devices including Cyclone IV GX devices, Cyclone IV E devices with 1.0-V core voltage, and Cyclone IV E devices with 1.2-V core voltage. However, user mode error detection is only supported in Cyclone IV GX devices and Cyclone IV E devices with 1.2-V core voltage.

Dedicated circuitry built into Cyclone IV devices consists of a CRC error detection feature that can optionally check for a single-event upset (SEU) continuously and automatically.

In critical applications used in the fields of avionics, telecommunications, system control, medical, and military applications, it is important to be able to:

- Confirm the accuracy of the configuration data stored in an FPGA device

- Alert the system to an occurrence of a configuration error

Using the CRC error detection feature for Cyclone IV devices does not impact fitting or performance.

This chapter contains the following sections:

- "Configuration Error Detection" on page 9–1

- "User Mode Error Detection" on page 9–2

- "Automated SEU Detection" on page 9–3

- "CRC\_ERROR Pin" on page 9–3

- "Error Detection Block" on page 9–4

- "Error Detection Timing" on page 9–5

- "Software Support" on page 9–6

- "Recovering from CRC Errors" on page 9–9

# **Configuration Error Detection**

Configuration error detection is available in all Cyclone IV devices including Cyclone IV GX devices, Cyclone IV E devices with 1.0-V core voltage, and Cyclone IV E devices with 1.2-V core voltage.

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

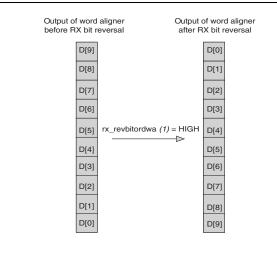

synchronization state machine mode. In bit-slip mode, you can dynamically enable the receiver bit reversal using the rx\_revbitorderwa port. When enabled, the 8-bit or 10-bit data D[7..0] or D[9..0] at the output of the word aligner is rewired to D[0..7] or D[0..9] respectively. Figure 1–20 shows the receiver bit reversal feature.

#### Note to Figure 1-20:

(1) The rx\_revbitordwa port is dynamic and is only available when the word aligner is configured in bit-slip mode.

- When using the receiver bit reversal feature to receive MSB-to-LSB transmission, reversal of the word alignment pattern is required.

- Receiver bit-slip indicator—provides the number of bits slipped in the word aligner for synchronization with rx\_bitslipboundaryselectout signal. For usage details, refer to "Receive Bit-Slip Indication" on page 1–76.

### **Deskew FIF0**

This module is only available when used for the XAUI protocol and is used to align all four channels to meet the maximum skew requirement of 40 UI (12.8 ns) as seen at the receiver of the four lanes. The deskew operation is compliant to the PCS deskew state machine diagram specified in clause 48 of the IEEE P802.3ae specification.

The deskew circuitry consists of a 16-word deep deskew FIFO in each of the four channels, and control logics in the central control unit of the transceiver block that controls the deskew FIFO write and read operations in each channel.

For details about the deskew FIFO operations for channel deskewing, refer to "XAUI Mode" on page 1–67.

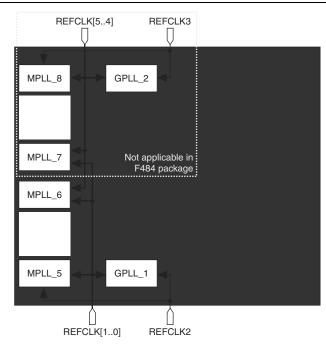

Figure 1–26. PLL Input Reference Clocks in Transceiver Operation for F484 and Larger Packages  $^{(1)}$ ,  $^{(2)}$ ,  $^{(3)}$

### Notes to Figure 1-26:

- (1) The REFCLK2 and REFCLK3 pins are dual-purpose CLKIO, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A respectively.

- (2) The REFCLK[1..0] and REFCLK[5..4] pins are dual-purpose differential REFCLK or DIFFCLK pins that reside in banks 3B and 8B respectively. These clock input pins do not have access to the clock control blocks and GCLK networks. For more details, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

- (3) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs and GPLLs may have reduced jitter performance.

The input reference clocks reside in banks 3A, 3B, 8A, and 8B have dedicated  $V_{CC\_CLKIN3A}$ ,  $V_{CC\_CLKIN3B}$ ,  $V_{CC\_CLKIN8A}$ , and  $V_{CC\_CLKIN8B}$  power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for general purpose I/Os (GPIOs). Table 1–6 lists the supported I/O standard for the REFCLK pins.

| I/O Standard                | HSSI     |                                                 | Terminatio | VCC_CLKIN Level |               | I/O Pin Type |         |                    |

|-----------------------------|----------|-------------------------------------------------|------------|-----------------|---------------|--------------|---------|--------------------|

|                             | Protocol | Coupling                                        | n          | Input           | Output        | Column I/O   | Row I/O | Supported<br>Banks |

| LVDS                        | ALL      | Differential                                    | Off-chip   | 2.5 V           | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |

| LVPECL                      | ALL      | AC (Needs<br>off-chip<br>resistor to<br>restore | Off-chip   | 2.5 V           | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |

| 4 0 1 4 5 1                 | ALL      |                                                 | Off-chip   | 2.5 V           | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |

| 1.2 V, 1.5 V,<br>3.3 V PCML | ALL      |                                                 | Off-chip   | 2.5 V           | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |

|                             | ALL      | V <sub>CM</sub> )                               | Off-chip   | 2.5 V           | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |

| HCSL                        | PCle     | Differential<br>DC                              | Off-chip   | 2.5 V           | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |

Table 1–6. REFCLK I/O Standard Support

In any configuration, a receiver channel cannot source CDR clocks from other PLLs beyond the two multipurpose PLLs directly adjacent to transceiver block where the channel resides.

The Cyclone IV GX transceivers support non-bonded (×1) and bonded (×2 and ×4) channel configurations. The two configurations differ in regards to clocking and phase compensation FIFO control. Bonded configuration provides a relatively lower channel-to-channel skew between the bonded channels than in non-bonded configuration. Table 1–8 lists the supported conditions in non-bonded and bonded channel configurations.

Table 1–8. Supported Conditions in Non-Bonded and Bonded Channel Configurations

| Channel<br>Configuration | Description                                                                                                                                                            | Supported Channel<br>Operation Mode                           |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Non-bonded               | <ul> <li>Low-speed clock in each channel is sourced independently</li> <li>Phase compensation FIFO in each channel has its own pointers and control logic</li> </ul>   | <ul><li>Transmitter Only</li><li>Receiver Only</li></ul>      |

| (×1)                     |                                                                                                                                                                        | <ul> <li>Transmitter and<br/>Receiver</li> </ul>              |

| Bonded (×2<br>and ×4)    | <ul> <li>Low-speed clock in each bonded channel is sourced from a common bonded<br/>clock path for lower channel-to-channel skew</li> </ul>                            | <ul> <li>Transmitter Only</li> <li>Transmitter and</li> </ul> |

|                          | <ul> <li>Phase compensation FIFOs in bonded channels share common pointers and<br/>control logic for equal latency through the FIFOs in all bonded channels</li> </ul> | Receiver                                                      |

|                          | <ul> <li>×2 bonded configuration is supported with channel 0 and channel 1 in a<br/>transceiver block</li> </ul>                                                       |                                                               |

|                          | • ×4 bonded configuration is supported with all four channels in a transceiver block                                                                                   |                                                               |

### **Non-Bonded Channel Configuration**

In non-bonded channel configuration, the high- and low-speed clocks for each channel are sourced independently. The phase compensation FIFOs in each channel has its own pointers and control logic. When implementing multi-channel serial interface in non-bonded channel configuration, the clock skew and unequal latency results in larger channel-to-channel skew.

Altera recommends using bonded channel configuration (×2 or ×4) when implementing multi-channel serial interface for a lower channel-to-channel skew.

In a transceiver block, the high- and low-speed clocks for each channel are distributed primarily from one of the two multipurpose PLLs directly adjacent to the block. Transceiver channels for devices in F484 and larger packages support additional clocking flexibility. In these packages, some channels support high-speed and low-speed clock distribution from PLLs beyond the two multipurpose PLLs directly adjacent to the block.

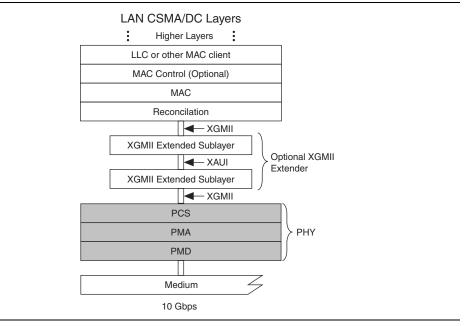

converted within the XGMII extender sublayer into an 8B/10B encoded data stream. Each data stream is then transmitted across a single differential pair running at 3.125 Gbps. At the XAUI receiver, the incoming data is decoded and mapped back to the 32bit XGMII format. This provides a transparent extension of the physical reach of the XGMII and also reduces the interface pin count.

Figure 1–62. XAUI in 10 Gbps LAN Layers

XAUI functions as a self-managed interface because code group synchronization, channel deskew, and clock domain decoupling is handled with no upper layer support requirements. This functionality is based on the PCS code groups that are used during the inter-packet gap time and idle periods.

### **Clock Rate Compensation**

In XAUI mode, the rate match FIFO compensates up to  $\pm 100$  ppm (200 ppm total) difference between the upstream transmitter and the local receiver reference clock. The XAUI protocol requires the transmitter to send /R/ (/K28.0/) code groups simultaneously on all four lanes (denoted as ||R|| column) during inter-packet gaps, adhering to rules listed in the IEEE P802.3ae specification.

The rate match operation begins after rx\_syncstatus and rx\_channelaligned are asserted. The rx\_syncstatus signal is from the word aligner, indicating that synchronization is acquired on all four channels, while rx\_channelaligned signal is from the deskew FIFO, indicating channel alignment.

The rate match FIFO looks for the ||R|| column (simultaneous /R/ code groups on all four channels) and deletes or inserts ||R|| columns to prevent the rate match FIFO from overflowing or under running. The rate match FIFO can insert or delete as many ||R|| columns as necessary to perform the rate match operation.

The rx\_rmfifodatadeleted and rx\_rmfifodatainserted flags that indicate rate match FIFO deletion and insertion events, respectively, are forwarded to the FPGA fabric. If an ||R|| column is deleted, the rx\_rmfifodeleted flag from each of the four channels goes high for one clock cycle per deleted ||R|| column. If an ||R|| column is inserted, the rx\_rmfifoinserted flag from each of the four channels goes high for one clock cycle per deleted ||R|| column. If an ||R|| column is inserted, the rx\_rmfifoinserted flag from each of the four channels goes high for one clock cycle per inserted ||R|| column.

The rate match FIFO does not insert or delete code groups automatically to overcome FIFO empty or full conditions. In this case, the rate match FIFO asserts the rx\_rmfifofull and rx\_rmfifoempty flags for at least three recovered clock cycles to indicate rate match FIFO full and empty conditions, respectively. You must then assert the rx\_digitalreset signal to reset the receiver PCS blocks.

# **Deterministic Latency Mode**

Deterministic Latency mode provides the transceiver configuration that allows no latency uncertainty in the datapath and features to strictly control latency variation. This mode supports non-bonded (×1) and bonded (×4) channel configurations, and is typically used to support CPRI and OBSAI protocols that require accurate delay measurements along the datapath. The Cyclone IV GX transceivers configured in Deterministic Latency mode provides the following features:

- registered mode phase compensation FIFO

- receive bit-slip indication

- transmit bit-slip control

- PLL PFD feedback

# **User Reset and Power-Down Signals**

Each transceiver channel in the Cyclone IV GX device has individual reset signals to reset its physical coding sublayer (PCS) and physical medium attachment (PMA). The transceiver block also has a power-down signal that affects the multipurpose phase-locked loops (PLLs), general purpose PLLs, and all the channels in the transceiver block.

Table 2–1 lists the reset signals available for each transceiver channel.

| Signal                         | ALTGX MegaWizard Plug-In<br>Manager Configurations                  | Description                                                                                                               |  |  |  |  |

|--------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| tx_digitalreset <sup>(1)</sup> | <ul><li>Transmitter Only</li><li>Receiver and Transmitter</li></ul> | Provides asynchronous reset to all digital logic in<br>the transmitter PCS, including the XAUI transmit<br>state machine. |  |  |  |  |

|                                |                                                                     | The minimum pulse width for this signal is two parallel clock cycles.                                                     |  |  |  |  |

|                                | <ul> <li>Receiver Only</li> <li>Receiver and Transmitter</li> </ul> | Resets all digital logic in the receiver PCS, including:                                                                  |  |  |  |  |

|                                |                                                                     | <ul> <li>XAUI receiver state machines</li> </ul>                                                                          |  |  |  |  |

|                                |                                                                     | <ul> <li>GIGE receiver state machines</li> </ul>                                                                          |  |  |  |  |

| rx_digitalreset <sup>(1)</sup> |                                                                     | <ul> <li>XAUI channel alignment state machine</li> </ul>                                                                  |  |  |  |  |

|                                |                                                                     | <ul> <li>BIST-PRBS verifier</li> </ul>                                                                                    |  |  |  |  |

|                                |                                                                     | <ul> <li>BIST-incremental verifier</li> </ul>                                                                             |  |  |  |  |

|                                |                                                                     | The minimum pulse width for this signal is two parallel clock cycles.                                                     |  |  |  |  |

|                                | <ul> <li>Receiver Only</li> <li>Receiver and Transmitter</li> </ul> | Resets the receiver CDR present in the receiver channel.                                                                  |  |  |  |  |

| rx_analogreset                 |                                                                     | The minimum pulse width is two parallel clock cycles.                                                                     |  |  |  |  |

Table 2–1. Transceiver Channel Reset Signals

### Note to Table 2–1:

(1) Assert this signal until the clocks coming out of the multipurpose PLL and receiver CDR are stabilized. Stable parallel clocks are essential for proper operation of transmitter and receiver phase-compensation FIFOs in the PCS.

| Transceiver Block                        | rx_digitalreset | rx_analogreset | tx_digitalreset | pll_areset | gxb_powerdown |

|------------------------------------------|-----------------|----------------|-----------------|------------|---------------|

| Serializer                               | —               |                | $\checkmark$    |            | $\checkmark$  |

| Transmitter Buffer                       | —               |                | —               | _          | $\checkmark$  |

| Transmitter XAUI State<br>Machine        | _               | —              | ~               | _          | ~             |

| Receiver Buffer                          | —               |                | —               | _          | $\checkmark$  |

| Receiver CDR                             | —               | $\checkmark$   | —               | —          | $\checkmark$  |

| Receiver Deserializer                    | —               |                | —               |            | $\checkmark$  |

| Receiver Word Aligner                    | $\checkmark$    |                | —               | _          | $\checkmark$  |

| Receiver Deskew FIFO                     | $\checkmark$    |                | —               | —          | $\checkmark$  |

| Receiver Clock Rate<br>Compensation FIFO | ~               | _              | —               | _          | ~             |

| Receiver 8B/10B<br>Decoder               | ~               | _              | _               | _          | ~             |

| Receiver Byte<br>Deserializer            | ~               | _              | _               | _          | ~             |

| Receiver Byte Ordering                   | ~               | —              | —               | —          | $\checkmark$  |

| Receiver Phase<br>Compensation FIFO      | ~               | _              | _               | _          | ~             |

| Receiver XAUI State<br>Machine           | ~               | —              | —               | _          | ~             |

| BIST Verifiers                           | ~               | —              | —               | —          | $\checkmark$  |

Table 2–3. Blocks Affected by Reset and Power-Down Signals (Part 2 of 2)

# **Transceiver Reset Sequences**

You can configure transceiver channels in Cyclone IV GX devices in various configurations. In all functional modes except XAUI functional mode, transceiver channels can be either bonded or non-bonded. In XAUI functional mode, transceiver channels must be bonded. In PCI Express<sup>®</sup> (PCIe<sup>®</sup>) functional mode, transceiver channels can be either bonded or non-bonded and need to follow a specific reset sequence.

The two categories of reset sequences for Cyclone IV GX devices described in this chapter are:

- "All Supported Functional Modes Except the PCIe Functional Mode" on page 2–6—describes the reset sequences in bonded and non-bonded configurations.

- "PCIe Functional Mode" on page 2–17—describes the reset sequence for the initialization/compliance phase and the normal operation phase in PCIe functional modes.

This solution may violate some of the protocol specific requirements. In such case, you can use Manual CDR lock option.

- For Manual CDR lock mode, rx\_freqlocked signal is not available. Upon detection of a dead link, take the following steps:

- a. Switch to LTR mode.

- b. Assert rx\_digitalreset.

- c. Wait for rx\_pll\_locked to go high.

- d. When you detect incoming data on the receive pins, switch to LTD mode.

- e. Wait for a duration of  $t_{LTD\_Manual}$ , which is the time taken to recover valid data after the rx\_locktodata signal is asserted in manual mode.

- f. De-assert rx\_digitalreset.

| Symbol                          | Modes | C6  |     | C7, 17 |     | C8, A7 |     | C8L, I8L |     | C9L |     | Unit |

|---------------------------------|-------|-----|-----|--------|-----|--------|-----|----------|-----|-----|-----|------|

|                                 |       | Min | Max | Min    | Max | Min    | Max | Min      | Max | Min | Max | UIII |

| t <sub>DUTY</sub>               | —     | 45  | 55  | 45     | 55  | 45     | 55  | 45       | 55  | 45  | 55  | %    |

| TCCS                            | —     | _   | 200 | —      | 200 | _      | 200 | _        | 200 | —   | 200 | ps   |

| Output jitter<br>(peak to peak) | _     |     | 500 | _      | 500 | _      | 550 | _        | 600 | _   | 700 | ps   |

| t <sub>LOCK</sub> (2)           | _     |     | 1   | _      | 1   |        | 1   |          | 1   | _   | 1   | ms   |

### Table 1–35. Emulated LVDS Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

#### Notes to Table 1-35:

(1) Cyclone IV E—emulated LVDS transmitter is supported at the output pin of all I/O Banks.

Cyclone IV GX—emulated LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                    | Modes | C6  |       | C7, I7 |       | C8, A7 |       | C8L, 18L |     | C9L |     | 11-1-14 |

|---------------------------|-------|-----|-------|--------|-------|--------|-------|----------|-----|-----|-----|---------|

|                           |       | Min | Max   | Min    | Max   | Min    | Max   | Min      | Max | Min | Max | Unit    |

| f <sub>HSCLK</sub> (input | ×10   | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz     |

|                           | ×8    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz     |

|                           | ×7    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz     |

| clock<br>frequency)       | ×4    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz     |

|                           | ×2    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz     |

|                           | ×1    | 10  | 437.5 | 10     | 402.5 | 10     | 402.5 | 10       | 362 | 10  | 265 | MHz     |

|                           | ×10   | 100 | 875   | 100    | 740   | 100    | 640   | 100      | 640 | 100 | 500 | Mbps    |

|                           | ×8    | 80  | 875   | 80     | 740   | 80     | 640   | 80       | 640 | 80  | 500 | Mbps    |

| HSIODR                    | ×7    | 70  | 875   | 70     | 740   | 70     | 640   | 70       | 640 | 70  | 500 | Mbps    |

| HOIDDA                    | ×4    | 40  | 875   | 40     | 740   | 40     | 640   | 40       | 640 | 40  | 500 | Mbps    |

|                           | ×2    | 20  | 875   | 20     | 740   | 20     | 640   | 20       | 640 | 20  | 500 | Mbps    |

|                           | ×1    | 10  | 437.5 | 10     | 402.5 | 10     | 402.5 | 10       | 362 | 10  | 265 | Mbps    |

| SW                        | —     | _   | 400   | _      | 400   | _      | 400   | _        | 550 | _   | 640 | ps      |

| Input jitter<br>tolerance | _     | _   | 500   | _      | 500   | _      | 550   | _        | 600 | _   | 700 | ps      |

| t <sub>LOCK</sub> (2)     | —     | _   | 1     | —      | 1     | _      | 1     | —        | 1   | —   | 1   | ms      |

Table 1–36. LVDS Receiver Timing Specifications for Cyclone IV Devices (1), (3)

#### Notes to Table 1-36:

(1) Cyclone IV E—LVDS receiver is supported at all I/O Banks.

Cyclone IV GX—LVDS receiver is supported at I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

### **External Memory Interface Specifications**

The external memory interfaces for Cyclone IV devices are auto-calibrating and easy to implement.