## Intel - EP4CE40F29I7 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                  |

|--------------------------------|---------------------------------------------------------|

| Number of LABs/CLBs            | 2475                                                    |

| Number of Logic Elements/Cells | 39600                                                   |

| Total RAM Bits                 | 1161216                                                 |

| Number of I/O                  | 532                                                     |

| Number of Gates                |                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 780-BGA                                                 |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce40f29i7 |

|                                |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Cyclone IV GX devices offer up to eight high-speed transceivers that provide:

- Data rates up to 3.125 Gbps

- 8B/10B encoder/decoder

- 8-bit or 10-bit physical media attachment (PMA) to physical coding sublayer (PCS) interface

- Byte serializer / deserializer (SERDES)

- Word aligner

- Rate matching FIFO

- TX bit slipper for Common Public Radio Interface (CPRI)

- Electrical idle

- Dynamic channel reconfiguration allowing you to change data rates and protocols on-the-fly

- Static equalization and pre-emphasis for superior signal integrity

- 150 mW per channel power consumption

- Flexible clocking structure to support multiple protocols in a single transceiver block

- Cyclone IV GX devices offer dedicated hard IP for PCI Express (PIPE) (PCIe) Gen 1:

- ×1, ×2, and ×4 lane configurations

- End-point and root-port configurations

- Up to 256-byte payload

- One virtual channel

- 2 KB retry buffer

- 4 KB receiver (Rx) buffer

- Cyclone IV GX devices offer a wide range of protocol support:

- PCIe (PIPE) Gen 1 ×1, ×2, and ×4 (2.5 Gbps)

- Gigabit Ethernet (1.25 Gbps)

- CPRI (up to 3.072 Gbps)

- XAUI (3.125 Gbps)

- Triple rate serial digital interface (SDI) (up to 2.97 Gbps)

- Serial RapidIO (3.125 Gbps)

- Basic mode (up to 3.125 Gbps)

- V-by-One (up to 3.0 Gbps)

- DisplayPort (2.7 Gbps)

- Serial Advanced Technology Attachment (SATA) (up to 3.0 Gbps)

- OBSAI (up to 3.072 Gbps)

# **Cyclone IV Device Family Speed Grades**

Table 1–5 lists the Cyclone IV GX devices speed grades.

| Device    | F169           | F324                                    | F484           | F672           | F896       |  |  |

|-----------|----------------|-----------------------------------------|----------------|----------------|------------|--|--|

| EP4CGX15  | C6, C7, C8, I7 | —                                       | —              | —              | —          |  |  |

| EP4CGX22  | C6, C7, C8, I7 | C6, C7, C8, I7                          | —              | —              | —          |  |  |

| EP4CGX30  | C6, C7, C8, I7 | 7, C8, I7 C6, C7, C8, I7 C6, C7, C8, I7 |                | —              | —          |  |  |

| EP4CGX50  | —              | —                                       | C6, C7, C8, I7 | C6, C7, C8, I7 | —          |  |  |

| EP4CGX75  | —              | —                                       | C6, C7, C8, I7 | C6, C7, C8, I7 | —          |  |  |

| EP4CGX110 | —              | —                                       | C7, C8, I7     | C7, C8, I7     | C7, C8, I7 |  |  |

| EP4CGX150 | —              | —                                       | C7, C8, I7     | C7, C8, I7     | C7, C8, I7 |  |  |

## Table 1–5. Speed Grades for the Cyclone IV GX Device Family

Table 1–6 lists the Cyclone IV E devices speed grades.

| Table 1-6. | <b>Speed Grades</b> | for the Cyclone | IV E Device Fa | mily (1), (2) |

|------------|---------------------|-----------------|----------------|---------------|

|------------|---------------------|-----------------|----------------|---------------|

| Device   | E144                                   | M164 | M256     | U256 | F256                                   | F324 | U484                                       | F484                                   | F780                            |

|----------|----------------------------------------|------|----------|------|----------------------------------------|------|--------------------------------------------|----------------------------------------|---------------------------------|

| EP4CE6   | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _                                          | _                                      | _                               |

| EP4CE10  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _                                          | _                                      | _                               |

| EP4CE15  | C8L, C9L, I8L<br>C6, C7, C8, I7        | I7N  | C7N, 17N | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | — C8L, C9L, I8L<br>— C6, C7, C8, I7,<br>A7 |                                        | _                               |

| EP4CE22  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    |          | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _                                          | _                                      | _                               |

| EP4CE30  | _                                      | _    | _        | _    | _                                      | A7N  | _                                          | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE40  | _                                      | _    | _        | _    | _                                      | A7N  | I7N                                        | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE55  | —                                      | _    | _        | _    | _                                      | _    | 17N                                        | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE75  | _                                      |      |          |      | _                                      |      | 17N                                        | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE115 | _                                      |      | _        |      | —                                      |      |                                            | C8L, C9L, I8L<br>C7, C8, I7            | C8L, C9L, I8L<br>C7, C8, I7     |

#### Notes to Table 1-6:

(1) C8L, C9L, and I8L speed grades are applicable for the 1.0-V core voltage.

(2) C6, C7, C8, I7, and A7 speed grades are applicable for the 1.2-V core voltage.

# 3. Memory Blocks in Cyclone IV Devices

Cyclone<sup>®</sup> IV devices feature embedded memory structures to address the on-chip memory needs of Altera<sup>®</sup> Cyclone IV device designs. The embedded memory structure consists of columns of M9K memory blocks that you can configure to provide various memory functions, such as RAM, shift registers, ROM, and FIFO buffers.

This chapter contains the following sections:

- "Memory Modes" on page 3–7

- "Clocking Modes" on page 3–14

- "Design Considerations" on page 3–15

# **Overview**

M9K blocks support the following features:

- 8,192 memory bits per block (9,216 bits per block including parity)

- Independent read-enable (rden ) and write-enable (wren ) signals for each port

- Packed mode in which the M9K memory block is split into two 4.5 K single-port RAMs

- Variable port configurations

- Single-port and simple dual-port modes support for all port widths

- True dual-port (one read and one write, two reads, or two writes) operation

- Byte enables for data input masking during writes

- Two clock-enable control signals for each port (port A and port B)

- Initialization file to pre-load memory content in RAM and ROM modes

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and sumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Control Signals**

The clock-enable control signal controls the clock entering the input and output registers and the entire M9K memory block. This signal disables the clock so that the M9K memory block does not see any clock edges and does not perform any operations.

The rden and wren control signals control the read and write operations for each port of M9K memory blocks. You can disable the rden or wren signals independently to save power whenever the operation is not required.

# **Parity Bit Support**

Parity checking for error detection is possible with the parity bit along with internal logic resources. Cyclone IV devices M9K memory blocks support a parity bit for each storage byte. You can use this bit as either a parity bit or as an additional data bit. No parity function is actually performed on this bit.

# **Byte Enable Support**

Cyclone IV devices M9K memory blocks support byte enables that mask the input data so that only specific bytes of data are written. The unwritten bytes retain the previous written value. The wren signals, along with the byte-enable (byteena ) signals, control the write operations of the RAM block. The default value of the byteena signals is high (enabled), in which case writing is controlled only by the wren signals. There is no clear port to the byteena registers. M9K blocks support byte enables when the write port has a data width of ×16, ×18, ×32, or ×36 bits.

Byte enables operate in one-hot manner, with the LSB of the byteena signal corresponding to the least significant byte of the data bus. For example, if byteena = 01 and you are using a RAM block in ×18 mode, data[8..0] is enabled and data[17..9] is disabled. Similarly, if byteena = 11 , both data[8..0] and data[17..9] are enabled. Byte enables are active high.

Table 3–2 lists the byte selection.

| hutoono[2_0] |            | Affecte    | d Bytes    |            |  |  |  |  |  |

|--------------|------------|------------|------------|------------|--|--|--|--|--|

| byteena[30]  | datain ×16 | datain ×18 | datain ×32 | datain ×36 |  |  |  |  |  |

| [0] = 1      | [70]       | [80]       | [70]       | [80]       |  |  |  |  |  |

| [1] = 1      | [158]      | [179]      | [158]      | [179]      |  |  |  |  |  |

| [2] = 1      | _          | —          | [2316]     | [2618]     |  |  |  |  |  |

| [3] = 1      |            | —          | [3124]     | [3527]     |  |  |  |  |  |

Table 3–2. byteena for Cyclone IV Devices M9K Blocks (1)

Note to Table 3-2:

(1) Any combination of byte enables is possible.

# 5. Clock Networks and PLLs in Cyclone IV Devices

This chapter describes the hierarchical clock networks and phase-locked loops (PLLs) with advanced features in the Cyclone<sup>®</sup> IV device family. It includes details about the ability to reconfigure the PLL counter clock frequency and phase shift in real time, allowing you to sweep PLL output frequencies and dynamically adjust the output clock phase shift.

The Quartus<sup>®</sup> II software enables the PLLs and their features without external devices.

This chapter contains the following sections:

- "Clock Networks" on page 5–1

- "PLLs in Cyclone IV Devices" on page 5–18

- "Cyclone IV PLL Hardware Overview" on page 5–20

- "Clock Feedback Modes" on page 5–23

- "Hardware Features" on page 5–26

- "Programmable Bandwidth" on page 5–32

- "Phase Shift Implementation" on page 5–32

- "PLL Cascading" on page 5–33

- "PLL Reconfiguration" on page 5–34

- "Spread-Spectrum Clocking" on page 5–41

- "PLL Specifications" on page 5–41

# **Clock Networks**

The Cyclone IV GX device provides up to 12 dedicated clock pins (CLK[15..4] ) that can drive the global clocks (GCLKs). Cyclone IV GX devices support four dedicated clock pins on each side of the device except the left side. These clock pins can drive up to 30 GCLKs.

The Cyclone IV E device provides up to 15 dedicated clock pins (CLK[15..1] ) that can drive up to 20 GCLKs. Cyclone IV E devices support three dedicated clock pins on the left side and four dedicated clock pins on the top, right, and bottom sides of the device except EP4CE6 and EP4CE10 devices. EP4CE6 and EP4CE10 devices only support three dedicated clock pins on the left side and four dedicated clock pins on the right side of the device.

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| GCLK Network Clock      |   |   |   |   |   | GCLK Networks |              |              |              |              |              |              |              | GC           | LK No        | etwo |              |              |    |    |              |              |              |              |              |              |    |    |              |              |

|-------------------------|---|---|---|---|---|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|------|--------------|--------------|----|----|--------------|--------------|--------------|--------------|--------------|--------------|----|----|--------------|--------------|

| Sources                 | 0 | 1 | 2 | 3 | 4 | 5             | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15   | 16           | 17           | 18 | 19 | 20           | 21           | 22           | 23           | 24           | 25           | 26 | 27 | 28           | 29           |

| PLL_8_C0 (3)            | — | — | — | — | — | —             | $\checkmark$ | —            | $\checkmark$ | —            | —            |              | _            | —            | —            | _    | —            |              | —  | —  |              | —            | —            | —            | —            | —            | —  | —  |              | —            |

| PLL_8_C1 <sup>(3)</sup> | - | — | — | — | — | —             | —            | —            | —            | —            | —            |              | _            | —            | _            | _    | —            | _            | —  | —  | —            | —            | —            | —            | —            | —            | —  | —  | —            | —            |

| PLL_8_C2 <sup>(3)</sup> | — | — | — | — | — | —             | —            | —            | —            | —            | —            | _            |              | —            | _            |      | —            | _            | —  | —  |              | —            | —            | —            | —            | —            | —  | —  |              | —            |

| PLL_8_C3 (3)            | — | — | — | — | — | —             | —            | $\checkmark$ | —            | $\checkmark$ | —            |              | _            | —            |              | _    | —            |              | —  | —  | —            | —            | —            | —            | —            | —            | —  | —  |              | —            |

| PLL_8_C4 (3)            | — | — | — | — | — | —             | —            | —            | $\checkmark$ | —            | $\checkmark$ | $\checkmark$ |              | —            | _            |      | —            | _            | —  | —  |              | —            | —            | —            | —            | —            | —  | —  |              | —            |

| DPCLK0                  | — | — | — | — | — | —             | —            | —            | —            | —            | —            | _            |              | —            | _            |      | —            | _            | —  | —  |              | —            | —            | —            | —            | $\checkmark$ | —  | —  |              | —            |

| DPCLK1                  | — | — | — | — | — | —             | —            | —            | —            | —            | —            | Ι            |              | —            |              |      | —            |              | —  | —  | —            | —            | —            | —            | —            | —            | —  | ~  | —            | —            |

| DPCLK2                  | — | — | — | — | — | —             | —            | —            | —            | —            | —            | _            |              |              | _            |      | —            |              | —  |    |              | —            | —            | —            | —            | —            | —  | —  |              | $\checkmark$ |

| DPCLK3                  | — | — | — | — | — |               | —            | —            | —            | —            | —            | _            |              |              | _            |      | —            |              | —  |    |              | —            | —            | —            | $\checkmark$ | —            | —  | —  |              | —            |

| DPCLK4                  | — | — | — | — | — | —             | —            | —            | —            | —            | —            |              |              |              | _            |      | —            |              | —  |    |              | —            | —            | —            | —            | —            | ~  | —  |              | —            |

| DPCLK5                  | — | — | — | — | — | —             | —            | —            | —            | —            | —            |              |              |              | _            |      | —            |              | —  |    |              | —            | —            | —            | —            | —            | —  | —  | $\checkmark$ | —            |

| DPCLK6                  | — | — | — | — | — | _             | —            | —            | —            | —            | —            |              | _            |              | _            | _    | —            | $\checkmark$ | —  |    |              | —            | —            | —            | —            | —            | —  | —  |              | —            |

| DPCLK7                  | - | — | — | — | — | —             | —            | —            | —            | —            | —            | -            | —            | —            | —            | ~    | —            | _            | —  | —  |              | —            | —            | —            | —            | —            | —  | —  |              | —            |

| DPCLK8                  | — | — | — | — | — | _             | —            | —            | —            | —            | —            |              | _            | $\checkmark$ | _            | _    | —            | _            | —  |    |              | —            | —            | —            | —            | —            | —  | —  |              | —            |

| DPCLK9                  | - | — | — | — | — | —             | —            | —            | —            | —            | —            | -            | —            | —            | —            | _    | $\checkmark$ | _            | —  | —  |              | —            | —            | —            | —            | —            | —  | —  |              | —            |

| DPCLK10                 | — | — | — | — | — | _             | —            | —            | —            | —            | —            | -            | _            |              | $\checkmark$ | _    | —            | _            | —  |    |              | —            | —            | —            | —            | —            | —  | —  |              | —            |

| DPCLK11                 | — | — | — | _ | _ |               | —            | —            | —            | _            | _            |              | $\checkmark$ |              | -            | _    | _            | _            | —  |    |              | —            | —            |              | _            | _            | —  | —  | —            | —            |

| DPCLK12                 | — | — | — | — | — | —             | —            | —            | —            | —            | —            |              |              |              | _            | —    | —            | _            | —  |    |              | —            | $\checkmark$ | —            | —            | —            | —  | —  |              | —            |

| DPCLK13                 | — | — | — | — | — | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | —    | —            | —            | —  | —  | $\checkmark$ | —            | —            | —            | —            | —            | —  | —  | —            | —            |

| DPCLK14                 | — | — | — | — | — |               | —            | —            | —            | —            | —            | —            | —            |              | —            | —    | —            | —            | ~  |    |              | —            | —            |              |              | —            | —  | —  |              | —            |

| DPCLK15                 | — | — | — | — | — | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | —    | —            | —            | —  | —  | —            | —            | —            | $\checkmark$ | —            | —            | —  | —  | —            | —            |

| DPCLK16                 | — | — | — | — | — | —             | —            | —            | —            | —            | —            |              | _            | —            | _            | _    | —            | —            | —  | —  | —            | $\checkmark$ | —            | —            | —            | —            | —  | —  | —            | —            |

## Table 5-2. GCLK Network Connections for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices (1), (2) (Part 3 of 4)

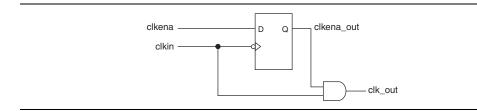

Figure 5–7 shows how to implement the clkena signal with a single register.

#### Figure 5–7. clkena Implementation

The clkena circuitry controlling the output C0 of the PLL to an output pin is implemented with two registers instead of a single register, as shown in Figure 5–7.

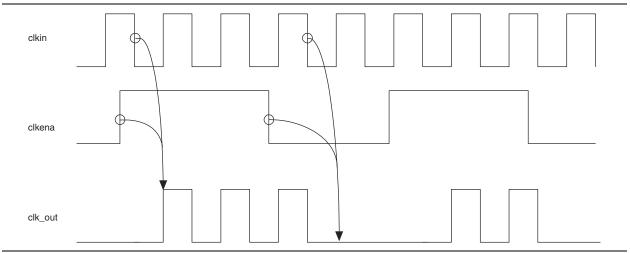

Figure 5–8 shows the waveform example for a clock output enable. The clkena signal is sampled on the falling edge of the clock (clkin ).

This feature is useful for applications that require low power or sleep mode.

Figure 5–8. clkena Implementation: Output Enable

The clkena signal can also disable clock outputs if the system is not tolerant to frequency overshoot during PLL resynchronization.

Altera recommends using the clkena signals when switching the clock source to the PLLs or the GCLK. The recommended sequence is:

- 1. Disable the primary output clock by de-asserting the clkena signal.

- 2. Switch to the secondary clock using the dynamic select signals of the clock control block.

- 3. Allow some clock cycles of the secondary clock to pass before reasserting the clkena signal. The exact number of clock cycles you must wait before enabling the secondary clock is design-dependent. You can build custom logic to ensure glitch-free transition when switching between different clock sources.

| Differential I/O Standards         | I/O Bank Location | External Resistor<br>Network at<br>Transmitter | Transmitter (TX)      | Receiver (RX) |  |

|------------------------------------|-------------------|------------------------------------------------|-----------------------|---------------|--|

| LVDS                               | 5,6               | Not Required                                   |                       | $\checkmark$  |  |

| LVDS                               | 3,4,5,6,7,8       | Three Resistors                                | · ·                   | ~             |  |

|                                    | 5,6               | Not Required                                   |                       |               |  |

| RSDS                               | 3,4,7,8           | Three Resistors                                | <ul> <li>✓</li> </ul> | —             |  |

|                                    | 3,4,5,6,7,8       | Single Resistor                                |                       |               |  |

|                                    | 5,6               | Not Required                                   |                       |               |  |

| mini-LVDS                          | 3,4,5,6,7,8       | Three Resistors                                |                       |               |  |

|                                    | 5,6               | Not Required                                   |                       |               |  |

| PPDS                               | 3,4,5,6,7,8       | Three Resistors                                |                       |               |  |

| BLVDS (1)                          | 3,4,5,6,7,8       | Single Resistor                                | $\checkmark$          | $\checkmark$  |  |

| LVPECL (2)                         | 3,4,5,6,7,8       | —                                              |                       | $\checkmark$  |  |

| Differential SSTL-2 <sup>(3)</sup> | 3,4,5,6,7,8       | —                                              | $\checkmark$          | $\checkmark$  |  |

| Differential SSTL-18 (3)           | 3,4,5,6,7,8       | —                                              | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-18 (3)           | 3,4,5,6,7,8       | —                                              | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-15 (3)           | 3,4,5,6,7,8       | —                                              | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-12 (3)           | 4,5,6,7,8         | —                                              | $\checkmark$          | $\checkmark$  |  |

Table 6–7. Differential I/O Standards Supported in Cyclone IV GX I/O Banks

#### Notes to Table 6-7:

(1) Transmitter and Receiver  $f_{MAX}$  depend on system topology and performance requirement.

(2) The LVPECL I/O standard is only supported on dedicated clock input pins.

(3) The differential SSTL-2, SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards are only supported on clock input pins and PLL output clock pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards.

You can use I/O pins and internal logic to implement a high-speed differential interface in Cyclone IV devices. Cyclone IV devices do not contain dedicated serialization or deserialization circuitry. Therefore, shift registers, internal phase-locked loops (PLLs), and I/O cells are used to perform serial-to-parallel conversions on incoming data and parallel-to-serial conversion on outgoing data. The differential interface data serializers and deserializers (SERDES) are automatically constructed in the core logic elements (LEs) with the Quartus II software ALTLVDS megafunction.

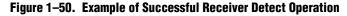

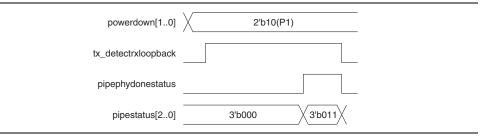

Figure 1–50 and Figure 1–51 show the detection mechanism example for a successful and unsuccessful receiver detection scenarios respectively. The tx\_forceelecidle port must be asserted at least 10 parallel clock cycles prior to assertion of tx\_detectrxloop port to ensure the transmitter buffer is properly tri-stated. Detection completion is indicated by pipephydonestatus assertion, with detection successful indicated by 3'b011 on pipestatus[2..0] port, or detection unsuccessful by 3'b000 on pipestatus[2..0] port.

Figure 1–51. Example of Unsuccessful Receiver Detect Operation

| powerdown[10]       | 2'b10(P1) |  |

|---------------------|-----------|--|

| tx_detectrxloopback |           |  |

| pipephydonestatus   |           |  |

| pipestatus[20]      | 3'b000    |  |

## **Electrical Idle Control**

The Cyclone IV GX transceivers support transmitter buffer in electrical idle state using the tx\_forceelecidle port. During electrical idle, the transmitter buffer differential and common mode output voltage levels are compliant to the PCIe Base Specification 2.0 for Gen1 signaling rate.

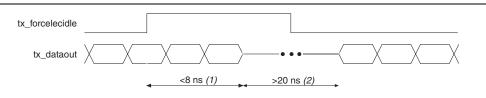

Figure 1–52 shows the relationship between assertion of the  $tx_forceelecidle$  port and the transmitter buffer output on the  $tx_dataout$  port.

Figure 1–52. Transmitter Buffer Electrical Idle State

#### Notes to Figure 1-52:

- (1) The protocol requires the transmitter buffer to transition to a valid electrical idle after sending an electrical idle ordered set within 8 ns.

- (2) The protocol requires transmitter buffer to stay in electrical idle for a minimum of 20 ns for Gen1 signaling rate.

| Block  | Port Name                    | Input/<br>Output | Clock Domain                                                                             | Description                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|--------|------------------------------|------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        | tx_datain                    | Input            | Synchronous to<br>tx_clkout (non-<br>bonded modes) or<br>coreclkout (bonded<br>modes)    | <ul> <li>Parallel data input from the FPGA fabric to the transmitter.</li> <li>Bus width depends on channel width multiplied by number of channels per instance.</li> </ul>                                                                                                                                                                                       |  |  |  |  |

|        | tx_clkout                    | Output           | Clock signal                                                                             | <ul> <li>FPGA fabric-transmitter interface clock in non-bonded modes</li> <li>Each channel has a tx_clkout signal that can be used to clock data (tx_datain) from the FPGA fabric into the transmitter.</li> </ul>                                                                                                                                                |  |  |  |  |

|        | tx_coreclk                   | Input            | Clock signal                                                                             | Optional write clock port for the TX phase compensation FIFO.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|        | tx_phase_comp_fifo<br>_error | Output           | Synchronous to<br>tx_clkout (non-<br>bonded modes) or<br>coreclkout (bonded<br>modes)    | TX phase compensation FIFO full or empty indicator.<br>A high level indicates FIFO is either full or empty.                                                                                                                                                                                                                                                       |  |  |  |  |

| TX PCS | tx_ctrlenable                | Input            | Synchronous to<br>tx_clkout (non-<br>bonded modes) or<br>coreclkout (bonded<br>modes)    | <ul> <li>8B/10B encoder control or data identifier. This signal passes through the TX Phase Compensation FIFO.</li> <li>A high level to encode data as a /Kx.y/ control code group.</li> <li>A low level to encode data as a /Dx.y/ data code group.</li> </ul>                                                                                                   |  |  |  |  |

|        | tx_forcedisp                 | Input            | Synchronous to<br>tx_clkout (non-<br>bonded<br>modes) or<br>coreclkout<br>(bonded modes) | <ul> <li>8B/10B encoder forcing disparity control. This signal passes through the TX Phase Compensation FIFO.</li> <li>A high level to force encoding to positive or negative disparity depending on the tx_dispval signal level.</li> <li>A low level to allow default encoding according to the 8B/10B running disparity rules.</li> </ul>                      |  |  |  |  |

|        | tx_dispval Ir                | Input            | Synchronous to<br>tx_clkout (non-<br>bonded<br>modes) or<br>coreclkout<br>(bonded modes) | <ul> <li>8B/10B encoder forcing disparity value. This signal passes through the TX Phase Compensation FIFO.</li> <li>A high level to force encoding with a negative disparity code group when tx_forcedisp port is asserted high.</li> <li>A low level to force encoding with a positive disparity code group when tx_forcedisp port is asserted high.</li> </ul> |  |  |  |  |

|        | tx_invpolarity               | Input            | Asynchronous signal.<br>Minimum pulse width is<br>two parallel clock cycles.             | <ul> <li>Transmitter polarity inversion control.</li> <li>A high level to invert the polarity of every bit of the 8-<br/>or 10-bit input data to the serializer.</li> </ul>                                                                                                                                                                                       |  |  |  |  |

|        | tx_bitslipboundarys<br>elect | Input            | Asynchronous signal.                                                                     | Control the number of bits to slip before serializer. <ul> <li>Valid values from 0 to 9</li> </ul>                                                                                                                                                                                                                                                                |  |  |  |  |

|        | tx_dataout                   | Output           | —                                                                                        | Transmitter serial data output signal.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| TX PMA | tx_forceelec<br>idle         | Input            | Asynchronous signal.                                                                     | Force the transmitter buffer to PIPE electrical idle signal<br>levels. For equivalent signal defined in PIPE 2.00<br>specification, refer to Table 1–15 on page 1–54.                                                                                                                                                                                             |  |  |  |  |

Table 1–26. Transmitter Ports in ALTGX Megafunction for Cyclone IV GX

# **Document Revision History**

Table 1–30 lists the revision history for this chapter.

| Table 1-30. | Document  | Revision   | History |

|-------------|-----------|------------|---------|

|             | Boounione | 1101101011 |         |

| Date              | Version | Changes                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |         | ■ Updated the GiGE row in Table 1–14.                                                                                                                                                                                                                                                                                                                                             |

| February 2015     | 3.7     | <ul> <li>Updated the "GIGE Mode" section.</li> </ul>                                                                                                                                                                                                                                                                                                                              |

|                   |         | <ul> <li>Updated the note in the "Clock Frequency Compensation" section.</li> </ul>                                                                                                                                                                                                                                                                                               |

| October 2013      | 3.6     | Updated Figure 1–15 and Table 1–4.                                                                                                                                                                                                                                                                                                                                                |

| May 2013          | 3.5     | Updated Table 1–27 by setting "rx_locktodata" and "rx_locktorefclk" to "Input"                                                                                                                                                                                                                                                                                                    |

|                   |         | <ul> <li>Updated the data rate for the V-by-one protocol and the F324 package support in<br/>HD-SDI in Table 1–1.</li> </ul>                                                                                                                                                                                                                                                      |

| October 2012      | 3.4     | ■ Updated note (1) to Figure 1–27.                                                                                                                                                                                                                                                                                                                                                |

|                   |         | <ul> <li>Added latency information to Figure 1–67.</li> </ul>                                                                                                                                                                                                                                                                                                                     |

| November 2011     | 3.3     | <ul> <li>Updated "Word Aligner" and "Basic Mode" sections.</li> </ul>                                                                                                                                                                                                                                                                                                             |

| November 2011 3.3 |         | ■ Updated Figure 1–37.                                                                                                                                                                                                                                                                                                                                                            |

|                   |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                                                                                                                                                                                                                                                     |

|                   |         | ■ Updated Table 1–1, Table 1–5, Table 1–11, Table 1–14, Table 1–24, Table 1–25, Table 1–26, Table 1–27, Table 1–28, and Table 1–29.                                                                                                                                                                                                                                               |

| December 2010     | 3.2     | <ul> <li>Updated "8B/10B Encoder", "Transmitter Output Buffer", "Receiver Input Buffer",<br/>"Clock Data Recovery", "Miscellaneous Transmitter PCS Features", "Miscellaneous<br/>Receiver PCS Feature", "Input Reference Clocking", "PCI Express (PIPE) Mode",<br/>"Channel Deskewing", "Lane Synchronization", "Serial Loopback", and "Self Test<br/>Modes" sections.</li> </ul> |

|                   |         | ■ Added Figure 1–9, Figure 1–10, Figure 1–19, Figure 1–20, and Figure 1–43.                                                                                                                                                                                                                                                                                                       |

|                   |         | ■ Updated Figure 1–53, Figure 1–55, Figure 1–59, Figure 1–60, Figure 1–69, Figure 1–70, Figure 1–71, Figure 1–72, Figure 1–73, and Figure 1–74.                                                                                                                                                                                                                                   |

| November 2010     | 3.1     | Updated Introductory information.                                                                                                                                                                                                                                                                                                                                                 |

|                   |         | <ul> <li>Updated information for the Quartus II software version 10.0 release.</li> </ul>                                                                                                                                                                                                                                                                                         |

| July 2010         | 3.0     | <ul> <li>Reset control, power down, and dynamic reconfiguration information moved to<br/>new Cyclone IV Reset Control and Power Down and Cyclone IV Dynamic<br/>Reconfiguration chapters.</li> </ul>                                                                                                                                                                              |

As shown in Figure 2–12, perform the following reset procedure when using the dynamic reconfiguration controller to change the configuration of the transceiver channel:

- After power up and establishing that the transceiver is operating as desired, write the desired new value in the appropriate registers (including reconfig\_mode\_sel[2:0]) and subsequently assert the write\_all signal (marker 1) to initiate the dynamic reconfiguration.

- **To** For more information, refer to the *Cyclone IV Dynamic Reconfiguration* chapter.

- 2. Assert the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals.

- 3. As soon as write\_all is asserted, the dynamic reconfiguration controller starts to execute its operation. This is indicated by the assertion of the busy signal (marker 2).

- 4. Wait for the assertion of the channel\_reconfig\_done signal (marker 4) that indicates the completion of dynamic reconfiguration in this mode.

- 5. Deassert the tx\_digitalreset signal (marker 5). This signal must be deasserted after assertion of the channel\_reconfig\_done signal (marker 4) and before the deassertion of the rx\_analogreset signal (marker 6).

- Wait for at least five parallel clock cycles after assertion of the channel\_reconfig\_done signal (marker 4) to deassert the rx\_analogreset signal (marker 6).

- Lastly, wait for the rx\_freqlocked signal to go high. After rx\_freqlocked goes high (marker 7), wait for t<sub>LTD\_Auto</sub> to deassert the rx\_digitalreset signal (marker 8). At this point, the receiver is ready for data traffic.

# **Power Down**

The Quartus II software automatically selects the power-down channel feature, which takes effect when you configure the Cyclone IV GX device. All unused transceiver channels and blocks are powered down to reduce overall power consumption. The gxb\_powerdown signal is an optional transceiver block signal. It powers down all transceiver channels and all functional blocks in the transceiver block. The minimum pulse width for this signal is 1 µs. After power up, if you use the gxb\_powerdown signal for a minimum of 1 µs. Lastly, follow the sequence shown in Figure 2–13.

There are three methods that you can use to dynamically reconfigure the PMA controls of a transceiver channel:

- "Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels" on page 3–14

- "Method 2: Writing the Same Control Signals to Control All the Transceiver Channels" on page 3–16

- "Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same Time" on page 3–19

# Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels

Enable the logical\_channel\_address port by selecting the **Use** '**logical\_channel\_address' port** option on the **Analog controls** tab. This method is applicable only for a design where the dynamic reconfiguration controller controls more than one channel.

You can additionally reconfigure either the receiver portion, transmitter portion, or both the receiver and transmitter portions of the transceiver channel by setting the corresponding value on the rx\_tx\_duplex\_sel input port. For more information, refer to Table 3–2 on page 3–4.

## **Connecting the PMA Control Ports**

The selected PMA control ports remain fixed in width, regardless of the number of channels controlled by the ALTGX\_RECONFIG instance:

- tx\_vodctrl and tx\_vodctrl\_out are fixed to 3 bits

- tx\_preemp and tx\_preemp\_out are fixed to 5 bits

- rx\_eqdcgain and rx\_eqdcgain\_out are fixed to 2 bits

- rx\_eqctrl and rx\_eqctrl\_out are fixed to 4 bits

#### Write Transaction

To complete a write transaction, perform the following steps:

- Set the selected PMA control ports to the desired settings (for example, tx\_vodctrl = 3'b001).

- 2. Set the logical\_channel\_address input port to the logical channel address of the transceiver channel whose PMA controls you want to reconfigure.

- 3. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 4. Ensure that the busy signal is low before you start a write transaction.

- 5. Assert the write\_all signal for one reconfig\_clk clock cycle.

The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

# Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same Time

If you disable the **Use the same control signal for all the channels** option, the PMA control ports for a write transaction are separate for each channel. If you disable this option, the width of the PMA control ports are fixed as follows:

## **PMA Control Ports Used in a Write Transaction**

- tx\_vodctrl is 3 bits per channel

- tx\_preemp are 5 bits per channel

- rx\_eqdcgain is 2 bits per channel

- rx\_eqctrl is 4 bits per channel

For example, if you have two channels, the tx\_vodctrl is 6 bits wide (tx\_vodctrl [2:0] corresponds to channel 1 and tx\_vodctrl [5:3] corresponds to channel 2).

## **PMA Control Ports Used in a Read Transaction**

The width of the PMA control ports for a read transaction are always separate for each channel as explained in "Method 2: Writing the Same Control Signals to Control All the Transceiver Channels" on page 3–16.

## Write Transaction

Because the PMA controls of all the channels are written, if you want to reconfigure a specific channel connected to the ALTGX\_RECONFIG instance, set the new value at the corresponding PMA control port of the channel under consideration and retain the previously stored values in the other active channels with a read transaction prior to this write transaction.

For example, if the number of channels controlled by the ALTGX\_RECONFIG instance is two, the tx\_vodctrl signal in this case would be 6 bits wide. The tx\_vodctrl[2:0] signal corresponds to channel 1 and the tx\_vodctrl[5:3] signal corresponds to channel 2.

- To dynamically reconfigure the PMA controls of only channel 2 with a new value, first perform a read transaction to retrieve the existing PMA control values from tx\_vodctrl\_out[5:0]. Use the tx\_vodctrl\_out[2:0] value for tx\_vodctrl[2:0] to write in channel 1. By doing so, channel 1 is overwritten with the same value.

- Perform a write transaction. This ensures that the new values are written only to channel 2 while channel 1 remains unchanged.

3-19

If you are reconfiguring the multipurpose PLL with a different M counter value, follow these steps:

- 1. During transceiver PLL reconfiguration, assert tx\_digitalreset, rx\_digitalreset, and rx\_analogreset signals.

- 2. Perform PLL reconfiguration to update the multipurpose PLL with the PLL **.mif** files.

- 3. Perform channel reconfiguration and update the transceiver with the GXB reconfiguration **.mif** files. If you have multiple channel instantiations connected to the same multipurpose PLL, reconfigure each channel.

- 4. Deassert tx\_digitalreset and rx\_analogreset signals.

- 5. After the rx\_freqlocked signal goes high, wait for at least 4 µs, and then deassert the rx\_digitalreset signal.

# **Error Indication During Dynamic Reconfiguration**

The ALTGX\_RECONFIG MegaWizard Plug-In Manager provides an error status signal when you select the **Enable illegal mode checking** option or the **Enable self recovery** option in the **Error checks/data rate switch** screen. The conditions under which the error signal is asserted are:

- Enable illegal mode checking option—when you select this option, the dynamic reconfiguration controller checks whether an attempted operation falls under one of the conditions listed below. The dynamic reconfiguration controller detects these conditions within two reconfig\_clk cycles, deasserts the busy signal, and asserts the error signal for two reconfig\_clk cycles.

- PMA controls, read operation—none of the output ports (rx\_eqctrl\_out, rx\_eqdcgain\_out, tx\_vodctrl\_out, and tx\_preemp\_out) are selected in the ALTGX\_RECONFIG instance and the read signal is asserted.

- PMA controls, write operation—none of the input ports (rx\_eqctrl, rx\_eqdcgain, tx\_vodctrl, and tx\_preemp) are selected in the ALTGX\_RECONFIG instance and the write\_all signal is asserted.

- Channel reconfiguration and PMA reconfiguration mode select read operation option:

- The reconfig\_mode\_sel input port is set to 3'b001 (Channel reconfiguration mode)

- The read signal is asserted

- Enable self recovery option—when you select this option, the ALTGX\_RECONFIG MegaWizard Plug-In Manager provides the error output port. The dynamic reconfiguration controller quits an operation if it did not complete within the expected number of clock cycles. After recovering from the illegal operation, the dynamic reconfiguration controller deasserts the busy signal and asserts the error output port for two reconfig\_clk cycles.

- The error signal is not asserted when an illegal value is written to any of the PMA controls.

# I/O Timing

Use the following methods to determine I/O timing:

- the Excel-based I/O Timing

- the Quartus II timing analyzer

The Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get a timing budget estimation as part of the link timing analysis. The Quartus II timing analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after place-and-route is complete.

The Excel-based I/O Timing spreadsheet is downloadable from Cyclone IV Devices Literature website.

# Glossary

Table 1–46 lists the glossary for this chapter.

| Letter | Term                                                            | Definitions                                                                             |  |  |  |  |  |  |  |

|--------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Α      | —                                                               |                                                                                         |  |  |  |  |  |  |  |

| В      |                                                                 | _                                                                                       |  |  |  |  |  |  |  |

| C      | —                                                               | —                                                                                       |  |  |  |  |  |  |  |

| D      | —                                                               | —                                                                                       |  |  |  |  |  |  |  |

| E      | _                                                               | —                                                                                       |  |  |  |  |  |  |  |

| F      | f <sub>HSCLK</sub>                                              | High-speed I/O block: High-speed receiver/transmitter input and output clock frequency. |  |  |  |  |  |  |  |

| G      | GCLK                                                            | Input pin directly to Global Clock network.                                             |  |  |  |  |  |  |  |

| u      | GCLK PLL                                                        | Input pin to Global Clock network through the PLL.                                      |  |  |  |  |  |  |  |

| Н      | HSIODR                                                          | High-speed I/O block: Maximum/minimum LVDS data transfer rate (HSIODR = 1/TUI).         |  |  |  |  |  |  |  |

| I      | Input Waveforms<br>for the SSTL<br>Differential I/O<br>Standard | Vswing<br>Vswing<br>V <sub>IH</sub><br>V <sub>REF</sub>                                 |  |  |  |  |  |  |  |

| Table | 1-46. | Glossary | (Part 1 | of 5) |

|-------|-------|----------|---------|-------|

| IUNIO | 1 40. | aiossaiy | 1       | 0.0/  |

## Table 1-46. Glossary (Part 5 of 5)

| Letter | Term                    | Definitions                                                                                                                                                                                    |  |  |

|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | V <sub>CM(DC)</sub>     | DC common mode input voltage.                                                                                                                                                                  |  |  |

|        | V <sub>DIF(AC)</sub>    | AC differential input voltage: The minimum AC input differential voltage required for switching.                                                                                               |  |  |

|        | V <sub>DIF(DC)</sub>    | DC differential input voltage: The minimum DC input differential voltage required for switching.                                                                                               |  |  |

|        | V <sub>ICM</sub>        | Input common mode voltage: The common mode of the differential signal at the receiver.                                                                                                         |  |  |

|        | V <sub>ID</sub>         | Input differential voltage swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                  |  |  |

|        | V <sub>IH</sub>         | Voltage input high: The minimum positive voltage applied to the input that is accepted by the device as a logic high.                                                                          |  |  |

|        | V <sub>IH(AC)</sub>     | High-level AC input voltage.                                                                                                                                                                   |  |  |

|        | V <sub>IH(DC)</sub>     | High-level DC input voltage.                                                                                                                                                                   |  |  |

|        | V <sub>IL</sub>         | Voltage input low: The maximum positive voltage applied to the input that is accepted by the device as a logic low.                                                                            |  |  |

|        | V <sub>IL (AC)</sub>    | Low-level AC input voltage.                                                                                                                                                                    |  |  |

|        | V <sub>IL (DC)</sub>    | Low-level DC input voltage.                                                                                                                                                                    |  |  |

|        | V <sub>IN</sub>         | DC input voltage.                                                                                                                                                                              |  |  |

|        | V <sub>OCM</sub>        | Output common mode voltage: The common mode of the differential signal at the transmitter.                                                                                                     |  |  |

| V      | V <sub>OD</sub>         | Output differential voltage swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. $V_{OD} = V_{OH} - V_{OL}$ . |  |  |

|        | V <sub>OH</sub>         | Voltage output high: The maximum positive voltage from an output that the device considers is accepted as the minimum positive high level.                                                     |  |  |

|        | V <sub>OL</sub>         | Voltage output low: The maximum positive voltage from an output that the device considers is accepted as the maximum positive low level.                                                       |  |  |

|        | V <sub>os</sub>         | Output offset voltage: $V_{OS} = (V_{OH} + V_{OL}) / 2$ .                                                                                                                                      |  |  |

|        | V <sub>OX (AC)</sub>    | AC differential output cross point voltage: the voltage at which the differential output signals must cross.                                                                                   |  |  |

|        | V <sub>REF</sub>        | Reference voltage for the SSTL and HSTL I/O standards.                                                                                                                                         |  |  |

|        | V <sub>REF (AC)</sub>   | AC input reference voltage for the SSTL and HSTL I/O standards. $V_{REF(AC)} = V_{REF(DC)} + noise$ . The peak-to-peak AC noise on $V_{REF}$ must not exceed 2% of $V_{REF(DC)}$ .             |  |  |

|        | V <sub>REF (DC)</sub>   | DC input reference voltage for the SSTL and HSTL I/O standards.                                                                                                                                |  |  |

|        | V <sub>SWING (AC)</sub> | AC differential input voltage: AC input differential voltage required for switching. For the SSTL differential I/O standard, refer to Input Waveforms.                                         |  |  |

|        | V <sub>SWING (DC)</sub> | DC differential input voltage: DC input differential voltage required for switching. For the SSTL differential I/O standard, refer to Input Waveforms.                                         |  |  |

|        | V <sub>TT</sub>         | Termination voltage for the SSTL and HSTL I/O standards.                                                                                                                                       |  |  |

|        | V <sub>X (AC)</sub>     | AC differential input cross point voltage: The voltage at which the differential input signals must cross.                                                                                     |  |  |

| W      | _                       | _                                                                                                                                                                                              |  |  |

| X      | —                       | _                                                                                                                                                                                              |  |  |

| Y      | _                       | _                                                                                                                                                                                              |  |  |

| Z      | —                       | _                                                                                                                                                                                              |  |  |