Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 3491                                                     |

| Number of Logic Elements/Cells | 55856                                                    |

| Total RAM Bits                 | 2396160                                                  |

| Number of I/O                  | 324                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce55f23c8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **LAB Interconnects**

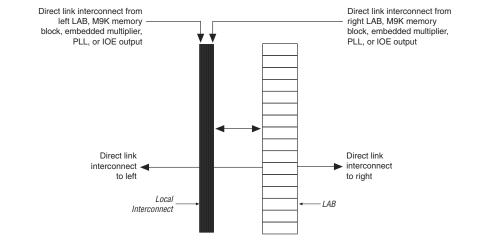

The LAB local interconnect is driven by column and row interconnects and LE outputs in the same LAB. Neighboring LABs, phase-locked loops (PLLs), M9K RAM blocks, and embedded multipliers from the left and right can also drive the local interconnect of a LAB through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive up to 48 LEs through fast local and direct link interconnects.

Figure 2–5 shows the direct link connection.

Figure 2–5. Cyclone IV Device Direct Link Connection

# **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include:

- Two clocks

- Two clock enables

- Two asynchronous clears

- One synchronous clear

- One synchronous load

You can use up to eight control signals at a time. Register packing and synchronous load cannot be used simultaneously.

Each LAB can have up to four non-global control signals. You can use additional LAB control signals as long as they are global signals.

Synchronous clear and load signals are useful for implementing counters and other functions. The synchronous clear and synchronous load signals are LAB-wide signals that affect all registers in the LAB.

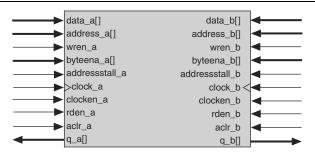

## **True Dual-Port Mode**

True dual-port mode supports any combination of two-port operations: two reads, two writes, or one read and one write, at two different clock frequencies. Figure 3–10 shows Cyclone IV devices true dual-port memory configuration.

Figure 3–10. Cyclone IV Devices True Dual-Port Memory (1)

#### Note to Figure 3-10:

- (1) True dual-port memory supports input or output clock mode in addition to the independent clock mode shown.

- The widest bit configuration of the M9K blocks in true dual-port mode is  $512 \times 16$ -bit (18-bit with parity).

Table 3–4 lists the possible M9K block mixed-port width configurations.

Table 3-4. Cyclone IV Devices M9K Block Mixed-Width Configurations (True Dual-Port Mode)

| Dood Doot |          | Write Port |          |          |          |          |          |  |  |  |  |  |  |  |

|-----------|----------|------------|----------|----------|----------|----------|----------|--|--|--|--|--|--|--|

| Read Port | 8192 × 1 | 4096 × 2   | 2048 × 4 | 1024 × 8 | 512 × 16 | 1024 × 9 | 512 × 18 |  |  |  |  |  |  |  |

| 8192 × 1  | V        | V          | V        | v v      | ,        | _        | _        |  |  |  |  |  |  |  |

| 4096 × 2  | V        | V          | V        | v v      |          | _        | _        |  |  |  |  |  |  |  |

| 2048 × 4  | V        | V          | V        | v v      |          | _        | _        |  |  |  |  |  |  |  |

| 1024 × 8  | V        | ٧          | V        | v v      |          | _        | _        |  |  |  |  |  |  |  |

| 512 × 16  | V        | V          | V        | v v      |          | _        | _        |  |  |  |  |  |  |  |

| 1024 × 9  | _        | _          | _        | _        | _        | V        | V        |  |  |  |  |  |  |  |

| 512 × 18  | _        | _          | _        | _        | _        | V        | V        |  |  |  |  |  |  |  |

In true dual-port mode, M9K memory blocks support separate wren and rden signals. You can save power by keeping the rden signal low (inactive) when not reading. Read-during-write operations to the same address can either output "New Data" at that location or "Old Data". To choose the desired behavior, set the **Read-During-Write** option to either **New Data** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about this behavior, refer to "Read-During-Write Operations" on page 3–15.

Table 5-10. Loop Filter Control of High Frequency Capacitor

| LFC[1] | LFC[0] | Setting (Decimal) |

|--------|--------|-------------------|

| 0      | 0      | 0                 |

| 0      | 1      | 1                 |

| 1      | 1      | 3                 |

## **Bypassing a PLL Counter**

Bypassing a PLL counter results in a divide (N, C0 to C4 counters) factor of one.

Table 5–11 lists the settings for bypassing the counters in PLLs of Cyclone IV devices.

Table 5-11. PLL Counter Settings

|   |     | PLL Sc | an Ch | ain Bit | Description |   |       |                      |                          |

|---|-----|--------|-------|---------|-------------|---|-------|----------------------|--------------------------|

|   | LSB |        |       |         |             |   | MSB   | Description          |                          |

| Χ | Χ   | Χ      | Χ     | Χ       | X X X       |   | 1 (1) | PLL counter bypassed |                          |

| Х | Χ   | Χ      | Χ     | Χ       | Χ           | Χ | Χ     | 0 (1)                | PLL counter not bypassed |

#### Note to Table 5-11:

(1) Bypass bit.

To bypass any of the PLL counters, set the bypass bit to 1. The values on the other bits are then ignored.

## **Dynamic Phase Shifting**

The dynamic phase shifting feature allows the output phase of individual PLL outputs to be dynamically adjusted relative to each other and the reference clock without sending serial data through the scan chain of the corresponding PLL. This feature simplifies the interface and allows you to quickly adjust  $t_{CO}$  delays by changing output clock phase shift in real time. This is achieved by incrementing or decrementing the VCO phase-tap selection to a given C counter or to the M counter. The phase is shifted by 1/8 the VCO frequency at a time. The output clocks are active during this phase reconfiguration process.

Table 5–12 lists the control signals that are used for dynamic phase shifting.

Table 5–12. Dynamic Phase Shifting Control Signals (Part 1 of 2)

| Signal Name            | Description                                                                                                                                                                                                            | Source                     | Destination                       |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|

| phasecounterselect[20] | Counter Select. Three bits decoded to select either the M or one of the C counters for phase adjustment. One address map to select all C counters. This signal is registered in the PLL on the rising edge of scanclk. | Logic array or I/O<br>pins | PLL<br>reconfiguration<br>circuit |

| phaseupdown            | Selects dynamic phase shift direction; 1= UP, 0 = DOWN. Signal is registered in the PLL on the rising edge of scanclk.                                                                                                 | Logic array or I/O pins    | PLL<br>reconfiguration<br>circuit |

| phasestep              | Logic high enables dynamic phase shifting.                                                                                                                                                                             | Logic array or I/O<br>pins | PLL<br>reconfiguration<br>circuit |

Each Cyclone IV I/O bank has a VREF bus to accommodate voltage-referenced I/O standards. Each VREF pin is the reference source for its  $V_{REF}$  group. If you use a  $V_{REF}$  group for voltage-referenced I/O standards, connect the VREF pin for that group to the appropriate voltage level. If you do not use all the V<sub>RFF</sub> groups in the I/O bank for voltage-referenced I/O standards, you can use the VREF pin in the unused voltage-referenced groups as regular I/O pins. For example, if you have SSTL-2 Class I input pins in I/O bank 1 and they are all placed in the VREFB1N[0] group, VREFB1N[0] must be powered with 1.25 V, and the remaining VREFB1N [1..3] pins (if available) are used as I/O pins. If multiple  $V_{REF}$  groups are used in the same I/O bank, the VREF pins must all be powered by the same voltage level because the VREF pins are shorted together within the same I/O bank.

- 1 When VREF pins are used as regular I/Os, they have higher pin capacitance than regular user I/O pins. This has an impact on the timing if the pins are used as inputs and outputs.

- f For more information about VREF pin capacitance, refer to the pin capacitance section in the Cyclone IV Device Datashedtapter.

- f For information about how to identify  $V_{RFF}$  groups, refer to the Cyclone IV **Device Pin-Out** files or the **Quartus II Pin Planner** tool.

Table 6–4 and Table 6–5 summarize the number of VREF pins in each I/O bank for the Cyclone IV device family.

Table 6–4. Number of VREF Pins Per I/O Bank for Cyclone IV E Devices (Part 1 of 2)

| Device             |          | EP4CE6   |          |          | EP4CE10 EP4CE22 EP4CE30 EP4CE40 |          |          |          | EP4CE15  |          |          |          | EP4CE55  |          |          | EP4CE75  |          | ED AP E11E | Er46E113 |          |          |          |          |          |          |          |          |          |          |          |

|--------------------|----------|----------|----------|----------|---------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| I/O<br>Bank<br>(1) | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 256-UBGA                        | 256-FBGA | 144-EQPF | 164-MBGA | 256-MBGA | 256-UBGA | 256-FBGA | 484-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 324-FBGA | 484-FBGA | 780-FBGA   | 324-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-FBGA | 780-FBGA |

| 1                  | 1        | 1        | 1        | 1        | 1                               | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4          | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 2                  | 1        | 1        | 1        | 1        | 1                               | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4          | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 3                  | 1        | 1        | 1        | 1        | 1                               | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4          | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 4                  | 1        | 1        | 1        | 1        | 1                               | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4          | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 5                  | 1        | 1        | 1        | 1        | 1                               | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4          | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 6                  | 1        | 1        | 1        | 1        | 1                               | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4          | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

| 7                  | 1        | 1        | 1        | 1        | 1                               | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4          | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

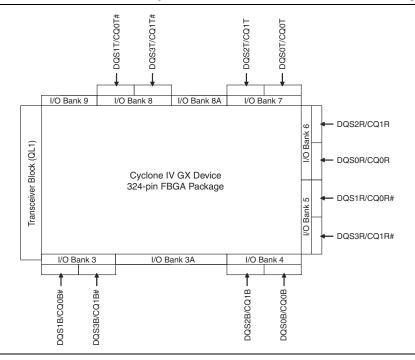

Figure 7–3 shows the location and numbering of the DQS, DQ, or CQ# pins in I/O banks of the Cyclone IV GX device in the 324-pin FBGA package only.

Figure 7-3. DQS, CQ, or CQ# Pins for Cyclone IV GX Devices in the 324-Pin FBGA Package

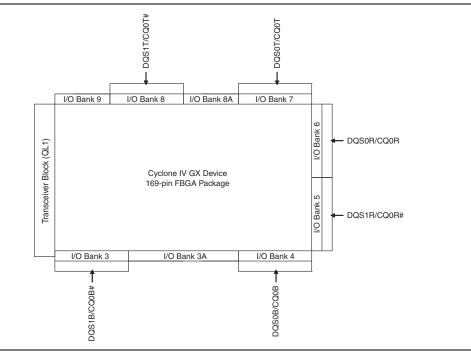

Figure 7–4 shows the location and numbering of the DQS, DQ, or CQ# pins in I/O banks of the Cyclone IV GX device in the 169-pin FBGA package.

Figure 7-4. DQS, CQ, or CQ# Pins for Cyclone IV GX Devices in the 169-Pin FBGA Package

In Cyclone IV devices, the DM pins are preassigned in the device pinouts. The Quartus II Fitter treats the DQ and DM pins in a DQS group equally for placement purposes. The preassigned DQ and DM pins are the preferred pins to use.

Some DDR2 SDRAM and DDR SDRAM devices support error correction coding (ECC), a method of detecting and automatically correcting errors in data transmission. In 72-bit DDR2 or DDR SDRAM, there are eight ECC pins and 64 data pins. Connect the DDR2 and DDR SDRAM ECC pins to a separate DQS or DQ group in Cyclone IV devices. The memory controller needs additional logic to encode and decode the ECC data.

# **Address and Control/Command Pins**

The address signals and the control or command signals are typically sent at a single data rate. You can use any of the user I/O pins on all I/O banks of Cyclone IV devices to generate the address and control or command signals to the memory device.

1 Cyclone IV devices do not support QDR II SRAM in the burst length of two.

# **Memory Clock Pins**

In DDR2 and DDR SDRAM memory interfaces, the memory clock signals (CK and CK#) are used to capture the address signals and the control or command signals. Similarly, QDR II SRAM devices use the write clocks (K and K#) to capture the address and command signals. The CK/CK# and K/K# signals are generated to resemble the write-data strobe using the DDIO registers in Cyclone IV devices.

- 1 CK/CK# pins must be placed on differential I/O pins (DIFFIO in Pin Planner) and in the same bank or on the same side as the data pins. You can use either side of the device for wraparound interfaces. As seen in the Pin Planner Pad View, CKO cannot be located in the same row and column pad group as any of the interfacing DQ pins.

- For more information about memory clock pin placement, refer to Volume 2: Device, Pin, and Board Layout Guidelines the External Memory Interface Handbook.

# **Cyclone IV Devices Memory Interfaces Features**

This section discusses Cyclone IV memory interfaces, including DDR input registers, DDR output registers, OCT, and phase-lock loops (PLLs).

# **DDR Input Registers**

The DDR input registers are implemented with three internal logic element (LE) registers for every DQ pin. These LE registers are located in the logic array block (LAB) adjacent to the DDR input pin.

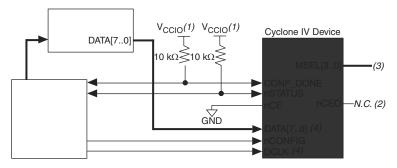

the device, must be stored in the external host device. Figure 8–19 shows the configuration interface connections between the Cyclone IV devices and an external device for single-device configuration.

Figure 8–19. Single-Device FPP Configuration Using an External Host

#### Notes to Figure 8-19:

- (1) Connect the pull-up resistor to a supply that provides an acceptable input signal for the device. V<sub>CC</sub> must be high enough to meet the V<sub>IH</sub> specification of the I/O on the device and the external host.

- (2) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–4 on page 8–8 and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [7..0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

After nSTATUS is released, the device is ready to receive configuration data and the configuration stage begins. When nSTATUS is pulled high, the external host device places the configuration data one byte at a time on the DATA[7..0] pins.

Cyclone IV devices receive configuration data on the DATA [7..0] pins and the clock is received on the DCLK pin. Data is latched into the device on the rising edge of DCLK. Data is continuously clocked into the target device until CONF\_DONE goes high. The CONF\_DONE pin goes high one byte early in FPP configuration mode. The last byte is required for serial configuration (AS and PS) modes.

1 Two DCLK falling edges are required after CONF\_DONE goes high to begin initialization of the device.

Supplying a clock on CLKUSR does not affect the configuration process. After the CONF\_DONE pin goes high, CLKUSR is enabled after the time specified as  $t_{CD2CU}$ . After this time period elapses, Cyclone IV devices require 3,192 clock cycles to initialize properly and enter user mode. For more information about the supported CLKUSR  $t_{MAX}$  value for Cyclone IV devices, refer to Table 8–13 on page 8–44.

The INIT\_DONE pin is released and pulled high when initialization is complete. The external host device must be able to detect this low-to-high transition, which signals the device has entered user mode. When initialization is complete, the device enters user mode. In user mode, the user I/O pins no longer have weak pull-up resistors and function as assigned in your design.

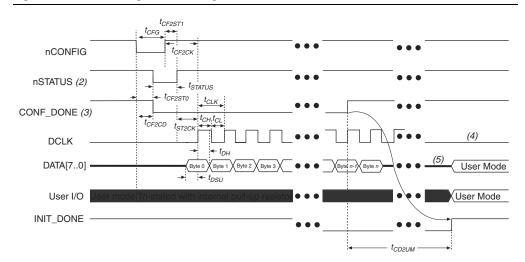

# **FPP Configuration Timing**

Figure 8–22 shows the timing waveform for the FPP configuration when using an external host.

Figure 8–22. FPP Configuration Timing Waveform (1)

#### Notes to Figure 8-22:

- (1) The beginning of this waveform shows the device in user mode. In user mode, nconfig, nstatus, and conf\_done are at logic-high levels. When nconfig is pulled low, a reconfiguration cycle begins.

- (2) After power up, the Cyclone IV device holds nSTATUS low during POR delay.

- (3) After power up, before and during configuration, CONF DONE is low.

- (4) Do not leave DCLK floating after configuration. It must be driven high or low, whichever is more convenient.

- (5) DATA [7..0] is available as a user I/O pin after configuration; the state of the pin depends on the dual-purpose pin settings.

Table 8–13 lists the FPP configuration timing parameters for Cyclone IV devices.

Table 8-13. FPP Timing Parameters for Cyclone IV Devices (Part 1 of 2)

| Cumbal              | Parameter                                       | Minir          | num              | Maxin          | num              | Unit  |  |

|---------------------|-------------------------------------------------|----------------|------------------|----------------|------------------|-------|--|

| Symbol              | Parameter                                       | Cyclone IV (1) | Cyclone IV E (2) | Cyclone IV (1) | Cyclone IV E (2) | UIIIL |  |

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low                    |                | -                | 50             | ns               |       |  |

| t <sub>CF2ST0</sub> | nCONFIG low to                                  |                | -                | 50             | ns               |       |  |

| t <sub>CFG</sub>    | nCONFIG low pulse width                         | 50             | 0                | _              | ns               |       |  |

| t <sub>STATUS</sub> | nSTATUS low pulse width                         | 45             | 5                | 230            | μs               |       |  |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high                    | _              | -                | 230            | (4)              | μs    |  |

| t <sub>CF2CK</sub>  | nCONFIG high to<br>first rising edge on<br>DCLK | 230            | 230 (3)          |                |                  |       |  |

■ In AP configuration scheme, the only way to re-engage the AP controller is to issue the ACTIVE\_ENGAGE instruction. In this case, asserting the nCONFIG pin does not reengage either active controller.

#### **ACTIVE ENGAGE**

The ACTIVE\_ENGAGE instruction allows you to re-engage a disengaged active controller. You can issue this instruction any time during configuration or user mode to reengage an already disengaged active controller, as well as trigger reconfiguration of the Cyclone IV device in the active configuration scheme.

The ACTIVE\_ENGAGE instruction functions as the PULSE\_NCONFIG instruction when the device is in the PS or FPP configuration schemes. The nconfig pin is disabled when the ACTIVE ENGAGE instruction is issued.

Altera does not recommend using the ACTIVE\_ENGAGE instruction, but it is provided as a fail-safe instruction for re-engaging the active configuration controller (AS and AP).

### **Overriding the Internal Oscillator**

This feature allows you to override the internal oscillator during the active configuration scheme. The AS and AP configuration controllers use the internal oscillator as the clock source. You can change the clock source to CLKUSR through the JTAG instruction.

The EN\_ACTIVE\_CLK and DIS\_ACTIVE\_CLK JTAG instructions toggle on or off whether or not the active clock is sourced from the CLKUSR pin or the internal configuration oscillator. To source the active clock from the CLKUSR pin, issue the EN\_ACTIVE\_CLK instruction. This causes the CLKUSR pin to become the active clock source. When using the EN\_ACTIVE\_CLK instruction, you must enable the internal oscillator for the clock change to occur. By default, the configuration oscillator is disabled after configuration and initialization is complete as well as the device has entered user mode.

However, the internal oscillator is enabled in user mode by any of the following conditions:

- A reconfiguration event (for example, driving the nCONFIG pin to go low)

- Remote update is enabled

- Error detection is enabled

- When using the EN\_ACTIVE\_CLK and DIS\_ACTIVE\_CLK JTAG instructions to override the internal oscillator, you must clock the CLKUSR pin at two times the expected DCLK frequency. The CLKUSR pin allows a maximum frequency of 40 MHz (40 MHz DCLK).

Normally, a test instrument uses the CLKUSR pin when it wants to drive its own clock to control the AS state machine.

To revert the clock source back to the configuration oscillator, issue the DIS\_ACTIVE\_CLK instruction. After you issue the DIS\_ACTIVE\_CLK instruction, you must continue to clock the CLKUSR pin for 10 clock cycles. Otherwise, even toggling the nCONFIG pin does not revert the clock source and reconfiguration does not occur. A POR reverts the clock source back to the configuration oscillator. Toggling the nCONFIG pin or driving the JTAG state machine to reset state does not revert the clock source.

Table 8–19. Configuration Pin Summary for Cyclone IV E Devices (Part 2 of 3)

| Bank | Description          | Input/Output  | Dedicated | Powered By         | Configuration Mode  |  |  |

|------|----------------------|---------------|-----------|--------------------|---------------------|--|--|

| 1    | DATA[0] (1), (2)     | Input         |           | V <sub>CCIO</sub>  | PS, FPP, AS         |  |  |

| '    | DATA[0] (7), (2)     | Bidirectional | ] — [     | V <sub>CCIO</sub>  | AP                  |  |  |

|      |                      | Input         |           | V <sub>CCIO</sub>  | FPP                 |  |  |

| 1    | DATA[1] (2)/ASDO (1) | Output        | ] — [     | V <sub>CCIO</sub>  | AS                  |  |  |

|      |                      | Bidirectional |           | V <sub>CCIO</sub>  | AP                  |  |  |

| 8    | DATA[72] (2)         | Input         |           | V <sub>CCIO</sub>  | FPP                 |  |  |

| 0    | DATA[/2]             | Bidirectional | ] —       | V <sub>CCIO</sub>  | AP                  |  |  |

| 8    | DATA[158] (2)        | Bidirectional | _         | V <sub>CCIO</sub>  | AP                  |  |  |

| 6    | INIT_DONE            | Output        | _         | Pull-up            | Optional, all modes |  |  |

| 1    | nSTATUS              | Bidirectional | Yes       | Pull-up            | All modes           |  |  |

| 1    | nCE                  | Input         | Yes       | V <sub>CCIO</sub>  | All modes           |  |  |

| 1    | DCLK (1), (2)        | Input         | Yes       | V <sub>CCIO</sub>  | PS, FPP             |  |  |

| '    | DCLK (17), (=)       | Output        | _         | V <sub>CCIO</sub>  | AS, AP              |  |  |

| 6    | CONF_DONE            | Bidirectional | Yes       | Pull-up            | All modes           |  |  |

| 1    | TDI                  | Input         | Yes       | V <sub>CCIO</sub>  | JTAG                |  |  |

| 1    | TMS                  | Input         | Yes       | V <sub>CCIO</sub>  | JTAG                |  |  |

| 1    | TCK                  | Input         | Yes       | V <sub>CCIO</sub>  | JTAG                |  |  |

| 1    | nCONFIG              | Input         | Yes       | V <sub>CCIO</sub>  | All modes           |  |  |

| 6    | CLKUSR               | Input         | _         | V <sub>CCIO</sub>  | Optional            |  |  |

| 6    | nCEO                 | Output        | _         | V <sub>CCIO</sub>  | Optional, all modes |  |  |

| 6    | MSEL[]               | Input         | Yes       | V <sub>CCINT</sub> | All modes           |  |  |

| 1    | TDO                  | Output        | Yes       | V <sub>CCIO</sub>  | JTAG                |  |  |

| 7    | PADD[140]            | Output        | _         | V <sub>CCIO</sub>  | AP                  |  |  |

| 8    | PADD[1915]           | Output        | _         | V <sub>CCIO</sub>  | AP                  |  |  |

| 6    | PADD[2320]           | Output        | _         | V <sub>CCIO</sub>  | AP                  |  |  |

| 1    | nRESET               | Output        | _         | V <sub>CCIO</sub>  | AP                  |  |  |

| 6    | nAVD                 | Output        | _         | V <sub>CCIO</sub>  | AP                  |  |  |

| 6    | nOE                  | Output        | _         | V <sub>CCIO</sub>  | AP                  |  |  |

| 6    | nWE                  | Output        | _         | V <sub>CCIO</sub>  | AP                  |  |  |

| 5    | DEV_OE               | Input         | _         | V <sub>CCIO</sub>  | Optional, AP        |  |  |

Table 8-28. Document Revision History (Part 2 of 2)

| Date                                    | Version | Changes                                                                                                                                                                                                       |

|-----------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         |         | Updated for the Quartus II software 10.0 release:                                                                                                                                                             |

| July 2010                               | 1.2     | ■ Updated "Power-On Reset (POR) Circuit", "Configuration and JTAG Pin I/O Requirements", and "Reset" sections.                                                                                                |

|                                         |         | ■ Updated Figure 8–10.                                                                                                                                                                                        |

|                                         |         | ■ Updated Table 8–16 and Table 8–17.                                                                                                                                                                          |

|                                         |         | Updated for the Quartus II software 9.1 SP1 release:                                                                                                                                                          |

|                                         |         | Added "Overriding the Internal Oscillator" and "AP Configuration (Supported Flash<br>Memories)" sections.                                                                                                     |

|                                         |         | ■ Updated "JTAG Instructions" section.                                                                                                                                                                        |

| February 2010                           | 1.1     | ■ Added Table 8–6.                                                                                                                                                                                            |

| , , , , , , , , , , , , , , , , , , , , |         | ■ Updated Table 8–2, Table 8–3, Table 8–4, Table 8–6, Table 8–11, Table 8–13, Table 8–14, Table 8–15, and Table 8–18.                                                                                         |

|                                         |         | ■ Updated Figure 8–4, Figure 8–5, Figure 8–6, Figure 8–13, Figure 8–14, Figure 8–15, Figure 8–17, Figure 8–18, Figure 8–23, Figure 8–24, Figure 8–25, Figure 8–26, Figure 8–27, Figure 8–28, and Figure 8–29. |

| November 2009                           | 1.0     | Initial release.                                                                                                                                                                                              |

May 2013 Altera Corporation

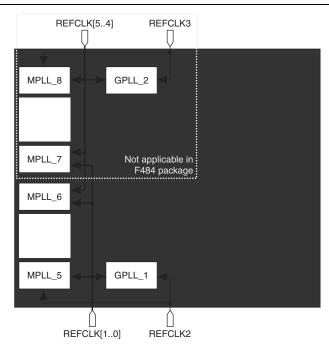

Figure 1–26. PLL Input Reference Clocks in Transceiver Operation for F484 and Larger Packages  $^{(1)}$ ,  $^{(2)}$ ,  $^{(3)}$

#### Notes to Figure 1-26:

- (1) The REFCLK2 and REFCLK3 pins are dual-purpose CLKIO, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A respectively.

- (2) The REFCLK [1..0] and REFCLK [5..4] pins are dual-purpose differential REFCLK or DIFFCLK pins that reside in banks 3B and 8B respectively. These clock input pins do not have access to the clock control blocks and GCLK networks. For more details, refer to the Clock Networks and PLLs in Cyclone IV Devices chapter.

- (3) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs and GPLLs may have reduced jitter performance.

The input reference clocks reside in banks 3A, 3B, 8A, and 8B have dedicated  $V_{CC\_CLKIN3A}$ ,  $V_{CC\_CLKIN3B}$ ,  $V_{CC\_CLKIN8A}$ , and  $V_{CC\_CLKIN8B}$  power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for general purpose I/Os (GPIOs). Table 1–6 lists the supported I/O standard for the REFCLK pins.

Table 1–6. REFCLK I/O Standard Support

|                             | HSSI     |                         | Terminatio | VCC_  | CLKIN Level   | I/O Pin Type |         |                    |  |  |

|-----------------------------|----------|-------------------------|------------|-------|---------------|--------------|---------|--------------------|--|--|

| I/O Standard                | Protocol | Coupling                | n          | Input | Output        | Column I/O   | Row I/O | Supported<br>Banks |  |  |

| LVDS                        | ALL      | Differential            | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| LVPECL                      | ALL      | AC (Needs               | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| 404454                      | ALL      | off-chip<br>resistor to | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| 1.2 V, 1.5 V,<br>3.3 V PCML | ALL      | restore                 | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| 0.0 1 1 02                  | ALL      | V <sub>CM</sub> )       | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| HCSL                        | PCle     | Differential<br>DC      | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

Table 1–9 lists the high- and low-speed clock sources for each channel.

Table 1-9. High- and Low-Speed Clock Sources for Each Channel in Non-Bonded Channel Configuration

| Dookowa          | Transaciver Black | Transcius Channel   | High- and Low-Speed Clocks Sources |                   |  |  |  |

|------------------|-------------------|---------------------|------------------------------------|-------------------|--|--|--|

| Package          | Transceiver Block | Transceiver Channel | Option 1                           | Option 2          |  |  |  |

| F324 and smaller | GXBL0             | All channels        | MPLL_1                             | MPLL_2            |  |  |  |

|                  | CVDIA             | Channels 0, 1       | MPLL_5/GPLL_1                      | MPLL_6            |  |  |  |

| F484 and larger  | GXBL0             | Channels 2, 3       | MPLL_5                             | MPLL_6/MPLL_7 (1) |  |  |  |

| r404 aliu laiyel | GXBL1 (1)         | Channels 0, 1       | MPLL_7/MPLL_6                      | MPLL_8            |  |  |  |

|                  | GVDIT (.)         | Channels 2, 3       | MPLL_7                             | MPLL_8/GPLL_2     |  |  |  |

#### Note to Table 1-9:

<sup>(1)</sup>  ${\tt MPLL\_7}$  and  ${\tt GXBL1}$  are not applicable for transceivers in F484 package

Table 1–13. Automatic RX Phase Compensation FIFO Read Clock Selection (Part 2 of 2)

| Chan    | nel Configuration        | Quartus II Selection                                                                                                                                                                                        |

|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bonded  | With rate match FIFO (1) | coreclkout clock feeds the FIFO read clock for the bonded channels. coreclkout clock is the common bonded low-speed clock, which also feeds the FIFO read clock and transmitter PCS in the bonded channels. |

| Bollued | Without rate match FIFO  | rx_clkout clock feeds the FIFO read clock. rx_clkout is forwarded through the receiver channel from low-speed recovered clock, which also feeds the FIFO write clock.                                       |

#### Note to Table 1-13:

(1) Configuration with rate match FIFO is supported in transmitter and receiver operation.

When using user-specified clock option, ensure that the clock feeding rx\_coreclk port has 0 ppm difference with the RX phase compensation FIFO write clock.

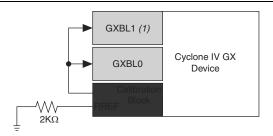

# **Calibration Block**

This block calibrates the OCT resistors and the analog portions of the transceiver blocks to ensure that the functionality is independent of process, voltage, and temperature (PVT) variations.

Figure 1–40 shows the location of the calibration block and how it is connected to the transceiver blocks.

Figure 1-40. Transceiver Calibration Blocks Location and Connection

#### Note to Figure 1-40:

(1) Transceiver block GXBL1 is only available for devices in F484 and larger packages.

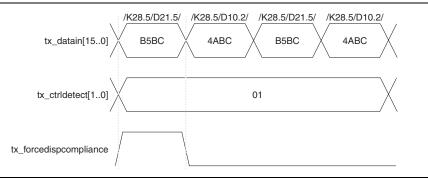

four code groups: /K28.5/;

The compliance pattern is a repeating sequence of the four code groups: /K28.5/; /D21.5/; /K28.5/; /D10.2/. Figure 1–53 shows the compliance pattern transmission where the tx\_forcedispcompliance port must be asserted in the same parallel clock cycle as /K28.5/D21.5/ of the compliance pattern on tx\_datain[15..0] port.

Figure 1–53. Compliance Pattern Transmission Support in PCI Express (PIPE) Mode

### **Reset Requirement**

Cyclone IV GX devices meets the PCIe reset time requirement from device power up to the link active state with the configuration schemes listed in Table 1–17.

Table 1–18. Electrical Idle Inference Conditions

| Device       | Configuration Scheme        | Configuration Time (ms) |

|--------------|-----------------------------|-------------------------|

| EP4CGX15     | Passive serial (PS)         | 51                      |

| EP4CGX22     | PS                          | 92                      |

| EP4CGX30 (1) | PS                          | 92                      |

| EP4CGX50     | Fast passive parallel (FPP) | 41                      |

| EP4CGX75     | FPP                         | 41                      |

| EP4CGX110    | FPP                         | 70                      |

| EP4CGX150    | FPP                         | 70                      |

#### Note to Table 1-18:

## **GIGE Mode**

GIGE mode provides the transceiver channel datapath configuration for GbE (specifically the 1000 Base-X physical layer device (PHY) standard) protocol implementation. The Cyclone IV GX transceiver provides the PMA and the following PCS functions as defined in the IEEE 802.3 specification for 1000 Base-X PHY:

- 8B/10B encoding and decoding

- synchronization

If you enabled the auto-negotiation state machine in the FPGA core with the rate match FIFO, refer to "Clock Frequency Compensation" on page 1–63.

<sup>(1)</sup> EP4CGX30 device in F484 package fulfills the PCIe reset time requirement using FPP configuration scheme with configuration time of 41 ms.

There are three methods that you can use to dynamically reconfigure the PMA controls of a transceiver channel:

- "Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels" on page 3–14

- "Method 2: Writing the Same Control Signals to Control All the Transceiver Channels" on page 3–16

- "Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same Time" on page 3–19

# Method 1: Using logical\_channel\_address to Reconfigure Specific Transceiver Channels

Enable the <code>logical\_channel\_address</code> port by selecting the <code>Use</code> 'logical\_channel\_address' port option on the <code>Analog</code> controls tab. This method is applicable only for a design where the dynamic reconfiguration controller controls more than one channel.

You can additionally reconfigure either the receiver portion, transmitter portion, or both the receiver and transmitter portions of the transceiver channel by setting the corresponding value on the rx\_tx\_duplex\_sel input port. For more information, refer to Table 3–2 on page 3–4.

#### **Connecting the PMA Control Ports**

The selected PMA control ports remain fixed in width, regardless of the number of channels controlled by the ALTGX\_RECONFIG instance:

- tx\_vodctrl and tx\_vodctrl\_out are fixed to 3 bits

- tx\_preemp and tx\_preemp\_out are fixed to 5 bits

- rx\_eqdcgain and rx\_eqdcgain\_out are fixed to 2 bits

- rx\_eqctrl and rx\_eqctrl\_out are fixed to 4 bits

#### **Write Transaction**

To complete a write transaction, perform the following steps:

- 1. Set the selected PMA control ports to the desired settings (for example, tx vodctrl = 3'b001).

- 2. Set the logical\_channel\_address input port to the logical channel address of the transceiver channel whose PMA controls you want to reconfigure.

- 3. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 4. Ensure that the busy signal is low before you start a write transaction.

- 5. Assert the write\_all signal for one reconfig\_clk clock cycle.

The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

# Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same Time

If you disable the **Use the same control signal for all the channels** option, the PMA control ports for a write transaction are separate for each channel. If you disable this option, the width of the PMA control ports are fixed as follows:

#### **PMA Control Ports Used in a Write Transaction**

- tx\_vodctrl is 3 bits per channel

- tx\_preemp are 5 bits per channel

- rx\_eqdcgain is 2 bits per channel

- rx eqctrl is 4 bits per channel

For example, if you have two channels, the tx\_vodctrl is 6 bits wide (tx\_vodctrl [2:0] corresponds to channel 1 and tx\_vodctrl [5:3] corresponds to channel 2).

#### **PMA Control Ports Used in a Read Transaction**

The width of the PMA control ports for a read transaction are always separate for each channel as explained in "Method 2: Writing the Same Control Signals to Control All the Transceiver Channels" on page 3–16.

#### **Write Transaction**

Because the PMA controls of all the channels are written, if you want to reconfigure a specific channel connected to the ALTGX\_RECONFIG instance, set the new value at the corresponding PMA control port of the channel under consideration and retain the previously stored values in the other active channels with a read transaction prior to this write transaction.

For example, if the number of channels controlled by the ALTGX\_RECONFIG instance is two, the tx\_vodctrl signal in this case would be 6 bits wide. The tx\_vodctrl[2:0] signal corresponds to channel 1 and the tx\_vodctrl[5:3] signal corresponds to channel 2.

- To dynamically reconfigure the PMA controls of only channel 2 with a new value, first perform a read transaction to retrieve the existing PMA control values from tx\_vodctrl\_out[5:0]. Use the tx\_vodctrl\_out[2:0] value for tx\_vodctrl[2:0] to write in channel 1. By doing so, channel 1 is overwritten with the same value.

- Perform a write transaction. This ensures that the new values are written only to channel 2 while channel 1 remains unchanged.

# **Functional Simulation of the Dynamic Reconfiguration Process**

This section describes the points to be considered during functional simulation of the dynamic reconfiguration process.

- You must connect the ALTGX\_RECONFIG instance to the ALTGX\_instance/ALTGX instances in your design for functional simulation.

- The functional simulation uses a reduced timing model of the dynamic reconfiguration controller. The duration of the offset cancellation process is 16 reconfig\_clk clock cycles for functional simulation only.

- The gxb\_powerdown signal must not be asserted during the offset cancellation sequence (for functional simulation and silicon).

# **Document Revision History**

Table 3–8 lists the revision history for this chapter.

Table 3–8. Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2011 | 2.1     | ■ Updated "Dynamic Reconfiguration Controller Architecture", "PMA Controls Reconfiguration Mode", "PLL Reconfiguration Mode", and "Error Indication During Dynamic Reconfiguration" sections.                                                                    |

|               |         | ■ Updated Table 3–2 and Table 3–4.                                                                                                                                                                                                                               |

|               |         | ■ Updated for the Quartus II software version 10.1 release.                                                                                                                                                                                                      |

|               |         | ■ Updated Table 3–1, Table 3–2, Table 3–3, Table 3–4, Table 3–5, and Table 3–6.                                                                                                                                                                                  |

|               |         | ■ Added Table 3–7.                                                                                                                                                                                                                                               |

| December 2010 | 2.0     | ■ Updated Figure 3–1, Figure 3–11, Figure 3–13, and Figure 3–14.                                                                                                                                                                                                 |

| 2010          |         | ■ Updated "Offset Cancellation Feature", "Error Indication During Dynamic Reconfiguration", "Data Rate Reconfiguration Mode Using RX Local Divider", "PMA Controls Reconfiguration Mode", and "Control and Status Signals for Channel Reconfiguration" sections. |

| July 2010     | 1.0     | Initial release.                                                                                                                                                                                                                                                 |

### **DC** Characteristics

This section lists the I/O leakage current, pin capacitance, on-chip termination (OCT) tolerance, and bus hold specifications for Cyclone IV devices.

# **Supply Current**

The device supply current requirement is the minimum current drawn from the power supply pins that can be used as a reference for power size planning. Use the Excel-based early power estimator (EPE) to get the supply current estimates for your design because these currents vary greatly with the resources used. Table 1–6 lists the I/O pin leakage current for Cyclone IV devices.

Table 1-6. I/O Pin Leakage Current for Cyclone IV Devices (1), (2)

| Symbol          | Parameter                         | Conditions                                 | Device | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|--------------------------------------------|--------|-----|-----|-----|------|

| I <sub>I</sub>  | Input pin leakage current         | $V_I = 0 V \text{ to } V_{CCIOMAX}$        |        | -10 | _   | 10  | μΑ   |

| I <sub>OZ</sub> | Tristated I/O pin leakage current | $V_0 = 0 \text{ V to } V_{\text{CCIOMAX}}$ |        | -10 | _   | 10  | μΑ   |

#### Notes to Table 1-6:

- This value is specified for normal device operation. The value varies during device power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 3.0, 2.5, 1.8, 1.5, and 1.2 V).

- (2) The 10  $\mu$ A I/O leakage current limit is applicable when the internal clamping diode is off. A higher current can be observed when the diode is on.

#### **Bus Hold**

The bus hold retains the last valid logic state after the source driving it either enters the high impedance state or is removed. Each I/O pin has an option to enable bus hold in user mode. Bus hold is always disabled in configuration mode.

Table 1–7 lists bus hold specifications for Cyclone IV devices.

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 1 of 2) (1)

|                                            |                                                | V <sub>CCIO</sub> (V) |      |     |      |     |      |     |      |     |      |     |      |      |

|--------------------------------------------|------------------------------------------------|-----------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                  | Condition                                      | 1.2                   |      | 1.5 |      | 1.8 |      | 2.5 |      | 3.0 |      | 3.3 |      | Unit |

|                                            |                                                | Min                   | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus hold<br>low,<br>sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 8                     | _    | 12  | _    | 30  | _    | 50  | _    | 70  | _    | 70  | _    | μА   |

| Bus hold<br>high,<br>sustaining<br>current | V <sub>IN</sub> < V <sub>IL</sub><br>(minimum) | -8                    | _    | -12 | _    | -30 | _    | -50 | _    | -70 | _    | -70 | _    | μА   |

| Bus hold<br>low,<br>overdrive<br>current   | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _                     | 125  | _   | 175  | _   | 200  | _   | 300  | _   | 500  | _   | 500  | μА   |

| Bus hold<br>high,<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _                     | -125 | _   | -175 | —   | -200 | _   | -300 | —   | -500 | —   | -500 | μА   |

For more information about receiver input and transmitter output waveforms, and for other differential I/O standards, refer to the I/O Features in Cyclone IV Devices chapter.

Table 1–18. Differential SSTL I/O Standard Specifications for Cyclone IV Devices (1)

| I/O Standard           | V <sub>CCIO</sub> (V) |     |       | V <sub>Swing</sub> | <sub>I(DC)</sub> (V) | V <sub>x(</sub> ,            | V <sub>Swir</sub> | ng(AC)<br><b>/)</b>             | V <sub>OX(AC)</sub> (V) |                  |                                 |     |                                 |

|------------------------|-----------------------|-----|-------|--------------------|----------------------|------------------------------|-------------------|---------------------------------|-------------------------|------------------|---------------------------------|-----|---------------------------------|

|                        | Min                   | Тур | Max   | Min                | Max                  | Min                          | Тур               | Max                             | Min                     | Max              | Min                             | Тур | Max                             |

| SSTL-2<br>Class I, II  | 2.375                 | 2.5 | 2.625 | 0.36               | V <sub>CCIO</sub>    | V <sub>CCIO</sub> /2 - 0.2   | _                 | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.7                     | V <sub>CCI</sub> | V <sub>CCIO</sub> /2 -<br>0.125 | _   | V <sub>CCIO</sub> /2<br>+ 0.125 |

| SSTL-18<br>Class I, II | 1.7                   | 1.8 | 1.90  | 0.25               | V <sub>CCIO</sub>    | V <sub>CCIO</sub> /2 - 0.175 | _                 | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                     | V <sub>CCI</sub> | V <sub>CCIO</sub> /2 - 0.125    | _   | V <sub>CCIO</sub> /2<br>+ 0.125 |

#### Note to Table 1-18:

Table 1–19. Differential HSTL I/O Standard Specifications for Cyclone IV Devices (1)

| I/O Standard           | V <sub>CCIO</sub> (V) |     |       | V <sub>DIF(DC)</sub> (V) |                   | V <sub>X(AC)</sub> (V)   |     |                             | V <sub>CM(DC)</sub> (V)     |     |                             |         | V <sub>DIF(AC)</sub> (V)    |  |  |

|------------------------|-----------------------|-----|-------|--------------------------|-------------------|--------------------------|-----|-----------------------------|-----------------------------|-----|-----------------------------|---------|-----------------------------|--|--|

|                        | Min                   | Тур | Max   | Min                      | Мах               | Min                      | Тур | Max                         | Min                         | Тур | Max                         | Mi<br>n | Max                         |  |  |

| HSTL-18<br>Class I, II | 1.71                  | 1.8 | 1.89  | 0.2                      | _                 | 0.85                     |     | 0.95                        | 0.85                        | _   | 0.95                        | 0.4     | _                           |  |  |

| HSTL-15<br>Class I, II | 1.425                 | 1.5 | 1.575 | 0.2                      | _                 | 0.71                     |     | 0.79                        | 0.71                        | _   | 0.79                        | 0.4     | _                           |  |  |

| HSTL-12<br>Class I, II | 1.14                  | 1.2 | 1.26  | 0.16                     | V <sub>CCIO</sub> | 0.48 x V <sub>CCIO</sub> |     | 0.52 x<br>V <sub>CCIO</sub> | 0.48 x<br>V <sub>CCIO</sub> | _   | 0.52 x<br>V <sub>CCIO</sub> | 0.3     | 0.48 x<br>V <sub>CCIO</sub> |  |  |

#### Note to Table 1-19:

Table 1–20. Differential I/O Standard Specifications for Cyclone IV Devices (1) (Part 1 of 2)

| I/O Standard                              | V <sub>CCIO</sub> (V) |     |       | V <sub>ID</sub> (mV) |         |      | V <sub>OD</sub> (mV) <sup>(3)</sup>                                                                |      |     | V <sub>0S</sub> (V) <sup>(3)</sup> |     |       |      |       |

|-------------------------------------------|-----------------------|-----|-------|----------------------|---------|------|----------------------------------------------------------------------------------------------------|------|-----|------------------------------------|-----|-------|------|-------|

|                                           | Min Typ Max           |     | Max   | Min                  | Min Max |      | n Condition Max                                                                                    |      |     | Тур                                | Max | Min   | Тур  | Max   |

| LVDEOL                                    |                       |     |       |                      |         | 0.05 | $D_{MAX} \leq 500 \; Mbps$                                                                         | 1.80 |     |                                    |     |       |      |       |

| LVPECL<br>(Row I/Os)<br>(6)               | 2.375                 | 2.5 | 2.625 | 100                  |         | 0.55 | $\begin{array}{l} 500 \; \text{Mbps} \leq  D_{\text{MAX}} \\ \leq  700 \; \text{Mbps} \end{array}$ | 1.80 | _   | $- \mid - \mid$                    | _   | _     | _    | _     |

|                                           |                       |     |       |                      |         | 1.05 | D <sub>MAX</sub> > 700 Mbps                                                                        | 1.55 |     |                                    |     |       |      |       |

| LVDEOL                                    |                       |     |       | 100                  | _       | 0.05 | $D_{MAX} \leq 500 \text{ Mbps}$                                                                    | 1.80 |     |                                    |     |       |      |       |

| LVPECL<br>(Column<br>I/Os) <sup>(6)</sup> | 2.375                 | 2.5 | 2.625 |                      |         | 0.55 | $\begin{array}{l} 500 \; \text{Mbps} \leq D_{\text{MAX}} \\ \leq 700 \; \text{Mbps} \end{array}$   | 1.80 | _   | _                                  | _   | _     | _    |       |

| 1/03)                                     |                       |     |       |                      |         | 1.05 | D <sub>MAX</sub> > 700 Mbps                                                                        | 1.55 |     |                                    |     |       |      |       |

|                                           |                       |     |       |                      | _       | 0.05 | $D_{MAX} \leq 500 \; Mbps$                                                                         | 1.80 |     |                                    |     |       |      |       |

| LVDS (Row<br>I/Os)                        | 2.375                 | 2.5 | 2.625 | 100                  |         | 0.55 | $\begin{array}{l} 500 \; \text{Mbps} \leq D_{\text{MAX}} \\ \leq 700 \; \text{Mbps} \end{array}$   | 1.80 | 247 | _                                  | 600 | 1.125 | 1.25 | 1.375 |

|                                           |                       |     |       |                      |         | 1.05 | $D_{MAX} > 700 \text{ Mbps}$                                                                       | 1.55 |     |                                    |     |       |      |       |

<sup>(1)</sup> Differential SSTL requires a  $V_{\text{REF}}$  input.

<sup>(1)</sup> Differential HSTL requires a  $V_{\text{REF}}$  input.