#### Intel - EP4CE55F23I7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 3491                                                     |

| Number of Logic Elements/Cells | 55856                                                    |

| Total RAM Bits                 | 2396160                                                  |

| Number of I/O                  | 324                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce55f23i7n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

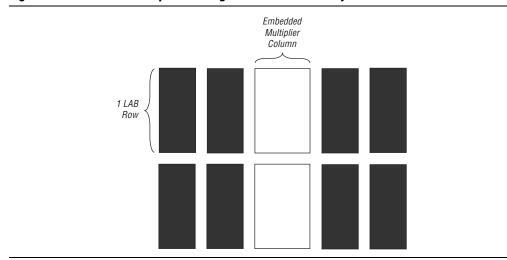

# 4. Embedded Multipliers in Cyclone IV Devices

Cyclone<sup>®</sup> IV devices include a combination of on-chip resources and external interfaces that help increase performance, reduce system cost, and lower the power consumption of digital signal processing (DSP) systems. Cyclone IV devices, either alone or as DSP device co-processors, are used to improve price-to-performance ratios of DSP systems. Particular focus is placed on optimizing Cyclone IV devices for applications that benefit from an abundance of parallel processing resources, which include video and image processing, intermediate frequency (IF) modems used in wireless communications systems, and multi-channel communications and video systems.

This chapter contains the following sections:

- "Embedded Multiplier Block Overview" on page 4–1

- "Architecture" on page 4–2

- "Operational Modes" on page 4–4

## **Embedded Multiplier Block Overview**

Figure 4–1 shows one of the embedded multiplier columns with the surrounding logic array blocks (LABs). The embedded multiplier is configured as either one  $18 \times 18$  multiplier or two  $9 \times 9$  multipliers. For multiplications greater than  $18 \times 18$ , the Quartus<sup>®</sup> II software cascades multiple embedded multiplier blocks together. There are no restrictions on the data width of the multiplier, but the greater the data width, the slower the multiplication process.

© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein exceept as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

Cyclone IV Device Handbook, Volume 1 February 2010

# 6. I/O Features in Cyclone IV Devices

This chapter describes the I/O and high speed I/O capabilities and features offered in Cyclone $^{\textcircled{B}}$  IV devices.

The I/O capabilities of Cyclone IV devices are driven by the diversification of I/O standards in many low-cost applications, and the significant increase in required I/O performance. Altera's objective is to create a device that accommodates your key board design needs with ease and flexibility.

The I/O flexibility of Cyclone IV devices is increased from the previous generation low-cost FPGAs by allowing all I/O standards to be selected on all I/O banks. Improvements to on-chip termination (OCT) support and the addition of true differential buffers have eliminated the need for external resistors in many applications, such as display system interfaces.

High-speed differential I/O standards have become popular in high-speed interfaces because of their significant advantages over single-ended I/O standards. The Cyclone IV devices support LVDS, BLVDS, RSDS, mini-LVDS, and PPDS. The transceiver reference clocks and the existing general-purpose I/O (GPIO) clock input features also support the LVDS I/O standards.

The Quartus<sup>®</sup> II software completes the solution with powerful pin planning features that allow you to plan and optimize I/O system designs even before the design files are available.

This chapter includes the following sections:

- "Cyclone IV I/O Elements" on page 6–2

- "I/O Element Features" on page 6–3

- "OCT Support" on page 6–6

- "I/O Standards" on page 6–11

- "Termination Scheme for I/O Standards" on page 6–13

- "I/O Banks" on page 6–16

<sup>© 2016</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# I/O Banks

I/O pins on Cyclone IV devices are grouped together into I/O banks. Each bank has a separate power bus.

Cyclone IV E devices have eight I/O banks, as shown in Figure 6–9. Each device I/O pin is associated with one I/O bank. All single-ended I/O standards are supported in all banks except HSTL-12 Class II, which is only supported in column I/O banks. All differential I/O standards are supported in all banks. The only exception is HSTL-12 Class II, which is only supported in column I/O banks.

Cyclone IV GX devices have up to ten I/O banks and two configuration banks, as shown in Figure 6–10 on page 6–18 and Figure 6–11 on page 6–19. The Cyclone IV GX configuration I/O bank contains three user I/O pins that can be used as normal user I/O pins if they are not used in configuration modes. Each device I/O pin is associated with one I/O bank. All single-ended I/O standards are supported except HSTL-12 Class II, which is only supported in column I/O banks. All differential I/O standards are supported in top, bottom, and right I/O banks. The only exception is HSTL-12 Class II, which is only supported in column I/O banks.

The entire left side of the Cyclone IV GX devices contain dedicated high-speed transceiver blocks for high speed serial interface applications. There are a total of 2, 4, and 8 transceiver channels for Cyclone IV GX devices, depending on the density and package of the device. For more information about the transceiver channels supported, refer to Figure 6–10 on page 6–18 and Figure 6–11 on page 6–19.

The nSTATUS and CONF\_DONE pins on all target devices are connected together with external pull-up resistors, as shown in Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27. These pins are open-drain bidirectional pins on the devices. When the first device asserts nCEO (after receiving all its configuration data), it releases its CONF\_DONE pin. However, the subsequent devices in the chain keep this shared CONF\_DONE line low until they receive their configuration data. When all target devices in the chain receive their configuration data and release CONF\_DONE, the pull-up resistor drives a high level on this line and all devices simultaneously enter initialization mode.

# Guidelines for Connecting Parallel Flash to Cyclone IV E Devices for an AP Interface

For single- and multi-device AP configuration, the board trace length and loading between the supported parallel flash and Cyclone IV E devices must follow the recommendations listed in Table 8–11. These recommendations also apply to an AP configuration with multiple bus masters.

| Cyclone IV E AP Pins | Maximum Board Trace Length from<br>Cyclone IV E Device to Flash Device<br>(inches) | Maximum Board Load (pF) |

|----------------------|------------------------------------------------------------------------------------|-------------------------|

| DCLK                 | 6                                                                                  | 15                      |

| DATA[150]            | 6                                                                                  | 30                      |

| PADD[230]            | 6                                                                                  | 30                      |

| nRESET               | 6                                                                                  | 30                      |

| Flash_nCE            | 6                                                                                  | 30                      |

| nOE                  | 6                                                                                  | 30                      |

| nAVD                 | 6                                                                                  | 30                      |

| nWE                  | 6                                                                                  | 30                      |

| I/O (1)              | 6                                                                                  | 30                      |

Table 8–11. Maximum Trace Length and Loading for AP Configuration

Note to Table 8-11:

(1) The AP configuration ignores the WAIT signal from the flash during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

## **Configuring With Multiple Bus Masters**

Similar to the AS configuration scheme, the AP configuration scheme supports multiple bus masters for the parallel flash. For another master to take control of the AP configuration bus, the master must assert nCONFIG low for at least 500 ns to reset the master Cyclone IV E device and override the weak 10-k $\Omega$  pull-down resistor on the nCE pin. This resets the master Cyclone IV E device then takes control of the AP configuration bus. The other master device then takes control of the AP configuration bus, then releases the nCE pin, and finally pulses nCONFIG low to restart the configuration.

In the AP configuration scheme, multiple masters share the parallel flash. Similar to the AS configuration scheme, the bus control is negotiated by the nCE pin.

The remote system upgrade status register is updated by the dedicated error monitoring circuitry after an error condition, but before the factory configuration is loaded.

| <b>Reconfiguration Error/Trigger</b> | Control Register Setting In Remote Update |

|--------------------------------------|-------------------------------------------|

| nCONFIG reset                        | All bits are 0                            |

| nSTATUS <b>error</b>                 | All bits are 0                            |

| CORE triggered reconfiguration       | Update register                           |

| CRC error                            | All bits are 0                            |

| Wd time out                          | All bits are 0                            |

Table 8–26. Control Register Contents After an Error or Reconfiguration Trigger Condition

### **User Watchdog Timer**

The user watchdog timer prevents a faulty application configuration from indefinitely stalling the device. The system uses the timer to detect functional errors after an application configuration is successfully loaded into the Cyclone IV device.

The user watchdog timer is a counter that counts down from the initial value loaded into the remote system upgrade control register by the factory configuration. The counter is 29 bits wide and has a maximum count value of 2<sup>29</sup>. When specifying the user watchdog timer value, specify only the most significant 12 bits. The remote system upgrade circuitry appends 17'b1000 to form the 29-bits value for the watchdog timer. The granularity of the timer setting is 2<sup>17</sup> cycles. The cycle time is based on the frequency of the 10-MHz internal oscillator or CLKUSR (maximum frequency of 40 MHz).

Table 8–27 lists the operating range of the 10-MHz internal oscillator.

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5       | 6.5     | 10      | MHz  |

The user watchdog timer begins counting after the application configuration enters device user mode. This timer must be periodically reloaded or reset by the application configuration before the timer expires by asserting RU\_nRSTIMER. If the application configuration does not reload the user watchdog timer before the count expires, a time-out signal is generated by the remote system upgrade dedicated circuitry. The time-out signal tells the remote system upgrade circuitry to set the user watchdog timer status bit (Wd) in the remote system upgrade status register and reconfigures the device by loading the factory configuration.

1 To allow the remote system upgrade dedicated circuitry to reset the watchdog timer, you must assert the RU\_nRSTIMER signal active for a minimum of 250 ns. This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE megafunction high for a minimum of 250 ns.

Errors during configuration are detected by the CRC engine. Functional errors must not exist in the factory configuration because it is stored and validated during production and is never updated remotely.

# **Receiver Channel Datapath**

The following sections describe the Cyclone IV GX receiver channel datapath architecture as shown in Figure 1–3 on page 1–4:

- "Receiver Input Buffer" on page 1–11

- "Clock Data Recovery" on page 1–15

- "Deserializer" on page 1–16

- "Word Aligner" on page 1–17

- "Deskew FIFO" on page 1–22

- "Rate Match FIFO" on page 1–23

- "8B/10B Decoder" on page 1–23

- "Byte Deserializer" on page 1–24

- "Byte Ordering" on page 1–24

- "RX Phase Compensation FIFO" on page 1–25

## **Receiver Input Buffer**

Table 1–2 lists the electrical features supported by the Cyclone IV GX receiver input buffer.

| I/O Standard | Programmable Common<br>Mode Voltage (V) | Coupling   |

|--------------|-----------------------------------------|------------|

| 1.4-V PCML   | 0.82                                    | AC, DC     |

| 1.5-V PCML   | 0.82                                    | AC, DC     |

| 2.5-V PCML   | 0.82                                    | AC         |

| LVPECL       | 0.82                                    | AC         |

| LVDS         | 0.82                                    | AC, DC (1) |

Note to Table 1–2:

(1) DC coupling is supported for LVDS with lower on-chip common mode voltage of 0.82 V.

- Programmable equalization—boosts the high-frequency gain of the incoming signal up to 7 dB. This compensates for the low-pass filter effects of the transmission media. The amount of high-frequency gain required depends on the loss characteristics of the physical medium.

- Programmable DC gain—provides equal boost to incoming signal across the frequency spectrum with DC gain settings up to 6 dB.

- Programmable differential OCT—provides calibrated OCT at 100 Ω or 150 Ω with on-chip receiver common mode voltage at 0.82 V. The common mode voltage is tristated when you disable the OCT to use external termination.

- Offset cancellation—corrects the analog offset voltages that might exist from process variations between the positive and negative differential signals in the equalizer stage and CDR circuit.

- Signal detection—detects if the signal level present at the receiver input buffer is higher than the threshold with a built-in signal threshold detection circuitry. The circuitry has a hysteresis response that filters out any high-frequency ringing caused by ISI effects or high-frequency losses in the transmission medium. Detection is indicated by the assertion of the rx\_signaldetect signal. Signal detection is only supported when 8B/10B encoder/decoder block is enabled. When not supported, the rx\_signaldetect signal is forced high, bypassing the signal detection function.

- 1 Disable OCT to use external termination if the link requires a  $85 \Omega$  termination, such as when you are interfacing with certain PCIe Gen1 or Gen2 capable devices.

- f For specifications on programmable equalization and DC gain settings, refer to the *Cyclone IV Device Data Sheet*.

# Figure 1–32. Clock Distribution in Non-Bonded Channel Configuration for Transceivers in F484 and Larger Packages

#### Notes to Figure 1-32:

- (1) High-speed clock.

- (2) Low-speed clock.

- (3) These PLLs have restricted clock driving capability and may not reach all connected channels. For details, refer to Table 1–9.

The transceiver datapath clocking varies in non-bonded channel configuration depending on the PCS configuration.

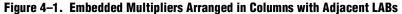

Figure 1–33 shows the datapath clocking in transmitter only operation. In this mode, each channel selects the high- and low-speed clock from one of the supported PLLs. The high-speed clock feeds to the serializer for parallel to serial operation. The low-speed clock feeds to the following blocks in the transmitter PCS:

- 8B/10B encoder

- read clock of the byte serializer

- read clock of the TX phase compensation FIFO

When the byte serializer is enabled, the common bonded low-speed clock frequency is halved before feeding to the read clock of TX phase compensation FIFO. The common bonded low-speed clock is available in FPGA fabric as coreclkout port, which can be used in FPGA fabric to send transmitter data and control signals to the bonded channels.

Figure 1–38. Transmitter Only Datapath Clocking in Bonded Channel Configuration

1 Bonded channel configuration is not available for Receiver Only channel operation because each of the channels are individually clocked by its recovered clock.

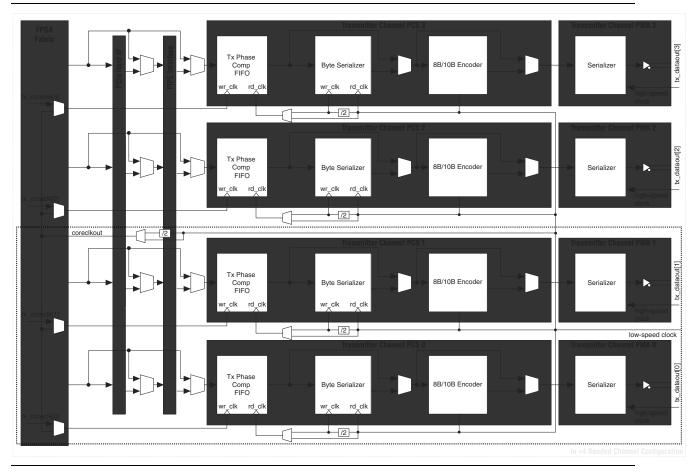

Figure 1–64 shows the transceiver configuration in XAUI mode.

## XGMII and PCS Code Conversions

In XAUI mode, the 8B/10B encoder in the transmitter datapath maps various 8-bit XGMII codes to 10-bit PCS code groups as listed in Table 1–21.

Table 1–21. XGMII Character to PCS Code Groups Mapping (Part 1 of 2)

| XGMII TXC (1) | XGMII TXD (2), (3) | PCS Code Group         | Description              |

|---------------|--------------------|------------------------|--------------------------|

| 0             | 00 through FF      | Dxx,y                  | Normal data transmission |

| 1             | 07                 | K28.0, K28.3, or K28.5 | Idle in   I              |

| 1             | 07                 | K28.5                  | Idle in   T              |

| 1             | 9C                 | K28.4                  | Sequence                 |

| 1             | FB                 | K27.7                  | Start                    |

| 1             | FD                 | K29.7                  | Terminate                |

| 1             | FE                 | K30.7                  | Error                    |

| Port Name           | Input/<br>Output | Clock Domain | Description                                                                              |  |

|---------------------|------------------|--------------|------------------------------------------------------------------------------------------|--|

|                     |                  |              | PIPE receiver status port.                                                               |  |

|                     |                  |              | <ul> <li>Signal is 3 bits wide and is encoded as follows:</li> </ul>                     |  |

|                     |                  |              | <ul> <li>3'b000: Received data OK</li> </ul>                                             |  |

|                     |                  | N/A          | <ul> <li>3'b001: one SKP symbol added</li> </ul>                                         |  |

| ninostatus          | 0                |              | <ul> <li>3'b010: one SKP symbol removed</li> </ul>                                       |  |

| pipestatus          | Output           |              | <ul> <li>3'b011: Receiver detected</li> </ul>                                            |  |

|                     |                  |              | <ul> <li>3'b100: 8B/10B decoder error</li> </ul>                                         |  |

|                     |                  |              | <ul> <li>3'b101: Elastic buffer overflow</li> </ul>                                      |  |

|                     |                  |              | <ul> <li>3'b110: Elastic buffer underflow</li> </ul>                                     |  |

|                     |                  |              | <ul> <li>3'b111: Received disparity error</li> </ul>                                     |  |

| rx_elecidleinfersel | Input            | N/A          | Controls the electrical idle inference mechanism as specified in Table 1–17 on page 1–57 |  |

## Table 1–28. PIPE Interface Ports in ALTGX Megafunction for Cyclone IV GX<sup>(1)</sup> (Part 2 of 2)

#### Note to Table 1-28:

(1) For equivalent signals defined in PIPE 2.00 specification, refer to Table 1–15 on page 1–54.

| Table 1-29. Multipurpose PLL, General Purpose PLL and Miscellaneous Ports in ALTGX Megafunction for |  |

|-----------------------------------------------------------------------------------------------------|--|

| Cyclone IV GX (Part 1 of 2)                                                                         |  |

| Block | Port Name  | Input/<br>Output | Clock Domain        | Description                                                                                                                                                                                                                                                                         |

|-------|------------|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | pll_inclk  | Input            | Clock signal        | Input reference clock for the PLL (multipurpose PLL or<br>general purpose PLL) used by the transceiver instance. When<br>configured with the transmitter and receiver channel<br>configuration in Deterministic Latency mode, multiple<br>pll_inclk ports are available as follows. |

|       |            |                  |                     | Configured with PLL PFD feedback—x is the number of<br>channels selected:                                                                                                                                                                                                           |

|       |            |                  |                     | pll_inclk[x-10] are input reference clocks for each transmitter in the transceiver instance                                                                                                                                                                                         |

|       |            |                  |                     | pll_inclk[x+1x] are input reference clocks for<br>receivers in the transceiver instance                                                                                                                                                                                             |

| PLL   |            |                  |                     | Configured without PLL PFD feedback:                                                                                                                                                                                                                                                |

|       |            |                  |                     | pll_inclk[0] is input reference clock for transmitters in<br>the transceiver instance                                                                                                                                                                                               |

|       |            |                  |                     | pll_inclk[1] is input reference clock for receivers in the transceiver instance                                                                                                                                                                                                     |

|       | pll_locked | Output           | Asynchronous signal | PLL (used by the transceiver instance) lock indicator.                                                                                                                                                                                                                              |

|       | pll_areset | Input            | Asynchronous signal | PLL (used by the transceiver instance) reset.                                                                                                                                                                                                                                       |

|       |            |                  |                     | <ul> <li>When asserted, the PLL is kept in reset state.</li> </ul>                                                                                                                                                                                                                  |

|       |            |                  |                     | <ul> <li>When deasserted, the PLL is active and locks to the input<br/>reference clock.</li> </ul>                                                                                                                                                                                  |

|       | coreclkout | Output           | Clock signal        | FPGA fabric-transceiver interface clock in bonded modes.                                                                                                                                                                                                                            |

1–91

| Port Name                        | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                    |                                                                                                                           |  |

|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

|                                  | Input            | Enabled by the ALTGX_RECONFIG MegaWizard Plug-In Manager when you enable the <b>Use</b><br>'logical_channel_address' port for Analog controls reconfiguration option in the Analog<br>controls screen.                                                                                                                                         |                                                                                                                           |  |

| logical_channel_                 |                  | The width of the logical_channel_address port depends on the value you set in the What is the number of channels controlled by the reconfig controller? option in the <b>Reconfiguration settings</b> screen. This port can be enabled only when the number of channels controlled by the dynamic reconfiguration controller is more than one. |                                                                                                                           |  |

| address[n0]                      |                  | Number of channels controlled<br>by the reconfiguration controller                                                                                                                                                                                                                                                                             | logical_channel_address input port width                                                                                  |  |

|                                  |                  | 2<br>3–4<br>5–8<br>9–16                                                                                                                                                                                                                                                                                                                        | <pre>logical_channel_address[0] logical_channel_address[10] logical_channel_address[20] logical_channel_address[30]</pre> |  |

|                                  |                  | This is a 2-bit wide signal. You can selec                                                                                                                                                                                                                                                                                                     |                                                                                                                           |  |

|                                  |                  | The advantage of using this optional port is that it allows you to reconfigure only the transmitter portion of a channel, even if the channel configuration is duplex.                                                                                                                                                                         |                                                                                                                           |  |

|                                  |                  | For a setting of:                                                                                                                                                                                                                                                                                                                              |                                                                                                                           |  |

| <pre>rx_tx_duplex_sel [10]</pre> | Input            | <pre>rx_tx_duplex_sel[1:0] = 2'b00—the transmitter and receiver portion of the<br/>channel is reconfigured.</pre>                                                                                                                                                                                                                              |                                                                                                                           |  |

|                                  |                  | <pre>rx_tx_duplex_sel[1:0] = 2'b01- reconfigured.</pre>                                                                                                                                                                                                                                                                                        | -the receiver portion of the channel is                                                                                   |  |

|                                  |                  | <pre>rx_tx_duplex_sel[1:0] = 2'b10- reconfigured.</pre>                                                                                                                                                                                                                                                                                        | -the transmitter portion of the channel is                                                                                |  |

Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 3 of 7)

| Port Name              | Input/<br>Output | Description                                                                                                                                                                                                                                                                                        |                                          |                                                |  |  |  |  |  |  |  |

|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------|--|--|--|--|--|--|--|

| Analog Settings Contro | I/Status S       | ignals                                                                                                                                                                                                                                                                                             |                                          |                                                |  |  |  |  |  |  |  |

|                        |                  | This is an optional transmit buffer $V_{0D}$ control signal. It is 3 bits per transmitter channel.<br>The number of settings varies based on the transmit buffer supply setting and the<br>termination resistor setting on the <b>TX Analog</b> screen of the ALTGX MegaWizard Plug-In<br>Manager. |                                          |                                                |  |  |  |  |  |  |  |

|                        |                  | 'logical_channel_addr                                                                                                                                                                                                                                                                              | •                                        |                                                |  |  |  |  |  |  |  |

|                        |                  | The following shows the $V_{0D}$ values corresponding to the <code>tx_vodctrl</code> settings for 100- $\Omega$ termination.                                                                                                                                                                       |                                          |                                                |  |  |  |  |  |  |  |

| tx_vodctrl[20]<br>(1)  | Input            | For more information, refer to the "Programmable Output Differential Voltage" sect the <i>Cyclone IV GX Device Datasheet</i> chapter.                                                                                                                                                              |                                          |                                                |  |  |  |  |  |  |  |

|                        |                  | <pre>tx_vodctrl[2:0]</pre>                                                                                                                                                                                                                                                                         | Corresponding ALTGX<br>instance settings | Corresponding V <sub>OD</sub><br>settings (mV) |  |  |  |  |  |  |  |

|                        |                  | 3'b001                                                                                                                                                                                                                                                                                             | 1                                        | 400                                            |  |  |  |  |  |  |  |

|                        |                  | 3'b010                                                                                                                                                                                                                                                                                             | 2                                        | 600                                            |  |  |  |  |  |  |  |

|                        |                  | 3'b011                                                                                                                                                                                                                                                                                             | 3                                        | 800                                            |  |  |  |  |  |  |  |

|                        |                  | 3'b111                                                                                                                                                                                                                                                                                             | 4 (2)                                    | 900 <sup>(2)</sup>                             |  |  |  |  |  |  |  |

|                        |                  | 3'b100                                                                                                                                                                                                                                                                                             | 5                                        | 1000                                           |  |  |  |  |  |  |  |

|                        |                  | 3'b101                                                                                                                                                                                                                                                                                             | 6                                        | 1200                                           |  |  |  |  |  |  |  |

|                        |                  | All other values => N/A                                                                                                                                                                                                                                                                            |                                          |                                                |  |  |  |  |  |  |  |

## Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 4 of 7)

The following are the channel reconfiguration mode options:

- Channel interface reconfiguration

- Data rate division at receiver channel

## **Channel Interface Reconfiguration Mode**

Enable this option if the reconfiguration of the transceiver channel involves the following changes:

- The reconfigured channel has a changed FPGA fabric-Transceiver channel interface data width

- The reconfigured channel has changed input control signals and output status signals

- The reconfigured channel has enabled and disabled the static PCS blocks of the transceiver channel

The following are the new input signals available when you enable this option:

- tx\_datainfull—the width of this input signal depends on the number of channels you set up in the ALTGX MegaWizard Plug-In Manager. It is 22 bits wide per channel. This signal is available only for Transmitter only and Receiver and Transmitter configurations. This port replaces the existing tx\_datain port.

- rx\_dataoutfull—the width of this output signal depends on the number of channels you set up in the ALTGX MegaWizard Plug-In Manager. It is 32 bits wide per channel. This signal is available only for **Receiver only** and **Receiver and Transmitter** configurations. This port replaces the existing rx\_dataout port.

The Quartus II software has legality checks for the connectivity of tx\_datainfull and rx\_dataoutfull and the various control and status signals you enable in the **Clocking/Interface** screen. For example, the Quartus II software allows you to select and connect the pipestatus and powerdn signals. It assumes that you are planning to switch to and from PCI Express (PIPE) functional mode.

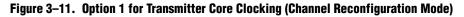

#### **Option 1: Share a Single Transmitter Core Clock Between Transmitters**

- Enable this option if you want tx\_clkout of the first channel (channel 0) of the transceiver block to provide the write clock to the Transmitter Phase Compensation FIFOs of the remaining channels in the transceiver block.

- This option is typically enabled when all the channels of a transceiver block have the same functional mode and data rate and are reconfigured to the identical functional mode and data rate.

Figure 3–11 shows the sharing of channel 0's tx\_clkout between all four regular channels of a transceiver block.

| Chapter Revision Dates  | v      |

|-------------------------|--------|

| Additional Information  |        |

| How to Contact Altera   | Info-1 |

| Typographic Conventions | Info–1 |

# Section I. Device Datasheet

## Chapter 1. Cyclone IV Device Datasheet

| Operating Conditions                              | 1–1  |

|---------------------------------------------------|------|

| Absolute Maximum Ratings                          | 1–2  |

| Maximum Allowed Overshoot or Undershoot Voltage   |      |

| Recommended Operating Conditions                  |      |

| ESD Performance                                   |      |

| DC Characteristics                                | 1–7  |

| Supply Current                                    |      |

| Bus Hold                                          | 1–7  |

| OCT Specifications                                | 1–8  |

| Pin Capacitance                                   |      |

| Internal Weak Pull-Up and Weak Pull-Down Resistor | 1–11 |

| Hot-Socketing                                     | 1–11 |

| Schmitt Trigger Input                             |      |

| I/O Standard Specifications                       | 1–12 |

| Power Consumption                                 |      |

| Switching Characteristics                         | 1–16 |

| Transceiver Performance Specifications            | 1–17 |

| Core Performance Specifications                   | 1–23 |

| Clock Tree Specifications                         |      |

| PLL Specifications                                | 1–24 |

| Embedded Multiplier Specifications                | 1–26 |

| Memory Block Specifications                       | 1–26 |

| Configuration and JTAG Specifications             | 1–26 |

| Periphery Performance                             |      |

| High-Speed I/O Specifications                     |      |

| External Memory Interface Specifications          | 1–32 |

| Duty Cycle Distortion Specifications              |      |

| OCT Calibration Timing Specification              |      |

| IOE Programmable Delay                            | 1–34 |

| I/O Timing                                        | 1–37 |

| Glossary                                          |      |

| Document Revision History                         | 1–42 |

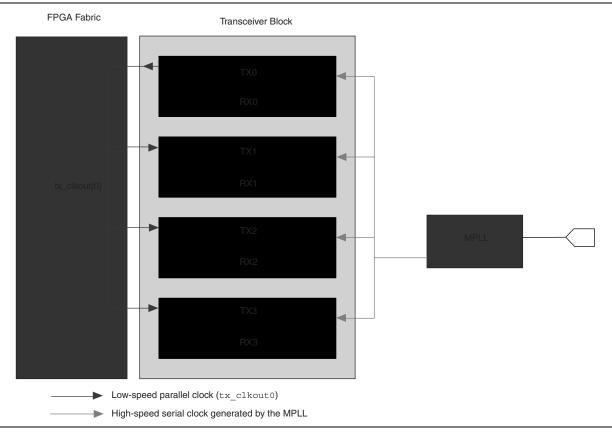

1 A DC signal is equivalent to 100% duty cycle. For example, a signal that overshoots to 4.3 V can only be at 4.3 V for 65% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 65/10ths of a year.

| Symbol | Parameter              | Condition (V)         | Overshoot Duration as % of High Time | Unit |

|--------|------------------------|-----------------------|--------------------------------------|------|

|        |                        | V <sub>1</sub> = 4.20 | 100                                  | %    |

|        |                        | V <sub>1</sub> = 4.25 | 98                                   | %    |

|        |                        | $V_1 = 4.30$          | 65                                   | %    |

|        | /i AC Input<br>Voltage | V <sub>1</sub> = 4.35 | 43                                   | %    |

| Vi     |                        | $V_1 = 4.40$          | 29                                   | %    |

|        |                        | V <sub>1</sub> = 4.45 | 20                                   | %    |

|        |                        | $V_1 = 4.50$          | 13                                   | %    |

|        |                        | V <sub>1</sub> = 4.55 | 9                                    | %    |

|        |                        | $V_1 = 4.60$          | 6                                    | %    |

Table 1–2. Maximum Allowed Overshoot During Transitions over a 10-Year Time Frame for Cyclone IV Devices

Figure 1–1 shows the methodology to determine the overshoot duration. The overshoot voltage is shown in red and is present on the input pin of the Cyclone IV device at over 4.3 V but below 4.4 V. From Table 1–2, for an overshoot of 4.3 V, the percentage of high time for the overshoot can be as high as 65% over a 10-year period. Percentage of high time is calculated as ([delta T]/T) × 100. This 10-year period assumes that the device is always turned on with 100% I/O toggle rate and 50% duty cycle signal. For lower I/O toggle rates and situations in which the device is in an idle state, lifetimes are increased.

#### Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 4 of 4)

| Symbol/<br>Description                           | Conditions                |                                    | C6  |        |     | C7, I7 |        |     | Unit |        |      |

|--------------------------------------------------|---------------------------|------------------------------------|-----|--------|-----|--------|--------|-----|------|--------|------|

|                                                  | Conultions                | Min                                | Тур | Max    | Min | Тур    | Max    | Min | Тур  | Max    | Unit |

| PLD-Transceiver Inte                             | PLD-Transceiver Interface |                                    |     |        |     |        |        |     |      |        |      |

| Interface speed<br>(F324 and smaller<br>package) | _                         | 25                                 | _   | 125    | 25  | _      | 125    | 25  | _    | 125    | MHz  |

| Interface speed<br>(F484 and larger<br>package)  | _                         | 25                                 | _   | 156.25 | 25  | _      | 156.25 | 25  | _    | 156.25 | MHz  |

| Digital reset pulse width                        | _                         | Minimum is 2 parallel clock cycles |     |        |     |        |        |     |      |        |      |

#### Notes to Table 1–21:

(1) This specification is valid for transmitter output jitter specification with a maximum total jitter value of 112 ps, typically for 3.125 Gbps SRIO and XAUI protocols.

(2) The minimum reconfig\_clk frequency is 2.5 MHz if the transceiver channel is configured in **Transmitter Only** mode. The minimum reconfig\_clk frequency is 37.5 MHz if the transceiver channel is configured in **Receiver Only** or **Receiver and Transmitter** mode.

(3) The device cannot tolerate prolonged operation at this absolute maximum.

- (4) The rate matcher supports only up to ±300 parts per million (ppm).

- (5) Supported for the F169 and F324 device packages only.

- (6) Supported for the F484, F672, and F896 device packages only. Pending device characterization.

- (7) To support CDR ppm tolerance greater than ±300 ppm, implement ppm detector in user logic and configure CDR to Manual Lock Mode.

- (8) Asynchronous spread-spectrum clocking is not supported.

- (9) For the EP4CGX30 (F484 package only), EP4CGX50, and EP4CGX75 devices, the CDR ppl tolerance is ±200 ppm.

- (10) Time taken until pll\_locked goes high after pll\_powerdown deasserts.

- (11) Time that the CDR must be kept in lock-to-reference mode after rx\_analogreset deasserts and before rx\_locktodata is asserted in manual mode.

(12) Time taken to recover valid data after the rx\_locktodata signal is asserted in manual mode (Figure 1-2), or after rx\_freqlocked signal goes high in automatic mode (Figure 1-3).

(13) Time taken to recover valid data after the rx\_locktodata signal is asserted in manual mode.

- (14) Time taken to recover valid data after the  $rx\_freqlocked$  signal goes high in automatic mode.

- (15) To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

- f For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to *Section III: System Performance Specifications* of the *External Memory Interfaces Handbook*.

- 1 Actual achievable frequency depends on design- and system-specific factors. Perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

## **High-Speed I/O Specifications**

Table 1–31 through Table 1–36 list the high-speed I/O timing for Cyclone IV devices. For definitions of high-speed timing specifications, refer to "Glossary" on page 1–37.

Table 1–31. RSDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4) (Part 1 of 2)

| Symbol                                               | Madar                                    | C6  |     | C7, 17 |     |     | C8, A7 |     |     | C8L, I8L |     |     | C9L   |     |     |       |      |

|------------------------------------------------------|------------------------------------------|-----|-----|--------|-----|-----|--------|-----|-----|----------|-----|-----|-------|-----|-----|-------|------|

|                                                      | Modes                                    | Min | Тур | Max    | Min | Тур | Max    | Min | Тур | Max      | Min | Тур | Max   | Min | Тур | Max   | Unit |

| f <sub>HSCLK</sub>                                   | ×10                                      | 5   |     | 180    | 5   |     | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   |     | 132.5 | MHz  |

|                                                      | ×8                                       | 5   |     | 180    | 5   |     | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   |     | 132.5 | MHz  |

|                                                      | ×7                                       | 5   | _   | 180    | 5   |     | 155.5  | 5   | _   | 155.5    | 5   | _   | 155.5 | 5   |     | 132.5 | MHz  |

| (input clock<br>frequency)                           | ×4                                       | 5   | _   | 180    | 5   | —   | 155.5  | 5   | _   | 155.5    | 5   | _   | 155.5 | 5   | —   | 132.5 | MHz  |

| 1 37                                                 | ×2                                       | 5   |     | 180    | 5   |     | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   |     | 132.5 | MHz  |

|                                                      | ×1                                       | 5   | _   | 360    | 5   |     | 311    | 5   | _   | 311      | 5   | _   | 311   | 5   |     | 265   | MHz  |

|                                                      | ×10                                      | 100 | _   | 360    | 100 |     | 311    | 100 | _   | 311      | 100 | _   | 311   | 100 |     | 265   | Mbps |

|                                                      | ×8                                       | 80  |     | 360    | 80  |     | 311    | 80  |     | 311      | 80  |     | 311   | 80  |     | 265   | Mbps |

| Device<br>operation in                               | ×7                                       | 70  |     | 360    | 70  | —   | 311    | 70  |     | 311      | 70  |     | 311   | 70  | —   | 265   | Mbps |

| Mbps                                                 | ×4                                       | 40  |     | 360    | 40  | —   | 311    | 40  |     | 311      | 40  |     | 311   | 40  | —   | 265   | Mbps |

|                                                      | ×2                                       | 20  | _   | 360    | 20  |     | 311    | 20  | _   | 311      | 20  | _   | 311   | 20  |     | 265   | Mbps |

|                                                      | ×1                                       | 10  |     | 360    | 10  | —   | 311    | 10  |     | 311      | 10  |     | 311   | 10  | —   | 265   | Mbps |

| t <sub>DUTY</sub>                                    | —                                        | 45  |     | 55     | 45  |     | 55     | 45  |     | 55       | 45  |     | 55    | 45  |     | 55    | %    |

| Transmitter<br>channel-to-<br>channel skew<br>(TCCS) | _                                        | _   |     | 200    | _   | _   | 200    | _   | _   | 200      | _   |     | 200   |     | _   | 200   | ps   |

| Output jitter<br>(peak to peak)                      |                                          | _   |     | 500    | _   | _   | 500    | _   |     | 550      | _   |     | 600   |     | _   | 700   | ps   |

| t <sub>RISE</sub>                                    | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _      | _   | 500 | _      | _   | 500 |          | _   | 500 |       | _   | 500 |       | ps   |

| t <sub>FALL</sub>                                    | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _      | _   | 500 | _      | _   | 500 |          | _   | 500 |       | _   | 500 |       | ps   |