### Intel - EP4CE55F29C6N Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Detailo                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 3491                                                     |

| Number of Logic Elements/Cells | 55856                                                    |

| Total RAM Bits                 | 2396160                                                  |

| Number of I/O                  | 374                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BGA                                                  |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce55f29c6n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. Memory Blocks in Cyclone IV Devices

Cyclone<sup>®</sup> IV devices feature embedded memory structures to address the on-chip memory needs of Altera<sup>®</sup> Cyclone IV device designs. The embedded memory structure consists of columns of M9K memory blocks that you can configure to provide various memory functions, such as RAM, shift registers, ROM, and FIFO buffers.

This chapter contains the following sections:

- "Memory Modes" on page 3–7

- "Clocking Modes" on page 3–14

- "Design Considerations" on page 3–15

## **Overview**

M9K blocks support the following features:

- 8,192 memory bits per block (9,216 bits per block including parity)

- Independent read-enable (rden) and write-enable (wren) signals for each port

- Packed mode in which the M9K memory block is split into two 4.5 K single-port RAMs

- Variable port configurations

- Single-port and simple dual-port modes support for all port widths

- True dual-port (one read and one write, two reads, or two writes) operation

- Byte enables for data input masking during writes

- Two clock-enable control signals for each port (port A and port B)

- Initialization file to pre-load memory content in RAM and ROM modes

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and sumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **18-Bit Multipliers**

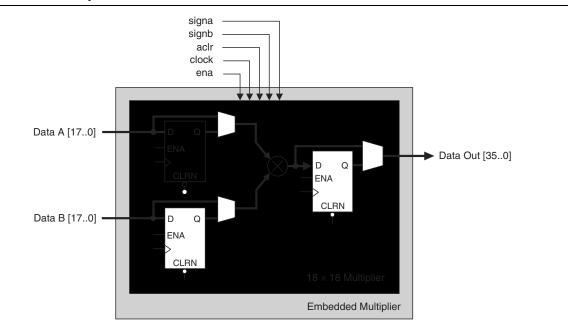

You can configure each embedded multiplier to support a single  $18 \times 18$  multiplier for input widths of 10 to 18 bits.

Figure 4–3 shows the embedded multiplier configured to support an 18-bit multiplier.

Figure 4–3. 18-Bit Multiplier Mode

All 18-bit multiplier inputs and results are independently sent through registers. The multiplier inputs can accept signed integers, unsigned integers, or a combination of both. Also, you can dynamically change the signa and signb signals and send these signals through dedicated input registers.

# **Document Revision History**

Table 5–14 lists the revision history for this chapter.

| Date             | Version | Changes                                                                                                                               |

|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| October 2012     | 2.4     | <ul> <li>Updated "Manual Override" and "PLL Cascading" sections.</li> </ul>                                                           |

| 0010ber 2012 2.4 |         | ■ Updated Figure 5–9.                                                                                                                 |

| November 2011    | 2.3     | <ul> <li>Updated the "Dynamic Phase Shifting" section.</li> </ul>                                                                     |

|                  | 2.3     | <ul> <li>Updated Figure 5–26.</li> </ul>                                                                                              |

|                  |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                         |

|                  |         | ■ Updated Figure 5–3 and Figure 5–10.                                                                                                 |

| December 2010    | 2.2     | <ul> <li>Updated "GCLK Network Clock Source Generation", "PLLs in Cyclone IV Devices",<br/>and "Manual Override" sections.</li> </ul> |

|                  |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                 |

|                  |         | ■ Updated Figure 5–2, Figure 5–3, Figure 5–4, and Figure 5–10.                                                                        |

| July 2010        | 2.1     | ■ Updated Table 5–1, Table 5–2, and Table 5–5.                                                                                        |

|                  |         | <ul> <li>Updated "Clock Feedback Modes" section.</li> </ul>                                                                           |

|                  |         | <ul> <li>Added Cyclone IV E devices information for the Quartus II software version 9.1 SP1<br/>release.</li> </ul>                   |

|                  |         | <ul> <li>Updated "Clock Networks" section.</li> </ul>                                                                                 |

| February 2010    | 2.0     | ■ Updated Table 5–1 and Table 5–2.                                                                                                    |

|                  |         | ■ Added Table 5–3.                                                                                                                    |

|                  |         | ■ Updated Figure 5–2, Figure 5–3, and Figure 5–9.                                                                                     |

|                  |         | <ul> <li>Added Figure 5–4 and Figure 5–10.</li> </ul>                                                                                 |

| November 2009    | 1.0     | Initial release.                                                                                                                      |

# Table 8–4. Configuration Schemes for Cyclone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150) (Part 2 of 2)

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) $^{(1)}$ |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------|

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   | _         | _                                           |

### Notes to Table 8-4:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to  $V_{CCA}$  or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

> Smaller Cyclone IV E devices or package options (E144 and F256 packages) do not have the MSEL[3] pin. The AS Fast POR configuration scheme at 3.0- or 2.5-V configuration voltage standard and the AP configuration scheme are not supported in Cyclone IV E devices without the MSEL[3] pin. To configure these devices with other supported configuration schemes, select MSEL[2..0] pins according to the MSEL settings in Table 8–5.

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------------|

|                              | 1     | 1     | 0     | 1     | Fast      | 3.3                                               |

| AS                           | 0     | 1     | 0     | 0     | Fast      | 3.0, 2.5                                          |

|                              | 0     | 0     | 1     | 0     | Standard  | 3.3                                               |

|                              | 0     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 0     | 1     | 0     | 1     | Fast      | 3.3                                               |

|                              | 0     | 1     | 1     | 0     | Fast      | 1.8                                               |

| AP                           | 0     | 1     | 1     | 1     | Standard  | 3.3                                               |

|                              | 1     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 1     | 0     | 0     | 0     | Standard  | 1.8                                               |

| PS                           | 1     | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| 15                           | 0     | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                                     |

| FPP                          | 1     | 1     | 1     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

|                              | 1     | 1     | 1     | 1     | Fast      | 1.8, 1.5                                          |

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   |           | _                                                 |

Table 8–5. Configuration Schemes for Cyclone IV E Devices

### Notes to Table 8-5:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to V<sub>CCA</sub> or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration. four devices. During the first configuration cycle, the master device reads its configuration data from the serial configuration device while holding nCEO high. After completing its configuration cycle, the master device drives nCE low and sends the second copy of the configuration data to all three slave devices, configuring them simultaneously.

The advantage of the setup in Figure 8–4 is that you can have a different **.sof** for the master device. However, all the slave devices must be configured with the same **.sof**. You can either compress or uncompress the **.sof** in this configuration method.

You can still use this method if the master and slave devices use the same **.sof**.

To ensure that DCLK and DATA[0] are not left floating at the end of the configuration, the MAX II device must drive them either high or low, whichever is convenient on your board. The DATA[0] pin is available as a user I/O pin after configuration. When you choose the FPP scheme in the Quartus II software, the DATA[0] pin is tri-stated by default in user mode and must be driven by the external host device. To change this default option in the Quartus II software, select the **Dual-Purpose Pins** tab of the **Device and Pin Options** dialog box.

The DCLK speed must be below the specified system frequency to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

The external host device can also monitor the CONF\_DONE and INIT\_DONE pins to ensure successful configuration. The CONF\_DONE pin must be monitored by the external device to detect errors and to determine when programming is complete. If all configuration data is sent, but CONF\_DONE or INIT\_DONE has not gone high, the external device must reconfigure the target device.

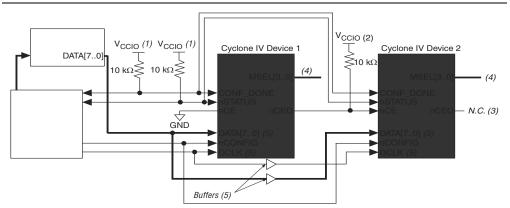

Figure 8–20 shows how to configure multiple devices with a MAX II device. This circuit is similar to the FPP configuration circuit for a single device, except the Cyclone IV devices are cascaded for multi-device configuration.

Figure 8–20. Multi-Device FPP Configuration Using an External Host

### Notes to Figure 8-20:

- (1) The pull-up resistor must be connected to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  must be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

- (2) Connect the pull-up resistor to the  $V_{CCI0}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–4 on page 8–8 and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [7..0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

After the first device completes configuration in a multi-device configuration chain, its nCEO pin drives low to activate the nCE pin of the second device, which prompts the second device to begin configuration. The second device in the chain begins configuration in one clock cycle; therefore, the transfer of data destinations is transparent to the MAX II device. All other configuration pins (nCONFIG, nSTATUS,

| Bank | Description | Input/Output | Dedicated | Powered By        | <b>Configuration Mode</b> |

|------|-------------|--------------|-----------|-------------------|---------------------------|

| 5    | DEV_CLRn    | Input        | _         | V <sub>CCIO</sub> | Optional, AP              |

| <b>Table 8–19</b> . | <b>Configuration Pin</b> | Summary for C   | yclone IV E Devices  | (Part 3 of 3)   |

|---------------------|--------------------------|-----------------|----------------------|-----------------|

|                     | oominguration i m        | ounninaly for o | YUIUIIC IV L DUVIUUS | (1 41 ( 0 01 0) |

#### Notes to Table 8–19:

(1) To tri-state AS configuration pins in the AS configuration scheme, turn-on the Enable input tri-state on active configuration pins in user mode option from the Device and Pin Options dialog box. This tri-states DCLK, nCSO, Data[0], and Data[1]/ASDO pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the Enable input tri-state on active configuration pins in user mode option and set the desired setting from the Dual-purpose Pins Setting menu.

- (2) To tri-state AP configuration pins in the AP configuration scheme, turn-on the Enable input tri-state on active configuration pins in user mode option from the Device and Pin Options dialog box. This tri-states DCLK, Data[0..15], FLASH\_nCE, and other AP pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the Enable input tri-state on active configuration pins in user mode option and set the desired setting from the Dual-purpose Pins Setting menu.

- (3) The CRC\_ERROR pin is not available in Cyclone IV E devices with 1.0-V core voltage.

- (4) The CRC\_ERROR pin is a dedicated open-drain output or an optional user I/O pin. Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device and Pin Options dialog box. When using this pin, connect it to an external 10-kΩ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.

Table 8–20 describes the dedicated configuration pins. You must properly connect these pins on your board for successful configuration. You may not need some of these pins for your configuration schemes.

| Pin Name | User Mode | Configuration<br>Scheme | Pin Type                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------|-------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSEL     | N/A       | All                     | Input                       | Configuration input that sets the Cyclone IV device configuration scheme. You must hardwire these pins to $V_{CCA}$ or GND. The MSEL pins have internal 9-k $\Omega$ pull-down resistors that are always active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| nCONFIG  | N/A       | All                     | Input                       | Configuration control input. Pulling this pin low with<br>external circuitry during user mode causes the Cyclone IV<br>device to lose its configuration data, enter a reset state, and<br>tri-state all I/O pins. Returning this pin to a logic-high level<br>starts a reconfiguration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| nSTATUS  | N/A       | All                     | Bidirectional<br>open-drain | <ul> <li>The Cyclone IV device drives nSTATUS low immediately after power-up and releases it after the POR time.</li> <li>Status output—if an error occurs during configuration, nSTATUS is pulled low by the target device.</li> <li>Status input—if an external source (for example, another Cyclone IV device) drives the nSTATUS pin low during configuration or initialization, the target device enters an error state.</li> <li>Driving nSTATUS low after configuration and initialization does not affect the configured device. If you use a configuration device, driving nSTATUS low causes the configuration device to attempt to configure the device, but because the device does not reconfigure. To start a reconfiguration, you must pull nCONFIG low.</li> </ul> |

Table 8-20. Dedicated Configuration Pins on the Cyclone IV Device (Part 1 of 4)

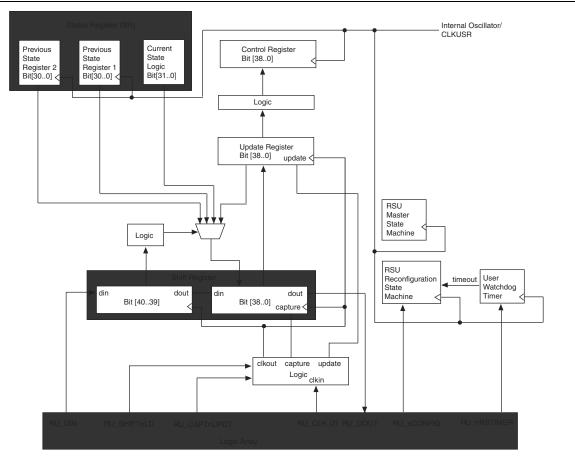

## **Dedicated Remote System Upgrade Circuitry**

This section describes the implementation of the Cyclone IV device remote system upgrade dedicated circuitry. The remote system upgrade circuitry is implemented in hard logic. This dedicated circuitry interfaces with the user-defined factory application configurations implemented in the Cyclone IV device logic array to provide the complete remote configuration solution. The remote system upgrade circuitry contains the remote system upgrade registers, a watchdog timer, and state machines that control those components. Figure 8–33 shows the data path of the remote system upgrade block.

Figure 8–33. Remote System Upgrade Circuit Data Path (1)

### Notes to Figure 8-33:

- (1) The RU\_DOUT, RU\_SHIFTnLD, RU\_CAPTNUPDT, RU\_CLK, RU\_DIN, RU\_nCONFIG, and RU\_nRSTIMER signals are internally controlled by the ALTREMOTE\_UPDATE megafunction.

- (2) The RU\_CLK refers to the ALTREMOTE\_UPDATE megafunction block "clock" input. For more information, refer to the *Remote Update Circuitry* (ALTREMOTE\_UPDATE) Megafunction User Guide.

# 11. Power Requirements for Cyclone IV Devices

#### CYIV-51011-1.3

This chapter describes information about external power supply requirements, hot-socketing specifications, power-on reset (POR) requirements, and their implementation in Cyclone IV devices.

This chapter includes the following sections:

- "External Power Supply Requirements" on page 11–1

- "Hot-Socketing Specifications" on page 11–2

- "Hot-socketing Feature Implementation" on page 11–3

- "Power-On Reset Circuitry" on page 11–3

# **External Power Supply Requirements**

This section describes the different external power supplies required to power Cyclone IV devices. Table 11–1 and Table 11–2 list the descriptions of external power supply pins for Cyclone IV GX and Cyclone IV E devices, respectively.

**To** For power supply pin connection guidelines and power regulator sharing, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

| Power Supply Pin Nominal Voltage Level (V) |                              | Description                                                                                                 |

|--------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------|

| VCCINT                                     | 1.2                          | Core voltage, PCI Express (PCIe) hard IP block, and transceiver physical coding sublayer (PCS) power supply |

| VCCA (1)                                   | 2.5                          | PLL analog power supply                                                                                     |

| VCCD_PLL                                   | 1.2                          | PLL digital power supply                                                                                    |

| VCCIO (2)                                  | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | I/O banks power supply                                                                                      |

| VCC_CLKIN (3), (4)                         | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | Differential clock input pins power supply                                                                  |

| VCCH_GXB                                   | 2.5                          | Transceiver output (TX) buffer power supply                                                                 |

| VCCA_GXB 2.5                               |                              | Transceiver physical medium attachment (PMA) and auxiliary power supply                                     |

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Chapter Revision Dates                          | vii    |

|-------------------------------------------------|--------|

| Additional Information                          |        |

| How to Contact Altera                           |        |

| Typographic Conventions                         | Info–1 |

| Section I. Transceivers                         |        |

|                                                 |        |

| Chapter 1. Cyclone IV Transceivers Architecture | 1.0    |

| Transceiver Architecture                        |        |

| Architectural Overview                          |        |

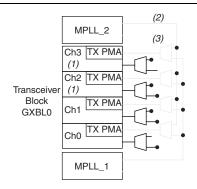

| Transmitter Channel Datapath                    |        |

| TX Phase Compensation FIFO      Byte Serializer |        |

| 8B/10B Encoder                                  |        |

| Miscellaneous Transmitter PCS Features          |        |

| Serializer                                      |        |

| Transmitter Output Buffer                       |        |

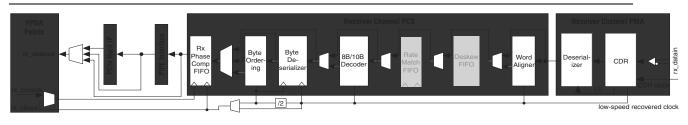

| Receiver Channel Datapath                       |        |

| Receiver Input Buffer                           |        |

| Clock Data Recovery                             |        |

| Automatic Lock Mode                             |        |

| Manual Lock Mode                                |        |

| Deserializer                                    |        |

| Word Aligner                                    |        |

| Deskew FIFO                                     |        |

| Rate Match FIFO                                 |        |

| 8B/10B Decoder                                  |        |

| Byte Deserializer                               |        |

| Byte Ordering                                   | 1–24   |

| RX Phase Compensation FIFO                      | 1–25   |

| Miscellaneous Receiver PCS Feature              |        |

| Transceiver Clocking Architecture               |        |

| Input Reference Clocking                        |        |

| Transceiver Channel Datapath Clocking           |        |

| Non-Bonded Channel Configuration                |        |

| Bonded Channel Configuration                    |        |

| FPGA Fabric-Transceiver Interface Clocking      |        |

| Calibration Block                               |        |

| PCI-Express Hard IP Block                       |        |

| Transceiver Functional Modes                    |        |

| Basic Mode                                      |        |

| Rate Match FIFO Operation in Basic Mode         |        |

| Additional Options in Basic Mode                |        |

| PCI Express (PIPE) Mode                         |        |

| PIPE Interface                                  |        |

| Receiver Detection Circuitry                    |        |

| Electrical Idle Control                         |        |

## **Word Aligner**

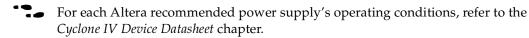

Figure 1–16 shows the word aligner block diagram. The word aligner receives parallel data from the deserializer and restores the word boundary based on a pre-defined alignment pattern that must be received during link synchronization. The word aligner supports three operational modes as listed in Table 1–3.

### Table 1-3. Word Aligner Modes

| Modes                                      | PMA-PCS Interface Widths | Allowed Word Alignment<br>Pattern Lengths |

|--------------------------------------------|--------------------------|-------------------------------------------|

| Manual Alignment                           | 8-bit                    | 16 bits                                   |

| Maruai Aigiment                            | 10-bit                   | 7 or 10 bits                              |

| Dit Clip                                   | 8-bit                    | 16 bits                                   |

| Bit-Slip                                   | 10-bit                   | 7 or 10 bits                              |

| Automatic Synchronization State<br>Machine | 10-bit                   | 7 or 10 bits                              |

### **Manual Alignment Mode**

In manual alignment mode, the rx\_enapatternalign port controls the word aligner with either an 8- or 10-bit data width setting.

The 8-bit word aligner is edge-sensitive to the rx\_enapatternalign signal. A rising edge on rx\_enapatternalign signal after deassertion of the rx\_digitalreset signal triggers the word aligner to look for the word alignment pattern in the received data stream. It updates the word boundary if it finds the word alignment pattern in a new word boundary. Any word alignment pattern received thereafter in a different word boundary causes the word aligner to re-align to the new word boundary only if there is a rising edge in the rx enapatternalign signal.

The 10-bit word aligner is level-sensitive to the rx\_enapatternalign signal. The word aligner looks for the programmed 7-bit or 10-bit word alignment pattern or its complement in the received data stream, if the rx\_enapatternalign signal is held high. It updates the word boundary if it finds the word alignment pattern in a new word boundary. If the rx\_enapatternalign signal is deasserted, the word alignment pattern maintains the current word boundary even when it receives the word alignment pattern in a new word boundary.

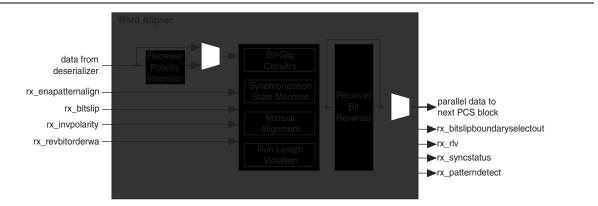

# **Transceiver Clocking Architecture**

The multipurpose PLLs and general-purpose PLLs located on the left side of the device generate the clocks required for the transceiver operation. The following sections describe the Cyclone IV GX transceiver clocking architecture:

- "Input Reference Clocking" on page 1–27

- "Transceiver Channel Datapath Clocking" on page 1–29

- "FPGA Fabric-Transceiver Interface Clocking" on page 1–43

Figure 1–31 and Figure 1–32 show the high- and low-speed clock distribution for transceivers in F324 and smaller packages, and in F484 and larger packages in non-bonded channel configuration.

# Figure 1–31. Clock Distribution in Non-Bonded Channel Configuration for Transceivers in F324 and Smaller Packages

### Notes to Figure 1-31:

- (1) Transceiver channels 2 and 3 are not available for devices in F169 and smaller packages.

- (2) High-speed clock.

- (3) Low-speed clock.

When the byte serializer is enabled, the low-speed clock frequency is halved before feeding into the read clock of TX phase compensation FIFO. The low-speed clock is available in the FPGA fabric as tx\_clkout port, which can be used in the FPGA fabric to send transmitter data and control signals.

Figure 1-33. Transmitter Only Datapath Clocking in Non-Bonded Channel Configuration

Figure 1–34 shows the datapath clocking in receiver only operation. In this mode, the receiver PCS supports configuration without the rate match FIFO. The CDR unit in the channel recovers the clock from the received serial data and generates the high-speed recovered clock for the deserializer, and low-speed recovered clock for forwarding to the receiver PCS. The low-speed recovered clock feeds to the following blocks in the receiver PCS:

- word aligner

- 8B/10B decoder

- write clock of byte deserializer

- byte ordering

- write clock of RX phase compensation FIFO

When the byte deserializer is enabled, the low-speed recovered clock frequency is halved before feeding into the write clock of the RX phase compensation FIFO. The low-speed recovered clock is available in the FPGA fabric as rx\_clkout port, which can be used in the FPGA fabric to capture receiver data and status signals.

Figure 1-34. Receiver Only Datapath Clocking without Rate Match FIFO in Non-Bonded Channel Configuration

Note to Figure 1-34:

(1) High-speed recovered clock.

When the transceiver is configured for transmitter and receiver operation in non-bonded channel configuration, the receiver PCS supports configuration with and without the rate match FIFO. The difference is only at the receiver datapath clocking. The transmitter datapath clocking is identical to transmitter only operation mode as shown in Figure 1–33.

Configuring the hard IP module requires using the PCI Express Compiler. When configuring the transceiver for PCIe implementation with hard IP module, the byte serializer and deserializer are not enabled, providing an 8-bit transceiver-PIPE-hard IP data interface width running at 250 MHz clock frequency.

**To** For more information about PCIe implementation with hard IP module, refer to the *PCI Express Compiler User Guide*.

Figure 1–49 shows the transceiver configuration in PIPE mode.

|                                                         | · · · · · · · · · · · · · · · · · · ·               |

|---------------------------------------------------------|-----------------------------------------------------|

| Functional Mode                                         | PCI Express (PIPE)                                  |

| Channel Bonding                                         | ×1, ×2, ×4                                          |

| Low-Latency PCS                                         | Disabled                                            |

| Word Aligner (Pattern Length)                           | Automatic Synchronization<br>State Machine (10-Bit) |

| 8B/10B Encoder/Decoder                                  | Enabled                                             |

| Rate Match FIFO                                         | Enabled                                             |

| Byte SERDES                                             | Enabled                                             |

| Data Rate (Gbps)                                        | 2.5                                                 |

| Byte Ordering                                           | Disabled                                            |

| FPGA Fabric-to-Transceiver<br>Interface Width           | 16-Bit                                              |

| FPGA Fabric-to-Transceiver<br>Interface Frequency (MHz) | 125                                                 |

Figure 1–49. Transceiver Configuration in PIPE Mode

When configuring the transceiver into PIPE mode using ALTGX megafunction for PCIe implementation, the PHY-MAC, data link and transaction layers must be implemented in user logics. The PCIe hard IP block is bypassed in this configuration.

- The busy signal remains low for the first reconfig\_clk clock cycle. It then gets asserted from the second reconfig\_clk clock cycle. Subsequent deassertion of the busy signal indicates the completion of the offset cancellation process. This busy signal is required in transceiver reset sequences except for transmitter only channel configurations. Refer to the reset sequences shown in Figure 2–2 and the associated references listed in the notes for the figure.

- Altera strongly recommends adhering to these reset sequences for proper operation of the Cyclone IV GX transceiver.

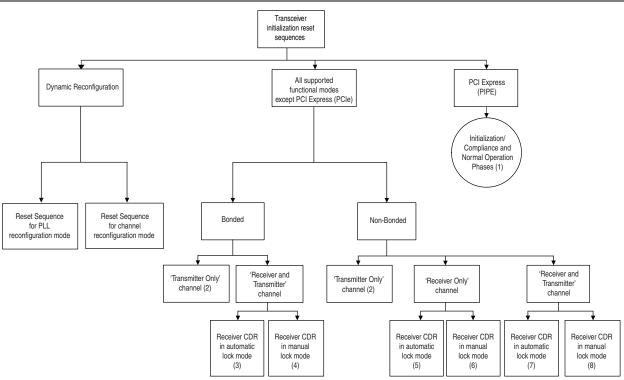

Figure 2–2 shows the transceiver reset sequences for Cyclone IV GX devices.

### Notes to Figure 2-2:

- (1) Refer to the Timing Diagram in Figure 2-10.

- (2) Refer to the Timing Diagram in Figure 2–3.

- (3) Refer to the Timing Diagram in Figure 2–4.

- (4) Refer to the Timing Diagram in Figure 2–5.

- (5) Refer to the Timing Diagram in Figure 2–6.

- (6) Refer to the Timing Diagram in Figure 2–7.

- (7) Refer to the Timing Diagram in Figure 2–8.

- (8) Refer to the Timing Diagram in Figure 2–9.

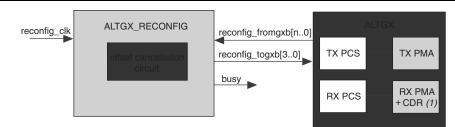

The **Offset cancellation for Receiver channels** option is automatically enabled in both the ALTGX and ALTGX\_RECONFIG MegaWizard Plug-In Managers for **Receiver and Transmitter** and **Receiver only** configurations. It is not available for **Transmitter only** configurations. For **Receiver and Transmitter** and **Receiver only** configurations, you must connect the necessary interface signals between the ALTGX\_RECONFIG and ALTGX (with receiver channels) instances.

Offset cancellation is automatically executed once every time the device is powered on. The control logic for offset cancellation is integrated into the dynamic reconfiguration controller. You must connect the ALTGX\_RECONFIG instance to the ALTGX instances (with receiver channels) in your design. You must connect the reconfig\_fromgxb, reconfig\_togxb, and necessary clock signals to both the ALTGX\_RECONFIG and ALTGX (with receiver channels) instances.

When the device powers up, the dynamic reconfiguration controller initiates offset cancellation on the receiver channel by disconnecting the receiver input pins from the receiver data path. Subsequently, the offset cancellation process goes through different states and culminates in the offset cancellation of the receiver buffer.

Offset cancellation process only occurs one time after power up and does not occur when subsequent reconfig\_reset is asserted. If you assert reconfig\_reset after the offset cancellation process is completed, the offset cancellation process will not run again.

If you assert reconfig\_reset upon power up; offset cancellation will not begin until reconfig\_reset is deasserted. If you assert reconfig\_reset after power up but before offset cancellation process is completed; offset cancellation will not complete and restart only when reconfig\_reset is deasserted.

Figure 3–2 shows the connection for offset cancellation mode.

### Figure 3–2. ALTGX and ALTGX\_RECONFIG Connection for the Offset Cancellation Process

### Note to Figure 3-2:

(1) This block is active during the offset cancellation process.

- The dynamic reconfiguration controller sends and receives data to the transceiver channel through the reconfig\_togxb and reconfig\_fromgxb signals.

- The gxb\_powerdown signal must not be asserted during the offset cancellation sequence.

The following are the channel reconfiguration mode options:

- Channel interface reconfiguration

- Data rate division at receiver channel

### **Channel Interface Reconfiguration Mode**

Enable this option if the reconfiguration of the transceiver channel involves the following changes:

- The reconfigured channel has a changed FPGA fabric-Transceiver channel interface data width

- The reconfigured channel has changed input control signals and output status signals

- The reconfigured channel has enabled and disabled the static PCS blocks of the transceiver channel

The following are the new input signals available when you enable this option:

- tx\_datainfull—the width of this input signal depends on the number of channels you set up in the ALTGX MegaWizard Plug-In Manager. It is 22 bits wide per channel. This signal is available only for Transmitter only and Receiver and Transmitter configurations. This port replaces the existing tx\_datain port.

- rx\_dataoutfull—the width of this output signal depends on the number of channels you set up in the ALTGX MegaWizard Plug-In Manager. It is 32 bits wide per channel. This signal is available only for **Receiver only** and **Receiver and Transmitter** configurations. This port replaces the existing rx\_dataout port.

The Quartus II software has legality checks for the connectivity of tx\_datainfull and rx\_dataoutfull and the various control and status signals you enable in the **Clocking/Interface** screen. For example, the Quartus II software allows you to select and connect the pipestatus and powerdn signals. It assumes that you are planning to switch to and from PCI Express (PIPE) functional mode.

Table 1–29 lists the active configuration mode specifications for Cyclone IV devices.

| Programming Mode                    | DCLK Range | Typical DCLK | Unit |

|-------------------------------------|------------|--------------|------|

| Active Parallel (AP) <sup>(1)</sup> | 20 to 40   | 33           | MHz  |

| Active Serial (AS)                  | 20 to 40   | 33           | MHz  |

Table 1–29. Active Configuration Mode Specifications for Cyclone IV Devices

#### Note to Table 1-29:

(1) AP configuration mode is only supported for Cyclone IV E devices.

Table 1-30 lists the JTAG timing parameters and values for Cyclone IV devices.

Table 1–30. JTAG Timing Parameters for Cyclone IV Devices (1)

| Symbol                | Parameter                                                    | Min | Max | Unit |

|-----------------------|--------------------------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>      | TCK clock period                                             | 40  | —   | ns   |

| t <sub>JCH</sub>      | TCK clock high time                                          | 19  | _   | ns   |

| t <sub>JCL</sub>      | TCK clock low time                                           | 19  | _   | ns   |

| t <sub>JPSU_TDI</sub> | JTAG port setup time for TDI                                 | 1   | _   | ns   |

| t <sub>JPSU_TMS</sub> | JTAG port setup time for TMS                                 | 3   | _   | ns   |

| t <sub>JPH</sub>      | JTAG port hold time                                          | 10  | _   | ns   |

| t <sub>JPCO</sub>     | JTAG port clock to output <sup>(2), (3)</sup>                | —   | 15  | ns   |

| t <sub>JPZX</sub>     | JTAG port high impedance to valid output <sup>(2), (3)</sup> | —   | 15  | ns   |

| t <sub>JPXZ</sub>     | JTAG port valid output to high impedance $(2)$ , $(3)$       | —   | 15  | ns   |

| t <sub>JSSU</sub>     | Capture register setup time                                  | 5   | _   | ns   |

| t <sub>JSH</sub>      | Capture register hold time                                   | 10  | _   | ns   |

| t <sub>JSC0</sub>     | Update register clock to output                              | —   | 25  | ns   |

| t <sub>JSZX</sub>     | Update register high impedance to valid output               | _   | 25  | ns   |

| t <sub>JSXZ</sub>     | Update register valid output to high impedance               | —   | 25  | ns   |

#### Notes to Table 1-30:

(1) For more information about JTAG waveforms, refer to "JTAG Waveform" in "Glossary" on page 1-37.

- (2) The specification is shown for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 16 ns.

- (3) For EP4CGX22, EP4CGX30 (F324 and smaller package), EP4CGX110, and EP4CGX150 devices, the output time specification for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins is 16 ns. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 18 ns.

### **Periphery Performance**

This section describes periphery performance, including high-speed I/O and external memory interface.

I/O performance supports several system interfaces, such as the high-speed I/O interface, external memory interface, and the PCI/PCI-X bus interface. I/Os using the SSTL-18 Class I termination standard can achieve up to the stated DDR2 SDRAM interfacing speeds. I/Os using general-purpose I/O standards such as 3.3-, 3.0-, 2.5-, 1.8-, or 1.5-LVTTL/LVCMOS are capable of a typical 200 MHz interfacing frequency with a 10 pF load.

### **IOE Programmable Delay**

Table 1–40 and Table 1–41 list the IOE programmable delay for Cyclone IV E 1.0 V core voltage devices.

| Table 1-40. IOE Prog | rammable Delay on Col | umn Pins for Cyclone IV | V E 1.0 V Core Voltage | Devices <sup>(1),</sup> <sup>(2)</sup> |

|----------------------|-----------------------|-------------------------|------------------------|----------------------------------------|

|----------------------|-----------------------|-------------------------|------------------------|----------------------------------------|

| Parameter                                                             | Paths Affected                 | Number<br>of<br>Setting | Min<br>Offset | Max Offset  |       |             |       |       |      |

|-----------------------------------------------------------------------|--------------------------------|-------------------------|---------------|-------------|-------|-------------|-------|-------|------|

|                                                                       |                                |                         |               | Fast Corner |       | Slow Corner |       |       | Unit |

|                                                                       |                                |                         |               | C8L         | 18L   | C8L         | C9L   | 18L   |      |

| Input delay from pin to<br>internal cells                             | Pad to I/O<br>dataout to core  | 7                       | 0             | 2.054       | 1.924 | 3.387       | 4.017 | 3.411 | ns   |

| Input delay from pin to<br>input register                             | Pad to I/O input register      | 8                       | 0             | 2.010       | 1.875 | 3.341       | 4.252 | 3.367 | ns   |

| Delay from output register to output pin                              | I/O output<br>register to pad  | 2                       | 0             | 0.641       | 0.631 | 1.111       | 1.377 | 1.124 | ns   |

| Input delay from<br>dual-purpose clock pin to<br>fan-out destinations | Pad to global<br>clock network | 12                      | 0             | 0.971       | 0.931 | 1.684       | 2.298 | 1.684 | ns   |

Notes to Table 1-40:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

| Parameter                                                             | Paths Affected                 | Number<br>of<br>Setting | Min<br>Offset | Max Offset  |       |             |       |       |      |

|-----------------------------------------------------------------------|--------------------------------|-------------------------|---------------|-------------|-------|-------------|-------|-------|------|

|                                                                       |                                |                         |               | Fast Corner |       | Slow Corner |       |       | Unit |

|                                                                       |                                |                         |               | C8L         | 18L   | C8L         | C9L   | 18L   |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to core  | 7                       | 0             | 2.057       | 1.921 | 3.389       | 4.146 | 3.412 | ns   |

| Input delay from pin to<br>input register                             | Pad to I/O input register      | 8                       | 0             | 2.059       | 1.919 | 3.420       | 4.374 | 3.441 | ns   |

| Delay from output register to output pin                              | I/O output<br>register to pad  | 2                       | 0             | 0.670       | 0.623 | 1.160       | 1.420 | 1.168 | ns   |

| Input delay from<br>dual-purpose clock pin to<br>fan-out destinations | Pad to global<br>clock network | 12                      | 0             | 0.960       | 0.919 | 1.656       | 2.258 | 1.656 | ns   |

Notes to Table 1-41:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.