## Intel - EP4CE55F29C8LN Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Product Status                 | Active                                                    |

|--------------------------------|-----------------------------------------------------------|

| Number of LABs/CLBs            | 3491                                                      |

| Number of Logic Elements/Cells | 55856                                                     |

| Total RAM Bits                 | 2396160                                                   |

| Number of I/O                  | 374                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 0.97V ~ 1.03V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 780-BGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce55f29c8ln |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Document Revision History**

Table 1–10 lists the revision history for this chapter.

## Table 1–10. Document Revision History

| Date          | Version | Changes                                                                                                                                        |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2016    | 2.0     | ■ Updated Table 1–4 and Table 1–5 to remove support for the N148 package.                                                                      |

| March 2016    | 2.0     | <ul> <li>Updated Figure 1–2 to remove support for the N148 package.</li> </ul>                                                                 |

| April 2014    | 1.9     | Updated "Packaging Ordering Information for the Cyclone IV E Device".                                                                          |

| May 2013      | 1.8     | Updated Table 1–3, Table 1–6 and Figure 1–3 to add new device options and packages.                                                            |

| February 2013 | 1.7     | Updated Table 1–3, Table 1–6 and Figure 1–3 to add new device options and packages.                                                            |

| October 2012  | 1.6     | Updated Table 1–3 and Table 1–4.                                                                                                               |

| November 2011 | 1.5     | <ul> <li>Updated "Cyclone IV Device Family Features" section.</li> </ul>                                                                       |

|               | 1.5     | ■ Updated Figure 1–2 and Figure 1–3.                                                                                                           |

|               |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                  |

|               |         | <ul> <li>Added Cyclone IV E new device package information.</li> </ul>                                                                         |

| December 2010 | 1.4     | ■ Updated Table 1–1, Table 1–2, Table 1–3, Table 1–5, and Table 1–6.                                                                           |

|               |         | ■ Updated Figure 1–3.                                                                                                                          |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                          |

| July 2010     | 1.3     | Updated Table 1–2 to include F484 package information.                                                                                         |

|               |         | ■ Updated Table 1–3 and Table 1–6.                                                                                                             |

| March 2010    | 1.2     | ■ Updated Figure 1–3.                                                                                                                          |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                          |

|               |         | <ul> <li>Added Cyclone IV E devices in Table 1–1, Table 1–3, and Table 1–6 for the<br/>Quartus II software version 9.1 SP1 release.</li> </ul> |

|               |         | <ul> <li>Added the "Cyclone IV Device Family Speed Grades" and "Configuration"<br/>sections.</li> </ul>                                        |

| February 2010 | 1.1     | <ul> <li>Added Figure 1–3 to include Cyclone IV E Device Packaging Ordering<br/>Information.</li> </ul>                                        |

|               |         | ■ Updated Table 1–2, Table 1–4, and Table 1–5 for Cyclone IV GX devices.                                                                       |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                          |

| November 2009 | 1.0     | Initial release.                                                                                                                               |

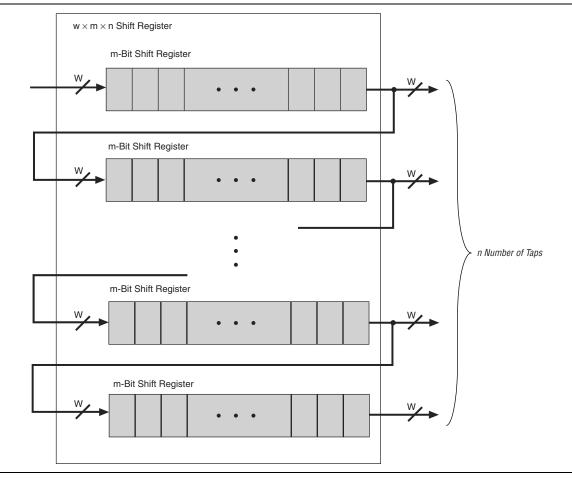

Figure 3–12 shows the Cyclone IV devices M9K memory block in shift register mode.

## **ROM Mode**

Cyclone IV devices M9K memory blocks support ROM mode. A **.mif** initializes the ROM contents of these blocks. The address lines of the ROM are registered. The outputs can be registered or unregistered. The ROM read operation is identical to the read operation in the single-port RAM configuration.

## **FIFO Buffer Mode**

Cyclone IV devices M9K memory blocks support single-clock or dual-clock FIFO buffers. Dual clock FIFO buffers are useful when transferring data from one clock domain to another clock domain. Cyclone IV devices M9K memory blocks do not support simultaneous read and write from an empty FIFO buffer.

**\*** For more information about FIFO buffers, refer to the *Single- and Dual-Clock FIFO Megafunction User Guide.*

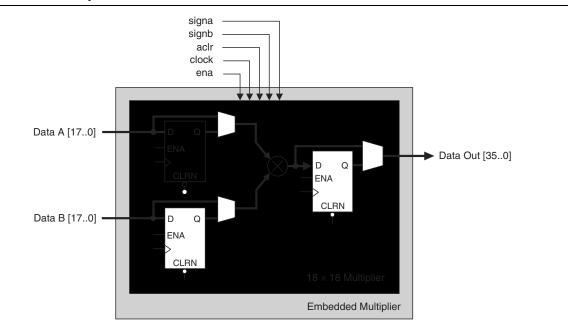

# **18-Bit Multipliers**

You can configure each embedded multiplier to support a single  $18 \times 18$  multiplier for input widths of 10 to 18 bits.

Figure 4–3 shows the embedded multiplier configured to support an 18-bit multiplier.

Figure 4–3. 18-Bit Multiplier Mode

All 18-bit multiplier inputs and results are independently sent through registers. The multiplier inputs can accept signed integers, unsigned integers, or a combination of both. Also, you can dynamically change the signa and signb signals and send these signals through dedicated input registers.

# 5. Clock Networks and PLLs in Cyclone IV Devices

This chapter describes the hierarchical clock networks and phase-locked loops (PLLs) with advanced features in the Cyclone<sup>®</sup> IV device family. It includes details about the ability to reconfigure the PLL counter clock frequency and phase shift in real time, allowing you to sweep PLL output frequencies and dynamically adjust the output clock phase shift.

The Quartus<sup>®</sup> II software enables the PLLs and their features without external devices.

This chapter contains the following sections:

- "Clock Networks" on page 5–1

- "PLLs in Cyclone IV Devices" on page 5–18

- "Cyclone IV PLL Hardware Overview" on page 5–20

- "Clock Feedback Modes" on page 5–23

- "Hardware Features" on page 5–26

- "Programmable Bandwidth" on page 5–32

- "Phase Shift Implementation" on page 5–32

- "PLL Cascading" on page 5–33

- "PLL Reconfiguration" on page 5–34

- "Spread-Spectrum Clocking" on page 5–41

- "PLL Specifications" on page 5–41

# **Clock Networks**

The Cyclone IV GX device provides up to 12 dedicated clock pins (CLK[15..4]) that can drive the global clocks (GCLKs). Cyclone IV GX devices support four dedicated clock pins on each side of the device except the left side. These clock pins can drive up to 30 GCLKs.

The Cyclone IV E device provides up to 15 dedicated clock pins (CLK[15..1]) that can drive up to 20 GCLKs. Cyclone IV E devices support three dedicated clock pins on the left side and four dedicated clock pins on the top, right, and bottom sides of the device except EP4CE6 and EP4CE10 devices. EP4CE6 and EP4CE10 devices only support three dedicated clock pins on the left side and four dedicated clock pins on the right side of the device.

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. For more information about the number of GCLK networks in each device density, refer to the *Cyclone IV FPGA Device Family Overview* chapter.

# **GCLK Network**

GCLKs drive throughout the entire device, feeding all device quadrants. All resources in the device (I/O elements, logic array blocks (LABs), dedicated multiplier blocks, and M9K memory blocks) can use GCLKs as clock sources. Use these clock network resources for control signals, such as clock enables and clears fed by an external pin. Internal logic can also drive GCLKs for internally generated GCLKs and asynchronous clears, clock enables, or other control signals with high fan-out.

Table 5–1, Table 5–2 on page 5–4, and Table 5–3 on page 5–7 list the connectivity of the clock sources to the GCLK networks.

Table 5-1. GCLK Network Connections for EP4CGX15, EP4CGX22, and EP4CGX30<sup>(1), (2)</sup> (Part 1 of 2)

| GCLK Network Clock            |              |              |              |              |              |              |              |              | GC           | LK N         | etwo         | rks          |              |              |              |              |              |              |              |              |

|-------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Sources                       | 0            | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           |

| CLK4/DIFFCLK_2n               |              | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            |

| CLK5/DIFFCLK_2p               | _            | —            |              | —            |              | —            | $\checkmark$ | $\checkmark$ | —            | —            |              |              | —            |              |              |              |              | —            |              | —            |

| CLK6/DIFFCLK_3n               |              | —            | —            | —            |              | —            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              | —            | —            |              | —            |              |              | —            |              | —            |

| CLK7/DIFFCLK_3p               |              | —            |              | —            |              | $\checkmark$ |              |              | $\checkmark$ |              |              |              | —            | _            |              | _            |              |              | —            | —            |

| CLK8/DIFFCLK_5n               |              | —            |              | _            |              |              |              |              |              |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              |              |              |              | —            |

| CLK9/DIFFCLK_5p               | —            | —            |              | —            | —            | —            |              | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | _            |              | _            | —            | —            | —            | —            |

| CLK10/DIFFCLK_4n/RE<br>FCLK1n | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | ~            | _            | ~            | ~            | _            | _            | _            | _            | —            |

| CLK11/DIFFCLK_4p/RE<br>FCLK1p | _            | _            | _            |              |              | _            |              |              | _            | _            | ~            |              | _            | ~            |              | _            |              | _            |              | —            |

| CLK12/DIFFCLK_7p/RE<br>FCLK0p | _            |              | _            |              | _            | _            | _            | _            | _            | _            | _            | _            | _            |              | _            | $\checkmark$ | _            | ~            | _            | ~            |

| CLK13/DIFFCLK_7n/RE<br>FCLK0n | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            |              | _            |              | ~            | ~            | _            | —            |

| CLK14/DIFFCLK_6p              |              | —            |              | —            |              | _            |              |              |              |              |              |              | —            | _            |              | _            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| CLK15/DIFFCLK_6n              |              | —            | —            | —            | _            | —            | —            |              | —            |              |              | —            | —            | _            | —            | $\checkmark$ | _            | —            | $\checkmark$ | —            |

| PLL_1_C0                      | $\checkmark$ | _            |              | $\checkmark$ |              |              |              |              |              |              |              |              |              |              |              | >            |              |              | $\checkmark$ | —            |

| PLL_1_C1                      |              | <b>~</b>     | _            |              | >            | _            |              |              | _            | _            | _            |              | _            |              |              |              | >            | _            |              | $\checkmark$ |

| PLL_1_C2                      | $\checkmark$ | —            | $\checkmark$ | —            | _            | —            |              |              | —            | —            | —            |              | —            |              |              | >            | _            | $\checkmark$ | _            | —            |

| PLL_1_C3                      |              | <b>~</b>     | _            | $\checkmark$ |              | _            |              |              | _            | _            | _            |              | _            |              |              |              | >            | _            | >            | —            |

| PLL_1_C4                      |              | _            | $\checkmark$ |              | >            |              |              |              | _            |              |              |              |              |              |              |              |              | $\checkmark$ |              | $\checkmark$ |

| PLL_2_C0                      | $\checkmark$ | —            |              | $\checkmark$ |              |              |              |              |              |              | $\checkmark$ |              |              | $\checkmark$ |              | _            |              |              | —            | —            |

| PLL_2_C1                      |              | $\checkmark$ |              | —            | $\checkmark$ | —            |              |              | —            |              |              | $\checkmark$ | —            | _            | $\checkmark$ | _            | _            | —            | —            | —            |

| PLL_2_C2                      | $\checkmark$ | —            | $\checkmark$ |              |              |              |              |              |              |              | $\checkmark$ |              | $\checkmark$ | _            |              | _            |              |              | —            | —            |

| PLL_2_C3                      | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | _            | >            | —            | —            | —            | —            | —            | —            |

| PLL_2_C4                      | _            | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            |              | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            |

| PLL_3_C0                      | —            | —            | —            | —            | _            | $\checkmark$ | —            | —            | ~            | —            | —            | —            | —            | _            | —            | >            | _            | —            | $\checkmark$ | —            |

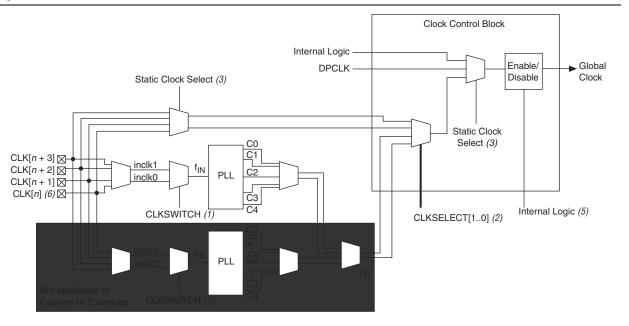

Figure 5–1 shows the clock control block.

### Figure 5–1. Clock Control Block

#### Notes to Figure 5-1:

- (1) The clkswitch signal can either be set through the configuration file or dynamically set when using the manual PLL switchover feature. The output of the multiplexer is the input clock  $(f_{IN})$  for the PLL.

- (2) The clkselect[1..0] signals are fed by internal logic and are used to dynamically select the clock source for the GCLK when the device is in user mode.

- (3) The static clock select signals are set in the configuration file. Therefore, dynamic control when the device is in user mode is not feasible.

- (4) Two out of four PLL clock outputs are selected from adjacent PLLs to drive into the clock control block.

- (5) You can use internal logic to enable or disable the GCLK in user mode.

- (6) CLK [12] is not available on the left side of Cyclone IV E devices.

Each PLL generates five clock outputs through the c[4..0] counters. Two of these clocks can drive the GCLK through a clock control block, as shown in Figure 5–1.

For more information about how to use the clock control block in the Quartus II software, refer to the *ALTCLKCTRL Megafunction User Guide*.

# Differential SSTL I/O Standard Support in Cyclone IV Devices

The differential SSTL I/O standard is a memory-bus standard used for applications such as high-speed DDR SDRAM interfaces. Cyclone IV devices support differential SSTL-2 and SSTL-18 I/O standards. The differential SSTL output standard is only supported at PLL#\_CLKOUT pins using two single-ended SSTL output buffers (PLL#\_CLKOUTp and PLL#\_CLKOUTn), with the second output programmed to have opposite polarity. The differential SSTL input standard is supported on the GCLK pins only, treating differential inputs as two single-ended SSTL and only decoding one of them.

The differential SSTL I/O standard requires two differential inputs with an external reference voltage (VREF) as well as an external termination voltage (VTT) of  $0.5 \times V_{CCIO}$  to which termination resistors are connected.

Figure 6–8 on page 6–15 shows the differential SSTL Class I and Class II interface.

# **Differential HSTL I/O Standard Support in Cyclone IV Devices**

The differential HSTL I/O standard is used for the applications designed to operate in 0 V to 1.2 V, 0 V to 1.5 V, or 0 V to 1.8 V HSTL logic switching range. Cyclone IV devices support differential HSTL-18, HSTL-15, and HSTL-12 I/O standards. The differential HSTL input standard is available on GCLK pins only, treating the differential inputs as two single-ended HSTL and only decoding one of them. The differential HSTL output standard is only supported at the PLL#\_CLKOUT pins using two single-ended HSTL output buffers (PLL#\_CLKOUT*p* and PLL#\_CLKOUT*n*), with the second output programmed to have opposite polarity.

The differential HSTL I/O standard requires two differential inputs with an external reference voltage (VREF), as well as an external termination voltage (VTT) of  $0.5 \times V_{CCIO}$  to which termination resistors are connected.

**•** For differential HSTL signaling characteristics, refer to "Differential I/O Standard Termination" on page 6–15 and the *Cyclone IV Device Datasheet* chapter.

Figure 6–7 on page 6–15 shows the differential HSTL Class I and Class II interface.

# **True Differential Output Buffer Feature**

Cyclone IV devices true differential transmitters offer programmable pre-emphasis—you can turn it on or off. The default setting is on.

## **Programmable Pre-Emphasis**

The programmable pre-emphasis boosts the high frequencies of the output signal to compensate the frequency-dependant attenuation of the transmission line to maximize the data eye opening at the far-end receiver. Without pre-emphasis, the output current is limited by the  $V_{OD}$  specification and the output impedance of the transmitter. At high frequency, the slew rate may not be fast enough to reach full  $V_{OD}$

# 7. External Memory Interfaces in Cyclone IV Devices

This chapter describes the memory interface pin support and the external memory interface features of Cyclone<sup>®</sup> IV devices.

In addition to an abundant supply of on-chip memory, Cyclone IV devices can easily interface with a broad range of external memory devices, including DDR2 SDRAM, DDR SDRAM, and QDR II SRAM. External memory devices are an important system component of a wide range of image processing, storage, communications, and general embedded applications.

Altera recommends that you construct all DDR2 or DDR SDRAM external memory interfaces using the Altera<sup>®</sup> ALTMEMPHY megafunction. You can implement the controller function using the Altera DDR2 or DDR SDRAM memory controllers, third-party controllers, or a custom controller for unique application needs. Cyclone IV devices support QDR II interfaces electrically, but Altera does not supply controller or physical layer (PHY) megafunctions for QDR II interfaces.

This chapter includes the following sections:

- "Cyclone IV Devices Memory Interfaces Pin Support" on page 7–2

- "Cyclone IV Devices Memory Interfaces Features" on page 7–12

- For more information about supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to the *External Memory Interface Handbook*.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

four devices. During the first configuration cycle, the master device reads its configuration data from the serial configuration device while holding nCEO high. After completing its configuration cycle, the master device drives nCE low and sends the second copy of the configuration data to all three slave devices, configuring them simultaneously.

The advantage of the setup in Figure 8–4 is that you can have a different **.sof** for the master device. However, all the slave devices must be configured with the same **.sof**. You can either compress or uncompress the **.sof** in this configuration method.

You can still use this method if the master and slave devices use the same **.sof**.

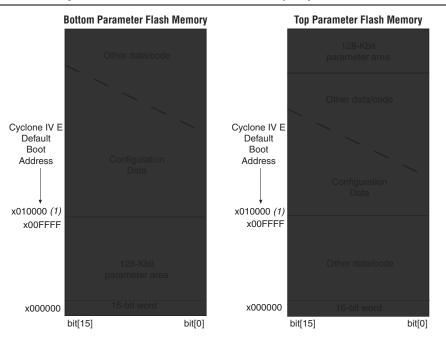

The default configuration boot address allows the system to use special parameter blocks in the flash memory map. Parameter blocks are at the top or bottom of the memory map. Figure 8–12 shows the configuration boot address in the AP configuration scheme. You can change the default configuration default boot address 0×010000 to any desired address using the APFC\_BOOT\_ADDR\_JTAG instruction. For more information about the APFC\_BOOT\_ADDR\_JTAG instruction, refer to "JTAG Instructions" on page 8–57.

#### Note to Figure 8-12:

(1) The default configuration boot address is x010000 when represented in 16-bit word addressing.

# **PS Configuration**

You can perform PS configuration on Cyclone IV devices with an external intelligent host, such as a MAX<sup>®</sup> II device, microprocessor with flash memory, or a download cable. In the PS scheme, an external host controls the configuration. Configuration data is clocked into the target Cyclone IV device through DATA[0] at each rising edge of DCLK.

If your system already contains a common flash interface (CFI) flash memory, you can use it for Cyclone IV device configuration storage as well. The MAX II PFL feature provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control the configuration from the flash memory device to the Cyclone IV device.

**Tor** For more information about the PFL, refer to *AN* 386: Using the Parallel Flash Loader with the Quartus II Software.

Cyclone IV devices do not support enhanced configuration devices for PS configuration.

| Chapter Revision Dates                          | vii    |

|-------------------------------------------------|--------|

| Additional Information                          |        |

| How to Contact Altera                           |        |

| Typographic Conventions                         | Info–1 |

| Section I. Transceivers                         |        |

|                                                 |        |

| Chapter 1. Cyclone IV Transceivers Architecture | 1.0    |

| Transceiver Architecture                        |        |

| Architectural Overview                          |        |

| Transmitter Channel Datapath                    |        |

| TX Phase Compensation FIFO      Byte Serializer |        |

| 8B/10B Encoder                                  |        |

| Miscellaneous Transmitter PCS Features          |        |

| Serializer                                      |        |

| Transmitter Output Buffer                       |        |

| Receiver Channel Datapath                       |        |

| Receiver Input Buffer                           |        |

| Clock Data Recovery                             |        |

| Automatic Lock Mode                             |        |

| Manual Lock Mode                                |        |

| Deserializer                                    |        |

| Word Aligner                                    |        |

| Deskew FIFO                                     |        |

| Rate Match FIFO                                 |        |

| 8B/10B Decoder                                  |        |

| Byte Deserializer                               |        |

| Byte Ordering                                   | 1–24   |

| RX Phase Compensation FIFO                      | 1–25   |

| Miscellaneous Receiver PCS Feature              |        |

| Transceiver Clocking Architecture               |        |

| Input Reference Clocking                        |        |

| Transceiver Channel Datapath Clocking           |        |

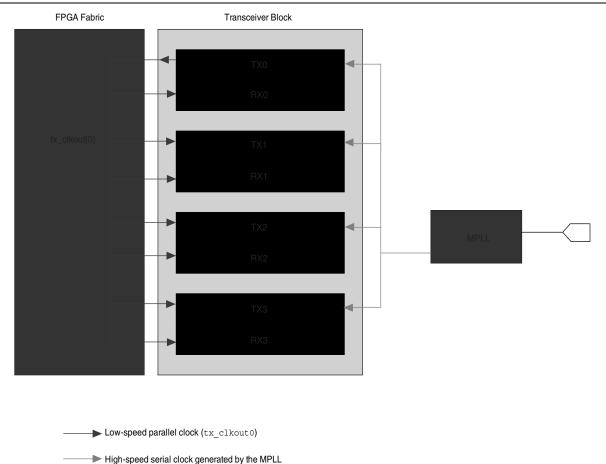

| Non-Bonded Channel Configuration                |        |

| Bonded Channel Configuration                    |        |

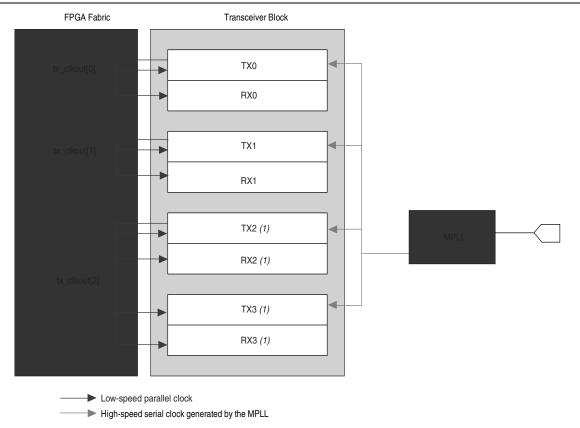

| FPGA Fabric-Transceiver Interface Clocking      |        |

| Calibration Block                               |        |

| PCI-Express Hard IP Block                       |        |

| Transceiver Functional Modes                    |        |

| Basic Mode                                      |        |

| Rate Match FIFO Operation in Basic Mode         |        |

| Additional Options in Basic Mode                |        |

| PCI Express (PIPE) Mode                         |        |

| PIPE Interface                                  |        |

| Receiver Detection Circuitry                    |        |

| Electrical Idle Control                         |        |

# **Document Revision History**

Table 1–30 lists the revision history for this chapter.

| Table 1-30. | Document | Revision   | History  |

|-------------|----------|------------|----------|

|             | Dooumont | 1101131011 | 11131019 |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|               |         | ■ Updated the GiGE row in Table 1–14.                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| February 2015 | 3.7     | <ul> <li>Updated the "GIGE Mode" section.</li> </ul>                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|               |         | <ul> <li>Updated the note in the "Clock Frequency Compensation" section.</li> </ul>                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| October 2013  | 3.6     | Updated Figure 1–15 and Table 1–4.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| May 2013      | 3.5     | Updated Table 1–27 by setting "rx_locktodata" and "rx_locktorefclk" to "Input"                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|               |         | <ul> <li>Updated the data rate for the V-by-one protocol and the F324 package support in<br/>HD-SDI in Table 1–1.</li> </ul>                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| October 2012  | 3.4     | ■ Updated note (1) to Figure 1–27.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|               |         | <ul> <li>Added latency information to Figure 1–67.</li> </ul>                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| November 2011 | 3.3     | <ul> <li>Updated "Word Aligner" and "Basic Mode" sections.</li> </ul>                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| November 2011 | 3.3     | ■ Updated Figure 1–37.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| December 2010 |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|               |         | ■ Updated Table 1–1, Table 1–5, Table 1–11, Table 1–14, Table 1–24, Table 1–25, Table 1–26, Table 1–27, Table 1–28, and Table 1–29.                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|               | 3.2     | <ul> <li>Updated "8B/10B Encoder", "Transmitter Output Buffer", "Receiver Input Buffer",<br/>"Clock Data Recovery", "Miscellaneous Transmitter PCS Features", "Miscellaneous<br/>Receiver PCS Feature", "Input Reference Clocking", "PCI Express (PIPE) Mode",<br/>"Channel Deskewing", "Lane Synchronization", "Serial Loopback", and "Self Test<br/>Modes" sections.</li> </ul> |  |  |  |  |  |  |

|               |         | ■ Added Figure 1–9, Figure 1–10, Figure 1–19, Figure 1–20, and Figure 1–43.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|               |         | ■ Updated Figure 1–53, Figure 1–55, Figure 1–59, Figure 1–60, Figure 1–69, Figure 1–70, Figure 1–71, Figure 1–72, Figure 1–73, and Figure 1–74.                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| November 2010 | 3.1     | Updated Introductory information.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|               |         | <ul> <li>Updated information for the Quartus II software version 10.0 release.</li> </ul>                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| July 2010     | 3.0     | <ul> <li>Reset control, power down, and dynamic reconfiguration information moved to<br/>new Cyclone IV Reset Control and Power Down and Cyclone IV Dynamic<br/>Reconfiguration chapters.</li> </ul>                                                                                                                                                                              |  |  |  |  |  |  |

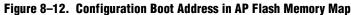

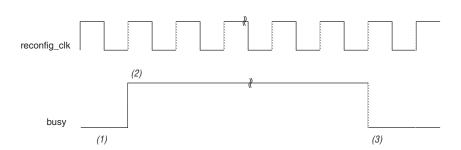

Figure 3–3 shows the timing diagram for a offset cancellation process.

### Notes to Figure 3-3:

- (1) After device power up, the busy signal remains low for the first reconfig\_clk cycle.

- (2) The busy signal then gets asserted for the second reconfig\_clk cycle, when the dynamic reconfiguration controller initiates the offset cancellation process.

- (3) The deassertion of the busy signal indicates the successful completion of the offset cancellation process.

## **Functional Simulation of the Offset Cancellation Process**

You must connect the ALTGX\_RECONFIG instances to the ALTGX instances in your design for functional simulation. Functional simulation uses a reduced timing model of the dynamic reconfiguration controller. Therefore, the duration of the offset cancellation process is 16 reconfig\_clk clock cycles for functional simulation only. The gxb\_powerdown signal must not be asserted during the offset cancellation sequence (for functional simulation and silicon).

# **Dynamic Reconfiguration Modes**

When you enable the dynamic reconfiguration feature, you can reconfigure the following portions of each transceiver channel dynamically, without powering down the other transceiver channels or the FPGA fabric of the device:

- Analog (PMA) controls reconfiguration

- Channel reconfiguration

- PLL reconfiguration

Table 3–3 lists the supported dynamic reconfiguration modes for Cyclone IV GX devices.

|                                           | Ope                 | erational Mo     | ode                                    | Qua          | l                  |                     |                      |

|-------------------------------------------|---------------------|------------------|----------------------------------------|--------------|--------------------|---------------------|----------------------|

| Dynamic Reconfiguration<br>Supported Mode | Transmitter<br>Only | Receiver<br>Only | Transmitter<br>and<br>Receiver<br>Only | ALTGX        | ALTGX_<br>Reconfig | ALTPLL_<br>Reconfig | .mif<br>Requirements |

| Offset Cancellation                       |                     | $\checkmark$     | $\checkmark$                           | $\checkmark$ | $\checkmark$       | _                   | —                    |

| Analog (PMA) Controls<br>Reconfiguration  | $\checkmark$        | ~                | ~                                      | $\checkmark$ | ~                  | _                   | _                    |

Table 3-3. Cyclone IV GX Supported Dynamic Reconfiguration Mode (Part 1 of 2)

## **PMA Control Ports Used in a Read Transaction**

- tx\_vodctrl\_out is 3 bits per channel

- tx\_preemp\_out is 5 bits per channel

- rx eqdcgain out is 2 bits per channel

- rx\_eqctrl\_out is 4 bits per channel

For example, assume the number of channels controlled by the dynamic reconfiguration controller is two, tx\_vodctrl\_out is 6 bits wide.

## Write Transaction

The value you set at the selected PMA control ports is written to all the transceiver channels connected to the ALTGX\_RECONFIG instance.

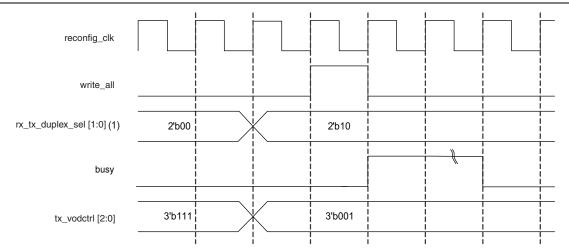

For example, assume you have enabled tx\_vodctrl in the ALTGX\_RECONFIG MegaWizard Plug-In Manager to reconfigure the V<sub>OD</sub> of the transceiver channels. To complete a write transaction to reconfigure the V<sub>OD</sub>, perform the following steps:

- 1. Before you initiate a write transaction, set the selected PMA control ports to the desired settings (for example, tx\_vodctrl = 3'b001).

- 2. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 3. Ensure that the busy signal is low before you start a write transaction.

- 4. Assert the write\_all signal for one reconfig\_clk clock cycle. This initiates the write transaction.

- 5. The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

Figure 3–6 shows the write transaction for Method 2.

## Figure 3–6. Write Transaction Waveform—Use the same control signal for all the channels Option

### Note to Figure 3-6:

(1) In this waveform example, you want to write to only the transmitter portion of the channel.

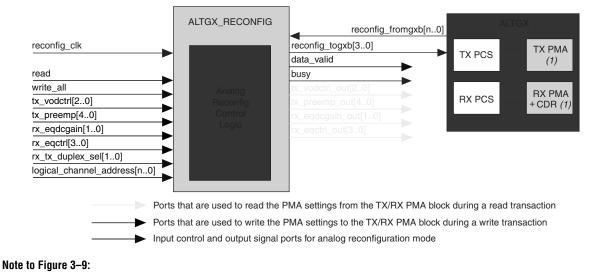

Figure 3–9 shows the connection for PMA reconfiguration mode.

(1) This block can be reconfigured in PMA reconfiguration mode.

# **Transceiver Channel Reconfiguration Mode**

You can dynamically reconfigure the transceiver channel from an existing functional mode to a different functional mode by selecting the **Channel Reconfiguration** option in ALTGX and ALTGX\_RECONFIG MegaWizards. The blocks that are reconfigured by channel reconfiguration mode are the PCS and RX PMA blocks of a transceiver channel.

For more information about reconfiguring the RX PMA blocks of the transceiver channel using channel reconfiguration mode, you can refer to "Data Rate Reconfiguration Mode Using RX Local Divider" on page 3–26.

In channel reconfiguration, only a write transaction can occur; no read transactions are allowed. You can optionally choose to trigger write\_all once by selecting the continuous write operation in the ALTGX\_RECONFIG MegaWizard Plug-In Manager. The Quartus II software then continuously writes all the words required for reconfiguration.

For channel reconfiguration, **.mif** files are required to dynamically reconfigure the transceivers channels in channel reconfiguration modes. The **.mif** carries the reconfiguration information that will be used to reconfigure the transceivers channel dynamically on-the-fly. The **.mif** contents is generated automatically when you select the **Generate GXB Reconfig MIF** option in the Quartus II software setting. For different **.mif** settings, you need to later reconfigure and recompile the ALTGX MegaWizard to generate the **.mif** based on the required reconfiguration settings.

The dynamic reconfiguration controller can optionally perform a continuos write operation or a regular write operation of the **.mif** contents in terms of word size (16-bit data) to the transceivers channel that is selected for reconfiguration.

## Figure 3–9. ALTGX and ALTGX\_RECONFIG Connection for PMA Reconfiguration Mode

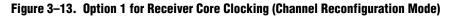

## **Option 1: Share a Single Transmitter Core Clock Between Receivers**

- Enable this option if you want tx\_clkout of the first channel (channel 0) of the transceiver block to provide the read clock to the Receive Phase Compensation FIFOs of the remaining receiver channels in the transceiver block.

- This option is typically enabled when all the channels of a transceiver block are in a Basic or Protocol configuration with rate matching enabled and are reconfigured to another Basic or Protocol configuration with rate matching enabled.

Figure 3–13 shows the sharing of channel 0's tx\_clkout between all four channels of a transceiver block.

## **Option 2: Use the Respective Channel Transmitter Core Clocks**

- Enable this option if you want the individual transmitter channel's tx\_clkout signal to provide the read clock to its respective Receive Phase Compensation FIFO.

- This option is typically enabled when all the transceiver channels have rate matching enabled with different data rates and are reconfigured to another Basic or Protocol functional mode with rate matching enabled.

Figure 3–14 shows the respective tx\_clkout of each channel clocking the respective channels of a transceiver block.

Figure 3–14. Option 2 for Receiver Core Clocking (Channel Reconfiguration Mode)

#### Note to Figure 3-14:

(1) Assuming channel 2 and 3 are running at the same data rate with rate matcher enabled and are reconfigured to another Basic or Protocol functional mode with rate matching enabled.

| Parameter              |           |     | V <sub>CCI0</sub> (V) |       |       |      |      |     |     |     |     |     |     |   |

|------------------------|-----------|-----|-----------------------|-------|-------|------|------|-----|-----|-----|-----|-----|-----|---|

|                        | Condition | 1.2 |                       | 1     | 1.5   |      | 1.8  |     | 2.5 |     | 3.0 |     | 3.3 |   |

|                        |           | Min | Max                   | Min   | Max   | Min  | Max  | Min | Max | Min | Max | Min | Max |   |

| Bus hold trip<br>point | —         | 0.3 | 0.9                   | 0.375 | 1.125 | 0.68 | 1.07 | 0.7 | 1.7 | 0.8 | 2   | 0.8 | 2   | V |

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 2 of 2)<sup>(1)</sup>

Note to Table 1-7:

(1) Bus hold trip points are based on the calculated input voltages from the JEDEC standard.

## **OCT Specifications**

Table 1–8 lists the variation of OCT without calibration across process, temperature, and voltage (PVT).

Table 1–8. Series OCT Without Calibration Specifications for Cyclone IV Devices

|                                   |                                                          | Resistance         |                                                               |      |

|-----------------------------------|----------------------------------------------------------|--------------------|---------------------------------------------------------------|------|

| Description                       | V <sub>CCI0</sub> (V)<br>3.0<br>2.5<br>1.8<br>1.5<br>1.2 | Commercial Maximum | Industrial, Extended<br>industrial, and<br>Automotive Maximum | Unit |

|                                   | 3.0                                                      | ±30                | ±40                                                           | %    |

|                                   | 2.5                                                      | ±30                | ±40                                                           | %    |

| Series OCT without<br>calibration | 1.8                                                      | ±40                | ±50                                                           | %    |

| ounoration                        | 1.5                                                      | ±50                | ±50                                                           | %    |

|                                   | 1.2                                                      | ±50                | ±50                                                           | %    |

OCT calibration is automatically performed at device power-up for OCT-enabled I/Os.

Table 1–9 lists the OCT calibration accuracy at device power-up.

| Table 1–9.             | Series OCT with Calibration at Device Power-Up Specifications for Cyclone IV |

|------------------------|------------------------------------------------------------------------------|

| Devices <sup>(1)</sup> |                                                                              |

|                       |                       | Calibratio         |                                                               |      |

|-----------------------|-----------------------|--------------------|---------------------------------------------------------------|------|

| calibration at device | V <sub>ccio</sub> (V) | Commercial Maximum | Industrial, Extended<br>industrial, and<br>Automotive Maximum | Unit |

|                       | 3.0                   | ±10                | ±10                                                           | %    |

| Series OCT with       | 2.5                   | ±10                | ±10                                                           | %    |

| calibration at device | 1.8                   | ±10                | ±10                                                           | %    |

| power-up              | 1.5                   | ±10                | ±10                                                           | %    |

|                       | 1.2                   | ±10                | ±10                                                           | %    |

### Note to Table 1-9:

(1) This specification is not applicable to EP4CGX15, EP4CGX22, and EP4CGX30 devices.

| Symbol                          | Modes   | C   | 6   | C7, | , 17 | C8, | A7  | C8L, | , 18L | C   | 9L  | Unit |

|---------------------------------|---------|-----|-----|-----|------|-----|-----|------|-------|-----|-----|------|

|                                 | INIUUC3 | Min | Max | Min | Max  | Min | Max | Min  | Max   | Min | Max | Unit |

| t <sub>DUTY</sub>               | —       | 45  | 55  | 45  | 55   | 45  | 55  | 45   | 55    | 45  | 55  | %    |

| TCCS                            | —       | _   | 200 | —   | 200  | _   | 200 | _    | 200   | _   | 200 | ps   |

| Output jitter<br>(peak to peak) | _       |     | 500 | _   | 500  | _   | 550 | _    | 600   | _   | 700 | ps   |

| t <sub>LOCK</sub> (2)           | _       |     | 1   | _   | 1    |     | 1   | _    | 1     | _   | 1   | ms   |

## Table 1–35. Emulated LVDS Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

#### Notes to Table 1-35:

(1) Cyclone IV E—emulated LVDS transmitter is supported at the output pin of all I/O Banks.

Cyclone IV GX—emulated LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                                           | Modes | C6  |       | C7, 17 |       | C8, A7 |       | C8L, 18L |     | C9L |     |      |

|--------------------------------------------------|-------|-----|-------|--------|-------|--------|-------|----------|-----|-----|-----|------|

|                                                  |       | Min | Max   | Min    | Max   | Min    | Max   | Min      | Max | Min | Max | Unit |

| f <sub>HSCLK</sub> (input<br>clock<br>frequency) | ×10   | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

|                                                  | ×8    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

|                                                  | ×7    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

|                                                  | ×4    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

|                                                  | ×2    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

|                                                  | ×1    | 10  | 437.5 | 10     | 402.5 | 10     | 402.5 | 10       | 362 | 10  | 265 | MHz  |

| HSIODR                                           | ×10   | 100 | 875   | 100    | 740   | 100    | 640   | 100      | 640 | 100 | 500 | Mbps |

|                                                  | ×8    | 80  | 875   | 80     | 740   | 80     | 640   | 80       | 640 | 80  | 500 | Mbps |

|                                                  | ×7    | 70  | 875   | 70     | 740   | 70     | 640   | 70       | 640 | 70  | 500 | Mbps |

|                                                  | ×4    | 40  | 875   | 40     | 740   | 40     | 640   | 40       | 640 | 40  | 500 | Mbps |

|                                                  | ×2    | 20  | 875   | 20     | 740   | 20     | 640   | 20       | 640 | 20  | 500 | Mbps |

|                                                  | ×1    | 10  | 437.5 | 10     | 402.5 | 10     | 402.5 | 10       | 362 | 10  | 265 | Mbps |

| SW                                               | —     | _   | 400   | _      | 400   | _      | 400   | _        | 550 | _   | 640 | ps   |

| Input jitter<br>tolerance                        | _     | _   | 500   | _      | 500   | _      | 550   | _        | 600 | _   | 700 | ps   |

| t <sub>LOCK</sub> (2)                            | —     | _   | 1     | —      | 1     | _      | 1     | —        | 1   | —   | 1   | ms   |

Table 1–36. LVDS Receiver Timing Specifications for Cyclone IV Devices (1), (3)

#### Notes to Table 1-36:

(1) Cyclone IV E—LVDS receiver is supported at all I/O Banks.

Cyclone IV GX—LVDS receiver is supported at I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

## **External Memory Interface Specifications**

The external memory interfaces for Cyclone IV devices are auto-calibrating and easy to implement.