### Intel - EP4CE55F29I8L Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 3491                                                     |

| Number of Logic Elements/Cells | 55856                                                    |

| Total RAM Bits                 | 2396160                                                  |

| Number of I/O                  | 374                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 780-BGA                                                  |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce55f29i8l |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

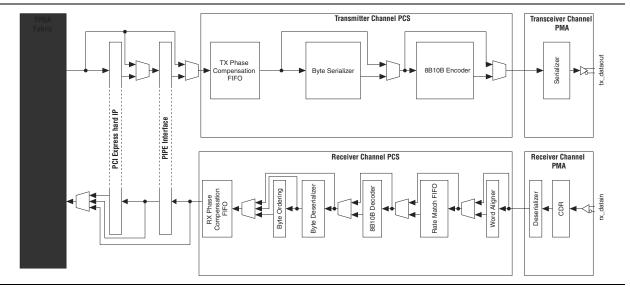

Figure 1–1 shows the structure of the Cyclone IV GX transceiver.

For more information, refer to the *Cyclone IV Transceivers Architecture* chapter.

# Hard IP for PCI Express (Cyclone IV GX Devices Only)

Cyclone IV GX devices incorporate a single hard IP block for ×1, ×2, or ×4 PCIe (PIPE) in each device. This hard IP block is a complete PCIe (PIPE) protocol solution that implements the PHY-MAC layer, Data Link Layer, and Transaction Layer functionality. The hard IP for the PCIe (PIPE) block supports root-port and end-point configurations. This pre-verified hard IP block reduces risk, design time, timing closure, and verification. You can configure the block with the Quartus II software's PCI Express Compiler, which guides you through the process step by step.

For more information, refer to the PCI Express Compiler User Guide.

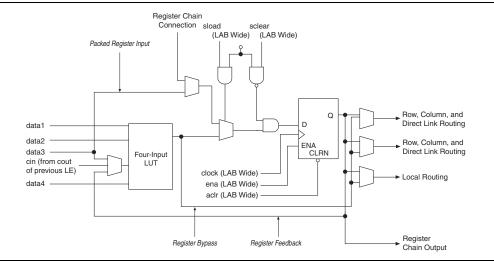

In addition to the three general routing outputs, LEs in an LAB have register chain outputs, which allows registers in the same LAB to cascade together. The register chain output allows the LUTs to be used for combinational functions and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources.

# **LE Operating Modes**

Cyclone IV LEs operate in the following modes:

- Normal mode

- Arithmetic mode

The Quartus<sup>®</sup> II software automatically chooses the appropriate mode for common functions, such as counters, adders, subtractors, and arithmetic functions, in conjunction with parameterized functions such as the library of parameterized modules (LPM) functions. You can also create special-purpose functions that specify which LE operating mode to use for optimal performance, if required.

## **Normal Mode**

Normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (Figure 2–2). The Quartus II Compiler automatically selects the carry-in (cin) or the data3 signal as one of the inputs to the LUT. LEs in normal mode support packed registers and register feedback.

Figure 2–2 shows LEs in normal mode.

## **GCLK Network Clock Source Generation**

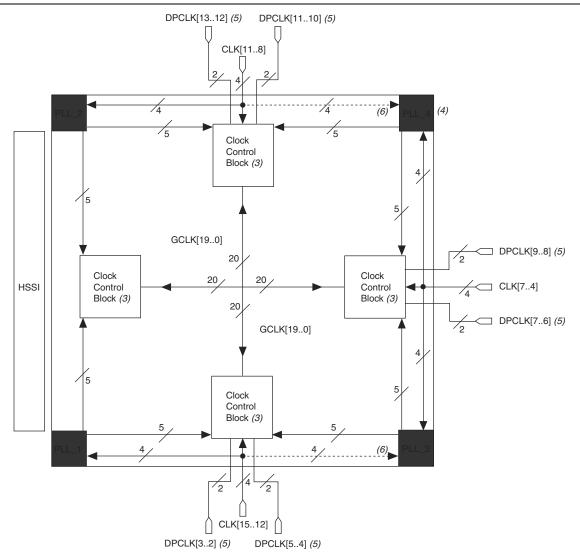

Figure 5–2, Figure 5–3, and Figure 5–4 on page 5–14 show the Cyclone IV PLLs, clock inputs, and clock control block location for different Cyclone IV device densities.

#### Notes to Figure 5-2:

- (1) The clock networks and clock control block locations apply to all EP4CGX15, EP4CGX22, and EP4CGX30 devices except EP4CGX30 device in F484 package.

- (2)  $\tt PLL_1$  and  $\tt PLL_2$  are multipurpose PLLs while  $\tt PLL_3$  and  $\tt PLL_4$  are general purpose PLLs.

- (3) There are five clock control blocks on each side.

- (4)  $PLL_4$  is only available in EP4CGX22 and EP4CGX30 devices in F324 package.

- (5) The EP4CGX15 device has two DPCLK pins on three sides of the device: DPCLK2 and DPCLK5 on bottom side, DPCLK7 and DPCLK8 on the right side, DPCLK10 and DPCLK13 on the top side of device.

- (6) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

Table 6–2 lists the I/O standards that support impedance matching and series termination.

| I/O Standard                                                   | IOH/IOL Current Strength<br>Setting (mA) <sup>(1)</sup> , <sup>(9)</sup> |                      | ${\rm R}_{\rm S}$ OCT with Calibration Setting, Ohm ( $\Omega$ ) |                           | ${\rm R_S}$ OCT Without Calibration Setting, Ohm ( $\Omega$ ) |                           | Cyclone<br>IV E I/O<br>Banks | Cyclone<br>IV GX I/O<br>Banks | Slew<br>Rate<br>Option | PCI-<br>clamp<br>Diode |

|----------------------------------------------------------------|--------------------------------------------------------------------------|----------------------|------------------------------------------------------------------|---------------------------|---------------------------------------------------------------|---------------------------|------------------------------|-------------------------------|------------------------|------------------------|

|                                                                | Column I/O                                                               | Row I/O              | Column<br>I/O                                                    | Row<br>I/O <sup>(8)</sup> | Column<br>I/O                                                 | Row<br>I/O <sup>(8)</sup> | Support                      | Support                       | (6)                    | Support                |

| 3.3-V LVTTL                                                    | 4,8                                                                      | 4,8                  | —                                                                |                           | —                                                             |                           |                              |                               | —                      | $\checkmark$           |

| 3.3-V LVCMOS                                                   | 2                                                                        | 2                    | —                                                                |                           | —                                                             |                           | -                            |                               |                        | $\checkmark$           |

| 3.0-V LVTTL                                                    | 4,8,12,16                                                                | 4,8,12,16            | 50,25                                                            | 50,25                     | 50,25                                                         | 50,25                     |                              |                               | 0 1 0                  | $\checkmark$           |

| 3.0-V LVCMOS                                                   | 4,8,12,16                                                                | 4,8,12,16            | 50,25                                                            | 50,25                     | 50,25                                                         | 50,25                     |                              |                               | 0,1, <b>2</b>          | $\checkmark$           |

| 3.0-V PCI/PCI-X                                                | —                                                                        |                      | _                                                                |                           | _                                                             |                           |                              | 3,4,5,6,                      |                        | $\checkmark$           |

| 2.5-V<br>LVTTL/LVCMOS                                          | 4,8,12,16                                                                | 4,8,12,16            | 50,25                                                            | 50,25                     | 50,25                                                         | 50,25                     | -                            | 7,8,9                         |                        | $\checkmark$           |

| 1.8-V<br>LVTTL/LVCMOS                                          | 2,4,6,8,10,12,1<br>6                                                     | 2,4,6,8,10,12,1<br>6 | 50,25                                                            | 50,25                     | 50,25                                                         | 50,25                     |                              |                               |                        |                        |

| 1.5-V LVCMOS                                                   | 2,4,6,8,10,12,1<br>6                                                     | 2,4,6,8,10,12,1<br>6 | 50,25                                                            | 50,25                     | 50,25                                                         | 50,25                     |                              |                               |                        | _                      |

| 1.2-V LVCMOS                                                   | 2,4,6,8,10,12                                                            | 2,4,6,8,10           | 50,25                                                            | 50                        | 50,25                                                         | 50                        | 1,2,3,4,<br>5,6,7,8          | 4,5,6,7,<br>8                 |                        | _                      |

| SSTL-2 Class I                                                 | 8,12                                                                     | 8,12                 | 50                                                               | 50                        | 50                                                            | 50                        |                              |                               |                        | _                      |

| SSTL-2 Class II                                                | 16                                                                       | 16                   | 25                                                               | 25                        | 25                                                            | 25                        |                              |                               | 0,1, <b>2</b>          | _                      |

| SSTL-18 Class I                                                | 8,10,12                                                                  | 8,10,12              | 50                                                               | 50                        | 50                                                            | 50                        |                              |                               | 5,                     | _                      |

| SSTL-18 Class II                                               | 12,16                                                                    | 12,16                | 25                                                               | 25                        | 25                                                            | 25                        | -                            | 3,4,5,6,                      |                        |                        |

| HSTL-18 Class I                                                | 8,10,12                                                                  | 8,10,12              | 50                                                               | 50                        | 50                                                            | 50                        | -                            | 7,8,9                         |                        |                        |

| HSTL-18 Class II                                               | 16                                                                       | 16                   | 25                                                               | 25                        | 25                                                            | 25                        |                              |                               |                        | _                      |

| HSTL-15 Class I                                                | 8,10,12                                                                  | 8,10,12              | 50                                                               | 50                        | 50                                                            | 50                        |                              |                               |                        | _                      |

| HSTL-15 Class II                                               | 16                                                                       | 16                   | 25                                                               | 25                        | 25                                                            | 25                        |                              |                               |                        |                        |

| HSTL-12 Class I                                                | 8,10,12                                                                  | 8,10                 | 50                                                               | 50                        | 50                                                            | 50                        |                              | 4,5,6,7,<br>8                 |                        | _                      |

| HSTL-12 Class II                                               | 14                                                                       | —                    | 25                                                               |                           | 25                                                            | —                         | 3,4,7,8                      | 4,7,8                         |                        | _                      |

| Differential SSTL-2<br>Class I <sup>(2), (7)</sup>             | 8,12                                                                     | 8,12                 | 50                                                               | 50                        | 50                                                            | 50                        |                              |                               |                        | _                      |

| Differential SSTL-2<br>Class II <sup>(2),</sup> <sup>(7)</sup> | 16                                                                       | 16                   | 25                                                               | 25                        | 25                                                            | 25                        |                              |                               |                        | —                      |

| Differential SSTL-<br>18 <sup>(2), (7)</sup>                   | 8,10,12                                                                  | —                    | 50                                                               | _                         | 50                                                            | _                         | 1,2,3,4,<br>5,6,7,8          | 3,4,5,6,<br>7,8               | 0,1, <b>2</b>          | —                      |

| Differential HSTL-<br>18 <sup>(2),</sup> <sup>(7)</sup>        | 8,10,12                                                                  | —                    | 50                                                               |                           | 50                                                            | _                         |                              |                               |                        | —                      |

| Differential HSTL-<br>15 <sup>(2), (7)</sup>                   | 8,10,12                                                                  | _                    | 50                                                               | _                         | 50                                                            | _                         |                              |                               |                        | —                      |

| Differential HSTL-<br>12 <sup>(2), (7)</sup>                   | 8,10,12                                                                  | _                    | 50                                                               | _                         | 50                                                            | _                         | 3,4,7,8                      | 4,7,8                         |                        | —                      |

Table 6–2. Cyclone IV Device I/O Features Support (Part 1 of 2)

Table 7–2 lists the number of DQS or DQ groups supported on each side of the Cyclone IV E device.

| Device  | Package       | Side                 | Number<br>×8<br>Groups | Number<br>×9<br>Groups | Number<br>×16<br>Groups | Number<br>×18<br>Groups | Number<br>×32<br>Groups | Number<br>×36<br>Groups |

|---------|---------------|----------------------|------------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| 144-pin |               | Left                 | 0                      | 0                      | 0                       | 0                       | —                       | —                       |

|         |               | Right                | 0                      | 0                      | 0                       | 0                       | —                       | —                       |

|         | 144-pin EQFP  | Bottom (1), (3)      | 1                      | 0                      | 0                       | 0                       | _                       |                         |

|         |               | Top (1), (4)         | 1                      | 0                      | 0                       | 0                       | —                       | —                       |

|         |               | Left (1)             | 1                      | 1                      | 0                       | 0                       | —                       | —                       |

| EP4CE6  | 256 pip LIPCA | Right <sup>(2)</sup> | 1                      | 1                      | 0                       | 0                       | —                       | —                       |

| EP4CE10 | 256-pin UBGA  | Bottom               | 2                      | 2                      | 1                       | 1                       | —                       | —                       |

|         |               | Тор                  | 2                      | 2                      | 1                       | 1                       | —                       | —                       |

|         |               | Left (1)             | 1                      | 1                      | 0                       | 0                       | —                       | _                       |

|         | 256 pip EPCA  | Right <sup>(2)</sup> | 1                      | 1                      | 0                       | 0                       | —                       | —                       |

|         | 256-pin FBGA  | Bottom               | 2                      | 2                      | 1                       | 1                       | —                       | —                       |

|         |               | Тор                  | 2                      | 2                      | 1                       | 1                       | —                       | —                       |

|         |               | Left                 | 0                      | 0                      | 0                       | 0                       | —                       | —                       |

|         | 144 pip EOED  | Right                | 0                      | 0                      | 0                       | 0                       | —                       | —                       |

|         | 144-pin EQFP  | Bottom (1), (3)      | 1                      | 0                      | 0                       | 0                       | —                       | —                       |

|         |               | Top (1), (4)         | 1                      | 0                      | 0                       | 0                       | —                       | —                       |

|         |               | Left                 | 0                      | 0                      | 0                       | 0                       | —                       | —                       |

|         | 164 pip MPCA  | Right                | 0                      | 0                      | 0                       | 0                       | —                       |                         |

|         | 164-pin MBGA  | Bottom (1), (3)      | 1                      | 0                      | 0                       | 0                       | —                       | —                       |

|         |               | Top (1), (4)         | 1                      | 0                      | 0                       | 0                       | —                       | —                       |

|         |               | Left                 | 1                      | 1                      | 0                       | 0                       | —                       | —                       |

|         | 256-pin MBGA  | Right                | 1                      | 1                      | 0                       | 0                       | —                       | —                       |

|         | 250-pill MBGA | Bottom (1), (3)      | 2                      | 2                      | 1                       | 1                       | —                       | —                       |

| EP4CE15 |               | Top (1), (4)         | 2                      | 2                      | 1                       | 1                       | —                       | —                       |

|         |               | Left (1)             | 1                      | 1                      | 0                       | 0                       | _                       | —                       |

|         | 256-pin UBGA  | Right <sup>(2)</sup> | 1                      | 1                      | 0                       | 0                       | —                       | —                       |

|         | 250-pill 0BGA | Bottom               | 2                      | 2                      | 1                       | 1                       | —                       | —                       |

|         |               | Тор                  | 2                      | 2                      | 1                       | 1                       | —                       | —                       |

|         |               | Left (1)             | 1                      | 1                      | 0                       | 0                       | —                       | —                       |

|         | 256-pin FBGA  | Right <sup>(2)</sup> | 1                      | 1                      | 0                       | 0                       | —                       | —                       |

|         |               | Bottom               | 2                      | 2                      | 1                       | 1                       |                         |                         |

|         |               | Тор                  | 2                      | 2                      | 1                       | 1                       |                         |                         |

|         |               | Left                 | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         | 484-pin FBGA  | Right                | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         | 404-рш госа   | Bottom               | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|         |               | Тор                  | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

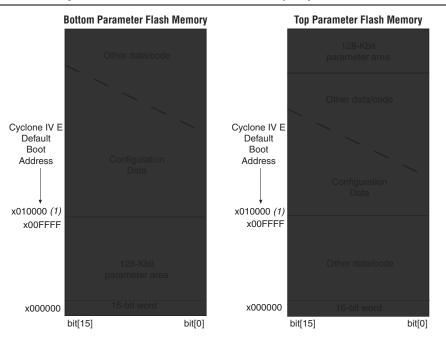

The default configuration boot address allows the system to use special parameter blocks in the flash memory map. Parameter blocks are at the top or bottom of the memory map. Figure 8–12 shows the configuration boot address in the AP configuration scheme. You can change the default configuration default boot address 0×010000 to any desired address using the APFC\_BOOT\_ADDR\_JTAG instruction. For more information about the APFC\_BOOT\_ADDR\_JTAG instruction, refer to "JTAG Instructions" on page 8–57.

#### Note to Figure 8-12:

(1) The default configuration boot address is x010000 when represented in 16-bit word addressing.

## **PS Configuration**

You can perform PS configuration on Cyclone IV devices with an external intelligent host, such as a MAX<sup>®</sup> II device, microprocessor with flash memory, or a download cable. In the PS scheme, an external host controls the configuration. Configuration data is clocked into the target Cyclone IV device through DATA[0] at each rising edge of DCLK.

If your system already contains a common flash interface (CFI) flash memory, you can use it for Cyclone IV device configuration storage as well. The MAX II PFL feature provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control the configuration from the flash memory device to the Cyclone IV device.

**Tor** For more information about the PFL, refer to *AN* 386: Using the Parallel Flash Loader with the Quartus II Software.

Cyclone IV devices do not support enhanced configuration devices for PS configuration.

| Bank | Description | Input/Output | Dedicated | Powered By        | <b>Configuration Mode</b> |

|------|-------------|--------------|-----------|-------------------|---------------------------|

| 5    | DEV_CLRn    | Input        | _         | V <sub>CCIO</sub> | Optional, AP              |

| <b>Table 8–19</b> . | <b>Configuration Pin</b> | Summary for C   | yclone IV E Devices  | (Part 3 of 3)   |

|---------------------|--------------------------|-----------------|----------------------|-----------------|

|                     | oominguration i m        | ounninaly for o | YUIUIIC IV L DUVIUUS | (1 41 ( 0 01 0) |

#### Notes to Table 8–19:

(1) To tri-state AS configuration pins in the AS configuration scheme, turn-on the Enable input tri-state on active configuration pins in user mode option from the Device and Pin Options dialog box. This tri-states DCLK, nCSO, Data[0], and Data[1]/ASDO pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the Enable input tri-state on active configuration pins in user mode option and set the desired setting from the Dual-purpose Pins Setting menu.

- (2) To tri-state AP configuration pins in the AP configuration scheme, turn-on the Enable input tri-state on active configuration pins in user mode option from the Device and Pin Options dialog box. This tri-states DCLK, Data[0..15], FLASH\_nCE, and other AP pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the Enable input tri-state on active configuration pins in user mode option and set the desired setting from the Dual-purpose Pins Setting menu.

- (3) The CRC\_ERROR pin is not available in Cyclone IV E devices with 1.0-V core voltage.

- (4) The CRC\_ERROR pin is a dedicated open-drain output or an optional user I/O pin. Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device and Pin Options dialog box. When using this pin, connect it to an external 10-kΩ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.

Table 8–20 describes the dedicated configuration pins. You must properly connect these pins on your board for successful configuration. You may not need some of these pins for your configuration schemes.

| Pin Name | User Mode | Configuration<br>Scheme | Pin Type                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------|-------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSEL     | N/A       | All                     | Input                       | Configuration input that sets the Cyclone IV device configuration scheme. You must hardwire these pins to $V_{CCA}$ or GND. The MSEL pins have internal 9-k $\Omega$ pull-down resistors that are always active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| nCONFIG  | N/A       | All                     | Input                       | Configuration control input. Pulling this pin low with<br>external circuitry during user mode causes the Cyclone IV<br>device to lose its configuration data, enter a reset state, and<br>tri-state all I/O pins. Returning this pin to a logic-high level<br>starts a reconfiguration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| nSTATUS  | N/A       | All                     | Bidirectional<br>open-drain | <ul> <li>The Cyclone IV device drives nSTATUS low immediately after power-up and releases it after the POR time.</li> <li>Status output—if an error occurs during configuration, nSTATUS is pulled low by the target device.</li> <li>Status input—if an external source (for example, another Cyclone IV device) drives the nSTATUS pin low during configuration or initialization, the target device enters an error state.</li> <li>Driving nSTATUS low after configuration and initialization does not affect the configured device. If you use a configuration device, driving nSTATUS low causes the configuration device to attempt to configure the device, but because the device does not reconfigure. To start a reconfiguration, you must pull nCONFIG low.</li> </ul> |

Table 8-20. Dedicated Configuration Pins on the Cyclone IV Device (Part 1 of 4)

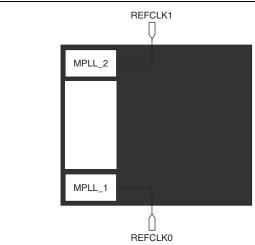

# **Input Reference Clocking**

When used for transceiver, the left PLLs synthesize the input reference clock to generate the required clocks for the transceiver channels. Figure 1–25 and Figure 1–26 show the sources of input reference clocks for PLLs used in the transceiver operation.

Clock output from PLLs in the FPGA core cannot feed into PLLs used by the transceiver as input reference clock.

### Notes to Figure 1-25:

- (1) The REFCLK0 and REFCLK1 pins are dual-purpose CLK, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A respectively.

- (2) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs may have reduced jitter performance.

1-27

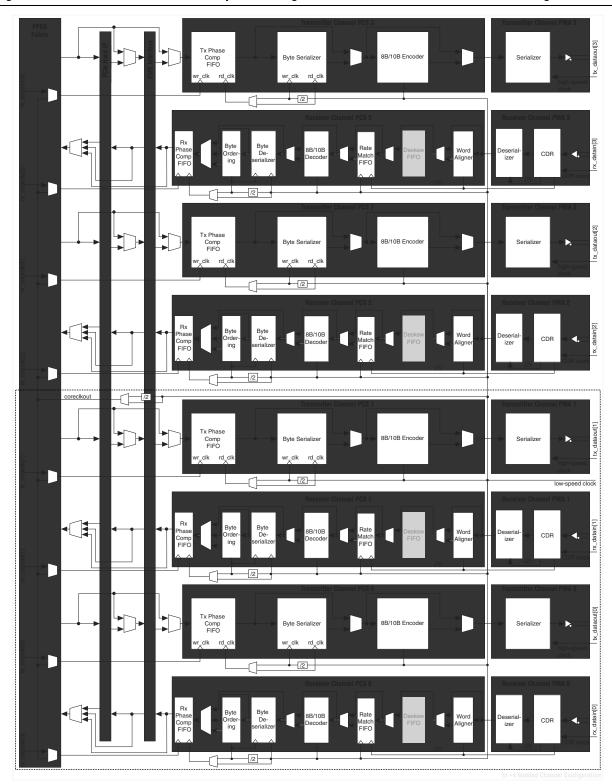

Figure 1–39. Transmitter and Receiver Datapath Clocking with Rate Match FIFO in Bonded Channel Configuration

### Notes to Figure 1–39:

- (1) Low-speed recovered clock.

- (2) High-speed recovered clock.

| Clock Name                 | <b>Clock Description</b>            | Interface Direction        |  |  |

|----------------------------|-------------------------------------|----------------------------|--|--|

| cal_blk_clk <sup>(2)</sup> | Transceiver calibration block clock | FPGA fabric to transceiver |  |  |

### Table 1–11. FPGA Fabric-Transceiver Interface Clocks (Part 2 of 2)

Notes to Table 1-11:

(1) Offset cancellation process that is executed after power cycle requires reconfig\_clk clock. The reconfig\_clk must be driven with a free-running clock and not derived from the transceiver blocks.

(2) For the supported clock frequency range, refer to the *Cyclone IV Device Data Sheet*.

In the transmitter datapath, TX phase compensation FIFO forms the FPGA fabric-transmitter interface. Data and control signals for the transmitter are clocked with the FIFO write clock. The FIFO write clock supports automatic clock selection by the Quartus II software (depending on channel configuration), or user-specified clock from tx\_coreclk port. Table 1–12 details the automatic TX phase compensation FIFO write clock selection by the Quartus II software.

The Quartus II software assumes automatic clock selection for TX phase compensation FIFO write clock if you do not enable the tx\_coreclk port.

### Table 1–12. Automatic TX Phase Compensation FIFO Write Clock Selection

| Channel<br>Configuration | Quartus II Selection                                                                                                                                                                     |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Non-bonded               | $tx\_clkout$ clock feeds the FIFO write clock. $tx\_clkout$ is forwarded through the transmitter channel from low-speed clock, which also feeds the FIFO read clock.                     |  |  |  |

| Bonded                   | coreclkout clock feeds the FIFO write clock for the bonded channels. coreclkout clock is the common bonded low-speed clock, which also feeds the FIFO read clock in the bonded channels. |  |  |  |

When using user-specified clock option, ensure that the clock feeding tx\_coreclk port has 0 ppm difference with the TX phase compensation FIFO read clock.

In the receiver datapath, RX phase compensation FIFO forms the receiver-FPGA fabric interface. Data and status signals from the receiver are clocked with the FIFO read clock. The FIFO read clock supports automatic clock selection by the Quartus II software (depending on channel configuration), or user-specified clock from rx\_coreclk port. Table 1–13 details the automatic RX phase compensation FIFO read clock selection by the Quartus II software.

The Quartus II software assumes automatic clock selection for RX phase compensation FIFO read clock if you do not enable the rx\_coreclk port.

| Table 1–13. | Automatic RX Phase | Compensation | <b>FIFO Read Clock</b> | <b>Selection</b> | (Part 1 of 2) |

|-------------|--------------------|--------------|------------------------|------------------|---------------|

|             |                    |              |                        |                  |               |

| Channel Configuration |                                     | Quartus II Selection                                                                                                                                                                  |  |  |  |

|-----------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Non-bonded            | With rate match FIFO <sup>(1)</sup> | $tx\_clkout$ clock feeds the FIFO read clock. $tx\_clkout$ is forwarded through the receiver channel from low-speed clock, which also feeds the FIFO write clock and transmitter PCS. |  |  |  |

| Non-bonded            | Without rate match FIFO             | $\tt rx\_clkout$ clock feeds the FIFO read clock. $\tt rx\_clkout$ is forwarded through the receiver channel from low-speed recovered clock, which also feeds the FIFO write clock.   |  |  |  |

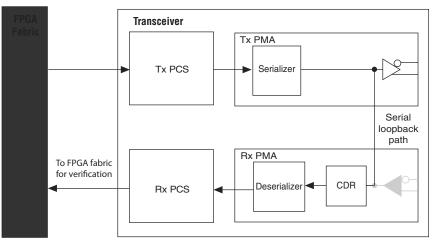

Serial loopback mode can only be dynamically enabled or disabled during user mode by performing a dynamic channel reconfiguration.

Figure 1–71. Serial Loopback Path<sup>(1)</sup>

Note to Figure 1–71:

(1) Grayed-Out Blocks are Not Active in this mode.

## **Reverse Serial Loopback**

The reverse serial loopback mode is available for all functional modes except for XAUI mode. The two reverse serial loopback options from the receiver to the transmitter are:

- Pre-CDR mode where data received through the RX input buffer is looped back to the TX output buffer using the **Reverse serial loopback (pre-CDR)** option

- Post-CDR mode where retimed data through the receiver CDR from the RX input buffer is looped back to the TX output buffer using the Reverse serial loopback option

The received data is also available to the FPGA logic. In the transmitter channel, only the transmitter buffer is active.

- The transmitter pre-emphasis feature is not available in reverse serial loopback (pre-CDR) mode.

- Reverse serial loopback modes can only be dynamically enabled or disabled during user mode by performing a dynamic channel reconfiguration.

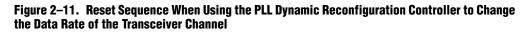

# **Dynamic Reconfiguration Reset Sequences**

When using dynamic reconfiguration in data rate divisions in PLL reconfiguration or channel reconfiguration mode, use the following reset sequences.

## **Reset Sequence in PLL Reconfiguration Mode**

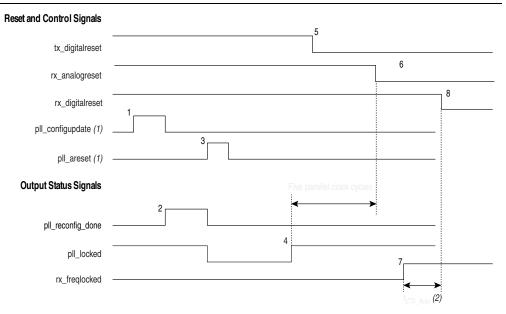

Use the example reset sequence shown in Figure 2–11 when you use the PLL dynamic reconfiguration controller to change the data rate of the transceiver channel. In this example, PLL dynamic reconfiguration is used to dynamically reconfigure the data rate of the transceiver channel configured in Basic ×1 mode with the receiver CDR in automatic lock mode.

#### Notes to Figure 2–11:

- (1) The pll\_configupdate and pll\_areset signals are driven by the ALTPLL\_RECONFIG megafunction. For more information, refer to AN 609: Implementing Dynamic Reconfiguration in Cyclone IV GX Devices and the Cyclone IV Dynamic Reconfiguration chapter.

- (2) For  $t_{LTD\_Auto}$  duration, refer to the *Cyclone IV Device Datasheet* chapter.

As shown in Figure 2–11, perform the following reset procedure when using the PLL dynamic reconfiguration controller to change the configuration of the PLLs in the transmitter channel:

1. Assert the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals. The pll\_configupdate signal is asserted (marker 1) by the ALTPLL\_RECONFIG megafunction after the final data bit is sent out. The pll\_reconfig\_done signal is asserted (marker 2) to inform the ALTPLL\_RECONFIG megafunction that the scan chain process is completed. The ALTPLL\_RECONFIG megafunction then asserts the pll\_areset signal (marker 3) to reset the transceiver PLL.

| Port Name                    | Input/<br>Output | Description                                                                                                                                                                                                                     |                                                                                                                                                  |                                             |  |  |  |

|------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|

|                              |                  | This is an optional pre-emphasis write control for the transmit buffer. Depending on what value you set at this input, the controller dynamically writes the value to the pre-emphasis control register of the transmit buffer. |                                                                                                                                                  |                                             |  |  |  |

|                              |                  | 'logical_channel_ad<br>same control signal                                                                                                                                                                                      | al is fixed to 5 bits if you enable e<br>dress' port for Analog controls re<br>for all the channels option in the<br>al is 5 bits per channel.   |                                             |  |  |  |

|                              |                  | <pre>tx_preemp[40]</pre>                                                                                                                                                                                                        | Corresponding ALTGX<br>instance settings                                                                                                         | Corresponding pre-<br>emphasis setting (mA) |  |  |  |

|                              |                  | 00000                                                                                                                                                                                                                           | 0                                                                                                                                                | Disabled                                    |  |  |  |

|                              |                  | 00001                                                                                                                                                                                                                           | 1                                                                                                                                                | 0.5                                         |  |  |  |

| tx preemp[40] (1)            | Input            | 00101                                                                                                                                                                                                                           | 5                                                                                                                                                | 1.0                                         |  |  |  |

|                              |                  | 01001                                                                                                                                                                                                                           | 9                                                                                                                                                | 1.5                                         |  |  |  |

|                              |                  | 01101                                                                                                                                                                                                                           | 13                                                                                                                                               | 2.0                                         |  |  |  |

|                              |                  | 10000                                                                                                                                                                                                                           | 16                                                                                                                                               | 2.375                                       |  |  |  |

|                              |                  | 10001                                                                                                                                                                                                                           | 17                                                                                                                                               | 2.5                                         |  |  |  |

|                              |                  | 10010                                                                                                                                                                                                                           | 18                                                                                                                                               | 2.625                                       |  |  |  |

|                              |                  | 10011                                                                                                                                                                                                                           | 19                                                                                                                                               | 2.75                                        |  |  |  |

|                              |                  | 10100                                                                                                                                                                                                                           | 20                                                                                                                                               | 2.875                                       |  |  |  |

|                              |                  | 10101                                                                                                                                                                                                                           | 21                                                                                                                                               | 3.0                                         |  |  |  |

|                              |                  | All other values => N/                                                                                                                                                                                                          | Ά                                                                                                                                                |                                             |  |  |  |

|                              |                  | This is an optional wr<br>the PMA.                                                                                                                                                                                              | ite control to write an equalization                                                                                                             | n control value for the receive side of     |  |  |  |

|                              |                  | 'logical_channel_ad<br>same control signal                                                                                                                                                                                      | nal is fixed to 4 bits if you enable of<br>dress' port for Analog controls re<br>for all the channels option in the<br>al is 4 bits per channel. |                                             |  |  |  |

| rx_eqctr1[30] <sup>(1)</sup> | Input            | <pre>rx_eqctrl[30]</pre>                                                                                                                                                                                                        | Corresponding ALTGX instance                                                                                                                     | settings                                    |  |  |  |

|                              |                  | 0001                                                                                                                                                                                                                            | Low                                                                                                                                              |                                             |  |  |  |

|                              |                  | 0101                                                                                                                                                                                                                            | Medium Low                                                                                                                                       |                                             |  |  |  |

|                              |                  | 0100                                                                                                                                                                                                                            | Medium High                                                                                                                                      |                                             |  |  |  |

|                              |                  | 0111                                                                                                                                                                                                                            | High                                                                                                                                             |                                             |  |  |  |

|                              |                  | All other values $=> N/$                                                                                                                                                                                                        | Ά                                                                                                                                                |                                             |  |  |  |

Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 5 of 7)

### **PMA Control Ports Used in a Read Transaction**

- tx\_vodctrl\_out is 3 bits per channel

- tx\_preemp\_out is 5 bits per channel

- rx eqdcgain out is 2 bits per channel

- rx\_eqctrl\_out is 4 bits per channel

For example, assume the number of channels controlled by the dynamic reconfiguration controller is two, tx\_vodctrl\_out is 6 bits wide.

### Write Transaction

The value you set at the selected PMA control ports is written to all the transceiver channels connected to the ALTGX\_RECONFIG instance.

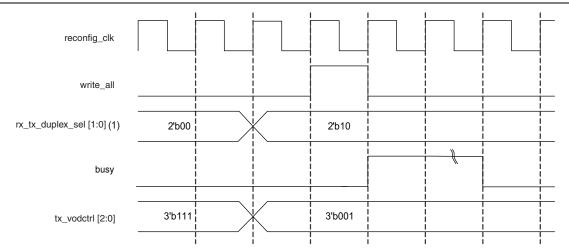

For example, assume you have enabled tx\_vodctrl in the ALTGX\_RECONFIG MegaWizard Plug-In Manager to reconfigure the V<sub>OD</sub> of the transceiver channels. To complete a write transaction to reconfigure the V<sub>OD</sub>, perform the following steps:

- 1. Before you initiate a write transaction, set the selected PMA control ports to the desired settings (for example, tx\_vodctrl = 3'b001).

- 2. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 3. Ensure that the busy signal is low before you start a write transaction.

- 4. Assert the write\_all signal for one reconfig\_clk clock cycle. This initiates the write transaction.

- 5. The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

Figure 3–6 shows the write transaction for Method 2.

### Figure 3–6. Write Transaction Waveform—Use the same control signal for all the channels Option

#### Note to Figure 3-6:

(1) In this waveform example, you want to write to only the transmitter portion of the channel.

Table 3–7 lists the ALTGX megafunction ports for PLL Reconfiguration mode.

| Port Name <sup>(1)</sup> | Input/<br>Output | Description                                                                                                                                                                                                                                                                                    | Comments                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pll_areset [n0]          | Input            | <ul> <li>Resets the transceiver PLL. The pll_areset are asserted in two conditions:</li> <li>Used to reset the transceiver PLL during the reset sequence. During reset sequence, this signal is user controlled.</li> <li>After the transceiver PLL is reconfigured, this signal is</li> </ul> | You must connect the pll_areset port of ALTGX to the<br>pll_areset port of the ALTPLL_RECONFIG<br>megafunction.<br>The ALTPLL_RECONFIG controller asserts the<br>pll_areset port at the next rising clock edge after the<br>pll_reconfig_done signal from the ALTGX<br>megafunction goes high. After the pll_reconfig_done<br>signal goes high, the transceiver PLL is reset. When the |

|                          |                  | asserted high by the<br>ALTPLL_RECONFIG controller. At<br>this time, this signal is not user<br>controlled.                                                                                                                                                                                    | PLL reconfiguration is completed, this reset is<br>performed automatically by the ALTPLL_RECONFIG<br>megafunction and is not user controlled.                                                                                                                                                                                                                                          |

| pll_scandata<br>[n0]     | Input            | Receives the scan data input from the ALTPLL_RECONFIG megafunction.                                                                                                                                                                                                                            | The reconfigurable transceiver PLL received the scan data input through this port for the dynamically reconfigurable bits from the ALTPLL_RECONFIG controller.                                                                                                                                                                                                                         |

| pll_scanclk<br>[n0]      | Input            | Drives the scanclk port on the reconfigurable transceiver PLL.                                                                                                                                                                                                                                 | Connect the pll_scanclk port of the ALTGX megafunction to the ALTPLL_RECONFIG scanclk port.                                                                                                                                                                                                                                                                                            |

| pll_scancikena<br>[n0]   | Input            | Acts as a clock enable for the scanclk port on the reconfigurable transceiver PLL.                                                                                                                                                                                                             | Connect the pll_scanclkena port of the ALTGX megafunction to the ALTPLL_RECONFIG scanclk port.                                                                                                                                                                                                                                                                                         |

| pll_configupdate<br>[n0] | Input            | Drives the configupdate port on the reconfigurable transceiver PLL.                                                                                                                                                                                                                            | This port is connected to the pll_configupdate port<br>from the ALTPLL_RECONFIG controller. After the final<br>data bit is sent out, the ALTPLL_RECONFIG controller<br>asserts this signal.                                                                                                                                                                                            |

| pll_reconfig_done[n0]    | Output           | This signal is asserted to indicate the reconfiguration process is done.                                                                                                                                                                                                                       | Connect the pll_reconfig_done port to the pll_scandone port on the ALTPLL_RECONFIG controller. The transceiver PLL scandone output signal drives this port and determines when the PLL is reconfigured.                                                                                                                                                                                |

| pll_scandataout<br>[n0]  | Output           | This port scan out the current configuration of the transceiver PLL.                                                                                                                                                                                                                           | Connect the pll_scandataout port to the<br>pll_scandataout port of the ALTPLL_RECONFIG<br>controller. This port reads the current configuration of<br>the transceiver PLL and send it to the<br>ALTPLL_RECONFIG megafunction.                                                                                                                                                          |

Table 3–7. ALTGX Megafunction Port List for PLL Reconfiguration Mode

Note to Table 3-7:

(1)  $\langle n \rangle$  = (number of transceiver PLLs configured in the ALTGX MegaWizard) - 1.

• For more information about the ALTPLL\_RECONFIG megafunction port list, description and usage, refer to the *Phase-Locked Loop Reconfiguration* (*ALTPL\_RECONFIG*) *Megafunction User Guide*.

| Table 1–3. Recomme | nded Operating Conditions | s for Cyclone IV E Devices <sup>(1),</sup> | <sup>(2)</sup> (Part 2 of 2) |

|--------------------|---------------------------|--------------------------------------------|------------------------------|

|--------------------|---------------------------|--------------------------------------------|------------------------------|

| Symbol             | Parameter                                                     | Conditions | Min | Тур | Max | Unit |

|--------------------|---------------------------------------------------------------|------------|-----|-----|-----|------|

| I <sub>Diode</sub> | Magnitude of DC current across<br>PCI-clamp diode when enable | _          | _   |     | 10  | mA   |

### Notes to Table 1-3:

Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades.

(2)  $V_{CCI0}$  for all I/O banks must be powered up during device operation. All vCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

(3)  $V_{CC}$  must rise monotonically.

(4)  $V_{CCIO}$  powers all input buffers.

(5) The POR time for Standard POR ranges between 50 and 200 ms. Each individual power supply must reach the recommended operating range within 50 ms.

(6) The POR time for Fast POR ranges between 3 and 9 ms. Each individual power supply must reach the recommended operating range within 3 ms.

| Symbol                            | Parameter                                                          | Conditions | Min   | Тур | Max   | Unit |

|-----------------------------------|--------------------------------------------------------------------|------------|-------|-----|-------|------|

| V <sub>ccint</sub> (3)            | Core voltage, PCIe hard IP block, and transceiver PCS power supply | _          | 1.16  | 1.2 | 1.24  | V    |

| V <sub>CCA</sub> (1), (3)         | PLL analog power supply                                            | —          | 2.375 | 2.5 | 2.625 | V    |

| V <sub>CCD_PLL</sub> (2)          | PLL digital power supply                                           |            | 1.16  | 1.2 | 1.24  | V    |

| V <sub>CCD_PLL</sub> (2)          | I/O banks power supply for 3.3-V operation                         | _          | 3.135 | 3.3 | 3.465 | V    |

|                                   | I/O banks power supply for 3.0-V operation                         | _          | 2.85  | 3   | 3.15  | V    |

| V <sub>CCIO</sub> <i>(3), (4)</i> | I/O banks power supply for 2.5-V operation                         | _          | 2.375 | 2.5 | 2.625 | V    |

| VCCIO                             | I/O banks power supply for 1.8-V operation                         | _          | 1.71  | 1.8 | 1.89  | V    |

|                                   | I/O banks power supply for 1.5-V operation                         | _          | 1.425 | 1.5 | 1.575 | V    |

|                                   | I/O banks power supply for 1.2-V operation                         | _          | 1.14  | 1.2 | 1.26  | V    |

|                                   | Differential clock input pins power supply for 3.3-V operation     | _          | 3.135 | 3.3 | 3.465 | V    |

|                                   | Differential clock input pins power supply for 3.0-V operation     | _          | 2.85  | 3   | 3.15  | V    |

| V <sub>CC CLKIN</sub>             | Differential clock input pins power supply for 2.5-V operation     | _          | 2.375 | 2.5 | 2.625 | V    |

| (3), (5), (6)                     | Differential clock input pins power supply for 1.8-V operation     | _          | 1.71  | 1.8 | 1.89  | V    |

|                                   | Differential clock input pins power supply for 1.5-V operation     | _          | 1.425 | 1.5 | 1.575 | V    |

|                                   | Differential clock input pins power supply for 1.2-V operation     | _          | 1.14  | 1.2 | 1.26  | V    |

| V <sub>CCH_GXB</sub>              | Transceiver output buffer power supply                             | —          | 2.375 | 2.5 | 2.625 | V    |

### Table 1–4. Recommended Operating Conditions for Cyclone IV GX Devices (Part 1 of 2)

# **Power Consumption**

Use the following methods to estimate power for a design:

- the Excel-based EPE

- the Quartus<sup>®</sup> II PowerPlay power analyzer feature

The interactive Excel-based EPE is used prior to designing the device to get a magnitude estimate of the device power. The Quartus II PowerPlay power analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The PowerPlay power analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, combined with detailed circuit models, can yield very accurate power estimates.

**\*** For more information about power estimation tools, refer to the *Early Power Estimator User Guide* and the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

# **Switching Characteristics**

This section provides performance characteristics of Cyclone IV core and periphery blocks for commercial grade devices.

These characteristics can be designated as Preliminary or Final.

- Preliminary characteristics are created using simulation results, process data, and other known parameters. The upper-right hand corner of these tables show the designation as "Preliminary".

- Final numbers are based on actual silicon characterization and testing. The numbers reflect the actual performance of the device under worst-case silicon process, voltage, and junction temperature conditions. There are no designations on finalized tables.

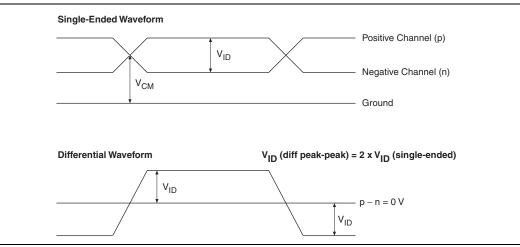

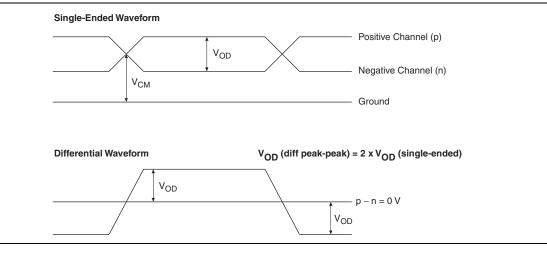

### Figure 1–4 shows the differential receiver input waveform.

Figure 1–5 shows the transmitter output waveform.

Table 1–22 lists the typical  $V_{OD}$  for Tx term that equals 100  $\Omega$ .

### Table 1–22. Typical V\_{0D} Setting, Tx Term = 100 $\Omega$

| Symbol                                                    | V <sub>OD</sub> Setting (mV) |     |     |              |      |      |  |  |

|-----------------------------------------------------------|------------------------------|-----|-----|--------------|------|------|--|--|

|                                                           | 1                            | 2   | 3   | <b>4</b> (1) | 5    | 6    |  |  |

| V <sub>OD</sub> differential peak<br>to peak typical (mV) | 400                          | 600 | 800 | 900          | 1000 | 1200 |  |  |

### Note to Table 1-22:

(1) This setting is required for compliance with the PCIe protocol.

## **IOE Programmable Delay**

Table 1–40 and Table 1–41 list the IOE programmable delay for Cyclone IV E 1.0 V core voltage devices.

| Table 1-40. IOE Prog | rammable Delay on Col | umn Pins for Cyclone IV | V E 1.0 V Core Voltage | Devices <sup>(1),</sup> <sup>(2)</sup> |

|----------------------|-----------------------|-------------------------|------------------------|----------------------------------------|

|----------------------|-----------------------|-------------------------|------------------------|----------------------------------------|

|                                                                       |                                | Number  |     | Max Offset  |       |             |       |       |      |

|-----------------------------------------------------------------------|--------------------------------|---------|-----|-------------|-------|-------------|-------|-------|------|

| Parameter                                                             | Paths Affected                 | of      | Min | Fast Corner |       | Slow Corner |       |       | Unit |

|                                                                       |                                | Setting |     | C8L         | 18L   | C8L         | C9L   | 18L   |      |

| Input delay from pin to<br>internal cells                             | Pad to I/O<br>dataout to core  | 7       | 0   | 2.054       | 1.924 | 3.387       | 4.017 | 3.411 | ns   |

| Input delay from pin to<br>input register                             | Pad to I/O input register      | 8       | 0   | 2.010       | 1.875 | 3.341       | 4.252 | 3.367 | ns   |

| Delay from output register to output pin                              | I/O output<br>register to pad  | 2       | 0   | 0.641       | 0.631 | 1.111       | 1.377 | 1.124 | ns   |

| Input delay from<br>dual-purpose clock pin to<br>fan-out destinations | Pad to global<br>clock network | 12      | 0   | 0.971       | 0.931 | 1.684       | 2.298 | 1.684 | ns   |

Notes to Table 1-40:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

|                                                                       |                                | Number  |        | Max Offset  |       |             |       |       |      |

|-----------------------------------------------------------------------|--------------------------------|---------|--------|-------------|-------|-------------|-------|-------|------|

| Parameter                                                             | Paths Affected                 | of      | of Min | Fast Corner |       | Slow Corner |       |       | Unit |

|                                                                       |                                | Setting |        | C8L         | 18L   | C8L         | C9L   | 18L   |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to core  | 7       | 0      | 2.057       | 1.921 | 3.389       | 4.146 | 3.412 | ns   |

| Input delay from pin to<br>input register                             | Pad to I/O input register      | 8       | 0      | 2.059       | 1.919 | 3.420       | 4.374 | 3.441 | ns   |

| Delay from output register to output pin                              | I/O output<br>register to pad  | 2       | 0      | 0.670       | 0.623 | 1.160       | 1.420 | 1.168 | ns   |

| Input delay from<br>dual-purpose clock pin to<br>fan-out destinations | Pad to global<br>clock network | 12      | 0      | 0.960       | 0.919 | 1.656       | 2.258 | 1.656 | ns   |

Notes to Table 1-41:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

# I/O Timing

Use the following methods to determine I/O timing:

- the Excel-based I/O Timing

- the Quartus II timing analyzer

The Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get a timing budget estimation as part of the link timing analysis. The Quartus II timing analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after place-and-route is complete.

The Excel-based I/O Timing spreadsheet is downloadable from Cyclone IV Devices Literature website.

# Glossary

Table 1–46 lists the glossary for this chapter.

| Letter | Term                                                            | Definitions                                                                             |  |  |  |  |  |

|--------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|

| Α      | —                                                               |                                                                                         |  |  |  |  |  |

| В      |                                                                 | _                                                                                       |  |  |  |  |  |

| C      | —                                                               | —                                                                                       |  |  |  |  |  |

| D      | —                                                               | —                                                                                       |  |  |  |  |  |

| E      | _                                                               | —                                                                                       |  |  |  |  |  |

| F      | f <sub>HSCLK</sub>                                              | High-speed I/O block: High-speed receiver/transmitter input and output clock frequency. |  |  |  |  |  |

| G      | GCLK                                                            | Input pin directly to Global Clock network.                                             |  |  |  |  |  |

| u      | GCLK PLL                                                        | Input pin to Global Clock network through the PLL.                                      |  |  |  |  |  |

| Н      | HSIODR                                                          | High-speed I/O block: Maximum/minimum LVDS data transfer rate (HSIODR = 1/TUI).         |  |  |  |  |  |

| I      | Input Waveforms<br>for the SSTL<br>Differential I/O<br>Standard | Vswing<br>Vswing<br>V <sub>IH</sub><br>V <sub>REF</sub>                                 |  |  |  |  |  |

| Table | 1-46. | Glossary | (Part 1 | of 5) |