# E·XFL

### Intel - EP4CE6E22C6 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                 |

|--------------------------------|--------------------------------------------------------|

| Number of LABs/CLBs            | 392                                                    |

| Number of Logic Elements/Cells | 6272                                                   |

| Total RAM Bits                 | 276480                                                 |

| Number of I/O                  | 91                                                     |

| Number of Gates                | -                                                      |

| Voltage - Supply               | 1.15V ~ 1.25V                                          |

| Mounting Type                  | Surface Mount                                          |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                        |

| Package / Case                 | 144-LQFP Exposed Pad                                   |

| Supplier Device Package        | 144-EQFP (20x20)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce6e22c6 |

|                                |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Cyclone IV Device Family Architecture**

This section describes Cyclone IV device architecture and contains the following topics:

- "FPGA Core Fabric"

- "I/O Features"

- "Clock Management"

- "External Memory Interfaces"

- "Configuration"

- "High-Speed Transceivers (Cyclone IV GX Devices Only)"

- "Hard IP for PCI Express (Cyclone IV GX Devices Only)"

## **FPGA Core Fabric**

Cyclone IV devices leverage the same core fabric as the very successful Cyclone series devices. The fabric consists of LEs, made of 4-input look up tables (LUTs), memory blocks, and multipliers.

Each Cyclone IV device M9K memory block provides 9 Kbits of embedded SRAM memory. You can configure the M9K blocks as single port, simple dual port, or true dual port RAM, as well as FIFO buffers or ROM. They can also be configured to implement any of the data widths in Table 1–7.

### Table 1–7. M9K Block Data Widths for Cyclone IV Device Family

| Mode                            | Data Width Configurations            |

|---------------------------------|--------------------------------------|

| Single port or simple dual port | ×1, ×2, ×4, ×8/9, ×16/18, and ×32/36 |

| True dual port                  | ×1, ×2, ×4, ×8/9, and ×16/18         |

The multiplier architecture in Cyclone IV devices is the same as in the existing Cyclone series devices. The embedded multiplier blocks can implement an 18 × 18 or two 9 × 9 multipliers in a single block. Altera offers a complete suite of DSP IP including finite impulse response (FIR), fast Fourier transform (FFT), and numerically controlled oscillator (NCO) functions for use with the multiplier blocks. The Quartus<sup>®</sup> II design software's DSP Builder tool integrates MathWorks Simulink and MATLAB design environments for a streamlined DSP design flow.

For more information, refer to the *Logic Elements and Logic Array Blocks in Cyclone IV Devices*, *Memory Blocks in Cyclone IV Devices*, and *Embedded Multipliers in Cyclone IV Devices* chapters.

## 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices

#### CYIV-51002-1.0

This chapter contains feature definitions for logic elements (LEs) and logic array blocks (LABs). Details are provided on how LEs work, how LABs contain groups of LEs, and how LABs interface with the other blocks in Cyclone<sup>®</sup> IV devices.

## **Logic Elements**

Logic elements (LEs) are the smallest units of logic in the Cyclone IV device architecture. LEs are compact and provide advanced features with efficient logic usage. Each LE has the following features:

- A four-input look-up table (LUT), which can implement any function of four variables

- A programmable register

- A carry chain connection

- A register chain connection

- The ability to drive the following interconnects:

- Local

- Row

- Column

- Register chain

- Direct link

- Register packing support

- Register feedback support

Violating the setup or hold time on the M9K memory block input registers may corrupt memory contents. This applies to both read and write operations.

### **Single-Port Mode**

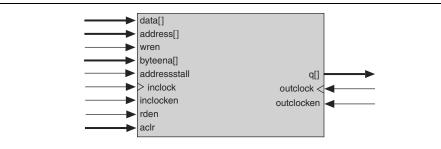

Single-port mode supports non-simultaneous read and write operations from a single address. Figure 3–6 shows the single-port memory configuration for Cyclone IV devices M9K memory blocks.

### Figure 3–6. Single-Port Memory <sup>(1)</sup>, <sup>(2)</sup>

#### Notes to Figure 3-6:

- (1) You can implement two single-port memory blocks in a single M9K block.

- (2) For more information, refer to "Packed Mode Support" on page 3-4.

During a write operation, the behavior of the RAM outputs is configurable. If you activate rden during a write operation, the RAM outputs show either the new data being written or the old data at that address. If you perform a write operation with rden deactivated, the RAM outputs retain the values they held during the most recent active rden signal.

To choose the desired behavior, set the **Read-During-Write** option to either **New Data** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about read-during-write mode, refer to "Read-During-Write Operations" on page 3–15.

The port width configurations for M9K blocks in single-port mode are as follow:

- 8192 × 1

- 4096 × 2

- 2048 × 4

- 1024 × 8

- 1024 × 9

- 512 × 16

- 512 × 18

- 256 × 32

- 256 × 36

implements either a high-speed deserializer receiver or a high-speed serializer transmitter. There is a list of parameters in the ALTLVDS megafunction that you can set to customize your SERDES based on your design requirements. The megafunction is optimized to use Cyclone IV devices resources to create high-speed I/O interfaces in the most effective manner.

When you use Cyclone IV devices with the ALTLVDS megafunction, the interface always sends the MSB of your parallel data first.

**C** For more details about designing your high-speed I/O systems interfaces using the ALTLVDS megafunction, refer to the *ALTLVDS Megafunction User Guide* and the *Quartus II Handbook*.

## **Document Revision History**

Table 6–12 lists the revision history for this chapter.

| Date          | Version     | Changes                                                                                                                                                                     |

|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2016    | 2.7         | ■ Updated Table 6–5 and Table 6–9 to remove support for the N148 package.                                                                                                   |

| May 2013 2.6  |             | ■ Updated Table 6–2 by adding Note (9).                                                                                                                                     |

| May 2013      | 2.0         | <ul> <li>Updated Table 6–4 and Table 6–8 to add new device options and packages.</li> </ul>                                                                                 |

| February 2013 | 2.5         | Updated Table 6–4 and Table 6–8 to add new device options and packages.                                                                                                     |

|               |             | <ul> <li>Updated "I/O Banks" and "High Speed Serial Interface (HSSI) Input Reference Clock<br/>Support " sections.</li> </ul>                                               |

| October 2012  | 2.4         | ■ Updated Table 6–3 and Table 6–5.                                                                                                                                          |

|               |             | ■ Updated Figure 6–10.                                                                                                                                                      |

|               | 2.3         | <ul> <li>Updated "Differential SSTL I/O Standard Support in Cyclone IV Devices" and<br/>"Differential HSTL I/O Standard Support in Cyclone IV Devices" sections.</li> </ul> |

| November 2011 |             | ■ Updated Table 6–1, Table 6–8, and Table 6–9.                                                                                                                              |

|               |             | ■ Updated Figure 6–1.                                                                                                                                                       |

|               |             | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                                               |

|               |             | <ul> <li>Added Cyclone IV E new device package information.</li> </ul>                                                                                                      |

| December 2010 | er 2010 2.2 | <ul> <li>Added "Clock Pins Functionality" section.</li> </ul>                                                                                                               |

|               |             | ■ Updated Table 6–4 and Table 6–8.                                                                                                                                          |

|               |             | <ul> <li>Minor text edits.</li> </ul>                                                                                                                                       |

|               |             | <ul> <li>Updated "Cyclone IV I/O Elements", "Programmable Pull-Up Resistor", "I/O Banks",<br/>"High-Speed I/O Interface", and "Designing with BLVDS" sections.</li> </ul>   |

| July 2010     | 2.1         | ■ Updated Table 6–6 and Table 6–7.                                                                                                                                          |

|               |             | <ul> <li>Updated Figure 6–19.</li> </ul>                                                                                                                                    |

Table 6–12. Document Revision History (Part 1 of 2)

| Date          | Version | Changes                                                                                                             |  |  |  |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

|               |         | <ul> <li>Added Cyclone IV E devices information for the Quartus II software version 9.1 SP1<br/>release.</li> </ul> |  |  |  |

|               |         | ■ Updated Table 6–2, Table 6–3, and Table 6–10.                                                                     |  |  |  |

| February 2010 | 2.0     | ■ Updated "I/O Banks" section.                                                                                      |  |  |  |

| -             |         | ■ Added Figure 6–9.                                                                                                 |  |  |  |

|               |         | ■ Updated Figure 6–10 and Figure 6–11.                                                                              |  |  |  |

|               |         | ■ Added Table 6–4, Table 6–6, and Table 6–8.                                                                        |  |  |  |

| November 2009 | 1.0     | Initial release.                                                                                                    |  |  |  |

Table 6–12. Document Revision History (Part 2 of 2)

| Device                               | Package       | Side   | Number<br>×8<br>Groups | Number<br>×9<br>Groups | Number<br>×16<br>Groups | Number<br>×18<br>Groups | Number<br>×32<br>Groups | Number<br>×36<br>Groups |

|--------------------------------------|---------------|--------|------------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

|                                      |               | Left   | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      | 484-pin UBGA  | Right  | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

| EP4CE40<br>EP4CE55 484-pi<br>EP4CE75 | 404-pill UBGA | Bottom | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      |               | Тор    | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      | 484-pin FBGA  | Left   | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      |               | Right  | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      | 404-ріїї град | Bottom | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      |               | Тор    | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      |               | Left   | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      |               | Right  | 4                      | 4                      | 2                       | 2                       | 1                       | 1                       |

|                                      | 780-pin FBGA  | Bottom | 6                      | 6                      | 2                       | 2                       | 1                       | 1                       |

|                                      |               | Тор    | 6                      | 6                      | 2                       | 2                       | 1                       | 1                       |

| Table 7–2. Cyclone IV E Device DQS and DQ Bus Mode Support for Each Side of the Device (Part 3 of 3) |

|------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------|

Notes to Table 7-2:

(1) Some of the DQ pins can be used as RUP and RDN pins. You cannot use these groups if you are using these pins as RUP and RDN pins for OCT calibration.

(2) Some of the DQ pins can be used as RUP pins while the DM pins can be used as RDN pins. You cannot use these groups if you are using the RUP and RDN pins for OCT calibration.

(3) There is no DM pin support for these groups.

(4) PLLCLKOUT3n and PLLCLKOUT3p pins are shared with the DQ or DM pins to gain ×8 DQ group. You cannot use these groups if you are using PLLCLKOUT3n and PLLCLKOUT3p.

**To** For more information about device package outline, refer to the Device Packaging Specifications webpage.

DQS pins are listed in the Cyclone IV pin tables as DQSXY, in which X indicates the DQS grouping number and Y indicates whether the group is located on the top (T), bottom (B), or right (R) side of the device. Similarly, the corresponding DQ pins are marked as DQXY, in which the X denotes the DQ grouping number and Y denotes whether the group is located on the top (T), bottom (B), or right (R) side of the device. For example, DQS2T indicates a DQS pin belonging to group 2, located on the top side of the device. Similarly, the DQ pins belonging to that group is shown as DQ2T.

Each DQ group is associated with its corresponding DQS pins, as defined in the Cyclone IV pin tables. For example:

- For DDR2 or DDR SDRAM, ×8 DQ group DQ3B[7..0] pins are associated with the DQS3B pin (same 3B group index)

- For QDR II SRAM, ×9 Q read-data group DQ3T[8..0] pins are associated with DQS0T/CQ0T and DQS1T/CQ0T# pins (same 0T group index)

The Quartus<sup>®</sup> II software issues an error message if a DQ group is not placed properly with its associated DQS.

## Table 8–4. Configuration Schemes for Cyclone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150) (Part 2 of 2)

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) $^{(1)}$ |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------|

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   | _         | _                                           |

### Notes to Table 8-4:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to  $V_{CCA}$  or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

> Smaller Cyclone IV E devices or package options (E144 and F256 packages) do not have the MSEL[3] pin. The AS Fast POR configuration scheme at 3.0- or 2.5-V configuration voltage standard and the AP configuration scheme are not supported in Cyclone IV E devices without the MSEL[3] pin. To configure these devices with other supported configuration schemes, select MSEL[2..0] pins according to the MSEL settings in Table 8–5.

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------------|

|                              | 1     | 1     | 0     | 1     | Fast      | 3.3                                               |

| AS                           | 0     | 1     | 0     | 0     | Fast      | 3.0, 2.5                                          |

|                              | 0     | 0     | 1     | 0     | Standard  | 3.3                                               |

|                              | 0     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 0     | 1     | 0     | 1     | Fast      | 3.3                                               |

|                              | 0     | 1     | 1     | 0     | Fast      | 1.8                                               |

| AP                           | 0     | 1     | 1     | 1     | Standard  | 3.3                                               |

|                              | 1     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 1     | 0     | 0     | 0     | Standard  | 1.8                                               |

| PS                           | 1     | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| P5                           | 0     | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                                     |

| FPP                          | 1     | 1     | 1     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| 111                          | 1     | 1     | 1     | 1     | Fast      | 1.8, 1.5                                          |

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   |           | _                                                 |

Table 8–5. Configuration Schemes for Cyclone IV E Devices

### Notes to Table 8-5:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to V<sub>CCA</sub> or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration. devices. The internal oscillator is designed to ensure that its maximum frequency is guaranteed to meet EPCS device specifications. Cyclone IV devices offer the option to select CLKUSR as the external clock source for DCLK. You can change the clock source option in the Quartus II software in the **Configuration** tab of the **Device and Pin Options** dialog box.

P

EPCS1 does not support Cyclone IV devices because of its insufficient memory capacity.

Table 8-6. AS DCLK Output Frequency

| Oscillator | Minimum | Typical | Maximum | Unit |

|------------|---------|---------|---------|------|

| 40 MHz     | 20      | 30      | 40      | MHz  |

In configuration mode, the Cyclone IV device enables the serial configuration device by driving the nCSO output pin low, which connects to the nCS pin of the configuration device. The Cyclone IV device uses the DCLK and DATA[1] pins to send operation commands and read address signals to the serial configuration device. The configuration device provides data on its DATA pin, which connects to the DATA[0] input of the Cyclone IV device.

All AS configuration pins (DATA[0], DCLK, nCSO, and DATA[1]) have weak internal pullup resistors that are always active. After configuration, these pins are set as input tristated and are driven high by the weak internal pull-up resistors.

The timing parameters for AS mode are not listed here because the  $t_{CF2CD}$ ,  $t_{CF2ST0}$ ,  $t_{CFG}$ ,  $t_{STATUS}$ ,  $t_{CF2ST1}$ , and  $t_{CD2UM}$  timing parameters are identical to the timing parameters for PS mode shown in Table 8–12 on page 8–36.

### **PS Configuration Using an External Host**

In the PS configuration scheme, you can use an intelligent host such as a MAX II device or microprocessor that controls the transfer of configuration data from a storage device, such as flash memory, to the target Cyclone IV device. You can store the configuration data in **.rbf**, **.hex**, or **.ttf** format.

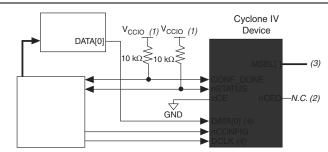

Figure 8–13 shows the configuration interface connections between a Cyclone IV device and an external host device for single-device configuration.

Figure 8–13. Single-Device PS Configuration Using an External Host

#### Notes to Figure 8-13:

- (1) Connect the pull-up resistor to a supply that provides an acceptable input signal for the device.  $V_{CC}$  must be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

- (2) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

To begin the configuration, the external host device must generate a low-to-high transition on the nCONFIG pin. When nSTATUS is pulled high, the external host device must place the configuration data one bit at a time on DATA[0]. If you use configuration data in **.rbf**, **.ttf**, or **.hex**, you must first send the LSB of each data byte. For example, if the **.rbf** contains the byte sequence 02 1B EE 01 FA, the serial bitstream you must send to the device is:

0100-0000 1101-1000 0111-0111 1000-0000 0101-1111

Cyclone IV devices receive configuration data on DATA[0] and the clock is received on DCLK. Data is latched into the device on the rising edge of DCLK. Data is continuously clocked into the target device until CONF\_DONE goes high and the device enters initialization state.

Two DCLK falling edges are required after CONF\_DONE goes high to begin the initialization of the device.

INIT\_DONE is released and pulled high when initialization is complete. The external host device must be able to detect this low-to-high transition which signals the device has entered user mode. When initialization is complete, the device enters user mode. In user mode, the user I/O pins no longer have weak pull-up resistors and function as assigned in your design.

## **FPP Configuration Timing**

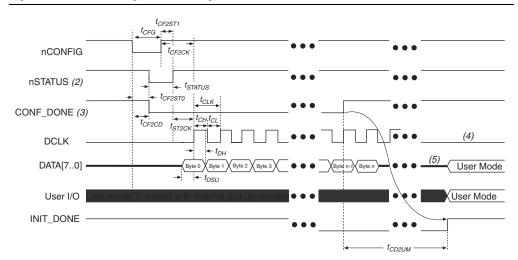

Figure 8–22 shows the timing waveform for the FPP configuration when using an external host.

### Notes to Figure 8-22:

- (1) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and  $CONF_DONE$  are at logic-high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (2) After power up, the Cyclone IV device holds  ${\tt nSTATUS}$  low during POR delay.

- (3) After power up, before and during configuration,  $CONF_DONE$  is low.

- (4) Do not leave DCLK floating after configuration. It must be driven high or low, whichever is more convenient.

- (5) DATA [7..0] is available as a user I/O pin after configuration; the state of the pin depends on the dual-purpose pin settings.

Table 8–13 lists the FPP configuration timing parameters for Cyclone IV devices.

Table 8–13. FPP Timing Parameters for Cyclone IV Devices (Part 1 of 2)

| 0hal                | Deventer                                        | Minimum Cyclone IV <sup>(1)</sup> Cyclone IV E <sup>(2)</sup> |     | Maxin                                                 | Unit |    |

|---------------------|-------------------------------------------------|---------------------------------------------------------------|-----|-------------------------------------------------------|------|----|

| Symbol              | Parameter                                       |                                                               |     | Cyclone IV <sup>(1)</sup> Cyclone IV E <sup>(2)</sup> |      |    |

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low                    | _                                                             | -   | 50                                                    | ns   |    |

| t <sub>CF2ST0</sub> | nCONFIG <b>low to</b><br>nSTATUS <b>low</b>     | _                                                             | -   | 50                                                    | ns   |    |

| t <sub>CFG</sub>    | nCONFIG low pulse width                         | 50                                                            | 00  | _                                                     | ns   |    |

| t <sub>status</sub> | nSTATUS low pulse width                         | 4                                                             | 5   | 230                                                   | μs   |    |

| t <sub>CF2ST1</sub> | nCONFIG high to<br>nSTATUS high                 | _                                                             | -   | 230 (4)                                               |      | μs |

| t <sub>CF2CK</sub>  | nCONFIG high to<br>first rising edge on<br>DCLK | 230                                                           | (3) | _                                                     |      |    |

The remote system upgrade status register is updated by the dedicated error monitoring circuitry after an error condition, but before the factory configuration is loaded.

| <b>Reconfiguration Error/Trigger</b> | Control Register Setting In Remote Update |  |  |

|--------------------------------------|-------------------------------------------|--|--|

| nCONFIG reset                        | All bits are 0                            |  |  |

| nSTATUS <b>error</b>                 | All bits are 0                            |  |  |

| CORE triggered reconfiguration       | Update register                           |  |  |

| CRC error                            | All bits are 0                            |  |  |

| Wd time out                          | All bits are 0                            |  |  |

Table 8–26. Control Register Contents After an Error or Reconfiguration Trigger Condition

### **User Watchdog Timer**

The user watchdog timer prevents a faulty application configuration from indefinitely stalling the device. The system uses the timer to detect functional errors after an application configuration is successfully loaded into the Cyclone IV device.

The user watchdog timer is a counter that counts down from the initial value loaded into the remote system upgrade control register by the factory configuration. The counter is 29 bits wide and has a maximum count value of 2<sup>29</sup>. When specifying the user watchdog timer value, specify only the most significant 12 bits. The remote system upgrade circuitry appends 17'b1000 to form the 29-bits value for the watchdog timer. The granularity of the timer setting is 2<sup>17</sup> cycles. The cycle time is based on the frequency of the 10-MHz internal oscillator or CLKUSR (maximum frequency of 40 MHz).

Table 8–27 lists the operating range of the 10-MHz internal oscillator.

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5       | 6.5     | 10      | MHz  |

The user watchdog timer begins counting after the application configuration enters device user mode. This timer must be periodically reloaded or reset by the application configuration before the timer expires by asserting RU\_nRSTIMER. If the application configuration does not reload the user watchdog timer before the count expires, a time-out signal is generated by the remote system upgrade dedicated circuitry. The time-out signal tells the remote system upgrade circuitry to set the user watchdog timer status bit (Wd) in the remote system upgrade status register and reconfigures the device by loading the factory configuration.

To allow the remote system upgrade dedicated circuitry to reset the watchdog timer, you must assert the RU\_nRSTIMER signal active for a minimum of 250 ns. This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE megafunction high for a minimum of 250 ns.

Errors during configuration are detected by the CRC engine. Functional errors must not exist in the factory configuration because it is stored and validated during production and is never updated remotely.

## 9. SEU Mitigation in Cyclone IV Devices

This chapter describes the cyclical redundancy check (CRC) error detection feature in user mode and how to recover from soft errors.

Configuration error detection is supported in all Cyclone<sup>®</sup> IV devices including Cyclone IV GX devices, Cyclone IV E devices with 1.0-V core voltage, and Cyclone IV E devices with 1.2-V core voltage. However, user mode error detection is only supported in Cyclone IV GX devices and Cyclone IV E devices with 1.2-V core voltage.

Dedicated circuitry built into Cyclone IV devices consists of a CRC error detection feature that can optionally check for a single-event upset (SEU) continuously and automatically.

In critical applications used in the fields of avionics, telecommunications, system control, medical, and military applications, it is important to be able to:

- Confirm the accuracy of the configuration data stored in an FPGA device

- Alert the system to an occurrence of a configuration error

Using the CRC error detection feature for Cyclone IV devices does not impact fitting or performance.

This chapter contains the following sections:

- "Configuration Error Detection" on page 9–1

- "User Mode Error Detection" on page 9–2

- "Automated SEU Detection" on page 9–3

- "CRC\_ERROR Pin" on page 9–3

- "Error Detection Block" on page 9–4

- "Error Detection Timing" on page 9–5

- "Software Support" on page 9–6

- "Recovering from CRC Errors" on page 9–9

## **Configuration Error Detection**

Configuration error detection is available in all Cyclone IV devices including Cyclone IV GX devices, Cyclone IV E devices with 1.0-V core voltage, and Cyclone IV E devices with 1.2-V core voltage.

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

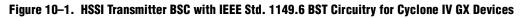

## IEEE Std. 1149.6 Boundary-Scan Register

The boundary-scan cell (BSC) for HSSI transmitters ( $GXB_TX[p,n]$ ) and receivers ( $GXB_RX[p,n]$ ) in Cyclone IV GX devices are different from the BSCs for I/O pins.

Figure 10–1 shows the Cyclone IV GX HSSI transmitter boundary-scan cell.

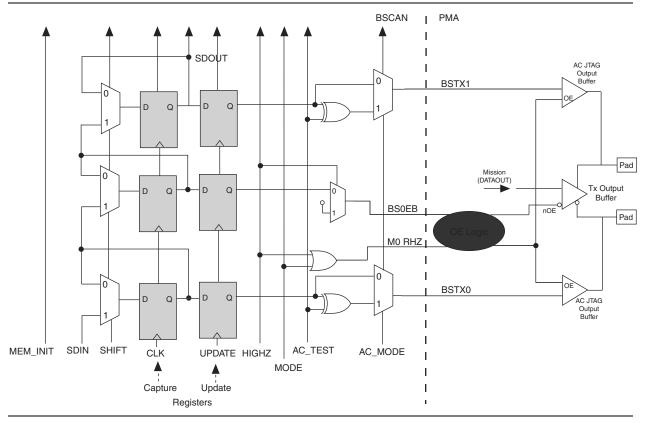

After updating the word boundary, word aligner status signals (rx\_syncstatus and rx\_patterndetect) are driven high for one parallel clock cycle synchronous to the most significant byte of the word alignment pattern. The rx\_syncstatus and rx\_patterndetect signals have the same latency as the datapath and are forwarded to the FPGA fabric to indicate the word aligner status. Any word alignment pattern received thereafter in the same word boundary causes only the rx\_patterndetect signal to go high for one clock cycle.

Figure 1–17 shows the manual alignment mode word aligner operation in 10-bit data width mode. In this example, a /K28.5/ (10'b0101111100) is specified as the word alignment pattern.

The word aligner aligns to the /K28.5/ alignment pattern (red) in cycle *n* because the rx\_enapatternalign signal is asserted high. The rx\_syncstatus signal goes high for one clock cycle indicating alignment to a new word boundary. The rx\_patterndetect signal also goes high for one clock cycle to indicate initial word alignment.

At time n + 1, the rx\_enapatternalign signal is deasserted to instruct the word aligner to lock the current word boundary.

The alignment pattern is detected again (green) in a new word boundary across cycles n + 2 and n + 3. The word aligner does not align to this new word boundary because the rx\_enapatternalign signal is held low.

The /K28.5/ word alignment pattern is detected again (blue) in the current word boundary during cycle n + 5 causing the rx\_patterndetect signal to go high for one parallel clock cycle.

Figure 1–17. Word Aligner in 10-bit Manual Alignment Mode

If the word alignment pattern is known to be unique and does not appear between word boundaries, you can hold the rx\_enapatternalign signal constantly high because there is no possibility of false word alignment. If there is a possibility of the word alignment pattern occurring across word boundaries, you must control the rx\_enapatternalign signal to lock the word boundary after the desired word alignment is achieved to avoid re-alignment to an incorrect word boundary.

### Table 1–21. XGMII Character to PCS Code Groups Mapping (Part 2 of 2)

| XGMII TXC <sup>(1)</sup> | XGMII TXD <sup>(2),</sup> (3) | PCS Code Group | Description             |

|--------------------------|-------------------------------|----------------|-------------------------|

| 1                        | Any other value               | K30.7          | Invalid XGMII character |

#### Notes to Table 1-21:

(2) Equivalent to 8-bit input data to 8B/10B encoder.

(3) The values in XGMII TXD column are in hexadecimal.

8B/10B decoder in the receiver datapath maps received PCS code groups into specific 8-bit XGMII codes as listed in Table 1–22.

| XGMII RXC <sup>(1)</sup> | XGMII RXD <sup>(2), (3)</sup> | PCS Code Group         | Description              |

|--------------------------|-------------------------------|------------------------|--------------------------|

| 0                        | 00 through FF                 | Dxx,y                  | Normal data transmission |

| 1                        | 07                            | K28.0, K28.3, or K28.5 | Idle in   I              |

| 1                        | 07                            | K28.5                  | Idle in   T              |

| 1                        | 9C                            | K28.4                  | Sequence                 |

| 1                        | FB                            | K27.7                  | Start                    |

| 1                        | FD                            | K29.7                  | Terminate                |

| 1                        | FE                            | K30.7                  | Error                    |

| 1                        | FE                            | Invalid code group     | Received code group      |

#### Notes to Table 1-22:

(1) Equivalent to rx\_ctrlenable port.

(2) Equivalent to 8-bit input data to 8B/10B encoder.

(3) The values in XGMII RXD column are in hexadecimal.

### **Channel Deskewing**

The deskew FIFO in each of the four lanes expects to receive /A/ code group simultaneously on all four channels during the inter-packet gap, as required by XAUI protocol. The skew introduced in the physical medium and the receiver channels might cause the /A/ code group to be received misaligned with respect to each other.

The deskew FIFO works to align the /A/ code group across the four channels, which operation is compliant to the PCS deskew state machine diagram specified in clause 48 of the IEEE P802.3ae specification. The deskew operation begins after link synchronization is achieved on all four channels as indicated by the word aligner in each channel. The following are the deskew FIFO operations:

- Until the first /A/ code group is received, the deskew FIFO read and write pointers in each channel are not incremented.

- After the first /A/ code group is received, the write pointer starts incrementing for each word received but the read pointer is frozen.

- When all the four channels received the /A/ code group within 10 recovered clock cycles of each other, the read pointer of all four deskew FIFOs is released simultaneously, aligning the /A/ code group of all four channels in a column.

<sup>(1)</sup> Equivalent to tx\_ctrlenable port.

| Port Name                     | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reconfig_address<br>_out[50]  | Output           | This signal is always available for you to select in the <b>Channel reconfiguration</b> screen. This signal is applicable only in the dynamic reconfiguration modes grouped under <b>Channel reconfiguration mode</b> including <b>channel interface</b> and <b>Use RX local divider</b> option.                                                                                                                                     |

|                               |                  | This signal represents the current address used by the ALTGX_RECONFIG instance when writing the <b>.mif</b> into the transceiver channel. This signal increments by 1, from 0 to the last address, then starts at 0 again. You can use this signal to indicate the end of all the <b>.mif</b> write transactions (reconfig_address_out[50] changes from the last address to 0 at the end of all the <b>.mif</b> write transactions). |

| reconfig_address<br>_en       | Output           | This is an optional signal you can select in the <b>Channel reconfiguration</b> screen. This signal is applicable only in dynamic reconfiguration modes grouped under the <b>Channel reconfiguration</b> option.                                                                                                                                                                                                                     |

|                               |                  | The dynamic reconfiguration controller asserts reconfig_address_en to indicate that reconfig_address_out [50] has changed. This signal is asserted only after the dynamic reconfiguration controller completes writing one 16-bit word of the <b>.mif</b> .                                                                                                                                                                          |

| reset_reconfig_<br>address    | Input            | This is an optional signal you can select in the <b>Channel reconfiguration</b> screen. This signal is applicable only in dynamic reconfiguration modes grouped under the <b>Channel reconfiguration</b> option.                                                                                                                                                                                                                     |

|                               |                  | Enable this signal and assert it for one reconfig_clk clock cycle if you want to reset the reconfiguration address used by the ALTGX_RECONFIG instance during reconfiguration.                                                                                                                                                                                                                                                       |

| reconfig_data<br>[150]        | Input            | This signal is applicable only in the dynamic reconfiguration modes grouped under the <b>Channel reconfiguration</b> option. This is a 16-bit word carrying the reconfiguration information. It is stored in a <b>.mif</b> that you must generate. The ALTGX_RECONFIG instance requires that you provide reconfig_data [150] on every <b>.mif</b> write transaction using the write_all signal.                                      |

| reconfig_reset <sup>(4)</sup> | Input            | You can use this signal to reset all the reconfiguration process in <b>Channel reconfiguration</b> mode. Asserting this port will reset all the register in the reconfiguration controller logics. This port only shows up in <b>Channel reconfiguration</b> mode.                                                                                                                                                                   |

|                               |                  | If you are feeding into this port, synchronize the reset signal to the $\tt reconfig_clk$ domain.                                                                                                                                                                                                                                                                                                                                    |

| channel_reconfig<br>_done     | Output           | This signal goes high to indicate that the dynamic reconfiguration controller has finished writing all the words of the <b>.mif</b> . The channel_reconfig_done signal is automatically deasserted at the start of a new dynamic reconfiguration write sequence. This signal is applicable only in channel reconfiguration mode.                                                                                                     |

### Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 7 of 7)

Notes to Table 3-2:

(1) Not all combinations of input bits are legal values.

(2) This setting is required for compliance to PCI Express® (PIPE) functional mode.

(3) PLL reconfiguration is performed using ALTPLL\_RECONFIG controller. Hence it is not selected through the reconfig\_mode\_sel[2..0] port.

(4) reconfig\_reset will not restart the offset cancellation operation. Offset cancellation only occurs one time after power up and does not occur when subsequent reconfig\_reset is asserted.

## **Offset Cancellation Feature**

The Cyclone IV GX devices provide an offset cancellation circuit per receiver channel to counter the offset variations due to process, voltage, and temperature (PVT). These variations create an offset in the analog circuit voltages, pushing them out of the expected range. In addition to reconfiguring the transceiver channel, the dynamic reconfiguration controller performs offset cancellation on all receiver channels connected to it on power up.

| Chapter Revision Dates  | v      |

|-------------------------|--------|

| Additional Information  |        |

| How to Contact Altera   | Info-1 |

| Typographic Conventions | Info–1 |

## Section I. Device Datasheet

## Chapter 1. Cyclone IV Device Datasheet

| Operating Conditions                              | 1–1    |

|---------------------------------------------------|--------|

| Absolute Maximum Ratings                          | 1–2    |

| Maximum Allowed Overshoot or Undershoot Voltage   |        |

| Recommended Operating Conditions                  |        |

| ESD Performance                                   |        |

| DC Characteristics                                | 1–7    |

| Supply Current                                    |        |

| Bus Hold                                          | 1–7    |

| OCT Specifications                                | 1–8    |

| Pin Capacitance                                   |        |

| Internal Weak Pull-Up and Weak Pull-Down Resistor | . 1–11 |

| Hot-Socketing                                     | . 1–11 |

| Schmitt Trigger Input                             |        |

| I/O Standard Specifications                       | . 1–12 |

| Power Consumption                                 |        |

| Switching Characteristics                         | . 1–16 |

| Transceiver Performance Specifications            | . 1–17 |

| Core Performance Specifications                   | . 1–23 |

| Clock Tree Specifications                         |        |

| PLL Specifications                                | . 1–24 |

| Embedded Multiplier Specifications                | . 1–26 |

| Memory Block Specifications                       | . 1–26 |

| Configuration and JTAG Specifications             | . 1–26 |

| Periphery Performance                             |        |

| High-Speed I/O Specifications                     |        |

| External Memory Interface Specifications          | . 1–32 |

| Duty Cycle Distortion Specifications              | . 1–33 |

| OCT Calibration Timing Specification              | . 1–33 |

| IOE Programmable Delay                            | . 1–34 |

| I/O Timing                                        | . 1–37 |

| Glossary                                          |        |

| Document Revision History                         | . 1–42 |

This chapter provides additional information about the document and Altera.

## **About this Handbook**

This handbook provides comprehensive information about the Altera<sup>®</sup> Cyclone<sup>®</sup> IV family of devices.

## **How to Contact Altera**

To locate the most up-to-date information about Altera products, refer to the following table.

| Contact <sup>(1)</sup>         | <b>Contact Method</b> | Address                   |

|--------------------------------|-----------------------|---------------------------|

| Technical support              | Website               | www.altera.com/support    |

| Technical training             | Website               | www.altera.com/training   |

| recinical training             | Email                 | custrain@altera.com       |

| Product literature             | Website               | www.altera.com/literature |

| Nontechnical support (general) | Email                 | nacomp@altera.com         |

| (software licensing)           | Email                 | authorization@altera.com  |

Note to Table:

(1) You can also contact your local Altera sales office or sales representative.

## **Typographic Conventions**

The following table shows the typographic conventions this document uses.

| Visual Cue                                | Meaning                                                                                                                                                                                                                       |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bold Type with Initial Capital<br>Letters | Indicate command names, dialog box titles, dialog box options, and other GUI labels. For example, <b>Save As</b> dialog box. For GUI elements, capitalization matches the GUI.                                                |  |

| bold type                                 | Indicates directory names, project names, disk drive names, file names, file name extensions, software utility names, and GUI labels. For example, <b>\qdesigns</b> directory, <b>D:</b> drive, and <b>chiptrip.gdf</b> file. |  |

| Italic Type with Initial Capital Letters  | Indicate document titles. For example, Stratix IV Design Guidelines.                                                                                                                                                          |  |

|                                           | Indicates variables. For example, $n + 1$ .                                                                                                                                                                                   |  |

| italic type                               | Variable names are enclosed in angle brackets (< >). For example, <i><file name=""></file></i> and <i><project name="">.pof</project></i> file.                                                                               |  |

| Initial Capital Letters                   | Indicate keyboard keys and menu names. For example, the Delete key and the Options menu.                                                                                                                                      |  |

| "Subheading Title"                        | Quotation marks indicate references to sections in a document and titles of Quartus II Help topics. For example, "Typographic Conventions."                                                                                   |  |

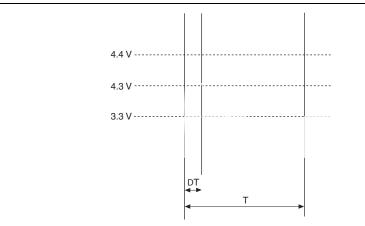

A DC signal is equivalent to 100% duty cycle. For example, a signal that overshoots to 4.3 V can only be at 4.3 V for 65% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 65/10ths of a year.

| Symbol                             | Parameter | Condition (V)         | Overshoot Duration as % of High Time | Unit |

|------------------------------------|-----------|-----------------------|--------------------------------------|------|

| V <sub>i</sub> AC Input<br>Voltage |           | V <sub>1</sub> = 4.20 | 100                                  | %    |

|                                    |           | V <sub>1</sub> = 4.25 | 98                                   | %    |

|                                    |           | $V_1 = 4.30$          | 65                                   | %    |

|                                    |           | V <sub>1</sub> = 4.35 | 43                                   | %    |

|                                    |           | $V_1 = 4.40$          | 29                                   | %    |

|                                    | Voltago   | $V_1 = 4.45$          | 20                                   | %    |

|                                    |           | $V_1 = 4.50$          | 13                                   | %    |

|                                    |           | V <sub>1</sub> = 4.55 | 9                                    | %    |

|                                    |           | $V_1 = 4.60$          | 6                                    | %    |

Table 1–2. Maximum Allowed Overshoot During Transitions over a 10-Year Time Frame for Cyclone IV Devices

Figure 1–1 shows the methodology to determine the overshoot duration. The overshoot voltage is shown in red and is present on the input pin of the Cyclone IV device at over 4.3 V but below 4.4 V. From Table 1–2, for an overshoot of 4.3 V, the percentage of high time for the overshoot can be as high as 65% over a 10-year period. Percentage of high time is calculated as ([delta T]/T) × 100. This 10-year period assumes that the device is always turned on with 100% I/O toggle rate and 50% duty cycle signal. For lower I/O toggle rates and situations in which the device is in an idle state, lifetimes are increased.