## Intel - EP4CE6E22C8N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                  |

|--------------------------------|---------------------------------------------------------|

| Number of LABs/CLBs            | 392                                                     |

| Number of Logic Elements/Cells | 6272                                                    |

| Total RAM Bits                 | 276480                                                  |

| Number of I/O                  | 91                                                      |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 144-LQFP Exposed Pad                                    |

| Supplier Device Package        | 144-EQFP (20x20)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce6e22c8n |

|                                |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1–2 lists Cyclone IV GX device resources.

| Resources                            | EP4CGX15 | EP4CGX22         | EP4CGX30 | EP4CGX30<br>(2)   | EP4CGX50          | EP4CGX75          | EP4CGX110         | EP4CGX150     |

|--------------------------------------|----------|------------------|----------|-------------------|-------------------|-------------------|-------------------|---------------|

| Logic elements (LEs)                 | 14,400   | 21,280           | 29,440   | 29,440            | 49,888            | 73,920            | 109,424           | 149,760       |

| Embedded memory (Kbits)              | 540      | 756              | 1,080    | 1,080             | 2,502             | 4,158             | 5,490             | 6,480         |

| Embedded 18 × 18 multipliers         | 0        | 40               | 80       | 80                | 140               | 198               | 280               | 360           |

| General purpose PLLs                 | 1        | 2                | 2        | 4 (4)             | 4 (4)             | 4 (4)             | 4 (4)             | 4 <i>(4)</i>  |

| Multipurpose PLLs                    | 2 (5)    | 2 <sup>(5)</sup> | 2 (5)    | 2 <sup>(5)</sup>  | 4 (5)             | 4 (5)             | 4 (5)             | 4 (5)         |

| Global clock networks                | 20       | 20               | 20       | 30                | 30                | 30                | 30                | 30            |

| High-speed transceivers (6)          | 2        | 4                | 4        | 4                 | 8                 | 8                 | 8                 | 8             |

| Transceiver maximum data rate (Gbps) | 2.5      | 2.5              | 2.5      | 3.125             | 3.125             | 3.125             | 3.125             | 3.125         |

| PCIe (PIPE) hard IP blocks           | 1        | 1                | 1        | 1                 | 1                 | 1                 | 1                 | 1             |

| User I/O banks                       | g (7)    | g (7)            | g (7)    | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <i>(8)</i> |

| Maximum user I/O <sup>(9)</sup>      | 72       | 150              | 150      | 290               | 310               | 310               | 475               | 475           |

Table 1–2. Resources for the Cyclone IV GX Device Family

Notes to Table 1-2:

(1) Applicable for the F169 and F324 packages.

(2) Applicable for the F484 package.

(3) Only two multipurpose PLLs for F484 package.

(4) Two of the general purpose PLLs are able to support transceiver clocking. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(5) You can use the multipurpose PLLs for general purpose clocking when they are not used to clock the transceivers. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(6) If PCIe ×1, you can use the remaining transceivers in a quad for other protocols at the same or different data rates.

(7) Including one configuration I/O bank and two dedicated clock input I/O banks for HSSI reference clock input.

(8) Including one configuration I/O bank and four dedicated clock input I/O banks for HSSI reference clock input.

(9) The user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins are not included in the pin count.

## I/O Features

Cyclone IV device I/O supports programmable bus hold, programmable pull-up resistors, programmable delay, programmable drive strength, programmable slew-rate control to optimize signal integrity, and hot socketing. Cyclone IV devices support calibrated on-chip series termination (Rs OCT) or driver impedance matching (Rs) for single-ended I/O standards. In Cyclone IV GX devices, the high-speed transceiver I/Os are located on the left side of the device. The top, bottom, and right sides can implement general-purpose user I/Os.

Table 1–8 lists the I/O standards that Cyclone IV devices support.

| Туре             | I/O Standard                                               |

|------------------|------------------------------------------------------------|

| Single-Ended I/O | LVTTL, LVCMOS, SSTL, HSTL, PCI, and PCI-X                  |

| Differential I/O | SSTL, HSTL, LVPECL, BLVDS, LVDS, mini-LVDS, RSDS, and PPDS |

Table 1–8. I/O Standards Support for the Cyclone IV Device Family

The LVDS SERDES is implemented in the core of the device using logic elements.

• For more information, refer to the *I/O Features in Cyclone IV Devices* chapter.

## **Clock Management**

Cyclone IV devices include up to 30 global clock (GCLK) networks and up to eight PLLs with five outputs per PLL to provide robust clock management and synthesis. You can dynamically reconfigure Cyclone IV device PLLs in user mode to change the clock frequency or phase.

Cyclone IV GX devices support two types of PLLs: multipurpose PLLs and generalpurpose PLLs:

- Use multipurpose PLLs for clocking the transceiver blocks. You can also use them for general-purpose clocking when they are not used for transceiver clocking.

- Use general purpose PLLs for general-purpose applications in the fabric and periphery, such as external memory interfaces. Some of the general purpose PLLs can support transceiver clocking.

**\*** For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

## **External Memory Interfaces**

Cyclone IV devices support SDR, DDR, DDR2 SDRAM, and QDRII SRAM interfaces on the top, bottom, and right sides of the device. Cyclone IV E devices also support these interfaces on the left side of the device. Interfaces may span two or more sides of the device to allow more flexible board design. The Altera® DDR SDRAM memory interface solution consists of a PHY interface and a memory controller. Altera supplies the PHY IP and you can use it in conjunction with your own custom memory controller or an Altera-provided memory controller. Cyclone IV devices support the use of error correction coding (ECC) bits on DDR and DDR2 SDRAM interfaces. Table 4–1 lists the number of embedded multipliers and the multiplier modes that can be implemented in each Cyclone IV device.

| Device Family | Device    | Embedded<br>Multipliers | 9 × 9<br>Multipliers <sup>(1)</sup> | 18 × 18<br>Multipliers <sup>(1)</sup> |

|---------------|-----------|-------------------------|-------------------------------------|---------------------------------------|

|               | EP4CGX15  | 0                       | 0                                   | 0                                     |

|               | EP4CGX22  | 40                      | 80                                  | 40                                    |

|               | EP4CGX30  | 80                      | 160                                 | 80                                    |

| Cyclone IV GX | EP4CGX50  | 140                     | 280                                 | 140                                   |

|               | EP4CGX75  | 198                     | 396                                 | 198                                   |

|               | EP4CGX110 | 280                     | 560                                 | 280                                   |

|               | EP4CGX150 | 360                     | 720                                 | 360                                   |

|               | EP4CE6    | 15                      | 30                                  | 15                                    |

|               | EP4CE10   | 23                      | 46                                  | 23                                    |

|               | EP4CE15   | 56                      | 112                                 | 56                                    |

|               | EP4CE22   | 66                      | 132                                 | 66                                    |

| Cyclone IV E  | EP4CE30   | 66                      | 132                                 | 66                                    |

|               | EP4CE40   | 116                     | 232                                 | 116                                   |

|               | EP4CE55   | 154                     | 308                                 | 154                                   |

|               | EP4CE75   | 200                     | 400                                 | 200                                   |

|               | EP4CE115  | 266                     | 532                                 | 266                                   |

Table 4–1. Number of Embedded Multipliers in Cyclone IV Devices

Note to Table 4-1:

(1) These columns show the number of  $9 \times 9$  or  $18 \times 18$  multipliers for each device.

In addition to the embedded multipliers in Cyclone IV devices, you can implement soft multipliers by using the M9K memory blocks as look-up tables (LUTs). The LUTs contain partial results from the multiplication of input data with coefficients that implement variable depth and width high-performance soft multipliers for low-cost, high-volume DSP applications. The availability of soft multipliers increases the number of available multipliers in the device.

- **For more information about M9K memory blocks, refer to the** *Memory Blocks in Cyclone IV Devices* chapter.

- **\*** For more information about soft multipliers, refer to *AN 306: Implementing Multipliers in FPGA Devices*.

## Architecture

Each embedded multiplier consists of the following elements:

- Multiplier stage

- Input and output registers

- Input and output interfaces

| GCLK Network Clock |   |   |   |              |              |              |   |              | GC           | LK N         | etwo         | rks          |              |              |              |              |              |              |              |              |

|--------------------|---|---|---|--------------|--------------|--------------|---|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Sources            | 0 | 1 | 2 | 3            | 4            | 5            | 6 | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           |

| DPCLK2 (4)         |   |   |   |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |              |              |

| CDPCLK1, Or        | — | — | — | $\checkmark$ | $\checkmark$ | —            | _ | —            | —            | _            | —            | —            | —            | —            |              | —            | —            | —            | —            |              |

| CDPCLK2 (2), (5)   |   |   |   |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |              |              |

| DPCLK5 (4)         |   |   |   |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |              |              |

| DPCLK7 (2)         |   | _ | _ | _            |              | $\checkmark$ |   | _            | _            |              |              | _            | _            | _            |              | _            | _            | _            | _            |              |

| DPCLK4 (4)         |   |   |   |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |              |              |

| DPCLK6 (2)         |   | _ | _ | _            |              | _            | ~ | _            | _            |              | _            | _            | _            | _            |              | _            | _            | _            | _            | _            |

| DPCLK6 (4)         |   |   |   |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |              |              |

| CDPCLK5, Or        | — | — | — | —            | —            | —            | _ | $\checkmark$ | —            | _            | —            | —            | —            | —            |              | —            | —            | —            | —            |              |

| CDPCLK6 (2), (5)   |   |   |   |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |              |              |

| DPCLK3 (4)         |   |   |   |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |              |              |

| CDPCLK4, Or        | — | — | — | —            | —            | —            | — |              | $\checkmark$ | $\checkmark$ | —            | —            | —            |              |              | —            |              | —            |              |              |

| CDPCLK3 (2), (5)   |   |   |   |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |              |              |

| DPCLK8             | — | — | — | —            | —            | —            | — | —            | —            | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | _            |

| DPCLK11            | — | — | — | —            | _            | _            | _ | _            | _            | _            | —            | $\checkmark$ | —            | _            |              | —            | _            | _            | _            |              |

| DPCLK9             | — | — | — | —            | —            | —            | — | —            | —            | —            | —            | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | _            |

| DPCLK10            | — | — | — | —            | —            | —            | — | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            | —            |

| DPCLK5             | — | — | — | —            | —            | —            | — | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | —            | —            | —            |

| DPCLK2             | — | — | — | —            | —            | —            | — | —            | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | —            | —            |

| DPCLK4             | — | — | — | —            | —            | —            | — | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | —            |

| DPCLK3             | — | — | — | —            | —            | —            | — | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ |

### Table 5–3. GCLK Network Connections for Cyclone IV E Devices <sup>(1)</sup> (Part 3 of 3)

#### Notes to Table 5-3:

(1) EP4CE6 and EP4CE10 devices only have GCLK networks 0 to 9.

(2) These pins apply to all Cyclone IV E devices except EP4CE6 and EP4CE10 devices.

(3) EP4CE6 and EP4CE10 devices only have PLL\_1 and PLL\_2.

(4) This pin applies only to EP4CE6 and EP4CE10 devices.

(5) Only one of the two CDPCLK pins can feed the clock control block. You can use the other pin as a regular I/O pin.

## **Programmable Bandwidth**

The PLL bandwidth is the measure of the PLL's ability to track the input clock and its associated jitter. PLLs of Cyclone IV devices provide advanced control of the PLL bandwidth using the programmable characteristics of the PLL loop, including loop filter and charge pump. The closed-loop gain 3-dB frequency in the PLL determines the PLL bandwidth. The bandwidth is approximately the unity gain point for open loop PLL response.

## **Phase Shift Implementation**

Phase shift is used to implement a robust solution for clock delays in Cyclone IV devices. Phase shift is implemented with a combination of the VCO phase output and the counter starting time. The VCO phase output and counter starting time are the most accurate methods of inserting delays, because they are based only on counter settings that are independent of process, voltage, and temperature.

You can phase shift the output clocks from the PLLs of Cyclone IV devices in one of two ways:

- Fine resolution using VCO phase taps

- Coarse resolution using counter starting time

Fine resolution phase shifts are implemented by allowing any of the output counters (C[4..0]) or the M counter to use any of the eight phases of the VCO as the reference clock. This allows you to adjust the delay time with a fine resolution.

Equation 5–1 shows the minimum delay time that you can insert using this method.

### Equation 5–1. Fine Resolution Phase Shift

$f_{\text{fine}} = \frac{T_{VCO}}{8} = \frac{1}{8f_{VCO}} = \frac{N}{8Mf_{REF}}$

in which  $f_{\text{REF}}$  is the input reference clock frequency.

For example, if  $f_{\text{REF}}$  is 100 MHz, N = 1, and M = 8, then  $f_{\text{VCO}}$  = 800 MHz, and  $\Phi_{\text{fine}}$  = 156.25 ps. The PLL operating frequency defines this phase shift, a value that depends on reference clock frequency and counter settings.

Coarse resolution phase shifts are implemented by delaying the start of the counters for a predetermined number of counter clocks. Equation 5–2 shows the coarse phase shift.

## Equation 5–2. Coarse Resolution Phase Shift

$\Phi_{\text{coarse}} = \frac{C-1}{f_{VCO}} = \frac{(C-1)N}{Mf_{REF}}$

*C* is the count value set for the counter delay time (this is the initial setting in the PLL usage section of the compilation report in the Quartus II software). If the initial value is 1,  $C - 1 = 0^{\circ}$  phase shift.

|              |              |                     | V <sub>ccio</sub> Leve | el (in V) | C            | olumn I/O P | Row I/O Pins <sup>(1)</sup> |              |                  |

|--------------|--------------|---------------------|------------------------|-----------|--------------|-------------|-----------------------------|--------------|------------------|

| I/O Standard | Туре         | Standard<br>Support | Input                  | Output    | CLK,<br>DQS  | PLL_OUT     | User<br>I/O<br>Pins         | CLK,<br>DQS  | User I/O<br>Pins |

| LVPECL (7)   | Differential | —                   | 2.5                    | _         | $\checkmark$ | —           |                             | $\checkmark$ | —                |

### Table 6–3. Cyclone IV Devices Supported I/O Standards and Constraints (Part 3 of 3)

Notes to Table 6-3:

(1) Cyclone IV GX devices only support right I/O pins.

(2) The PCI-clamp diode must be enabled for 3.3-V/3.0-V LVTTL/LVCMOS.

(3) The Cyclone IV architecture supports the MultiVolt I/O interface feature that allows Cyclone IV devices in all packages to interface with I/O systems that have different supply voltages.

(4) Cyclone IV GX devices do not support 1.2-V V<sub>CCIO</sub> in banks 3 and 9. I/O pins in bank 9 are dual-purpose I/O pins that are used as configuration or GPIO pins. Configuration scheme is not support at 1.2 V, therefore bank 9 can not be powered up at 1.2-V V<sub>CCIO</sub>.

(5) Differential HSTL and SSTL outputs use two single-ended outputs with the second output programmed as inverted. Differential HSTL and SSTL inputs treat differential inputs as two single-ended HSTL and SSTL inputs and only decode one of them. Differential HSTL and SSTL are only supported on CLK pins.

(6) PPDS, mini-LVDS, and RSDS are only supported on output pins.

- (7) LVPECL is only supported on clock inputs.

- (8) Bus LVDS (BLVDS) output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses LVDS input buffer.

- (9) 1.2-V HSTL input is supported at both column and row I/Os regardless of Class I or Class II.

- (10) True LVDS, RSDS, and mini-LVDS I/O standards are supported in left and right I/O pins, while emulated LVDS, RSDS, and mini-LVDS I/O standards are supported in the top, bottom, and right I/O pins.

Cyclone IV devices support PCI and PCI-X I/O standards at 3.0-V V<sub>CCIO</sub>. The 3.0-V PCI and PCI-X I/O are fully compatible for direct interfacing with 3.3-V PCI systems without requiring any additional components. The 3.0-V PCI and PCI-X outputs meet the V<sub>IH</sub> and V<sub>IL</sub> requirements of 3.3-V PCI and PCI-X inputs with sufficient noise margin.

For more information about the 3.3/3.0/2.5-V LVTTL & LVCMOS multivolt I/O support, refer to AN 447: Interfacing Cyclone III and Cyclone IV Devices with 3.3/3.0/2.5-V LVTTL/LVCMOS I/O Systems.

## **Termination Scheme for I/O Standards**

This section describes recommended termination schemes for voltage-referenced and differential I/O standards.

The 3.3-V LVTTL, 3.0-V LVTTL and LVCMOS, 2.5-V LVTTL and LVCMOS, 1.8-V LVTTL and LVCMOS, 1.5-V LVCMOS, 1.2-V LVCMOS, 3.0-V PCI, and PCI-X I/O standards do not specify a recommended termination scheme per the JEDEC standard

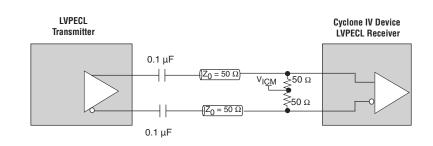

## **LVPECL I/O Support in Cyclone IV Devices**

The LVPECL I/O standard is a differential interface standard that requires a 2.5-V  $V_{CCIO}$ . This standard is used in applications involving video graphics, telecommunications, data communications, and clock distribution. Cyclone IV devices support the LVPECL input standard at the dedicated clock input pins only. The LVPECL receiver requires an external 100- $\Omega$  termination resistor between the two signals at the input buffer.

For the LVPECL I/O standard electrical specification, refer to the Cyclone IV Device Datasheet chapter.

AC coupling is required when the LVPECL common mode voltage of the output buffer is higher than the Cyclone IV devices LVPECL input common mode voltage.

Figure 6–18 shows the AC-coupled termination scheme. The  $50-\Omega$  resistors used at the receiver are external to the device. DC-coupled LVPECL is supported if the LVPECL output common mode voltage is in the Cyclone IV devices LVPECL input buffer specification (refer to Figure 6–19).

### Figure 6–18. LVPECL AC-Coupled Termination (1)

### Note to Figure 6–18:

(1) The LVPECL AC-coupled termination is applicable only when an Altera FPGA transmitter is used.

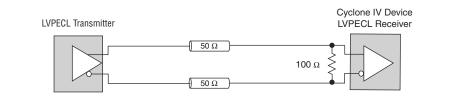

Figure 6–19 shows the LVPECL DC-coupled termination.

### Figure 6–19. LVPECL DC-Coupled Termination (1)

### Note to Figure 6–19:

(1) The LVPECL DC-coupled termination is applicable only when an Altera FPGA transmitter is used.

| Date          | Version | Changes                                                                                                             |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------|

|               |         | <ul> <li>Added Cyclone IV E devices information for the Quartus II software version 9.1 SP1<br/>release.</li> </ul> |

|               |         | ■ Updated Table 6–2, Table 6–3, and Table 6–10.                                                                     |

| February 2010 | 2.0     | ■ Updated "I/O Banks" section.                                                                                      |

| -             |         | ■ Added Figure 6–9.                                                                                                 |

|               |         | ■ Updated Figure 6–10 and Figure 6–11.                                                                              |

|               |         | ■ Added Table 6–4, Table 6–6, and Table 6–8.                                                                        |

| November 2009 | 1.0     | Initial release.                                                                                                    |

Table 6–12. Document Revision History (Part 2 of 2)

- 3. Click the **Configuration** tab.

- 4. Turn on Generate compressed bitstreams.

- 5. Click OK.

- 6. In the **Settings** dialog box, click **OK**.

You can enable compression when creating programming files from the **Convert Programming Files** dialog box. To enable compression, perform the following steps:

- 1. On the File menu, click Convert Programming Files.

- 2. Under **Output programming file**, select your desired file type from the **Programming file type** list.

- 3. If you select **Programmer Object File (.pof)**, you must specify the configuration device in the **Configuration device** list.

- 4. Under Input files to convert, select SOF Data.

- 5. Click Add File to browse to the Cyclone IV device SRAM object files (.sof).

- 6. In the **Convert Programming Files** dialog box, select the **.pof** you added to **SOF Data** and click **Properties**.

- 7. In the SOF File Properties dialog box, turn on the Compression option.

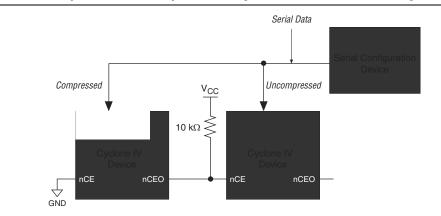

When multiple Cyclone IV devices are cascaded, you can selectively enable the compression feature for each device in the chain. Figure 8–1 shows a chain of two Cyclone IV devices. The first device has compression enabled and receives compressed bitstream from the configuration device. The second device has the compression feature disabled and receives uncompressed data. You can generate programming files for this setup in the **Convert Programming Files** dialog box.

Figure 8–1. Compressed and Uncompressed Configuration Data in the Same Configuration File

## **Configuration Requirement**

This section describes Cyclone IV device configuration requirement and includes the following topics:

- "Power-On Reset (POR) Circuit" on page 8–4

- "Configuration File Size" on page 8–4

- "Power Up" on page 8–6

resistors.

Default read mode of the supported parallel flash memory and all writes to the parallel flash memory are asynchronous. Both the parallel flash families support a synchronous read mode, with data supplied on the positive edge of DCLK.

The serial clock (DCLK) generated by Cyclone IV E devices controls the entire configuration cycle and provides timing for the parallel interface.

## **Multi-Device AP Configuration**

You can configure multiple Cyclone IV E devices using a single parallel flash. You can cascade multiple Cyclone IV E devices using the chip-enable (nCE) and chip-enable-out (nCEO) pins. The first device in the chain must have its nCE pin connected to GND. You must connect its nCEO pin to the nCE pin of the next device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the nCEO signal high to its V<sub>CCIO</sub> level to help the internal weak pull-up resistor. When the first device captures all its configuration data from the bitstream, it drives the nCEO pin low, enabling the next device in the chain. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in the chain is a Cyclone IV E device. The nCONFIG, nSTATUS, CONF\_DONE, DCLK, DATA[15..8], and DATA[7..0] pins of each device in the chain are connected (Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27).

The first Cyclone IV E device in the chain, as shown in Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27, is the configuration master device and controls the configuration of the entire chain. You must connect its MSEL pins to select the AP configuration scheme. The remaining Cyclone IV E devices are used as configuration slaves. You must connect their MSEL pins to select the FPP configuration scheme. Any other Altera device that supports FPP configuration can also be part of the chain as a configuration slave.

The following are the configurations for the DATA[15..0] bus in a multi-device AP configuration:

- Byte-wide multi-device AP configuration

- Word-wide multi-device AP configuration

The programming hardware or download cable then places the configuration data one bit at a time on the DATA [0] pin of the device. The configuration data is clocked into the target device until CONF\_DONE goes high. The CONF\_DONE pin must have an external  $10-k\Omega$  pull-up resistor for the device to initialize.

When you use a download cable, setting the **Auto-restart configuration after error** option does not affect the configuration cycle because you must manually restart configuration in the Quartus II software if an error occurs. Additionally, the **Enable user-supplied start-up clock (CLKUSR)** option has no effect on device initialization, because this option is disabled in the **.sof** when programming the device with the Quartus II Programmer and download cable. Therefore, if you turn on the **CLKUSR** option, you do not have to provide a clock on CLKUSR when you configure the device with the Quartus II Programmer and a download cable.

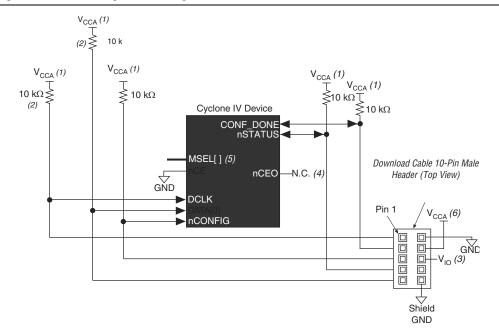

Figure 8–17 shows PS configuration for Cyclone IV devices with a download cable.

Figure 8–17. PS Configuration Using a Download Cable

#### Notes to Figure 8-17:

- (1) You must connect the pull-up resistor to the same supply voltage as the V<sub>CCA</sub> supply.

- (2) The pull-up resistors on DATA[0] and DCLK are only required if the download cable is the only configuration scheme used on your board. This is to ensure that DATA[0] and DCLK are not left floating after configuration. For example, if you also use a configuration device, the pull-up resistors on DATA[0] and DCLK are not required.

- (3) Pin 6 of the header is a V<sub>10</sub> reference voltage for the MasterBlaster output driver. V<sub>10</sub> must match the V<sub>CCA</sub> of the device. For this value, refer to the *MasterBlaster Serial/USB Communications Cable User Guide*. With the USB-Blaster, ByteBlaster II, ByteBlaster MV, and EthernetBlaster, this pin is a no connect.

- (4) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (5) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9 for PS configuration schemes. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (6) Power up the V<sub>CC</sub> of the ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5-V supply from V<sub>CCA</sub>. Third-party programmers must switch to 2.5 V. Pin 4 of the header is a V<sub>CC</sub> power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the *MasterBlaster Serial/USB Communications Cable User Guide*.

Figure 8–34 shows the control register bit positions. Table 8–23 defines the control register bit contents. The numbers in Figure 8–34 show the bit position of a setting in a register. For example, bit number 35 is the enable bit for the watchdog timer.

Figure 8–34. Remote System Upgrade Control Register

| 38   | 37       | 36      | 35    | 34   | 33     | 12        | 11    | 0        |

|------|----------|---------|-------|------|--------|-----------|-------|----------|

| Rsv2 | Cd_early | Osc_int | Wd_en | Rsv1 | Ru_add | ress[210] | Wd_ti | mer[110] |

Table 8–23. Remote System Upgrade Control Register Contents

| <b>Control Register Bit</b> | Value                                   | Definition                                                                                                                       |

|-----------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Wd_timer[110]               | 12'b00000000000                         | User watchdog time-out value (most significant 12 bits of 29-bit count value:<br>{Wd_timer[110],17'b1000})                       |

| Ru_address[210]             | 22'b00000000000000000000000000000000000 | Configuration address (most significant 22 bits of 24-bit<br>boot address value:<br>boot_address[23:0] = {Ru_address[210],2'b0}) |

| Rsv1                        | 1'b0                                    | Reserved bit                                                                                                                     |

| Wd_en                       | 1'b1                                    | User watchdog timer enable bit                                                                                                   |

| Osc_int (1)                 | 1'b1                                    | Internal oscillator as startup state machine clock enable bit                                                                    |

| Cd_early (1)                | 1'b1                                    | Early CONF_DONE check                                                                                                            |

| Rsv2                        | 1'b1                                    | Reserved bit                                                                                                                     |

#### Note to Table 8-23:

(1) Option bit for the application configuration.

When enabled, the early CONF\_DONE check (Cd\_early) option bit ensures that there is a valid configuration at the boot address specified by the factory configuration and that it is of the proper size. If an invalid configuration is detected or the CONF\_DONE pin is asserted too early, the device resets and then reconfigures the factory configuration image. The internal oscillator (as the startup state machine clock [Osc\_int] option bit) ensures a functional startup clock to eliminate the hanging of startup. When all option bits are turned on, they provide complete coverage for the programming and startup portions of the application configuration. Altera recommends turning on both the Cd early and Osc int option bits.

The Cd\_early and Osc\_int option bits for the application configuration must be turned on by the factory configuration.

### **Remote System Upgrade Status Register**

The remote system upgrade status register specifies the reconfiguration trigger condition. The various trigger and error conditions include:

- Cyclical redundancy check (CRC) error during application configuration

- nSTATUS assertion by an external device due to an error

- Cyclone IV device logic array triggers a reconfiguration cycle, possibly after downloading a new application configuration image

## **Error Detection Block**

Table 9–3 lists the types of CRC detection to check the configuration bits.

Table 9–3. Types of CRC Detection to Check the Configuration Bits

| First Type of CRC Detection                                                                  | Second Type of CRC Detection                                                                                                                                                               |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>CRAM error checking ability (32-bit CRC)</li> </ul>                                 | <ul> <li>16-bit CRC embedded in every configuration data frame.</li> </ul>                                                                                                                 |

| during user mode, for use by the CRC_ERROR pin.                                              | <ul> <li>During configuration, after a frame of data is loaded into the device, the<br/>pre-computed CRC is shifted into the CRC circuitry.</li> </ul>                                     |

| <ul> <li>There is only one 32-bit CRC value. This value covers all the CRAM data.</li> </ul> | <ul> <li>Simultaneously, the CRC value for the data frame shifted-in is calculated.<br/>If the pre-computed CRC and calculated CRC values do not match,<br/>nSTATUS is set low.</li> </ul> |

|                                                                                              | <ul> <li>Every data frame has a 16-bit CRC. Therefore, there are many 16-bit CRC values for the whole configuration bit stream.</li> </ul>                                                 |

|                                                                                              | <ul> <li>Every device has a different length of configuration data frame.</li> </ul>                                                                                                       |

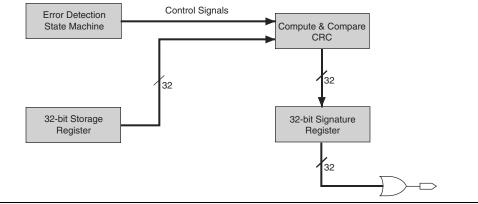

This section focuses on the first type—the 32-bit CRC when the device is in user mode.

## **Error Detection Registers**

There are two sets of 32-bit registers in the error detection circuitry that store the computed CRC signature and pre-calculated CRC value. A non-zero value on the signature register causes the CRC\_ERROR pin to set high.

Figure 9–1 shows the block diagram of the error detection block and the two related 32-bit registers: the signature register and the storage register.

Figure 9–1. Error Detection Block Diagram

| Visual Cue                               | Meaning                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input. The suffix n denotes an active-low signal. For example, resetn.                 |

| Courier type                             | Indicates command line commands and anything that must be typed exactly as it appears. For example, c:\qdesigns\tutorial\chiptrip.gdf.                                                 |

|                                          | Also indicates sections of an actual file, such as a Report File, references to parts of files (for example, the AHDL keyword SUBDESIGN), and logic function names (for example, TRI). |

| 4                                        | An angled arrow instructs you to press the Enter key.                                                                                                                                  |

| 1., 2., 3., and<br>a., b., c., and so on | Numbered steps indicate a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                          |

|                                          | Bullets indicate a list of items when the sequence of the items is not important.                                                                                                      |

| LP                                       | The hand points to information that requires special attention.                                                                                                                        |

| ?                                        | The question mark directs you to a software help system with related information.                                                                                                      |

|                                          | The feet direct you to another document or website with related information.                                                                                                           |

| <b>∄</b> ,∰∄                             | The multimedia icon directs you to a related multimedia presentation.                                                                                                                  |

| CAUTION                                  | A caution calls attention to a condition or possible situation that can damage or destroy the product or your work.                                                                    |

| WARNING                                  | A warning calls attention to a condition or possible situation that can cause you injury.                                                                                              |

|                                          | The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents.                 |

## **Signal Detect at Receiver**

In PIPE mode, signal detection is supported with the built-in signal threshold detection circuitry. When electrical idle inference is not enabled, the rx\_signaldetect signal is inverted and available as pipeelecidle port in the PIPE interface.

## **Lane Synchronization**

In PIPE mode, the word aligner is configured in automatic synchronization state machine mode that complies with the PCIe specification. Table 1–16 lists the synchronization state machine parameters that implement the PCIe-compliant synchronization.

## Table 1–16. Synchronization State Machine Parameters (1)

| Parameter                                                                                 | Value |

|-------------------------------------------------------------------------------------------|-------|

| Number of valid synchronization (/K28.5/) code groups received to achieve synchronization | 4     |

| Number of erroneous code groups received to lose synchronization                          | 17    |

| Number of continuous good code groups received to reduce the error count by one           | 16    |

Note to Table 1-16:

(1) The word aligner supports 10-bit pattern lengths in PIPE mode.

## **Clock Rate Compensation**

In PIPE mode, the rate match FIFO compensates up to ±300 ppm (600 ppm total) difference between the upstream transmitter and the local receiver reference clock. In PIPE mode, the rate match FIFO operation is compliant to the version 2.0 of the PCIe Base Specification. The PCIe protocol requires the receiver to recognize a skip (SKP) ordered set, and inserts or deletes only one SKP symbol per SKP ordered set received to prevent the rate match FIFO from overflowing or underflowing. The SKP ordered set is a /K28.5/ comma (COM) symbol followed by one to five consecutive /K28.0/ SKP symbols, which are sent by transmitter during the inter-packet gap.

The rate match operation begins after the synchronization state machine in the word aligner indicates synchronization is acquired, as indicated with logic high on rx\_syncstatus signal. Rate match FIFO insertion and deletion events are communicated to FPGA fabric on the pipestatus [2..0] port from each channel.

## **Low-Latency Synchronous PCIe**

In PIPE mode, the Cyclone IV GX transceiver supports a lower latency in synchronous PCIe by reducing the latency across the rate match FIFO. In synchronous PCIe, the system uses a common reference clocking that gives a 0 ppm difference between the upstream transmitter's and local receiver's reference clock.

When using common reference clocking, the transceiver supports spread-spectrum clocking. For more information about the SSC support in PCIe Express (PIPE) mode, refer to the *Cyclone IV Device Data Sheet*.

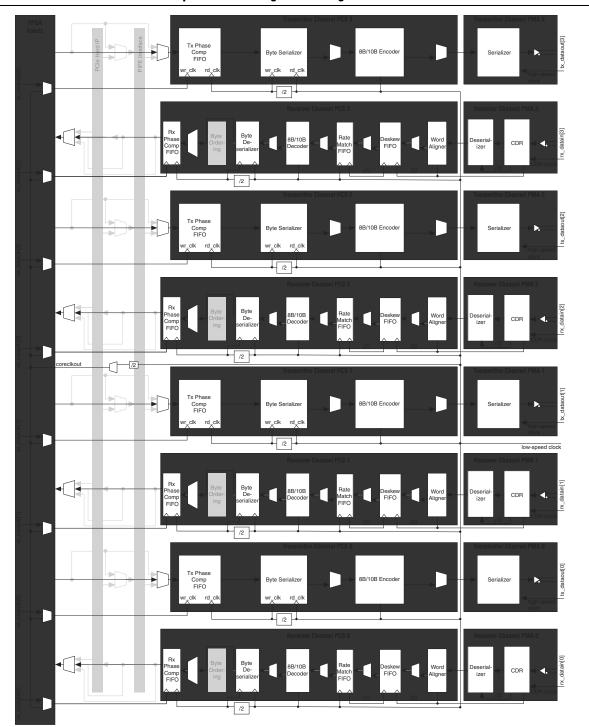

Figure 1–63 shows the transceiver channel datapath and clocking when configured in XAUI mode.

#### Notes to Figure 1-63:

- (1) Channel 1 low-speed recovered clock.

- (2) Low-speed recovered clock.

- (3) High-speed recovered clock.

## 3. Cyclone IV Dynamic Reconfiguration

Cyclone<sup>®</sup> IV GX transceivers allow you to dynamically reconfigure different portions of the transceivers without powering down any part of the device. This chapter describes and provides examples about the different modes available for dynamic reconfiguration.

You can use the ALTGX\_RECONFIG and ALTPLL\_RECONFIG controller instance to reconfigure the physical medium attachment (PMA) controls, physical coding sublayer (PCS), multipurpose phase locked loops (PLLs), and general purpose PLLs.

This chapter contains the following sections:

- "Glossary of Terms" on page 3–1

- "Dynamic Reconfiguration Controller Architecture" on page 3–2

- "Dynamic Reconfiguration Modes" on page 3–12

- "Error Indication During Dynamic Reconfiguration" on page 3–36

- "Functional Simulation of the Dynamic Reconfiguration Process" on page 3–37

## **Glossary of Terms**

Table 3–1 lists the terms used in this chapter:

| Table 3-1. | <b>Glossary</b> of | <b>Terms Used in</b> | this Chapter | (Part 1 of 2) |

|------------|--------------------|----------------------|--------------|---------------|

|------------|--------------------|----------------------|--------------|---------------|

| Term                       | Description                                                                                                                                                                                    |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALTGX_RECONFIG Instance    | Dynamic reconfiguration controller instance generated by the ALTGX_RECONFIG MegaWizard <sup>™</sup> Plug-In Manager.                                                                           |

| ALTGX Instance             | Transceiver instance generated by the ALTGX MegaWizard Plug-In Manager.                                                                                                                        |

| ALTPLL_RECONFIG Instance   | Dynamic PLL reconfiguration controller instance generated by the ALTPLL_RECONFIG Megawizard Plug-In Manager                                                                                    |

| Logical Channel Addressing | Used whenever the concept of logical channel addressing is explained. This term does not refer to the logical_channel_address port available in the ALTGX_RECONFIG MegaWizard Plug-In Manager. |

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Port Name                     | Input/<br>Output |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| reconfig_address<br>_out[50]  | Output           | This signal is always available for you to select in the <b>Channel reconfiguration</b> screen. This signal is applicable only in the dynamic reconfiguration modes grouped under <b>Channel reconfiguration mode</b> including <b>channel interface</b> and <b>Use RX local divider</b> option.                                                                                                                                     |  |  |

|                               |                  | This signal represents the current address used by the ALTGX_RECONFIG instance when writing the <b>.mif</b> into the transceiver channel. This signal increments by 1, from 0 to the last address, then starts at 0 again. You can use this signal to indicate the end of all the <b>.mif</b> write transactions (reconfig_address_out[50] changes from the last address to 0 at the end of all the <b>.mif</b> write transactions). |  |  |

| reconfig_address<br>_en       | Output           | This is an optional signal you can select in the <b>Channel reconfiguration</b> screen. This signal is applicable only in dynamic reconfiguration modes grouped under the <b>Channel reconfiguration</b> option.                                                                                                                                                                                                                     |  |  |

|                               |                  | The dynamic reconfiguration controller asserts reconfig_address_en to indicate that reconfig_address_out [50] has changed. This signal is asserted only after the dynamic reconfiguration controller completes writing one 16-bit word of the <b>.mif</b> .                                                                                                                                                                          |  |  |

| reset_reconfig_<br>address    | Input            | This is an optional signal you can select in the <b>Channel reconfiguration</b> screen. This signal is applicable only in dynamic reconfiguration modes grouped under the <b>Channel reconfiguration</b> option.                                                                                                                                                                                                                     |  |  |

|                               |                  | Enable this signal and assert it for one reconfig_clk clock cycle if you want to reset the reconfiguration address used by the ALTGX_RECONFIG instance during reconfiguration.                                                                                                                                                                                                                                                       |  |  |

| reconfig_data<br>[150]        | Input            | This signal is applicable only in the dynamic reconfiguration modes grouped under the <b>Channel reconfiguration</b> option. This is a 16-bit word carrying the reconfiguration information. It is stored in a <b>.mif</b> that you must generate. The ALTGX_RECONFIG instanc requires that you provide reconfig_data [150] on every <b>.mif</b> write transaction using the write_all signal.                                       |  |  |

| reconfig_reset <sup>(4)</sup> | Input            | You can use this signal to reset all the reconfiguration process in <b>Channel reconfiguration</b> mode. Asserting this port will reset all the register in the reconfiguration controller logics. This port only shows up in <b>Channel reconfiguration</b> mode.                                                                                                                                                                   |  |  |

|                               |                  | If you are feeding into this port, synchronize the reset signal to the $\tt reconfig_clk$ domain.                                                                                                                                                                                                                                                                                                                                    |  |  |

| channel_reconfig<br>_done     | Output           | This signal goes high to indicate that the dynamic reconfiguration controller has finished writing all the words of the <b>.mif</b> . The channel_reconfig_done signal is automatically deasserted at the start of a new dynamic reconfiguration write sequence. This signal is applicable only in channel reconfiguration mode.                                                                                                     |  |  |

## Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 7 of 7)

Notes to Table 3-2:

(1) Not all combinations of input bits are legal values.

(2) This setting is required for compliance to PCI Express® (PIPE) functional mode.

(3) PLL reconfiguration is performed using ALTPLL\_RECONFIG controller. Hence it is not selected through the reconfig\_mode\_sel[2..0] port.

(4) reconfig\_reset will not restart the offset cancellation operation. Offset cancellation only occurs one time after power up and does not occur when subsequent reconfig\_reset is asserted.

## **Offset Cancellation Feature**

The Cyclone IV GX devices provide an offset cancellation circuit per receiver channel to counter the offset variations due to process, voltage, and temperature (PVT). These variations create an offset in the analog circuit voltages, pushing them out of the expected range. In addition to reconfiguring the transceiver channel, the dynamic reconfiguration controller performs offset cancellation on all receiver channels connected to it on power up.

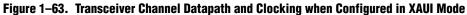

Figure 3–5 shows the read transaction waveform for Method 1.

Figure 3–5. Read Transaction Waveform—Use 'logical\_channel\_address port' Option

#### Notes to Figure 3-5:

- (1) In this waveform example, you want to read from only the transmitter portion of the channel.

- (2) In this waveform example, the number of channels connected to the dynamic reconfiguration controller is four. Therefore, the logical channel address port is 2 bits wide.

Simultaneous write and read transactions are not allowed.

# Method 2: Writing the Same Control Signals to Control All the Transceiver Channels

This method does not require the logical\_channel\_address port. The PMA controls of all the transceiver channels connected to the ALTGX\_RECONFIG instance are reconfigured.

The **Use the same control signal for all the channels** option is available on the **Analog controls** tab of the ALTGX\_RECONFIG MegaWizard Plug-In Manager. If you enable this option, the width of the PMA control ports are fixed as follows:

### **PMA Control Ports Used in a Write Transaction**

- tx\_vodctrl is fixed to 3 bits

- tx preemp is fixed to 5 bits

- rx eqdcgain is fixed to 2 bits

- rx\_eqctrl is fixed to 4 bits

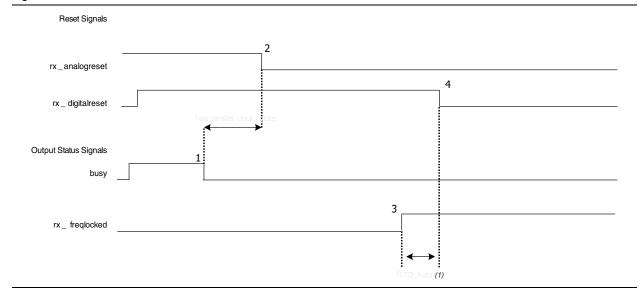

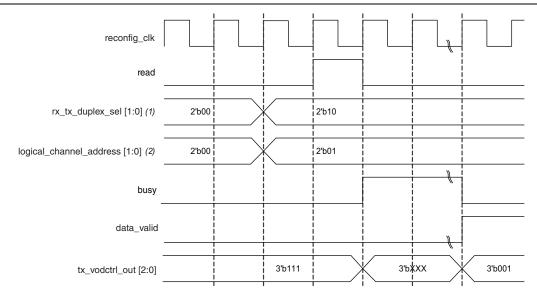

Figure 1–2 shows the lock time parameters in manual mode.

LTD = lock-to-data. LTR = lock-to-reference.

Figure 1–2. Lock Time Parameters for Manual Mode

Figure 1–3 shows the lock time parameters in automatic mode.

Figure 1–3. Lock Time Parameters for Automatic Mode