#### Intel - EP4CE6F17C9LN Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 392                                                      |

| Number of Logic Elements/Cells | 6272                                                     |

| Total RAM Bits                 | 276480                                                   |

| Number of I/O                  | 179                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 256-LBGA                                                 |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce6f17c9In |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Differential HSTL I/O Standard Support in Cyclone IV Devices |      |

|--------------------------------------------------------------|------|

| True Differential Output Buffer Feature                      |      |

| Programmable Pre-Emphasis                                    | 6–35 |

| High-Speed I/O Timing                                        |      |

| Design Guidelines                                            |      |

| Differential Pad Placement Guidelines                        |      |

| Board Design Considerations                                  |      |

| Software Overview                                            |      |

| Document Revision History                                    |      |

|                                                              |      |

## **Chapter 7. External Memory Interfaces in Cyclone IV Devices**

| Cyclone IV Devices Memory Interfaces Pin Support      | 7–2  |

|-------------------------------------------------------|------|

| Data and Data Clock/Strobe Pins                       | 7–2  |

| Optional Parity, DM, and Error Correction Coding Pins | 7–11 |

| Address and Control/Command Pins                      | 7–12 |

| Memory Clock Pins                                     | 7–12 |

| Cyclone IV Devices Memory Interfaces Features         | 7–12 |

| DDR Input Registers                                   | 7–12 |

| DDR Output Registers                                  | 7–14 |

| OCT with Calibration                                  | 7–15 |

| PLL                                                   | 7–15 |

| Document Revision History                             | 7–16 |

## Section III. System Integration

## Chapter 8. Configuration and Remote System Upgrades in Cyclone IV Devices

| Configuration                                                                          |                 |

|----------------------------------------------------------------------------------------|-----------------|

| Configuration Features                                                                 |                 |

| Configuration Data Decompression                                                       |                 |

| Configuration Requirement                                                              |                 |

| Power-On Reset (POR) Circuit                                                           |                 |

| Configuration File Size                                                                |                 |

| Configuration and JTAG Pin I/O Requirements                                            |                 |

| Configuration Process                                                                  |                 |

| Power Up                                                                               |                 |

| Reset                                                                                  |                 |

| Configuration                                                                          |                 |

| Configuration Error                                                                    |                 |

| Initialization                                                                         |                 |

| User Mode                                                                              |                 |

| Configuration Scheme                                                                   |                 |

| AS Configuration (Serial Configuration Devices)                                        |                 |

| Single-Device AS Configuration                                                         |                 |

| Multi-Device AS Configuration                                                          |                 |

| Configuring Multiple Cyclone IV Devices with the Same Design                           |                 |

| Guidelines for Connecting a Serial Configuration Device to Cyclone IV Devices for 8–18 | an AS Interface |

| Programming Serial Configuration Devices                                               |                 |

| AP Configuration (Supported Flash Memories)                                            |                 |

| AP Configuration Supported Flash Memories                                              |                 |

| Single-Device AP Configuration                                                         |                 |

| Multi-Device AP Configuration                                                          |                 |

| Byte-Wide Multi-Device AP Configuration                                                |                 |

|                                                                                        |                 |

- Cyclone IV GX devices offer up to eight high-speed transceivers that provide:

- Data rates up to 3.125 Gbps

- 8B/10B encoder/decoder

- 8-bit or 10-bit physical media attachment (PMA) to physical coding sublayer (PCS) interface

- Byte serializer / deserializer (SERDES)

- Word aligner

- Rate matching FIFO

- TX bit slipper for Common Public Radio Interface (CPRI)

- Electrical idle

- Dynamic channel reconfiguration allowing you to change data rates and protocols on-the-fly

- Static equalization and pre-emphasis for superior signal integrity

- 150 mW per channel power consumption

- Flexible clocking structure to support multiple protocols in a single transceiver block

- Cyclone IV GX devices offer dedicated hard IP for PCI Express (PIPE) (PCIe) Gen 1:

- ×1, ×2, and ×4 lane configurations

- End-point and root-port configurations

- Up to 256-byte payload

- One virtual channel

- 2 KB retry buffer

- 4 KB receiver (Rx) buffer

- Cyclone IV GX devices offer a wide range of protocol support:

- PCIe (PIPE) Gen 1 ×1, ×2, and ×4 (2.5 Gbps)

- Gigabit Ethernet (1.25 Gbps)

- CPRI (up to 3.072 Gbps)

- XAUI (3.125 Gbps)

- Triple rate serial digital interface (SDI) (up to 2.97 Gbps)

- Serial RapidIO (3.125 Gbps)

- Basic mode (up to 3.125 Gbps)

- V-by-One (up to 3.0 Gbps)

- DisplayPort (2.7 Gbps)

- Serial Advanced Technology Attachment (SATA) (up to 3.0 Gbps)

- OBSAI (up to 3.072 Gbps)

In this mode, the activeclock signal mirrors the clkswitch signal. As both blocks are still functional during the manual switch, neither clkbad signals go high. Because the switchover circuit is positive edge-sensitive, the falling edge of the clkswitch signal does not cause the circuit to switch back from inclk1 to inclk0. When the clkswitch signal goes high again, the process repeats. The clkswitch signal and the automatic switch only works depending on the availability of the clock that is switched to. If the clock is unavailable, the state machine waits until the clock is available.

When CLKSWITCH = 1, it overrides the automatic switch-over function. As long as clkswitch signal is high, further switch-over action is blocked.

|               | • |

|---------------|---|

| inclk0        |   |

| inclk1        |   |

| muxout        |   |

| clkswitch _   |   |

| activeclock _ |   |

| clkbad0 -     |   |

| clkbad1 -     |   |

#### Figure 5–19. Clock Switchover Using the clkswitch Control (1)

#### Note to Figure 5–19:

(1) Both inclk0 and inclk1 must be running when the clkswitch signal goes high to start a manual clock switchover event.

## **Manual Clock Switchover**

PLLs of Cyclone IV devices support manual switchover, in which the clkswitch signal controls whether inclk0 or inclk1 is the input clock to the PLL. The characteristics of a manual switchover are similar to the manual override feature in an automatic clock switchover, in which the switchover circuit is edge-sensitive. When the clkswitch signal goes high, the switchover sequence starts. The falling edge of the clkswitch signal does not cause the circuit to switch back to the previous input clock.

• For more information about PLL software support in the Quartus II software, refer to the *ALTPLL Megafunction User Guide*.

#### Guidelines

Use the following guidelines to design with clock switchover in PLLs:

Clock loss detection and automatic clock switchover require the inclk0 and inclk1 frequencies be within 20% of each other. Failing to meet this requirement causes the clkbad0 and clkbad1 signals to function improperly. Table 6–6 and Table 6–7 summarize which I/O banks support these I/O standards in the Cyclone IV device family.

| Differential I/O Standards                           | I/O Bank Location | External Resistor<br>Network at Transmitter | Transmitter (TX)      | Receiver (RX) |  |

|------------------------------------------------------|-------------------|---------------------------------------------|-----------------------|---------------|--|

| LVDS                                                 | 1,2,5,6           | Not Required                                | <ul> <li>✓</li> </ul> | $\checkmark$  |  |

|                                                      | All               | Three Resistors                             | •                     | ~             |  |

|                                                      | 1,2,5,6           | Not Required                                |                       |               |  |

| RSDS                                                 | 3,4,7,8           | Three Resistors                             | <ul> <li>✓</li> </ul> |               |  |

|                                                      | All               | Single Resistor                             | -                     |               |  |

|                                                      | 1,2,5,6           | Not Required                                | ~                     |               |  |

| mini-LVDS                                            | All               | Three Resistors                             | · ·                   |               |  |

| PPDS                                                 | 1,2,5,6           | Not Required                                | ~                     |               |  |

| PPD3                                                 | All               | Three Resistors                             | · ·                   | _             |  |

| BLVDS (1)                                            | All               | Single Resistor                             | $\checkmark$          | $\checkmark$  |  |

| LVPECL (2)                                           | All               | —                                           | —                     | $\checkmark$  |  |

| Differential SSTL-2 <sup>(3)</sup>                   | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

| Differential SSTL-18 <sup>(3)</sup>                  | All               | _                                           | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-18 (3)                             | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-15 (3)                             | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-12 <sup>(3)</sup> , <sup>(4)</sup> | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

#### Notes to Table 6-6:

(1) Transmitter and Receiver f<sub>MAX</sub> depend on system topology and performance requirement.

(2) The LVPECL I/O standard is only supported on dedicated clock input pins.

(3) The differential SSTL-2, SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards are only supported on clock input pins and PLL output clock pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-15, and HSTL-12 I/O standards.

(4) Differential HSTL-12 Class II is supported only in column I/O banks.

You can begin reconfiguration by pulling the nCONFIG pin low. The nCONFIG pin must be low for at least 500 ns. When nCONFIG is pulled low, the Cyclone IV device is reset. The Cyclone IV device also pulls nSTATUS and CONF\_DONE low and all I/O pins are tri-stated. When nCONFIG returns to a logic-high level and nSTATUS is released by the Cyclone IV device, reconfiguration begins.

## **Configuration Error**

If an error occurs during configuration, Cyclone IV devices assert the nSTATUS signal low, indicating a data frame error and the CONF\_DONE signal stays low. If the **Auto-restart configuration after error** option (available in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box) is turned on, the Cyclone IV device releases nSTATUS after a reset time-out period (a maximum of 230  $\mu$ s), and retries configuration. If this option is turned off, the system must monitor nSTATUS for errors and then pulse nCONFIG low for at least 500 ns to restart configuration.

## Initialization

In Cyclone IV devices, the initialization clock source is either the internal oscillator or the optional CLKUSR pin. By default, the internal oscillator is the clock source for initialization. If you use the internal oscillator, the device provides itself with enough clock cycles for proper initialization. When using the internal oscillator, you do not have to send additional clock cycles from an external source to the CLKUSR pin during the initialization stage. Additionally, you can use the CLKUSR pin as a user I/O pin.

You also have the flexibility to synchronize initialization of multiple devices or to delay initialization with the **CLKUSR** option. The CLKUSR pin allows you to control when your device enters user mode for an indefinite amount of time. You can turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box. When you turn on the **Enable user supplied start-up clock option (CLKUSR)** option, the CLKUSR pin is the initialization clock source. Supplying a clock on the CLKUSR pin does not affect the configuration process. After the configuration data is accepted and CONF\_DONE goes high, Cyclone IV devices require 3,192 clock cycles to initialize properly and enter user mode.

If you use the optional CLKUSR pin and the nCONFIG pin is pulled low to restart configuration during device initialization, ensure that the CLKUSR pin continues to toggle when nSTATUS is low (a maximum of 230 µs).

## **User Mode**

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user mode with a low-to-high transition. The **Enable INIT\_DONE Output** option is available in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box. If you use the INIT\_DONE pin, it is high due to an external  $10-k\Omega$  pull-up resistor when nCONFIG is low and during the beginning of configuration. After the option bit to enable INIT\_DONE is programmed into the device (during the first frame of configuration data), the INIT\_DONE pin goes low. When initialization is complete, the INIT\_DONE pin is released and pulled high. This low-to-high transition signals that the device has entered user mode. In user mode, the user I/O pins function as assigned in your design and no longer have weak pull-up resistors.

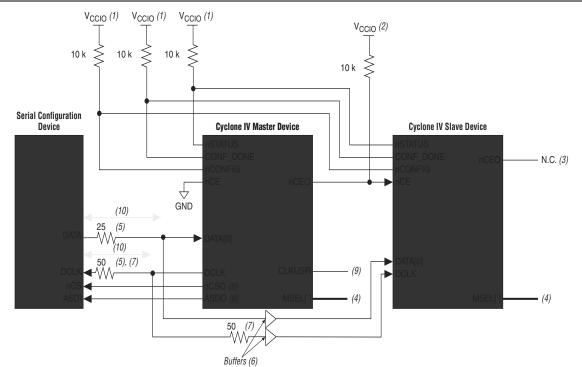

## **Multi-Device AS Configuration**

You can configure multiple Cyclone IV devices with a single serial configuration device. When the first device captures all its configuration data from the bitstream, it drives the nCEO pin low, enabling the next device in the chain. If the last device in the chain is a Cyclone IV device, you can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration. The nCONFIG, nSTATUS, CONF\_DONE, DCLK, and DATA[0] pins of each device in the chain are connected together (Figure 8–3).

#### Notes to Figure 8-3:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of I/O bank in which the nCE pin resides.

- (3) You can leave the nCEO pin unconnected or use it as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device of the Cyclone IV device in AS mode and the slave devices in PS mode. To connect the MSEL pins for the master device in AS mode and slave devices in PS mode, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) Connect the series resistor at the near end of the serial configuration device.

- (6) Connect the repeater buffers between the master and slave devices of the Cyclone IV device for DATA [0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (7) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

- (8) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (9) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- (10) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration device to the junction-split on both DCLK and Data0 line is 3.5 inches.

Altera recommends putting a buffer before the DATA and DCLK output from the master device to avoid signal strength and signal integrity issues. The buffer must not significantly change the DATA-to-DCLK relationships or delay them with respect to other AS signals (ASDI and nCS). Also, the buffer must only drive the slave devices to ensure that the timing between the master device and the serial configuration device is unaffected.

This configuration method supports both compressed and uncompressed **.sof**. Therefore, if the configuration bitstream size exceeds the capacity of a serial configuration device, you can enable the compression feature in the **.sof** or you can select a larger serial configuration device.

# Guidelines for Connecting a Serial Configuration Device to Cyclone IV Devices for an AS Interface

For single- and multi-device AS configurations, the board trace length and loading between the supported serial configuration device and Cyclone IV device must follow the recommendations listed in Table 8–7.

| Cyclone IV<br>Device AS Pins | Cyclone IV Device to | race Length from a<br>a Serial Configuration<br>(Inches) | Maximum Board Load (pF) |

|------------------------------|----------------------|----------------------------------------------------------|-------------------------|

|                              | Cyclone IV E         | Cyclone IV GX                                            |                         |

| DCLK                         | 10 6                 |                                                          | 15                      |

| DATA [0]                     | 10 6                 |                                                          | 30                      |

| nCSO                         | 10 6                 |                                                          | 30                      |

| ASDO                         | 10 6                 |                                                          | 30                      |

Table 8–7. Maximum Trace Length and Loading for AS Configuration

Note to Table 8-7:

(1) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration device to the junction-split on both DCLK and Data0 line is 3.5 inches.

#### **Estimating AS Configuration Time**

AS configuration time is dominated by the time it takes to transfer data from the serial configuration device to the Cyclone IV device. This serial interface is clocked by the Cyclone IV device DCLK output (generated from a 40-MHz internal oscillator for Cyclone IV E devices, a 20- or 40-MHz internal oscillator, or an external CLKUSR of up to 40 MHz for Cyclone IV GX devices).

Equation 8–2 and Equation 8–3 show the configuration time calculations.

#### Equation 8-2.

```

Size \times \left(\frac{\text{maximum DCLK period}}{1 \text{ bit}}\right) = estimated maximum configuration ti

```

#### Equation 8-3.

9,600,000 bits  $\times \left(\frac{50 \text{ ns}}{1 \text{ bit}}\right) = 480 \text{ ms}$

- The **.rbf** used by the JRunner software driver cannot be a compressed **.rbf** because the JRunner software driver uses JTAG-based configuration. During JTAG-based configuration, the real-time decompression feature is not available.

- **C** For more information about the JRunner software driver, refer to *AN* 414: JRunner *Software Driver: An Embedded Solution for PLD JTAG Configuration* and the source files on the Altera website at (www.altera.com).

## **Combining JTAG and AS Configuration Schemes**

You can combine the AS configuration scheme with the JTAG-based configuration (Figure 8–28). This setup uses two 10-pin download cable headers on the board. One download cable is used in JTAG mode to configure the Cyclone IV device directly through the JTAG interface. The other download cable is used in AS mode to program the serial configuration device in-system through the AS programming interface. If you try configuring the device using both schemes simultaneously, JTAG configuration takes precedence and AS configuration terminates.

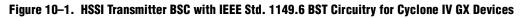

## IEEE Std. 1149.6 Boundary-Scan Register

The boundary-scan cell (BSC) for HSSI transmitters ( $GXB_TX[p,n]$ ) and receivers ( $GXB_RX[p,n]$ ) in Cyclone IV GX devices are different from the BSCs for I/O pins.

Figure 10–1 shows the Cyclone IV GX HSSI transmitter boundary-scan cell.

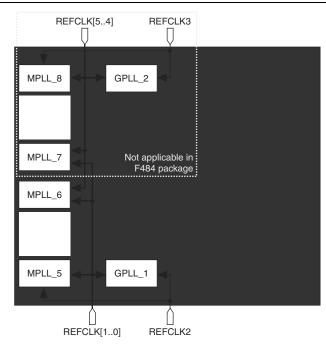

Figure 1–26. PLL Input Reference Clocks in Transceiver Operation for F484 and Larger Packages  $^{(1)}$ ,  $^{(2)}$ ,  $^{(3)}$

#### Notes to Figure 1-26:

- (1) The REFCLK2 and REFCLK3 pins are dual-purpose CLKIO, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A respectively.

- (2) The REFCLK[1..0] and REFCLK[5..4] pins are dual-purpose differential REFCLK or DIFFCLK pins that reside in banks 3B and 8B respectively. These clock input pins do not have access to the clock control blocks and GCLK networks. For more details, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

- (3) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs and GPLLs may have reduced jitter performance.

The input reference clocks reside in banks 3A, 3B, 8A, and 8B have dedicated  $V_{CC\_CLKIN3A}$ ,  $V_{CC\_CLKIN3B}$ ,  $V_{CC\_CLKIN8A}$ , and  $V_{CC\_CLKIN8B}$  power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for general purpose I/Os (GPIOs). Table 1–6 lists the supported I/O standard for the REFCLK pins.

| I/O Standard                | HSSI                  |                         | Terminatio | VCC_          | CLKIN Level   | I/O Pin Type       |                |                    |  |

|-----------------------------|-----------------------|-------------------------|------------|---------------|---------------|--------------------|----------------|--------------------|--|

|                             | Protocol              | Coupling                | n          | Input         | Output        | Column I/O Row I/O |                | Supported<br>Banks |  |

| LVDS                        | ALL                   | Differential            | Off-chip   | 2.5 V         | Not Supported | Yes                | No             | 3A, 3B, 8A, 8B     |  |

| LVPECL                      | ALL                   | AC (Needs               | Off-chip   | 2.5 V         | Not Supported | Yes                | No             | 3A, 3B, 8A, 8B     |  |

| 1.2 V, 1.5 V,<br>3.3 V PCML | ALL                   | off-chip<br>resistor to | Off-chip   | 2.5 V         | Not Supported | Yes                | No             | 3A, 3B, 8A, 8B     |  |

|                             | ALL                   | restore                 | Off-chip   | 2.5 V         | Not Supported | Yes                | No             | 3A, 3B, 8A, 8B     |  |

|                             | ALL V <sub>CM</sub> ) | Off-chip                | 2.5 V      | Not Supported | Yes           | No                 | 3A, 3B, 8A, 8B |                    |  |

| HCSL                        | PCle                  | Differential<br>DC      | Off-chip   | 2.5 V         | Not Supported | Yes                | No             | 3A, 3B, 8A, 8B     |  |

Table 1–6. REFCLK I/O Standard Support

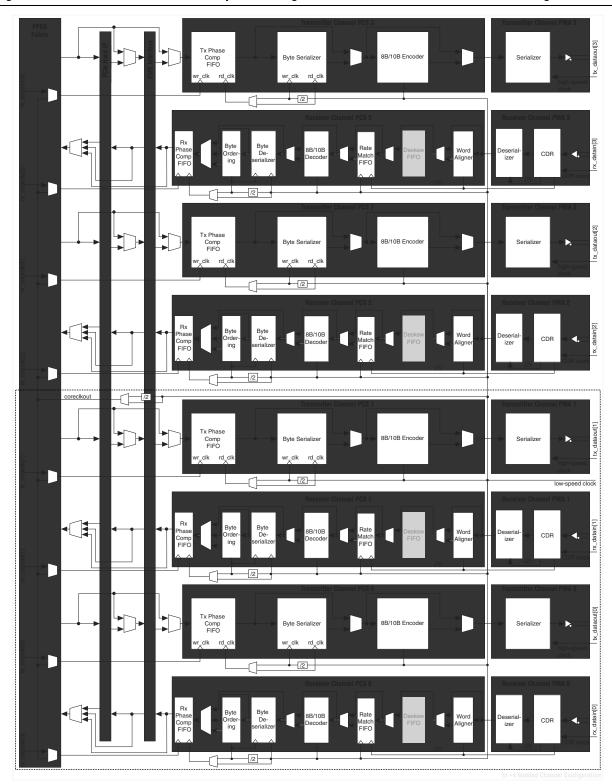

Figure 1–39. Transmitter and Receiver Datapath Clocking with Rate Match FIFO in Bonded Channel Configuration

#### Notes to Figure 1–39:

- (1) Low-speed recovered clock.

- (2) High-speed recovered clock.

| Functional Mode          | Protocol                    | Key Feature                                                                               | Reference                                    |  |  |

|--------------------------|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------|--|--|

| Deterministic<br>Latency | Proprietary, CPRI,<br>OBSAI | TX PLL phase frequency detector (PFD) feedback, registered mode FIFO, TX bit-slip control | "Deterministic Latency<br>Mode" on page 1–73 |  |  |

| SDI                      | SDI                         | High-speed SERDES, CDR                                                                    | "SDI Mode" on<br>page 1–76                   |  |  |

Table 1–14. Transceiver Functional Modes for Protocol Implementation (Part 2 of 2)

## **Basic Mode**

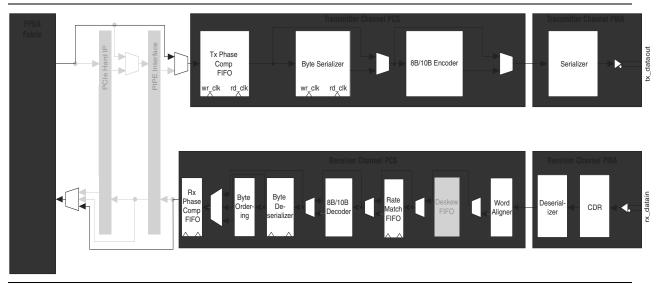

The Cyclone IV GX transceiver channel datapath is highly flexible in Basic mode to implement proprietary protocols. SATA, V-by-One, and Display Port protocol implementations in Cyclone IV GX transceiver are supported with Basic mode. Figure 1–44 shows the transceiver channel datapath supported in Basic mode.

Figure 1-44. Transceiver Channel Datapath in Basic Mode

|                                 |            | 8-bit Channel Width                     |                              |                                                                       |                                                                      | 10-bit Channel Width                     |                              |                                                                       |                                                                      |

|---------------------------------|------------|-----------------------------------------|------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------|------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|

| Patterns                        | Polynomial | Channel<br>Width<br>of<br>8 bits<br>(1) | Word<br>Alignment<br>Pattern | Maximum<br>Data Rate<br>(Gbps) for<br>F324 and<br>Smaller<br>Packages | Maximum<br>Data Rate<br>(Gbps) for<br>F484 and<br>Larger<br>Packages | Channel<br>Width<br>of<br>10-bits<br>(1) | Word<br>Alignment<br>Pattern | Maximum<br>Data Rate<br>(Gbps) for<br>F324 and<br>Smaller<br>Packages | Maximum<br>Data Rate<br>(Gbps) for<br>F484 and<br>Larger<br>Packages |

| Low<br>Frequency <sup>(2)</sup> | 1111100000 | Ν                                       | _                            | _                                                                     | _                                                                    | Y                                        | _                            | 2.5                                                                   | 3.125                                                                |

#### Notes to Table 1-25:

(1) Channel width refers to the **What is the channel width?** option in the **General** screen of the ALTGX MegaWizard Plug-In Manager. Based on the selection, an 8 or 10 bits wide pattern is generated as indicated by a **Yes (Y)** or **No (N)**.

(2) A verifier and associated rx bistdone and rx bisterr signals are not available for the specified patterns.

You can enable the serial loopback option to loop the generated PRBS patterns to the receiver channel for verifier to check the PRBS patterns. When the PRBS pattern is received, the rx\_bisterr and rx\_bistdone signals indicate the status of the verifier. After the word aligner restores the word boundary, the rx\_bistdone signal is driven high when the verifier receives a complete pattern cycle and remains asserted until it is reset using the rx\_digitalreset port. After the assertion of rx\_bistdone, the rx\_bisterr signal is asserted for a minimum of three rx\_clkout cycles when errors are detected in the data and deasserts if the following PRBS sequence contains no error. You can reset the PRBS pattern generator and verifier by asserting the tx\_digitalreset and rx\_digitalreset ports, respectively.

## **Transceiver Top-Level Port Lists**

Table 1–26 through Table 1–29 provide descriptions of the ports available when instantiating a transceiver using the ALTGX megafunction. The ALTGX megafunction requires a relatively small number of signals. There are also a large number of optional signals that facilitate debugging by providing information about the state of the transceiver.

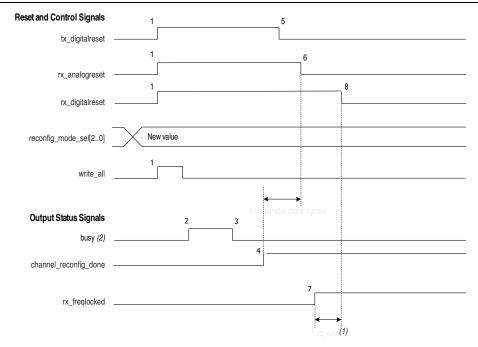

- 2. After the PLL is reset, wait for the pll\_locked signal to go high (marker 4) indicating that the PLL is locked to the input reference clock. After the assertion of the pll\_locked signal, deassert the tx\_digitalreset signal (marker 5).

- 3. Wait at least five parallel clock cycles after the pll\_locked signal is asserted to deassert the rx\_analogreset signal (marker 6).

- 4. When the rx\_freqlocked signal goes high (marker 7), from that point onwards, wait for at least t<sub>LTD\_Auto</sub> time, then deassert the rx\_digitalreset signal (marker 8). At this point, the receiver is ready for data traffic.

## **Reset Sequence in Channel Reconfiguration Mode**

Use the example reset sequence shown in Figure 2–12 when you are using the dynamic reconfiguration controller to change the PCS settings of the transceiver channel. In this example, the dynamic reconfiguration is used to dynamically reconfigure the transceiver channel configured in Basic ×1 mode with receiver CDR in automatic lock mode.

## Figure 2–12. Reset Sequence When Using the Dynamic Reconfiguration Controller to Change the PCS Settings of the Transceiver Channel

#### Notes to Figure 2-12:

- (1) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

## **Dynamic Reconfiguration Controller Port List**

Table 3–2 lists the input control ports and output status ports of the dynamic reconfiguration controller.

| Table 3–2  | Dynamic Reconfiguration | n Controller Port List (ALTG)    | ( <b>RECONEIG</b> Instance) | (Part 1 of 7)  |

|------------|-------------------------|----------------------------------|-----------------------------|----------------|

| Table J-2. | Dynamic necomiguratio   | II OUIILIUIIGI I UIL LISL (ALIU/ | Lucom na motancej           | (1 alt 1 01 7) |

| Port Name                               | Input/<br>Output |                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-----------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Clock Inputs to ALTGX_RECONFIG Instance |                  |                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                                         |                  | The frequency range of this clock depends on the following transceiver channel configuration modes:                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                         |                  | <ul> <li>Receiver only (37.5 MHz to 50 MHz)</li> <li>Receiver and Transmitter (37.5 MHz to 50 MHz)</li> </ul>                                                                                                                                                                                         |  |  |  |  |  |  |

| reconfig_clk                            | Input            | <ul> <li>Receiver and Transmitter (37.5 MHz to 50 MHz)</li> <li>Transmitter only (2.5 MHz to 50 MHz)</li> </ul>                                                                                                                                                                                       |  |  |  |  |  |  |

|                                         |                  | By default, the Quartus <sup>®</sup> II software assigns a global clock resource to this port. This clock must be a free-running clock sourced from an I/O clock pin. Do not use dedicated transceiver REFCLK pins or any clocks generated by transceivers.                                           |  |  |  |  |  |  |

| ALTGX and ALTGX_RECO                    | NFIG Inte        | rface Signals                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                         |                  | An output port in the ALTGX instance and an input port in the ALTGX_RECONFIG instance.<br>This signal is transceiver-block based. Therefore, the width of this signal increases in steps<br>of 5 bits per transceiver block.                                                                          |  |  |  |  |  |  |

|                                         |                  | In the ALTGX MegaWizard Plug-In Manager, the width of this signal depends on the number of channels you select in the <b>What is the number of channels?</b> option in the <b>General</b> screen.                                                                                                     |  |  |  |  |  |  |

|                                         |                  | For example, if you select the number of channels in the ALTGX instance as follows:                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                         |                  | $1 \le$ Channels $\le 4$ , then the output port reconfig_fromgxb[40] = 5 bits                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                         |                  | $5 \le$ Channels $\le$ 8, then the output port reconfig_fromgxb[90] = 10 bits                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                         |                  | $9 \le$ Channels $\le$ 12, then the output port reconfig_fromgxb[140] = 15 bits                                                                                                                                                                                                                       |  |  |  |  |  |  |

| reconfig_fromgxb                        | Input            | $13 \leq$ Channels $\leq$ 16, then the output port reconfig_fromgx[190] = 20 bits                                                                                                                                                                                                                     |  |  |  |  |  |  |

| [n0]                                    | Input            | To connect the reconfig_fromgxb port between the ALTGX_RECONFIG instance and multiple ALTGX instances, follow these rules:                                                                                                                                                                            |  |  |  |  |  |  |

|                                         |                  | <ul> <li>Connect the reconfig_fromgxb[40] of ALTGX Instance 1 to the<br/>reconfig_fromgxb[40] of the ALTGX_RECONFIG instance. Connect the<br/>reconfig_fromgxb[] port of the next ALTGX instance to the next available bits of the<br/>ALTGX_RECONFIG instance, and so on.</li> </ul>                 |  |  |  |  |  |  |

|                                         |                  | <ul> <li>Connect the reconfig_fromgxb port of the ALTGX instance, which has the highest<br/>What is the starting channel number? option, to the MSB of the reconfig_fromgxb<br/>port of the ALTGX_RECONFIG instance.</li> </ul>                                                                       |  |  |  |  |  |  |

|                                         |                  | The Quartus II Fitter produces a warning if the dynamic reconfiguration option is enabled in the ALTGX instance but the reconfig_fromgxb and reconfig_togxb ports are not connected to the ALTGX_RECONFIG instance.                                                                                   |  |  |  |  |  |  |

| reconfig_togxb<br>[30]                  | Output           | An input port of the ALTGX instance and an output port of the ALTGX_RECONFIG instance.<br>You must connect the reconfig_togxb[30] input port of every ALTGX instance<br>controlled by the dynamic reconfiguration controller to the reconfig_togxb[30]<br>output port of the ALTGX_RECONFIG instance. |  |  |  |  |  |  |

|                                         |                  | The width of this port is always fixed to 4 bits.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

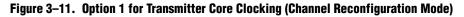

#### **Option 1: Share a Single Transmitter Core Clock Between Transmitters**

- Enable this option if you want tx\_clkout of the first channel (channel 0) of the transceiver block to provide the write clock to the Transmitter Phase Compensation FIFOs of the remaining channels in the transceiver block.

- This option is typically enabled when all the channels of a transceiver block have the same functional mode and data rate and are reconfigured to the identical functional mode and data rate.

Figure 3–11 shows the sharing of channel 0's tx\_clkout between all four regular channels of a transceiver block.

| Symbol               | Parameter                                                      | Conditions                           | Min   | Тур | Max               | Unit |

|----------------------|----------------------------------------------------------------|--------------------------------------|-------|-----|-------------------|------|

| V <sub>CCA_GXB</sub> | Transceiver PMA and auxiliary power supply                     | —                                    | 2.375 | 2.5 | 2.625             | V    |

| V <sub>CCL_GXB</sub> | Transceiver PMA and auxiliary power supply                     | —                                    | 1.16  | 1.2 | 1.24              | V    |

| VI                   | DC input voltage                                               | —                                    | -0.5  |     | 3.6               | V    |

| V <sub>0</sub>       | DC output voltage                                              | —                                    | 0     | —   | V <sub>CCIO</sub> | V    |

| т                    | Operating junction temperature                                 | For commercial use                   | 0     | _   | 85                | °C   |

| TJ                   | Operating junction temperature                                 | For industrial use                   | -40   |     | 100               | °C   |

| t <sub>RAMP</sub>    | Power supply ramp time                                         | Standard power-on reset<br>(POR) (7) | 50 µs | _   | 50 ms             | _    |

|                      |                                                                | Fast POR <sup>(8)</sup>              | 50 µs | —   | 3 ms              | —    |

| I <sub>Diode</sub>   | Magnitude of DC current across<br>PCI-clamp diode when enabled | _                                    | _     | _   | 10                | mA   |

Table 1-4. Recommended Operating Conditions for Cyclone IV GX Devices (Part 2 of 2)

#### Notes to Table 1-4:

- (1) All VCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

- (2) You must connect  $V_{CCD PLL}$  to  $V_{CCINT}$  through a decoupling capacitor and ferrite bead.

- (3) Power supplies must rise monotonically.

- (4) V<sub>CCI0</sub> for all I/O banks must be powered up during device operation. Configurations pins are powered up by V<sub>CCI0</sub> of I/O Banks 3, 8, and 9 where I/O Banks 3 and 9 only support V<sub>CCI0</sub> of 1.5, 1.8, 2.5, 3.0, and 3.3 V. For fast passive parallel (FPP) configuration mode, the V<sub>CCI0</sub> level of I/O Bank 8 must be powered up to 1.5, 1.8, 2.5, 3.0, and 3.3 V.

- (5) You must set  $V_{CC_{CLKIN}}$  to 2.5 V if you use CLKIN as a high-speed serial interface (HSSI) refclk or as a DIFFCLK input.

- (6) The CLKIN pins in I/O Banks 3B and 8B can support single-ended I/O standard when the pins are used to clock left PLLs in non-transceiver applications.

- (7) The POR time for Standard POR ranges between 50 and 200 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCI0</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 50 ms.

- (8) The POR time for Fast POR ranges between 3 and 9 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 3 ms.

## **ESD** Performance

This section lists the electrostatic discharge (ESD) voltages using the human body model (HBM) and charged device model (CDM) for Cyclone IV devices general purpose I/Os (GPIOs) and high-speed serial interface (HSSI) I/Os. Table 1–5 lists the ESD for Cyclone IV devices GPIOs and HSSI I/Os.

| Table 1–5. ESD for Cyclone IV Devices GPIOs and HSSI I/Os |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

| Symbol              | Parameter                                        | Passing Voltage | Unit |

|---------------------|--------------------------------------------------|-----------------|------|

| M                   | ESD voltage using the HBM (GPIOs) <sup>(1)</sup> | ± 2000          | V    |

| VESDHBM             | ESD using the HBM (HSSI I/Os) <sup>(2)</sup>     | ± 1000          | V    |

| V <sub>ESDCDM</sub> | ESD using the CDM (GPIOs)                        | ± 500           | V    |

|                     | ESD using the CDM (HSSI I/Os) <sup>(2)</sup>     | ± 250           | V    |

#### Notes to Table 1-5:

(1) The passing voltage for EP4CGX15 and EP4CGX30 row I/Os is ±1000V.

(2) This value is applicable only to Cyclone IV GX devices.

## **Embedded Multiplier Specifications**

Table 1–26 lists the embedded multiplier specifications for Cyclone IV devices.

#### Table 1–26. Embedded Multiplier Specifications for Cyclone IV Devices

| Mode                   | <b>Resources Used</b> |     | I          | Performance | )        |     | 11   |

|------------------------|-----------------------|-----|------------|-------------|----------|-----|------|

| Mude                   | Number of Multipliers | C6  | C7, I7, A7 | C8          | C8L, 18L | C9L | Unit |

| 9 × 9-bit multiplier   | 1                     | 340 | 300        | 260         | 240      | 175 | MHz  |

| 18 × 18-bit multiplier | 1                     | 287 | 250        | 200         | 185      | 135 | MHz  |

## **Memory Block Specifications**

Table 1–27 lists the M9K memory block specifications for Cyclone IV devices.

|           |                                    | <b>Resources Used</b> |               | Performance |            |     |          |     |      |

|-----------|------------------------------------|-----------------------|---------------|-------------|------------|-----|----------|-----|------|

| Memory    | Mode                               | LEs                   | M9K<br>Memory | C6          | C7, I7, A7 | C8  | C8L, 18L | C9L | Unit |

| M9K Block | FIFO 256 × 36                      | 47                    | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | Single-port 256 × 36               | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | Simple dual-port 256 × 36 CLK      | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | True dual port 512 × 18 single CLK | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

## **Configuration and JTAG Specifications**

Table 1–28 lists the configuration mode specifications for Cyclone IV devices.

#### Table 1–28. Passive Configuration Mode Specifications for Cyclone IV Devices (1)

| Programming Mode                           | V <sub>CCINT</sub> Voltage Level (V) | DCLK f <sub>max</sub> | Unit |

|--------------------------------------------|--------------------------------------|-----------------------|------|

| Passive Serial (PS)                        | 1.0 <i>(3</i> )                      | 66                    | MHz  |

| rassive Sellai (rS)                        | 1.2                                  | 133                   | MHz  |

| East Dessive Derellel (EDD) (2)            | 1.0 <i>(3)</i>                       | 66                    | MHz  |

| Fast Passive Parallel (FPP) <sup>(2)</sup> | 1.2 (4)                              | 100                   | MHz  |

#### Notes to Table 1-28:

- (1) For more information about PS and FPP configuration timing parameters, refer to the *Configuration and Remote System Upgrades in Cyclone IV Devices* chapter.

- (2) FPP configuration mode supports all Cyclone IV E devices (except for E144 package devices) and EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 only.

- (3) V<sub>CCINT</sub> = 1.0 V is only supported for Cyclone IV E 1.0 V core voltage devices.

- (4) Cyclone IV E devices support 1.2 V V<sub>CCINT</sub>. Cyclone IV E 1.2 V core voltage devices support 133 MHz DCLK f<sub>MAX</sub> for EP4CE6, EP4CE10, EP4CE15, EP4CE22, EP4CE30, and EP4CE40 only.