Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 392                                                     |

| Number of Logic Elements/Cells | 6272                                                    |

| Total RAM Bits                 | 276480                                                  |

| Number of I/O                  | 179                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 0.97V ~ 1.03V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 256-LBGA                                                |

| Supplier Device Package        | 256-FBGA (17x17)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce6f17i8l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 4–2lists the sign of the multiplication results for the various operand sign representations. The results of the multiplication are signed if any one of the operands is a signed value.

Table 4–2. Multiplier Sign Representation

| Da          | ta A        | Data B      |             | Dogult   |

|-------------|-------------|-------------|-------------|----------|

| signa Value | Logic Level | signb Value | Logic Level | Result   |

| Unsigned    | Low         | Unsigned    | Low         | Unsigned |

| Unsigned    | Low         | Signed      | High        | Signed   |

| Signed      | High        | Unsigned    | Low         | Signed   |

| Signed      | High        | Signed      | High        | Signed   |

Each embedded multiplier block has only one signa and one signb signal to control the sign representation of the input data to the block. If the embedded multiplier block has two  $9 \times 9$  multipliers, the Data A input of both multipliers share the same signa signal, and the Data B input of both multipliers share the same signb signal. You can dynamically change the signa and signb signals to modify the sign representation of the input operands at run time. You can send the signa and signb signals through a dedicated input register. The multiplier offers full precision, regardless of the sign representation.

When the signa and signb signals are unused, the Quartus II software sets the multiplier to perform unsigned multiplication by default.

## **Output Registers**

You can register the embedded multiplier output with output registers in either 18- or 36-bit sections, depending on the operational mode of the multiplier. The following control signals are available for each output register in the embedded multiplier:

clock

clock enable

asynchronous clear

All input and output registers in a single embedded multiplier are fed by the same clock, clock enable, and asynchronous clear signals.

# **Operational Modes**

You can use an embedded multiplier block in one of two operational modes, depending on the application needs:

One 18 x 18 multiplier

Up to two 9 x 9 independent multipliers

You can also use embedded multipliers of Cyclone IV devices to implement multiplier adder and multiplier accumulator functions, in which the multiplier portion of the function is implemented with embedded multipliers, and the adder or accumulator function is implemented in logic elements (LEs).

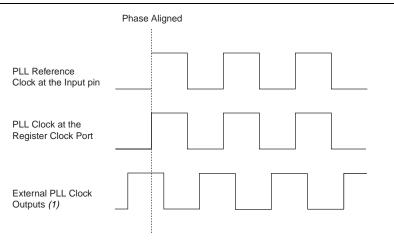

Figure 5–14shows a waveform example of the phase relationship of the PLL clocks in this mode.

Figure 5-14. Phase Relationship Between PLL Clocks in Normal Mode

Note to Figure 5-14

(1) The external clock output can lead or lag the PLL internal clock signals.

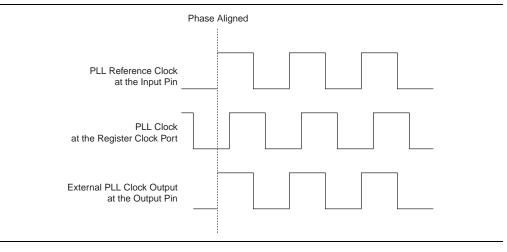

# Zero Delay Buffer Mode

In zero delay buffer (ZDB) mode, the external clock output pin is phase-aligned with the clock input pin for zero delay through the device. When using this mode, use the same I/O standard on the input clock and output clocks to guarantee clock alignment at the input and output pins.

Figure 5–15 shows an example waveform of the phase relationship of the PLL clocks in ZDB mode.

Figure 5-15. Phase Relationship Between PLL Clocks in ZDB Mode

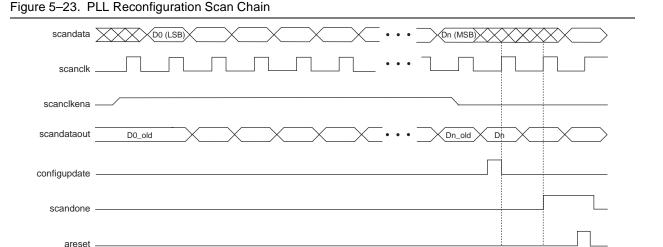

Figure 5–23 shows a functional simulation of the PLL reconfiguration feature.

When reconfiguring the counter clock frequency, the corresponding counter phase shift settings cannot be reconfigured using the same interface. You can reconfigure phase shifts in real time using the dynamic phase shift reconfiguration interface. If you reconfigure the counter frequency, but wish to keep the same non-zero phase shift setting (for example, 90°) on the clock output, you must reconfigure the phase shift after reconfiguring the counter clock frequency.

### Post-Scale Counters (C0 to C4)

You can configure multiply or divide values and duty cycle of post-scale counters in real time. Each counter has an 8-bit high time setting and an 8-bit low time setting. The duty cycle is the ratio of output high or low time to the total cycle time, that is the sum of the two. Additionally, these counters have two control bits, rbypass, for bypassing the counter, and rselodd, to select the output clock duty cycle.

When the rbypass bit is set to 1, it bypasses the counter, resulting in a divide by one. When this bit is set to 0, the PLL computes the effective division of the VCO output frequency based on the high and low time counters. For example, if the post-scale divide factor is 10, the high and low count values are set to 5 and 5, to achieve a 50–50% duty cycle. The PLL implements this duty cycle by transitioning the output clock from high-to-low on the rising edge of the VCO output clock. However, a 4 and 6 setting for the high and low count values, respectively, would produce an output clock with a 40–60% duty cycle.

The rselodd bit indicates an odd divide factor for the VCO output frequency with a 50% duty cycle. For example, if the post-scale divide factor is three, the high and low time count values are 2 and 1, respectively, to achieve this division. This implies a 67%–33% duty cycle. If you need a 50%–50% duty cycle, you must set the elodd control bit to 1 to achieve this duty cycle despite an odd division factor. The PLL implements this duty cycle by transitioning the output clock from high-to-low on a falling edge of the VCO output clock. When you set rselodd = 1, subtract 0.5 cycles from the high time and add 0.5 cycles to the low time.

For example:

High time count = 2 cycles

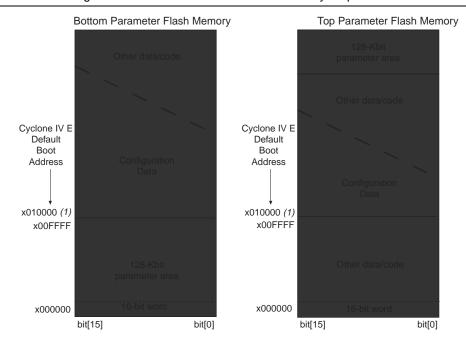

The default configuration boot address allows the system to use special parameter blocks in the flash memory map. Parameter blocks are at the top or bottom of the memory map. Figure 8–12 shows the configuration boot address in the AP configuration scheme. You can change the default configuration default boot address 0x010000 to any desired address using the APFC\_BOOT\_ADDRITAG instruction. For more information about the APFC\_BOOT\_ADDRITAG instruction, refer to "JTAG Instructions" on page 8–57.

Figure 8–12. Configuration Boot Address in AP Flash Memory Map

Note to Figure 8-12

(1) The default configuration boot address is x010000 when represented in 16-bit word addressing.

# **PS** Configuration

You can perform PS configuration on Cyclone IV devices with an external intelligent host, such as a MAX® II device, microprocessor with flash memory, or a download cable. In the PS scheme, an external host controls the configuration. Configuration data is clocked into the target Cyclone IV device through DATA[0] at each rising edge of DCLK

If your system already contains a common flash interface (CFI) flash memory, you can use it for Cyclone IV device configuration storage as well. The MAX II PFL feature provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control the configuration from the flash memory device to the Cyclone IV device.

- f For more information about the PFL, refer to AN 386: Using the Parallel Flash Loader with the Quartus II Software

- 1 Cyclone IV devices do not support enhanced configuration devices for PS configuration.

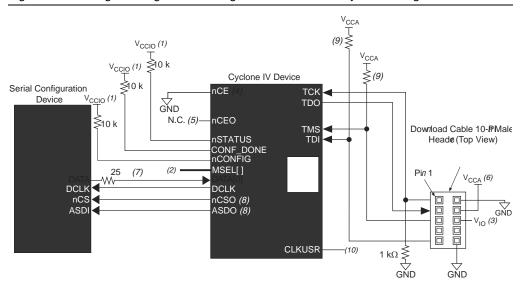

If you configure a master device with an SFL design, the master device enters user mode even though the slave devices in the multiple device chain are not being configured. The master device enters user mode with a SFL design even though the CONF\_DONEignal is externally held low by the other slave devices in chain. Figure 8–29 shows the JTAG configuration of a single Cyclone IV device with a SFL design.

Figure 8-29. Programming Serial Configuration Devices In-System Using the JTAG Interface

#### Notes to Figure 8-29

- (1) Connect the pull-up resistors to the supply of the bank in which the pin resides.

- (2) TheMSELpin settings vary for different configuration voltage standards and POR time. ToMSfrirfectAS configuration schemes, referflable 8–3 on page 8–Bable 8–4 on page 8,-andTable 8–5 on page 8–9onnect theMSELpins directly to

√CAOT GND.

- (3) Pin 6 of the header is a Veference voltage for the MasterBlaster output driver. In the the the of the device. For this value, refer to MasterBlaster Serial/USB Communications Cable User With the ByteBlasterMV download cable, this pin is a no connect. When using USB-Blaster, ByteBlaster II, and EthernetBlaster cables, this pin is connected the when it is used for AS programming, otherwise it is a no connect.

- (4) You must connect the Epin to GND or driven low for successful JTAG configuration.

- (5) ThenCEOpin is left unconnected or used as a user I/O pin when it does not fee@ pine of another device.

- (6) Power up the of the EthernetBlaster, ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a வர்ல் Third-party programmers must switch to 2.5 V. Pin 4 of the header is cawer supply for the MasterBlaster cable.

The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to MaeterBlaster Serial/USB Communications Cable User Guide

- (7) Connect the series resistor at the near end of the serial configuration device.

- (8) These pins are dual-purpose I/O pins notions as LASH\_nCEpin in AP mode. TIMSDOpin functions as DATA[1] pin in AP and FPP modes.

- (9) Resistor value can vary from 1 to 10 k:.

- (10) Only Cyclone IV GX devices have an option to Selfel R(40 MHz maximum) as the external clock source for DCI K

#### ISP of the Configuration Device

In the second stage, the SFL design in the master device allows you to write the configuration data for the device chain into the serial configuration device with the Cyclone IV device JTAG interface. The JTAG interface sends the programming data for the serial configuration device to the Cyclone IV device first. The Cyclone IV device then uses the ASMI pins to send the data to the serial configuration device.

In AP configuration scheme, the only way to re-engage the AP controller is to issue the ACTIVE\_ENGAGEnstruction. In this case, asserting thenCONFIGpin does not reengage either active controller.

### ACTIVE\_ENGAGE

The ACTIVE\_ENGAGEnstruction allows you to re-engage a disengaged active controller. You can issue this instruction any time during configuration or user mode to reengage an already disengaged active controller, as well as trigger reconfiguration of the Cyclone IV device in the active configuration scheme.

The ACTIVE\_ENGAGEnstruction functions as the PULSE\_NCONFIGnstruction when the device is in the PS or FPP configuration schemes. The CONFIGnin is disabled when the ACTIVE ENGAGEnstruction is issued.

Altera does not recommend using the ACTIVE\_ENGAGEInstruction, but it is provided as a fail-safe instruction for re-engaging the active configuration controller (AS and AP).

### Overriding the Internal Oscillator

This feature allows you to override the internal oscillator during the active configuration scheme. The AS and AP configuration controllers use the internal oscillator as the clock source. You can change the clock source to CLKUSR through the JTAG instruction.

The EN\_ACTIVE\_CLK and DIS\_ACTIVE\_CLK JTAG instructions toggle on or off whether or not the active clock is sourced from the CLKUSRpin or the internal configuration oscillator. To source the active clock from the CLKUSRpin, issue the EN\_ACTIVE\_CLK instruction. This causes the CLKUSRpin to become the active clock source. When using the EN\_ACTIVE\_CLKinstruction, you must enable the internal oscillator for the clock change to occur. By default, the configuration oscillator is disabled after configuration and initialization is complete as well as the device has entered user mode.

However, the internal oscillator is enabled in user mode by any of the following conditions:

A reconfiguration event (for example, driving the nCONFIGpin to go low)

Remote update is enabled

Error detection is enabled

When using the EN\_ACTIVE\_CLK and DIS\_ACTIVE\_CLK JTAG instructions to override the internal oscillator, you must clock the CLKUSRpin at two times the expected DCLK frequency. The CLKUSRpin allows a maximum frequency of 40 MHz (40 MHz DCLK).

Normally, a test instrument uses the CLKUSRpin when it wants to drive its own clock to control the AS state machine.

To revert the clock source back to the configuration oscillator, issue the DIS\_ACTIVE\_CLK instruction. After you issue the DIS\_ACTIVE\_CLK instruction, you must continue to clock the CLKUSRpin for 10 clock cycles. Otherwise, even toggling the nCONFIGpin does not revert the clock source and reconfiguration does not occur. A POR reverts the clock source back to the configuration oscillator. Toggling the nCONFIG pin or driving the JTAG state machine to reset state does not revert the clock source.

#### EN ACTIVE CLK

The EN\_ACTIVE\_CLKinstruction causes the CLKUSRpin signal to replace the internal oscillator as the clock source. When using the EN\_ACTIVE\_CLKinstruction, you must enable the internal oscillator for the clock change to occur. After this instruction is issued, other JTAG instructions can be issued while the CLKUSRpin signal remains as the clock source. The clock source is only reverted back to the internal oscillator by issuing the DIS\_ACTIVE\_CLK instruction or a POR.

#### DIS ACTIVE CLK

The DIS\_ACTIVE\_CLK instruction breaks the CLKUSRenable latch set by the EN\_ACTIVE\_CLKinstruction and causes the clock source to revert back to the internal oscillator. After the DIS\_ACTIVE\_CLK instruction is issued, you must continue to clock the CLKUSRpin for 10 clock cycles.

### Changing the Start Boot Address of the AP Flash

In the AP configuration scheme (for Cyclone IV E devices only), you can change the default configuration boot address of the parallel flash memory to any desired address using the APFC\_BOOT\_ADDRTAG instruction.

### APFC\_BOOT\_ADDR

The APFC\_BOOT\_ADDR struction is for Cyclone IV E devices only and allows you to define a start boot address for the parallel flash memory in the AP configuration scheme.

This instruction shifts in a start boot address for the AP flash. When this instruction becomes the active instruction, the TDI and TDOpins are connected through a 22-bit active boot address shift register. The shifted-in boot address bits get loaded into the 22-bit AP boot address update register, which feeds into the AP controller. The content of the AP boot address update register can be captured and shifted-out of the active boot address shift register from TDO

The boot address in the boot address shift register and update register are shifted to the right (in the LSB direction) by two bits versus the intended boot address. The reason for this is that the two LSB of the address are not accessible. When this boot address is fed into the AP controller, two 0s are attached in the end as LSB, thereby pushing the shifted-in boot address to the left by two bits, which become the actual AP boot address the AP controller gets.

If you have enabled the remote update feature, the APFC\_BOOT\_ADDR struction sets the boot address for the factory configuration only.

The APFC\_BOOT\_ADDMstruction is retained after reconfiguration while the system board is still powered on. However, you must reprogram the instruction whenever you restart the system board.

This chapter provides additional information about the document and Altera.

# About this Handbook

This handbook provides comprehensive information about the Altera® Cyclone® IV family of devices.

# How to Contact Altera

To locate the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                    | Contact Method | Address                   |

|--------------------------------|----------------|---------------------------|

| Technical support              | Website        | www.altera.com/support    |

| Technical training             | Website        | www.altera.com/training   |

| recrimear training             | Email          | custrain@altera.com       |

| Product literature             | Website        | www.altera.com/literature |

| Nontechnical support (general) | Email          | nacomp@altera.com         |

| (software licensing)           | Email          | authorization@altera.com  |

Note to Table:

# Typographic Conventions

The following table shows the typographic conventions this document uses.

| Visual Cue                                | Meaning                                                                                                                                                                                                  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial Capital<br>Letters | Indicate command names, dialog box titles, dialog box options, and other GUI labels. For example, Save As dialog box. For GUI elements, capitalization matches the GUI.                                  |

| bold type                                 | Indicates directory names, project names, disk drive names, file names, file name extensions, software utility names, and GUI labels. For example, \qdesigns directory, D: drive, and chiptrip.gdf file. |

| Italic Type with Initial Capital Letters  | Indicate document titles. For example, Stratix IV Design Guidelines.                                                                                                                                     |

|                                           | Indicates variables. For example, n + 1.                                                                                                                                                                 |

| italic type                               | Variable names are enclosed in angle brackets (< >). For example, <file name=""> and <project name="">.pof file.</project></file>                                                                        |

| Initial Capital Letters                   | Indicate keyboard keys and menu names. For example, the Delete key and the Options menu.                                                                                                                 |

| "Subheading Title"                        | Quotation marks indicate references to sections in a document and titles of Quartus II Help topics. For example, "Typographic Conventions."                                                              |

<sup>(1)</sup> You can also contact your local Altera sales office or sales representative.