#### Intel - EP4CE75F23C9LN Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                    |

|--------------------------------|-----------------------------------------------------------|

| Number of LABs/CLBs            | 4713                                                      |

| Number of Logic Elements/Cells | 75408                                                     |

| Total RAM Bits                 | 2810880                                                   |

| Number of I/O                  | 292                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 0.97V ~ 1.03V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 484-BGA                                                   |

| Supplier Device Package        | 484-FBGA (23x23)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce75f23c9ln |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| GCLK Network Clock              |              | GCLK Networks |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

|---------------------------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Sources                         | 0            | 1             | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           | 20           | 21           | 22           | 23           | 24           | 25           | 26           | 27           | 28           | 29           |

| CLKIO4/DIFFCLK_2n               | —            | —             | —            |              | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | $\checkmark$ |              | —            | —            | _            | —            | —            | _            |              |              | —            |              |              |              |

| CLKIO5/DIFFCLK_2p               | —            | _             | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | —            | —            | $\checkmark$ | —            |              |              | —            | —            |              | —            | —            | —            | —            |              | —            |

| CLKIO6/DIFFCLK_3n               | —            |               | —            | —            | —            | —            | —            | —            | —            |              | —            | —            | —            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              |              | _            | _            |              | —            | _            |              |              |              |              | —            | —            |

| CLKIO7/DIFFCLK_3p               | —            |               | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | ~            | —            |              | ~            | —            | $\checkmark$ |              |              | —            |              | —            | —            |              |              |              |              | —            | —            |

| CLKIO8/DIFFCLK_5n               | _            | _             | —            |              | —            |              | —            | —            |              |              | —            |              | —            | —            |              |              | —            |              | $\checkmark$ | _            | $\checkmark$ |              | $\checkmark$ | _            |              |              |              |              | —            | —            |

| CLKIO9/DIFFCLK_5p               | —            | _             | —            | —            | —            | —            | —            | —            | —            |              | —            | —            | —            | —            |              |              | —            |              |              | $\checkmark$ | $\checkmark$ |              | —            | $\checkmark$ |              |              |              |              | —            | —            |

| CLKIO10/DIFFCLK_4n/RE<br>FCLK3n |              |               | _            | _            |              | _            | _            |              | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | ~            | _            | ~            | ~            |              | _            | _            | _            | _            |              | —            |

| CLKIO11/DIFFCLK_4p/RE<br>FCLK3p | —            |               | _            | —            | _            | _            | —            | _            | _            | —            | _            | _            | —            | _            | _            | —            | —            | _            | ~            |              | _            | ~            | —            | ~            | _            | _            | —            | _            |              | —            |

| CLKIO12/DIFFCLK_7p/RE<br>FCLK2p | —            | _             | _            | _            | —            | —            | _            | —            | —            | _            | _            | —            | _            | _            | _            | —            | _            | _            | —            | _            |              | —            | _            | _            | ~            | _            | ~            | _            | ~            | —            |

| CLKIO13/DIFFCLK_7n/RE<br>FCLK2n | —            |               | _            | _            |              | _            | _            |              | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | ~            | ~            | _            |              | ~            |

| CLKIO14/DIFFCLK_6p              | —            |               | —            | _            | —            |              | —            | —            |              | —            | —            |              | —            | —            |              | —            | —            |              |              | _            | _            |              | —            | _            |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | —            |

| CLKIO15/DIFFCLK_6n              | —            |               | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            |              | —            | —            |              |              |              | —            |              | —            | —            | $\checkmark$ |              |              | $\checkmark$ | —            | $\checkmark$ |

| PLL_1_C0                        | $\checkmark$ |               | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            |              | —            | —            |              | —            | —            |              | —            | —            |              |              | _            | _            |              | —            | _            | $\checkmark$ |              |              | $\checkmark$ | —            | $\checkmark$ |

| PLL_1_C1                        | _            | >             | —            |              | $\checkmark$ |              | —            | —            |              |              | —            |              | —            | —            |              |              | _            |              |              | _            |              |              | _            |              | _            | ~            |              |              | $\checkmark$ | —            |

| PLL_1_C2                        | $\checkmark$ |               | $\checkmark$ | _            | —            | —            | _            | —            | —            |              | —            | —            | _            | —            |              | _            | —            |              | _            |              |              | _            | —            |              | $\checkmark$ |              | $\checkmark$ |              | —            | —            |

| PLL_1_C3                        | _            | >             | —            | $\checkmark$ | —            |              | —            | —            |              |              | —            |              | —            | —            |              |              | _            |              |              | _            |              |              | _            |              | _            | ~            |              | ~            | —            | —            |

| PLL_1_C4                        | -            | —             | $\checkmark$ |              | ~            | ~            | —            | _            |              |              | —            |              | —            | —            |              |              | _            |              |              | _            |              |              | _            |              |              |              | ~            |              | ~            | $\checkmark$ |

| PLL_2_C0                        | -            | _             | —            | _            | —            |              | $\checkmark$ | —            |              | ~            | —            | $\checkmark$ | —            | —            | _            |              | _            |              | ~            | _            |              | ~            | _            | <            | -            |              |              | -            |              | —            |

| PLL_2_C1                        | -            | —             | —            |              | _            |              | —            | ~            |              |              | $\checkmark$ |              | —            | —            |              |              | _            |              |              | ~            |              |              | ~            |              |              |              |              |              | —            | —            |

| PLL_2_C2                        | —            | —             | —            | _            | —            | _            | $\checkmark$ | —            | $\checkmark$ | —            | —            | _            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | _            | —            | —            | —            | —            | _            | —            | _            | —            |

| PLL_2_C3                        |              | _             | _            |              |              |              |              | $\checkmark$ |              | $\checkmark$ | _            |              |              | _            |              | —            |              |              | —            | $\checkmark$ |              | $\checkmark$ |              |              | —            |              |              | —            | —            | —            |

| PLL_2_C4                        | —            | _             | —            | _            | —            | _            | —            | —            | $\checkmark$ | _            | $\checkmark$ | $\checkmark$ | —            | —            | —            | _            | —            |              | _            | —            | $\checkmark$ | _            | $\checkmark$ | $\checkmark$ | —            |              | _            | —            |              | —            |

### Table 5–2. GCLK Network Connections for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices <sup>(1), (2)</sup> (Part 1 of 4)

October 2012 Altera Corporation

| Signal Name | Description                                                                                                                                                                                                                                | Source                      | Destination                       |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------|--|

| scanclk     | Free running clock from core used in<br>combination with phasestep to enable or<br>disable dynamic phase shifting. Shared with<br>scanclk for dynamic reconfiguration.                                                                     | GCLK or I/O pins            | PLL<br>reconfiguration<br>circuit |  |

| phasedone   | When asserted, it indicates to core logic that<br>the phase adjustment is complete and PLL is<br>ready to act on a possible second adjustment<br>pulse. Asserts based on internal PLL timing.<br>De-asserts on the rising edge of scanclk. | PLL reconfiguration circuit | Logic array or<br>I/O pins        |  |

| Table 5-12. | <b>Dynamic Phase</b> | Shiftina | <b>Control Sign</b> | als ( | (Part 2 of 2) |

|-------------|----------------------|----------|---------------------|-------|---------------|

|             |                      | ••••••   | eenner ergn         |       |               |

Table 5–13 lists the PLL counter selection based on the corresponding PHASECOUNTERSELECT setting.

Table 5–13. Phase Counter Select Mapping

|     | phasecounterselec | Colosta |                     |  |  |

|-----|-------------------|---------|---------------------|--|--|

| [2] | [1]               | [0]     | Selects             |  |  |

| 0   | 0                 | 0       | All Output Counters |  |  |

| 0   | 0                 | 1       | M Counter           |  |  |

| 0   | 1                 | 0       | C0 Counter          |  |  |

| 0   | 1                 | 1       | C1 Counter          |  |  |

| 1   | 0                 | 0       | C2 Counter          |  |  |

| 1   | 0                 | 1       | C3 Counter          |  |  |

| 1   | 1                 | 0       | C4 Counter          |  |  |

To perform one dynamic phase-shift, follow these steps:

- 1. Set PHASEUPDOWN and PHASECOUNTERSELECT as required.

- 2. Assert PHASESTEP for at least two SCANCLK cycles. Each PHASESTEP pulse allows one phase shift.

- 3. Deassert PHASESTEP after PHASEDONE goes low.

- 4. Wait for PHASEDONE to go high.

- 5. Repeat steps 1 through 4 as many times as required to perform multiple phaseshifts.

<code>PHASEUPDOWN</code> and <code>PHASECOUNTERSELECT</code> signals are synchronous to <code>SCANCLK</code> and must meet the  $t_{su}$  and  $t_h$  requirements with respect to the <code>SCANCLK</code> edges.

You can repeat dynamic phase-shifting indefinitely. For example, in a design where the VCO frequency is set to 1,000 MHz and the output clock frequency is set to 100 MHz, performing 40 dynamic phase shifts (each one yields 125 ps phase shift) results in shifting the output clock by 180°, in other words, a phase shift of 5 ns.

- "Pad Placement and DC Guidelines" on page 6–23

- "Clock Pins Functionality" on page 6–23

- "High-Speed I/O Interface" on page 6–24

- "High-Speed I/O Standards Support" on page 6–28

- "True Differential Output Buffer Feature" on page 6–35

- "High-Speed I/O Timing" on page 6–36

- "Design Guidelines" on page 6–37

- "Software Overview" on page 6–38

## **Cyclone IV I/O Elements**

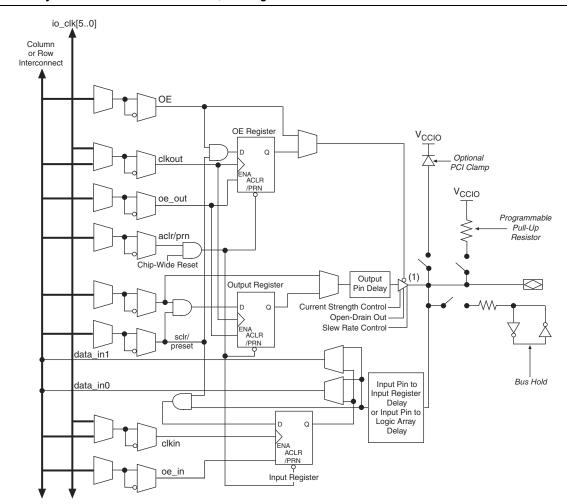

Cyclone IV I/O elements (IOEs) contain a bidirectional I/O buffer and five registers for registering input, output, output-enable signals, and complete embedded bidirectional single-data rate transfer. I/O pins support various single-ended and differential I/O standards.

The IOE contains one input register, two output registers, and two output-enable (OE) registers. The two output registers and two OE registers are used for DDR applications. You can use input registers for fast setup times and output registers for fast clock-to-output times. Additionally, you can use OE registers for fast clock-to-output enable timing. You can use IOEs for input, output, or bidirectional data paths.

Figure 6–1 shows the Cyclone IV devices IOE structure for single data rate (SDR) operation.

#### Figure 6-1. Cyclone IV IOEs in a Bidirectional I/O Configuration for SDR Mode

#### Note to Figure 6–1:

(1) Tri-state control is not available for outputs configured with true differential I/O standards.

## **I/O Element Features**

The Cyclone IV IOE offers a range of programmable features for an I/O pin. These features increase the flexibility of I/O utilization and provide a way to reduce the usage of external discrete components, such as pull-up resistors and diodes.

### **Programmable Current Strength**

The output buffer for each Cyclone IV I/O pin has a programmable current strength control for certain I/O standards.

The LVTTL, LVCMOS, SSTL-2 Class I and II, SSTL-18 Class I and II, HSTL-18 Class I and II, HSTL-15 Class I and II, and HSTL-12 Class I and II I/O standards have several levels of current strength that you can control.

### **External Memory Interfacing**

Cyclone IV devices support I/O standards required to interface with a broad range of external memory interfaces, such as DDR SDRAM, DDR2 SDRAM, and QDR II SRAM.

For more information about Cyclone IV devices external memory interface support, refer to the *External Memory Interfaces in Cyclone IV Devices* chapter.

## **Pad Placement and DC Guidelines**

You can use the Quartus II software to validate your pad and pin placement.

### **Pad Placement**

Altera recommends that you create a Quartus II design, enter your device I/O assignments and compile your design to validate your pin placement. The Quartus II software checks your pin connections with respect to the I/O assignment and placement rules to ensure proper device operation. These rules depend on device density, package, I/O assignments, voltage assignments and other factors that are not fully described in this chapter.

For more information about how the Quartus II software checks I/O restrictions, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

### **DC Guidelines**

For the Quartus II software to automatically check for illegally placed pads according to the DC guidelines, set the DC current sink or source value to **Electromigration Current** assignment on each of the output pins that are connected to the external resistive load.

The programmable current strength setting has an impact on the amount of DC current that an output pin can source or sink. Determine if the current strength setting is sufficient for the external resistive load condition on the output pin.

## **Clock Pins Functionality**

Cyclone IV clock pins have multiple purposes, as per listed:

- CLK pins—Input support for single-ended and voltage-referenced standards. For I/O standard support, refer to Table 6–3 on page 6–11.

- DIFFCLK pins—Input support for differential standards. For I/O standard support, refer to Table 6–3 on page 6–11. When used as DIFFCLK pins, DC or AC coupling can be used depending on the interface requirements and external termination is required. For more information, refer to "High-Speed I/O Standards Support" on page 6–28.

- REFCLK pins—Input support for high speed differential reference clocks used by the transceivers in Cyclone IV GX devices. For I/O support, coupling, and termination requirements, refer to Table 6–10 on page 6–29.

# Section III. System Integration

This section includes the following chapters:

- Chapter 8, Configuration and Remote System Upgrades in Cyclone IV Devices

- Chapter 9, SEU Mitigation in Cyclone IV Devices

- Chapter 10, JTAG Boundary-Scan Testing for Cyclone IV Devices

- Chapter 11, Power Requirements for Cyclone IV Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

## **Device Configuration Pins**

Table 8–18 through Table 8–21 describe the connections and functionality of all the configuration related pins on Cyclone IV devices. Table 8–18 and Table 8–19 list the device pin configuration for the Cyclone IV GX and Cyclone IV E, respectively.

Table 8–18. Configuration Pin Summary for Cyclone IV GX Devices

| Bank | Description        | Input/Output  | Dedicated | Powered By                     | <b>Configuration Mode</b> |

|------|--------------------|---------------|-----------|--------------------------------|---------------------------|

| 8    | Data[4:2]          | Input         | —         | V <sub>CCIO</sub>              | FPP                       |

| 3    | Data[7:5]          | Input         |           | V <sub>CCIO</sub>              | FPP                       |

| 9    | nCSO (2)           | Output        |           | V <sub>CCIO</sub>              | AS                        |

| 3    | CRC_ERROR          | Output        | —         | V <sub>CCIO</sub> /Pull-up (1) | Optional, all modes       |

| 9    | DATA[0] (2)        | Input         | Yes       | V <sub>CCIO</sub>              | PS, FPP, AS               |

| 9    | DATA [1] /ASDO (2) | Input         |           | V <sub>CCIO</sub>              | FPP                       |

| 9    | DATA[1]/ASDO (2)   | Output        |           | V <sub>CCIO</sub>              | AS                        |

| 3    | INIT_DONE          | Output        |           | Pull-up                        | Optional, all modes       |

| 3    | nSTATUS            | Bidirectional | Yes       | Pull-up                        | All modes                 |

| 9    | nCE                | Input         | Yes       | V <sub>CCIO</sub>              | All modes                 |

| 9    | DCLK (2)           | Input         | Yes       | V <sub>CCIO</sub>              | PS, FPP                   |

| 9    | DCLK (-)           | Output        | res       | V <sub>CCIO</sub>              | AS                        |

| 3    | CONF_DONE          | Bidirectional | Yes       | Pull-up                        | All modes                 |

| 9    | TDI                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | TMS                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | TCK                | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 9    | nCONFIG            | Input         | Yes       | V <sub>CCIO</sub>              | All modes                 |

| 8    | CLKUSR             | Input         |           | V <sub>CCIO</sub>              | Optional                  |

| 3    | nCEO               | Output        |           | V <sub>ccio</sub>              | Optional, all modes       |

| 3    | MSEL               | Input         | Yes       | V <sub>CCINT</sub>             | All modes                 |

| 9    | TDO                | Output        | Yes       | V <sub>CCIO</sub>              | JTAG                      |

| 6    | DEV_OE             | Input         | —         | V <sub>CCIO</sub>              | Optional                  |

| 6    | DEV_CLRn           | Input         | —         | V <sub>CCIO</sub>              | Optional                  |

Notes to Table 8-18:

(1) The CRC\_ERROR pin is a dedicated open-drain output or an optional user I/O pin. Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device and Pin Options dialog box. When using this pin, connect it to an external 10-kΩ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.

(2) To tri-state AS configuration pins in the AS configuration scheme, turn on the **Enable input tri-state on active configuration pins in user mode** option from the **Device and Pin Options** dialog box. This tri-states DCLK, nCSO, Data[0], and Data[1]/ASDO pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the **Enable input tri-state on active configuration pins in user mode** option and set the desired setting from the Dual-purpose Pins Setting menu.

| Bank | Description               | Input/Output | Dedicated | Powered By                            | <b>Configuration Mode</b> |

|------|---------------------------|--------------|-----------|---------------------------------------|---------------------------|

| 1    | nCSO (1)<br>FLASH_nCE (2) | Output       | —         | V <sub>CCIO</sub>                     | AS, AP                    |

| 6    | CRC_ERROR (3)             | Output       | —         | V <sub>CCIO</sub> /Pull-up <i>(4)</i> | Optional, all modes       |

The user watchdog timer is disabled in factory configurations and during the configuration cycle of the application configuration. It is enabled after the application configuration enters user mode.

## **Quartus II Software Support**

Implementation in your design requires a remote system upgrade interface between the Cyclone IV device logic array and remote system upgrade circuitry. You must also generate configuration files for production and remote programming of the system configuration memory. The Quartus II software provides these features.

The two implementation options, ALTREMOTE\_UPDATE megafunction and remote system upgrade atom, are for the interface between the remote system upgrade circuitry and the device logic array interface. Using the megafunction block instead of creating your own logic saves design time and offers more efficient logic synthesis and device implementation.

• For more information about the ALTREMOTE\_UPDATE megafunction, refer to the *Remote Update Circuitry (ALTREMOTE\_UPDATE) Megafunction User Guide*.

# **Document Revision History**

Table 8–28 lists the revision history for this chapter.

| Date          | Version | Changes                                                                                                                                                             |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         | Added Table 8–6.                                                                                                                                                    |

|               |         | <ul> <li>Updated Table 8–9 to add new device options and packages.</li> </ul>                                                                                       |

| May 2013      | 1.7     | <ul> <li>Updated Figure 8–16 and Figure 8–22 to include user mode.</li> </ul>                                                                                       |

|               |         | <ul> <li>Updated the "Dedicated" column for DATA[0] and DCLK in Table 8–19.</li> </ul>                                                                              |

|               |         | <ul> <li>Updated the "User Mode" and "Pin Type" columns for DCLK in Table 8–20.</li> </ul>                                                                          |

| February 2013 | 1.6     | Updated Table 8–9 to add new device options and packages.                                                                                                           |

|               |         | <ul> <li>Updated "AP Configuration Supported Flash Memories", "Configuration Data<br/>Decompression", and "Overriding the Internal Oscillator" sections.</li> </ul> |

| October 2012  | 1.5     | ■ Updated Figure 8–3, Figure 8–4, Figure 8–5, Figure 8–7, Figure 8–8, Figure 8–9, Figure 8–10, and Figure 8–11.                                                     |

|               |         | ■ Updated Table 8–2, Table 8–8, Table 8–12, Table 8–13, Table 8–18, and Table 8–1                                                                                   |

|               |         | <ul> <li>Added information about how to gain control of EPCS pins.</li> </ul>                                                                                       |

|               |         | <ul> <li>Updated "Reset", "Single-Device AS Configuration", "Single-Device AP<br/>Configuration", and "Overriding the Internal Oscillator" sections.</li> </ul>     |

| November 2011 | 1.4     | ■ Added Table 8–7.                                                                                                                                                  |

|               |         | ■ Updated Table 8–6 and Table 8–19.                                                                                                                                 |

|               |         | ■ Updated Figure 8–3, Figure 8–4, and Figure 8–5.                                                                                                                   |

| December 2010 |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                                       |

|               | 1.3     | <ul> <li>Added Cyclone IV E new device package information.</li> </ul>                                                                                              |

| December 2010 | 1.0     | ■ Updated Table 8–7, Table 8–10, and Table 8–11.                                                                                                                    |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                                               |

Table 8–28. Document Revision History (Part 1 of 2)

8-19.

<sup>••••</sup>

In some applications, it is necessary for a device to wake up very quickly to begin operation. Cyclone IV devices offer the Fast-On feature to support fast wake-up time applications. The MSEL pin settings determine the POR time ( $t_{POR}$ ) of the device.

- **To** For more information about the MSEL pin settings, refer to the *Configuration and Remote System Upgrades in Cyclone IV Devices* chapter.

- For more information about the POR specifications, refer to the *Cyclone IV Device Datasheet* chapter.

# **Document Revision History**

Table 11–3 lists the revision history for this chapter.

Table 11-3. Document Revision History

| Date          | Version | Changes                                                                                                                                                                           |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2013      | 1.3     | Updated Note (4) in Table 11–1.                                                                                                                                                   |

| July 2010     | 1.2     | <ul> <li>Updated for the Quartus II software version 10.0 release.</li> <li>Updated "I/O Pins Remain Tri-stated During Power-Up" section.</li> <li>Updated Table 11–1.</li> </ul> |

| February 2010 | 1.1     | Updated Table 11–1 and Table 11–2 for the Quartus II software version 9.1 SP1 release.                                                                                            |

| November 2009 | 1.0     | Initial release.                                                                                                                                                                  |

This chapter provides additional information about the document and Altera.

# **About this Handbook**

This handbook provides comprehensive information about the Altera<sup>®</sup> Cyclone<sup>®</sup> IV family of devices.

## **How to Contact Altera**

To locate the most up-to-date information about Altera products, refer to the following table.

| Contact <sup>(1)</sup>         | <b>Contact Method</b> | Address                   |

|--------------------------------|-----------------------|---------------------------|

| Technical support              | Website               | www.altera.com/support    |

| Technical training             | Website               | www.altera.com/training   |

|                                | Email                 | custrain@altera.com       |

| Product literature             | Website               | www.altera.com/literature |

| Nontechnical support (general) | Email                 | nacomp@altera.com         |

| (software licensing)           | Email                 | authorization@altera.com  |

Note to Table:

(1) You can also contact your local Altera sales office or sales representative.

# **Typographic Conventions**

The following table shows the typographic conventions this document uses.

| Visual Cue                                | Meaning                                                                                                                                                                                                                             |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial Capital<br>Letters | Indicate command names, dialog box titles, dialog box options, and other GUI labels. For example, <b>Save As</b> dialog box. For GUI elements, capitalization matches the GUI.                                                      |

| bold type                                 | Indicates directory names, project names, disk drive names, file names, file name<br>extensions, software utility names, and GUI labels. For example, <b>\qdesigns</b><br>directory, <b>D:</b> drive, and <b>chiptrip.gdf</b> file. |

| Italic Type with Initial Capital Letters  | Indicate document titles. For example, Stratix IV Design Guidelines.                                                                                                                                                                |

|                                           | Indicates variables. For example, $n + 1$ .                                                                                                                                                                                         |

| italic type                               | Variable names are enclosed in angle brackets (< >). For example, <i><file name=""></file></i> and <i><project name="">.pof</project></i> file.                                                                                     |

| Initial Capital Letters                   | Indicate keyboard keys and menu names. For example, the Delete key and the Options menu.                                                                                                                                            |

| "Subheading Title"                        | Quotation marks indicate references to sections in a document and titles of Quartus II Help topics. For example, "Typographic Conventions."                                                                                         |

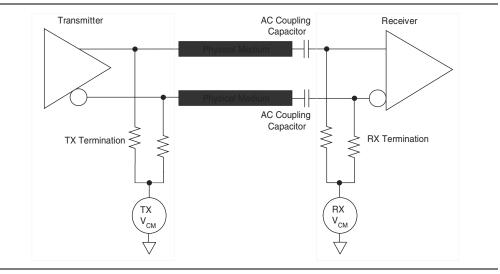

The high-speed serial link can be AC- or DC-coupled, depending on the serial protocol implementation. In an AC-coupled link, the AC-coupling capacitor blocks the transmitter DC common mode voltage as shown in Figure 1–12. Receiver OCT and on-chip biasing circuitry automatically restores the common mode voltage. The biasing circuitry is also enabled by enabling OCT. If you disable the OCT, then you must externally terminate and bias the receiver. AC-coupled links are required for PCIe, GbE, Serial RapidIO, SDI, XAUI, SATA, V-by-One and Display Port protocols.

Figure 1–12. AC-Coupled Link with OCT

### **Clock Frequency Compensation**

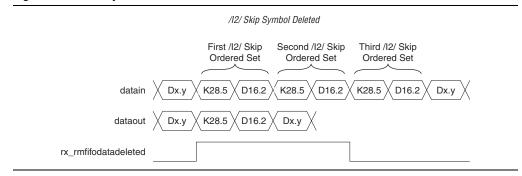

In GIGE mode, the rate match FIFO compensates up to  $\pm 100$  ppm (200 ppm total) difference between the upstream transmitter and the local receiver reference clock. The GIGE protocol requires the transmitter to send idle ordered sets /I1/ (/K28.5/D5.6/) and /I2/ (/K28.5/D16.2/) during inter-packet gaps, adhering to the rules listed in the IEEE 802.3 specification.

The rate match operation begins after the synchronization state machine in the word aligner indicates synchronization has been acquired by driving the rx\_syncstatus signal high. The rate match FIFO deletes or inserts both symbols of the /I2/ ordered sets (/K28.5/ and /D16.2/) to prevent the rate match FIFO from overflowing or underflowing. It can insert or delete as many /I2/ ordered sets as necessary to perform the rate match operation.

IF you have the auto-negotiation state machine in the FPGA, note that the rate match FIFO is capable of inserting or deleting the first two bytes (/K28.5//D2.2/) of /C2/ ordered sets during auto-negotiation. However, the insertion or deletion of the first two bytes of /C2/ ordered sets can cause the auto-negotiation link to fail. For more information, refer to the Altera Knowledge Base Support Solution.

The status flags rx\_rmfifodatadeleted and rx\_rmfifodatainserted to indicate rate match FIFO deletion and insertion events, respectively, are forwarded to the FPGA fabric. These two flags are asserted for two clock cycles for each deleted and inserted /I2/ ordered set.

Figure 1–58 shows an example of rate match FIFO deletion where three symbols must be deleted. Because the rate match FIFO can only delete /I2/ ordered sets, it deletes two /I2/ ordered sets (four symbols deleted).

#### Figure 1–58. Example of Rate Match FIFO Deletion in GIGE Mode

In Serial RapidIO mode, the rate match FIFO compensates up to  $\pm 100$  ppm (200 ppm total) difference between the upstream transmitter and the local receiver reference clock.

Rate matcher is an optional block available for selection in Serial RapidIO mode. However, this block is not fully compliant to the SRIO specification. When enabled in the ALTGX MegaWizard Plug-In Manager, the default settings are:

- control pattern 1 = K28.5 with positive disparity

- skip pattern 1 = K29.7 with positive disparity

- control pattern 2 = K28.5 with negative disparity

- skip pattern 2 = K29.7 with negative disparity

When enabled, the rate match FIFO operation begins after the link is synchronized (indicated by assertion of rx\_syncstatus from the word aligner). When the rate matcher receives either of the two 10-bit control patterns followed by the respective 10-bit skip pattern, it inserts or deletes the 10-bit skip pattern as necessary to avoid the rate match FIFO from overflowing or under-running. The rate match FIFO can delete/insert a maximum of one skip pattern from a cluster.

The rate match FIFO may perform multiple insertion or deletion if the ppm difference is more than the allowable 200 ppm range. Ensure that the ppm difference in your system is less than 200 ppm.

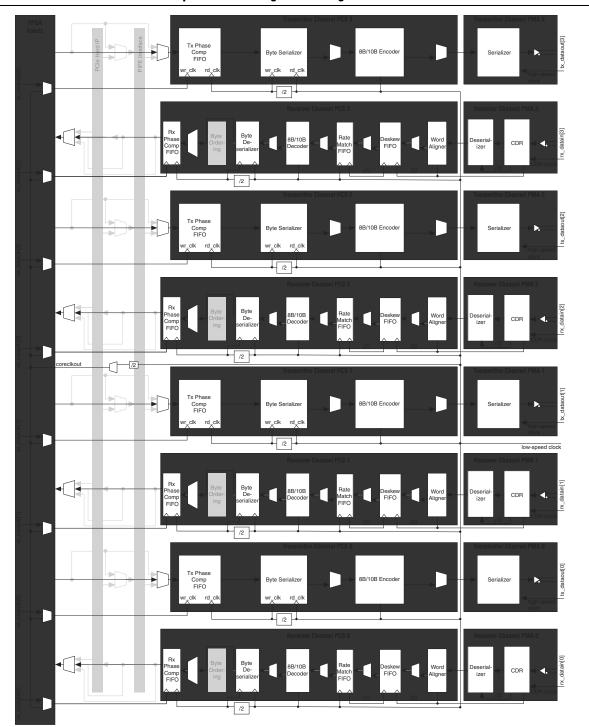

### **XAUI Mode**

XAUI mode provides the bonded (×4) transceiver channel datapath configuration for XAUI protocol implementation. The Cyclone IV GX transceivers configured in XAUI mode provides the following functions:

- XGMII-to-PCS code conversion at transmitter datapath

- PCS-to-XGMII code conversion at receiver datapath

- channel deskewing of four lanes

- 8B/10B encoding and decoding

- IEEE P802.3ae-compliant synchronization state machine

- clock rate compensation

The XAUI is a self-managed interface to transparently extend the physical reach of the XGMII between the reconciliation sublayer and the PHY layer in the 10 Gbps LAN as shown in Figure 1–62. The XAUI interface consists of four lanes, each running at 3.125 Gbps with 8B/10B encoded data for a total of actual 10 Gbps data throughput. At the transmit side of the XAUI interface, the data and control characters are

Figure 1–63 shows the transceiver channel datapath and clocking when configured in XAUI mode.

#### Notes to Figure 1-63:

- (1) Channel 1 low-speed recovered clock.

- (2) Low-speed recovered clock.

- (3) High-speed recovered clock.

The following are the channel reconfiguration mode options:

- Channel interface reconfiguration

- Data rate division at receiver channel

### **Channel Interface Reconfiguration Mode**

Enable this option if the reconfiguration of the transceiver channel involves the following changes:

- The reconfigured channel has a changed FPGA fabric-Transceiver channel interface data width

- The reconfigured channel has changed input control signals and output status signals

- The reconfigured channel has enabled and disabled the static PCS blocks of the transceiver channel

The following are the new input signals available when you enable this option:

- tx\_datainfull—the width of this input signal depends on the number of channels you set up in the ALTGX MegaWizard Plug-In Manager. It is 22 bits wide per channel. This signal is available only for Transmitter only and Receiver and Transmitter configurations. This port replaces the existing tx\_datain port.

- rx\_dataoutfull—the width of this output signal depends on the number of channels you set up in the ALTGX MegaWizard Plug-In Manager. It is 32 bits wide per channel. This signal is available only for **Receiver only** and **Receiver and Transmitter** configurations. This port replaces the existing rx\_dataout port.

The Quartus II software has legality checks for the connectivity of tx\_datainfull and rx\_dataoutfull and the various control and status signals you enable in the **Clocking/Interface** screen. For example, the Quartus II software allows you to select and connect the pipestatus and powerdn signals. It assumes that you are planning to switch to and from PCI Express (PIPE) functional mode.

| FPGA Fabric-Transceiver Channel<br>Interface Description | Receive Signal Description (Based on Cyclone IV GX Supported FPGA<br>Fabric-Transceiver Channel Interface Widths)                                                       |  |  |  |  |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                          | Two 8-bit unencoded Data (rx_dataout)                                                                                                                                   |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[7:0] - rx_dataout (LSByte) and                                                                                                                           |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[23:16]-rx_dataout (MSByte)                                                                                                                               |  |  |  |  |  |  |

|                                                          | The following signals are used in 16-bit 8B/10B modes:                                                                                                                  |  |  |  |  |  |  |

|                                                          | Two Control Bits                                                                                                                                                        |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[8] - rx_ctrldetect (LSB) and</pre>                                                                                                                  |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[24]-rx_ctrldetect (MSB)</pre>                                                                                                                       |  |  |  |  |  |  |

|                                                          | Two Receiver Error Detect Bits                                                                                                                                          |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[9] - rx_errdetect (LSB) and</pre>                                                                                                                   |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[25]-rx_errdetect (MSB)</pre>                                                                                                                        |  |  |  |  |  |  |

|                                                          | Two Receiver Sync Status Bits                                                                                                                                           |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull [10] - rx_syncstatus (LSB) and</pre>                                                                                                                |  |  |  |  |  |  |

| 16-bit FPGA fabric-Transceiver                           | <pre>rx_dataoutfull[26] - rx_syncstatus (MSB)</pre>                                                                                                                     |  |  |  |  |  |  |

| Channel Interface with PCS-PMA set to 8/10 bits          | Two Receiver Disparity Error Bits                                                                                                                                       |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull [11] - rx_disperr (LSB) and</pre>                                                                                                                   |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[27] - rx_disperr (MSB)</pre>                                                                                                                        |  |  |  |  |  |  |

|                                                          | Two Receiver Pattern Detect Bits                                                                                                                                        |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[12] - rx_patterndetect (LSB) and</pre>                                                                                                              |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[28] - rx_patterndetect (MSB)</pre>                                                                                                                  |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[13] and rx_dataoutfull[29]: Rate Match FIFO deletion statu<br/>indicator (rx_rmfifodatadeleted) in non-PCI Express (PIPE) functional modes</pre>    |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[14] and rx_dataoutfull[30]: Rate Match FIFO insertion status<br/>indicator (rx_rmfifodatainserted) in non-PCI Express (PIPE) functional modes</pre> |  |  |  |  |  |  |

|                                                          | Two 2-bit PCI Express (PIPE) Functional Mode Status Bits                                                                                                                |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[14:13] - rx_pipestatus (LSB) and rx_dataoutfull[30:29] · rx_pipestatus (MSB)</pre>                                                                  |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[15] and rx_dataoutfull[31]: 8B/10B running disparity indicator (rx_runningdisp)</pre>                                                               |  |  |  |  |  |  |

### Table 3–5. rx\_dataoutfull[31..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions (Part 2 of 3)

# **Functional Simulation of the Dynamic Reconfiguration Process**

This section describes the points to be considered during functional simulation of the dynamic reconfiguration process.

- You must connect the ALTGX\_RECONFIG instance to the ALTGX\_instance/ALTGX instances in your design for functional simulation.

- The functional simulation uses a reduced timing model of the dynamic reconfiguration controller. The duration of the offset cancellation process is 16 reconfig\_clk clock cycles for functional simulation only.

- The gxb\_powerdown signal must not be asserted during the offset cancellation sequence (for functional simulation and silicon).

# **Document Revision History**

Table 3–8 lists the revision history for this chapter.

Table 3–8.

Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                                                                                        |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2011 | 2.1     | <ul> <li>Updated "Dynamic Reconfiguration Controller Architecture", "PMA Controls<br/>Reconfiguration Mode", "PLL Reconfiguration Mode", and "Error Indication During<br/>Dynamic Reconfiguration" sections.</li> </ul>                                                                        |

|               |         | ■ Updated Table 3–2 and Table 3–4.                                                                                                                                                                                                                                                             |

|               |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                                                                                                                                                                  |

|               |         | ■ Updated Table 3–1, Table 3–2, Table 3–3, Table 3–4, Table 3–5, and Table 3–6.                                                                                                                                                                                                                |

|               |         | ■ Added Table 3–7.                                                                                                                                                                                                                                                                             |

| December 2010 | 2.0     | ■ Updated Figure 3–1, Figure 3–11, Figure 3–13, and Figure 3–14.                                                                                                                                                                                                                               |

|               |         | <ul> <li>Updated "Offset Cancellation Feature", "Error Indication During Dynamic<br/>Reconfiguration", "Data Rate Reconfiguration Mode Using RX Local Divider", "PMA<br/>Controls Reconfiguration Mode", and "Control and Status Signals for Channel<br/>Reconfiguration" sections.</li> </ul> |

| July 2010     | 1.0     | Initial release.                                                                                                                                                                                                                                                                               |

This chapter provides additional information about the document and Altera.

# **About this Handbook**

This handbook provides comprehensive information about the Altera<sup>®</sup> Cyclone<sup>®</sup> IV family of devices.

## **How to Contact Altera**

To locate the most up-to-date information about Altera products, refer to the following table.

| Contact <sup>(1)</sup>         | <b>Contact Method</b> | Address                   |  |  |

|--------------------------------|-----------------------|---------------------------|--|--|

| Technical support              | Website               | www.altera.com/support    |  |  |

| Technical training             | Website               | www.altera.com/training   |  |  |

| recinical training             | Email                 | custrain@altera.com       |  |  |

| Product literature             | Website               | www.altera.com/literature |  |  |

| Nontechnical support (general) | Email                 | nacomp@altera.com         |  |  |

| (software licensing)           | Email                 | authorization@altera.com  |  |  |

Note to Table:

(1) You can also contact your local Altera sales office or sales representative.

# **Typographic Conventions**

The following table shows the typographic conventions this document uses.

| Visual Cue                                | Meaning                                                                                                                                                                                                                       |  |  |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bold Type with Initial Capital<br>Letters | Indicate command names, dialog box titles, dialog box options, and other GUI labels. For example, <b>Save As</b> dialog box. For GUI elements, capitalization matche the GUI.                                                 |  |  |  |  |  |

| bold type                                 | Indicates directory names, project names, disk drive names, file names, file name extensions, software utility names, and GUI labels. For example, <b>\qdesigns</b> directory, <b>D:</b> drive, and <b>chiptrip.gdf</b> file. |  |  |  |  |  |

| Italic Type with Initial Capital Letters  | Indicate document titles. For example, Stratix IV Design Guidelines.                                                                                                                                                          |  |  |  |  |  |

|                                           | Indicates variables. For example, $n + 1$ .                                                                                                                                                                                   |  |  |  |  |  |

| italic type                               | Variable names are enclosed in angle brackets (< >). For example, <i><file name=""></file></i> and <i><project name="">.pof</project></i> file.                                                                               |  |  |  |  |  |

| Initial Capital Letters                   | Indicate keyboard keys and menu names. For example, the Delete key and the Options menu.                                                                                                                                      |  |  |  |  |  |

| "Subheading Title"                        | Quotation marks indicate references to sections in a document and titles of Quartus II Help topics. For example, "Typographic Conventions."                                                                                   |  |  |  |  |  |

| Visual Cue                               | Meaning                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input. The suffix n denotes an active-low signal. For example, resetn.                 |

| Courier type                             | Indicates command line commands and anything that must be typed exactly as it appears. For example, c:\qdesigns\tutorial\chiptrip.gdf.                                                 |

|                                          | Also indicates sections of an actual file, such as a Report File, references to parts of files (for example, the AHDL keyword SUBDESIGN), and logic function names (for example, TRI). |

| 4                                        | An angled arrow instructs you to press the Enter key.                                                                                                                                  |

| 1., 2., 3., and<br>a., b., c., and so on | Numbered steps indicate a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                          |

|                                          | Bullets indicate a list of items when the sequence of the items is not important.                                                                                                      |

| IP                                       | The hand points to information that requires special attention.                                                                                                                        |

| ?                                        | The question mark directs you to a software help system with related information.                                                                                                      |

| ••                                       | The feet direct you to another document or website with related information.                                                                                                           |

| <b>I</b> , <b>™</b> I                    | The multimedia icon directs you to a related multimedia presentation.                                                                                                                  |

| CAUTION                                  | A caution calls attention to a condition or possible situation that can damage or destroy the product or your work.                                                                    |

| VARNING                                  | A warning calls attention to a condition or possible situation that can cause you injury.                                                                                              |

|                                          | The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents.                 |

Table 1–44 and Table 1–45 list the IOE programmable delay for Cyclone IV GX devices.

| Parameter                                                             |                                   | Number<br>of<br>Settings | Min<br>Offset | Max Offset  |       |             |       |       |       |      |

|-----------------------------------------------------------------------|-----------------------------------|--------------------------|---------------|-------------|-------|-------------|-------|-------|-------|------|

|                                                                       | Paths<br>Affected                 |                          |               | Fast Corner |       | Slow Corner |       |       |       | Unit |

|                                                                       |                                   |                          |               | C6          | 17    | C6          | C7    | C8    | 17    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core  | 7                        | 0             | 1.313       | 1.209 | 2.184       | 2.336 | 2.451 | 2.387 | ns   |

| Input delay from pin to input register                                | Pad to I/O<br>input register      | 8                        | 0             | 1.312       | 1.208 | 2.200       | 2.399 | 2.554 | 2.446 | ns   |

| Delay from output<br>register to output pin                           | I/O output<br>register to<br>pad  | 2                        | 0             | 0.438       | 0.404 | 0.751       | 0.825 | 0.886 | 0.839 | ns   |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock<br>network | 12                       | 0             | 0.713       | 0.682 | 1.228       | 1.41  | 1.566 | 1.424 | ns   |

Notes to Table 1-44:

(1) The incremental values for the settings are generally linear. For exact values of each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software.

| Parameter                                                             | Paths<br>Affected                | Number<br>of<br>Settings | Min<br>Offset | Max Offset  |       |             |            |       |       |      |

|-----------------------------------------------------------------------|----------------------------------|--------------------------|---------------|-------------|-------|-------------|------------|-------|-------|------|

|                                                                       |                                  |                          |               | Fast Corner |       | Slow Corner |            |       |       | Unit |

|                                                                       |                                  |                          |               | C6          | 17    | C6          | <b>C</b> 7 | C8    | 17    |      |

| Input delay from pin to internal cells                                | Pad to I/O<br>dataout to<br>core | 7                        | 0             | 1.314       | 1.210 | 2.209       | 2.398      | 2.526 | 2.443 | ns   |

| Input delay from pin to input register                                | Pad to I/O<br>input register     | 8                        | 0             | 1.313       | 1.208 | 2.205       | 2.406      | 2.563 | 2.450 | ns   |

| Delay from output<br>register to output pin                           | I/O output<br>register to<br>pad | 2                        | 0             | 0.461       | 0.421 | 0.789       | 0.869      | 0.933 | 0.884 | ns   |

| Input delay from<br>dual-purpose clock pin<br>to fan-out destinations | Pad to global<br>clock network   | 12                       | 0             | 0.712       | 0.682 | 1.225       | 1.407      | 1.562 | 1.421 | ns   |

Table 1–45. IOE Programmable Delay on Row Pins for Cyclone IV GX Devices (1), (2)

#### Notes to Table 1-45:

(1) The incremental values for the settings are generally linear. For exact values of each setting, use the latest version of Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting **0** as available in the Quartus II software