### Intel - EP4CE75F23I7 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Product StatusActiveNumber of LABs/CLBs4713Number of Logic Elements/Cells5408Total RAM Bits2810880Number of I/O92Number of Gates-Voltage - Supply1.5V ~ 1.25VMounting TypeSurface MountOperating Temperature484-BGASupplier Device Package844-FBGA (23x23)Purchase URLhttps://www.exefl.com/product-detail/intel/package1 | Details                        |                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------|

| Number of Logic Elements/Cells75408Total RAM Bits2810880Number of I/O292Number of Gates-Voltage - Supply1.15V ~ 1.25VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case484-BGASupplier Device Package484-FBGA (23x23)                                                                        | Product Status                 | Active                                                  |

| Total RAM Bits2810880Number of I/O292Number of Gates-Voltage - Supply1.15V ~ 1.25VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case484-BGASupplier Device Package484-FBGA (23x23)                                                                                                           | Number of LABs/CLBs            | 4713                                                    |

| Number of I/O292Number of Gates-Voltage - Supply1.15V ~ 1.25VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case484-BGASupplier Device Package484-FBGA (23x23)                                                                                                                                | Number of Logic Elements/Cells | 75408                                                   |

| Number of Gates-Voltage - Supply1.15V ~ 1.25VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case484-BGASupplier Device Package484-FBGA (23x23)                                                                                                                                                | Total RAM Bits                 | 2810880                                                 |

| Voltage - Supply1.15V ~ 1.25VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case484-BGASupplier Device Package484-FBGA (23x23)                                                                                                                                                                | Number of I/O                  | 292                                                     |

| Mounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case484-BGASupplier Device Package484-FBGA (23x23)                                                                                                                                                                                             | Number of Gates                | -                                                       |

| Operating Temperature-40°C ~ 100°C (TJ)Package / Case484-BGASupplier Device Package484-FBGA (23x23)                                                                                                                                                                                                                       | Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Package / Case     484-BGA       Supplier Device Package     484-FBGA (23x23)                                                                                                                                                                                                                                             | Mounting Type                  | Surface Mount                                           |

| Supplier Device Package     484-FBGA (23x23)                                                                                                                                                                                                                                                                              | Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

|                                                                                                                                                                                                                                                                                                                           | Package / Case                 | 484-BGA                                                 |

| Purchase URL https://www.e-xfl.com/product-detail/intel/ep4ce75f23i7                                                                                                                                                                                                                                                      | Supplier Device Package        | 484-FBGA (23x23)                                        |

|                                                                                                                                                                                                                                                                                                                           | Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce75f23i7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section I. Device Core**

This section provides a complete overview of all features relating to the Cyclone<sup>®</sup> IV device family, which is the most architecturally advanced, high-performance, low-power FPGA in the marketplace. This section includes the following chapters:

- Chapter 1, Cyclone IV FPGA Device Family Overview

- Chapter 2, Logic Elements and Logic Array Blocks in Cyclone IV Devices

- Chapter 3, Memory Blocks in Cyclone IV Devices

- Chapter 4, Embedded Multipliers in Cyclone IV Devices

- Chapter 5, Clock Networks and PLLs in Cyclone IV Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information about when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

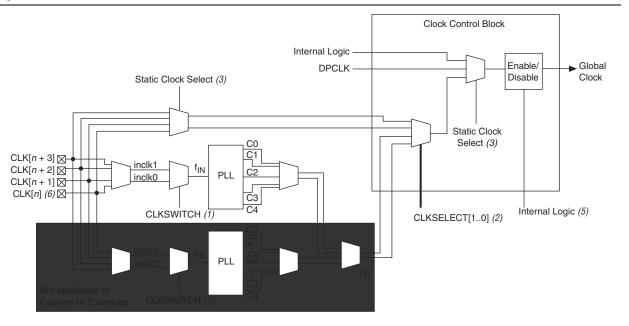

Figure 5–1 shows the clock control block.

### Figure 5–1. Clock Control Block

#### Notes to Figure 5-1:

- (1) The clkswitch signal can either be set through the configuration file or dynamically set when using the manual PLL switchover feature. The output of the multiplexer is the input clock  $(f_{IN})$  for the PLL.

- (2) The clkselect[1..0] signals are fed by internal logic and are used to dynamically select the clock source for the GCLK when the device is in user mode.

- (3) The static clock select signals are set in the configuration file. Therefore, dynamic control when the device is in user mode is not feasible.

- (4) Two out of four PLL clock outputs are selected from adjacent PLLs to drive into the clock control block.

- (5) You can use internal logic to enable or disable the GCLK in user mode.

- (6) CLK [12] is not available on the left side of Cyclone IV E devices.

Each PLL generates five clock outputs through the c[4..0] counters. Two of these clocks can drive the GCLK through a clock control block, as shown in Figure 5–1.

For more information about how to use the clock control block in the Quartus II software, refer to the *ALTCLKCTRL Megafunction User Guide*.

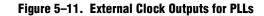

Figure 5–11 shows the external clock outputs for PLLs.

### Notes to Figure 5-11:

- (1) These external clock enable signals are available only when using the ALTCLKCTRL megafunction.

- (2) PLL#\_CLKOUTp and PLL#\_CLKOUTn pins are dual-purpose I/O pins that you can use as one single-ended clock output or one differential clock output. When using both pins as single-ended I/Os, one of them can be the clock output while the other pin is configured as a regular user I/O.

Each pin of a differential output pair is 180° out of phase. The Quartus II software places the NOT gate in your design into the I/O element to implement 180° phase with respect to the other pin in the pair. The clock output pin pairs support the same I/O standards as standard output pins.

**To** determine which I/O standards are supported by the PLL clock input and output pins, refer to the *Cyclone IV Device I/O Features* chapter.

Cyclone IV PLLs can drive out to any regular I/O pin through the GCLK. You can also use the external clock output pins as GPIO pins if external PLL clocking is not required.

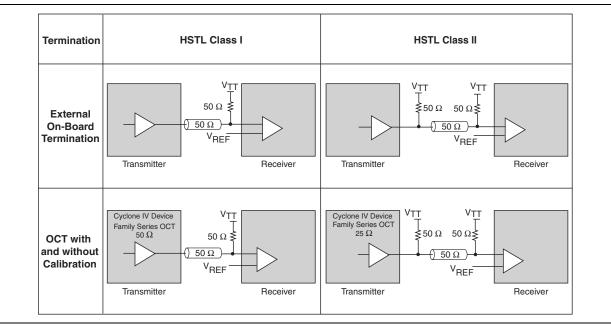

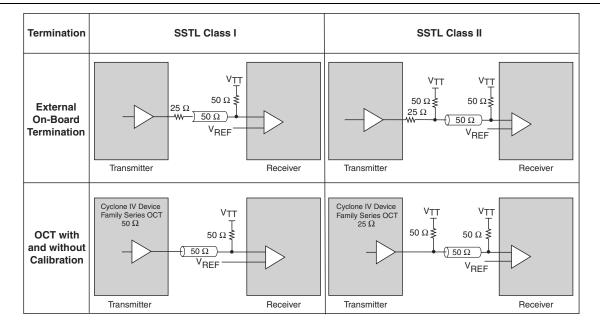

## **Voltage-Referenced I/O Standard Termination**

Voltage-referenced I/O standards require an input reference voltage ( $V_{REF}$ ) and a termination voltage ( $V_{TT}$ ). The reference voltage of the receiving device tracks the termination voltage of the transmitting device, as shown in Figure 6–5 and Figure 6–6.

Figure 6–5. Cyclone IV Devices HSTL I/O Standard Termination

Figure 6–6. Cyclone IV Devices SSTL I/O Standard Termination

### **External Memory Interfacing**

Cyclone IV devices support I/O standards required to interface with a broad range of external memory interfaces, such as DDR SDRAM, DDR2 SDRAM, and QDR II SRAM.

For more information about Cyclone IV devices external memory interface support, refer to the *External Memory Interfaces in Cyclone IV Devices* chapter.

## **Pad Placement and DC Guidelines**

You can use the Quartus II software to validate your pad and pin placement.

### **Pad Placement**

Altera recommends that you create a Quartus II design, enter your device I/O assignments and compile your design to validate your pin placement. The Quartus II software checks your pin connections with respect to the I/O assignment and placement rules to ensure proper device operation. These rules depend on device density, package, I/O assignments, voltage assignments and other factors that are not fully described in this chapter.

For more information about how the Quartus II software checks I/O restrictions, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

### **DC Guidelines**

For the Quartus II software to automatically check for illegally placed pads according to the DC guidelines, set the DC current sink or source value to **Electromigration Current** assignment on each of the output pins that are connected to the external resistive load.

The programmable current strength setting has an impact on the amount of DC current that an output pin can source or sink. Determine if the current strength setting is sufficient for the external resistive load condition on the output pin.

## **Clock Pins Functionality**

Cyclone IV clock pins have multiple purposes, as per listed:

- CLK pins—Input support for single-ended and voltage-referenced standards. For I/O standard support, refer to Table 6–3 on page 6–11.

- DIFFCLK pins—Input support for differential standards. For I/O standard support, refer to Table 6–3 on page 6–11. When used as DIFFCLK pins, DC or AC coupling can be used depending on the interface requirements and external termination is required. For more information, refer to "High-Speed I/O Standards Support" on page 6–28.

- REFCLK pins—Input support for high speed differential reference clocks used by the transceivers in Cyclone IV GX devices. For I/O support, coupling, and termination requirements, refer to Table 6–10 on page 6–29.

## **LVPECL I/O Support in Cyclone IV Devices**

The LVPECL I/O standard is a differential interface standard that requires a 2.5-V  $V_{CCIO}$ . This standard is used in applications involving video graphics, telecommunications, data communications, and clock distribution. Cyclone IV devices support the LVPECL input standard at the dedicated clock input pins only. The LVPECL receiver requires an external 100- $\Omega$  termination resistor between the two signals at the input buffer.

For the LVPECL I/O standard electrical specification, refer to the Cyclone IV Device Datasheet chapter.

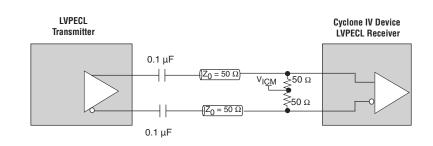

AC coupling is required when the LVPECL common mode voltage of the output buffer is higher than the Cyclone IV devices LVPECL input common mode voltage.

Figure 6–18 shows the AC-coupled termination scheme. The  $50-\Omega$  resistors used at the receiver are external to the device. DC-coupled LVPECL is supported if the LVPECL output common mode voltage is in the Cyclone IV devices LVPECL input buffer specification (refer to Figure 6–19).

### Figure 6–18. LVPECL AC-Coupled Termination (1)

### Note to Figure 6–18:

(1) The LVPECL AC-coupled termination is applicable only when an Altera FPGA transmitter is used.

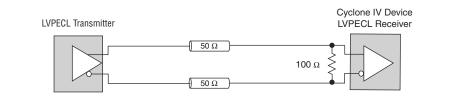

Figure 6–19 shows the LVPECL DC-coupled termination.

### Figure 6–19. LVPECL DC-Coupled Termination (1)

### Note to Figure 6–19:

(1) The LVPECL DC-coupled termination is applicable only when an Altera FPGA transmitter is used.

JTAG instructions have precedence over any other configuration modes. Therefore, JTAG configuration can take place without waiting for other configuration modes to complete. For example, if you attempt JTAG configuration in Cyclone IV devices during PS configuration, PS configuration terminates and JTAG configuration begins. If the MSEL pins are set to AS mode, the Cyclone IV device does not output a DCLK signal when JTAG configuration takes place.

The four required pins for a device operating in JTAG mode are TDI, TDO, TMS, and TCK. All the JTAG input pins are powered by the  $V_{CCIO}$  pin and support the LVTTL I/O standard only. All user I/O pins are tri-stated during JTAG configuration. Table 8-14 explains the function of each JTAG pin.

**Pin Name Pin Type** Description Serial input pin for instructions as well as test and programming data. Data shifts in on the Test data rising edge of TCK. If the JTAG interface is not required on the board, the JTAG circuitry is TDI disabled by connecting this pin to  $V_{CC}$ . TDI pin has weak internal pull-up resistors (typically 25 input kΩ). Serial data output pin for instructions as well as test and programming data. Data shifts out on Test data the falling edge of TCK. The pin is tri-stated if data is not being shifted out of the device. If the TDO output JTAG interface is not required on the board, the JTAG circuitry is disabled by leaving this pin unconnected. Input pin that provides the control signal to determine the transitions of the TAP controller state machine. Transitions in the state machine occur on the rising edge of TCK. Therefore, Test mode TMS must be set up before the rising edge of TCK. TMS is evaluated on the rising edge of TCK. TMS select If the JTAG interface is not required on the board, the JTAG circuitry is disabled by connecting this pin to  $V_{CC}$ . TMS pin has weak internal pull-up resistors (typically 25 k $\Omega$ ). The clock input to the BST circuitry. Some operations occur at the rising edge, while others Test clock occur at the falling edge. If the JTAG interface is not required on the board, the JTAG circuitry TCK input

Table 8–14. Dedicated JTAG Pins

You can download data to the device through the USB-Blaster, MasterBlaster, ByteBlaster II, or ByteBlasterMV download cable, or the EthernetBlaster communications cable during JTAG configuration. Configuring devices with a cable is similar to programming devices in-system. Figure 8-23 and Figure 8-24 show the JTAG configuration of a single Cyclone IV device.

is disabled by connecting this pin to GND. The TCK pin has an internal weak pull-down resistor.

### ACTIVE\_DISENGAGE

The ACTIVE\_DISENGAGE instruction places the active configuration controller (AS and AP) into an idle state prior to JTAG programming. The two purposes of placing the active controller in an idle state are:

- To ensure that it is not trying to configure the device during JTAG programming

- To allow the controllers to properly recognize a successful JTAG programming that results in the device reaching user mode

The ACTIVE\_DISENGAGE instruction is required before JTAG programming regardless of the current state of the Cyclone IV device if the MSEL pins are set to an AS or AP configuration scheme. If the ACTIVE\_DISENGAGE instruction is issued during a passive configuration scheme (PS or FPP), it has no effect on the Cyclone IV device. Similarly, the CONFIG\_IO instruction is issued after an ACTIVE\_DISENGAGE instruction, but is no longer required to properly halt configuration. Table 8–17 lists the required, recommended, and optional instructions for each configuration mode. The ordering of the required instructions is a hard requirement and must be met to ensure functionality.

|                                     | Configuration Scheme and Current State of the Cyclone IV Device |     |    |    |           |     |    |    |          |     |    |    |

|-------------------------------------|-----------------------------------------------------------------|-----|----|----|-----------|-----|----|----|----------|-----|----|----|

| JTAG Instruction                    | Prior to User Mode (Interrupting<br>Configuration)              |     |    |    | User Mode |     |    |    | Power Up |     |    |    |

|                                     | PS                                                              | FPP | AS | AP | PS        | FPP | AS | AP | PS       | FPP | AS | AP |

| ACTIVE_DISENGAGE                    | 0                                                               | 0   | R  | R  | 0         | 0   | 0  | R  | 0        | 0   | R  | R  |

| CONFIG_IO                           | Rc                                                              | Rc  | 0  | 0  | 0         | 0   | 0  | 0  | NA       | NA  | NA | NA |

| Other JTAG instructions             | 0                                                               | 0   | 0  | 0  | 0         | 0   | 0  | 0  | 0        | 0   | 0  | 0  |

| JTAG_PROGRAM                        | R                                                               | R   | R  | R  | R         | R   | R  | R  | R        | R   | R  | R  |

| CHECK_STATUS                        | Rc                                                              | Rc  | Rc | Rc | Rc        | Rc  | Rc | Rc | Rc       | Rc  | Rc | Rc |

| JTAG_STARTUP                        | R                                                               | R   | R  | R  | R         | R   | R  | R  | R        | R   | R  | R  |

| JTAG TAP Reset/other<br>instruction | R                                                               | R   | R  | R  | R         | R   | R  | R  | R        | R   | R  | R  |

Table 8–17. JTAG Programming Instruction Flows (1)

### Note to Table 8-17:

(1) "R" indicates that the instruction must be executed before the next instruction, "O" indicates the optional instruction, "Rc" indicates the recommended instruction, and "NA" indicates that the instruction is not allowed in this mode.

In the AS or AP configuration scheme, the ACTIVE\_DISENGAGE instruction puts the active configuration controller into idle state. If a successful JTAG programming is executed, the active controller is automatically re-engaged after user mode is reached through JTAG programming. This causes the active controller to transition to their respective user mode states.

If JTAG programming fails to get the Cyclone IV device to enter user mode and re-engage active programming, there are available methods to achieve this:

■ In AS configuration scheme, you can re-engage the AS controller by moving the JTAG TAP controller to the reset state or by issuing the ACTIVE\_ENGAGE instruction.

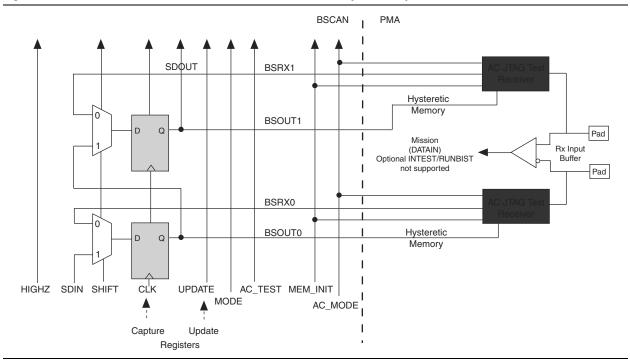

Figure 10–2 shows the Cyclone IV GX HSSI receiver BSC.

**To** For more information about Cyclone IV devices user I/O boundary-scan cells, refer to the *IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone III Devices* chapter.

## **BST Operation Control**

Table 10–1 lists the boundary-scan register length for Cyclone IV devices.

Table 10–1. Boundary-Scan Register Length for Cyclone IV Devices (Part 1 of 2)

| Device       | Boundary-Scan Register Length |

|--------------|-------------------------------|

| EP4CE6       | 603                           |

| EP4CE10      | 603                           |

| EP4CE15      | 1080                          |

| EP4CE22      | 732                           |

| EP4CE30      | 1632                          |

| EP4CE40      | 1632                          |

| EP4CE55      | 1164                          |

| EP4CE75      | 1314                          |

| EP4CE115     | 1620                          |

| EP4CGX15     | 260                           |

| EP4CGX22     | 494                           |

| EP4CGX30 (1) | 494                           |

| EP4CGX50     | 1006                          |

| Visual Cue                               | Meaning                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input. The suffix n denotes an active-low signal. For example, resetn.                 |

| Courier type                             | Indicates command line commands and anything that must be typed exactly as it appears. For example, c:\qdesigns\tutorial\chiptrip.gdf.                                                 |

|                                          | Also indicates sections of an actual file, such as a Report File, references to parts of files (for example, the AHDL keyword SUBDESIGN), and logic function names (for example, TRI). |

| 4                                        | An angled arrow instructs you to press the Enter key.                                                                                                                                  |

| 1., 2., 3., and<br>a., b., c., and so on | Numbered steps indicate a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                          |

|                                          | Bullets indicate a list of items when the sequence of the items is not important.                                                                                                      |

| LP                                       | The hand points to information that requires special attention.                                                                                                                        |

| ?                                        | The question mark directs you to a software help system with related information.                                                                                                      |

|                                          | The feet direct you to another document or website with related information.                                                                                                           |

| <b>∄</b> ,∰∄                             | The multimedia icon directs you to a related multimedia presentation.                                                                                                                  |

| CAUTION                                  | A caution calls attention to a condition or possible situation that can damage or destroy the product or your work.                                                                    |

| WARNING                                  | A warning calls attention to a condition or possible situation that can cause you injury.                                                                                              |

|                                          | The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents.                 |

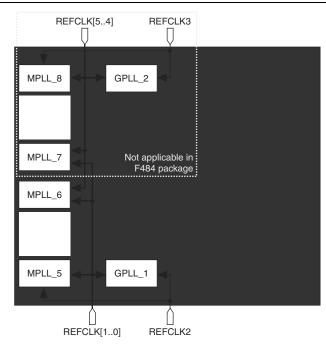

Figure 1–26. PLL Input Reference Clocks in Transceiver Operation for F484 and Larger Packages  $^{(1)}$ ,  $^{(2)}$ ,  $^{(3)}$

### Notes to Figure 1-26:

- (1) The REFCLK2 and REFCLK3 pins are dual-purpose CLKIO, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A respectively.

- (2) The REFCLK[1..0] and REFCLK[5..4] pins are dual-purpose differential REFCLK or DIFFCLK pins that reside in banks 3B and 8B respectively. These clock input pins do not have access to the clock control blocks and GCLK networks. For more details, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

- (3) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs and GPLLs may have reduced jitter performance.

The input reference clocks reside in banks 3A, 3B, 8A, and 8B have dedicated  $V_{CC\_CLKIN3A}$ ,  $V_{CC\_CLKIN3B}$ ,  $V_{CC\_CLKIN8A}$ , and  $V_{CC\_CLKIN8B}$  power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for general purpose I/Os (GPIOs). Table 1–6 lists the supported I/O standard for the REFCLK pins.

| I/O Standard                | HSSI                     |                    | Terminatio | VCC_          | CLKIN Level   | I/O Pin Type |                |                    |  |

|-----------------------------|--------------------------|--------------------|------------|---------------|---------------|--------------|----------------|--------------------|--|

|                             | Protocol                 | Coupling           | n          | Input         | Output        | Column I/O   | Row I/O        | Supported<br>Banks |  |

| LVDS                        | ALL                      | Differential       | Off-chip   | 2.5 V         | Not Supported | Yes          | No             | 3A, 3B, 8A, 8B     |  |

| LVPECL                      | ALL                      | AC (Needs          | Off-chip   | 2.5 V         | Not Supported | Yes          | No             | 3A, 3B, 8A, 8B     |  |

| 4 0 1 4 5 1                 | ALL off-chip resistor to | Off-chip           | 2.5 V      | Not Supported | Yes           | No           | 3A, 3B, 8A, 8B |                    |  |

| 1.2 V, 1.5 V,<br>3.3 V PCML | ALL                      | restore            | Off-chip   | 2.5 V         | Not Supported | Yes          | No             | 3A, 3B, 8A, 8B     |  |

|                             | ALL                      | V <sub>CM</sub> )  | Off-chip   | 2.5 V         | Not Supported | Yes          | No             | 3A, 3B, 8A, 8B     |  |

| HCSL                        | PCle                     | Differential<br>DC | Off-chip   | 2.5 V         | Not Supported | Yes          | No             | 3A, 3B, 8A, 8B     |  |

Table 1–6. REFCLK I/O Standard Support

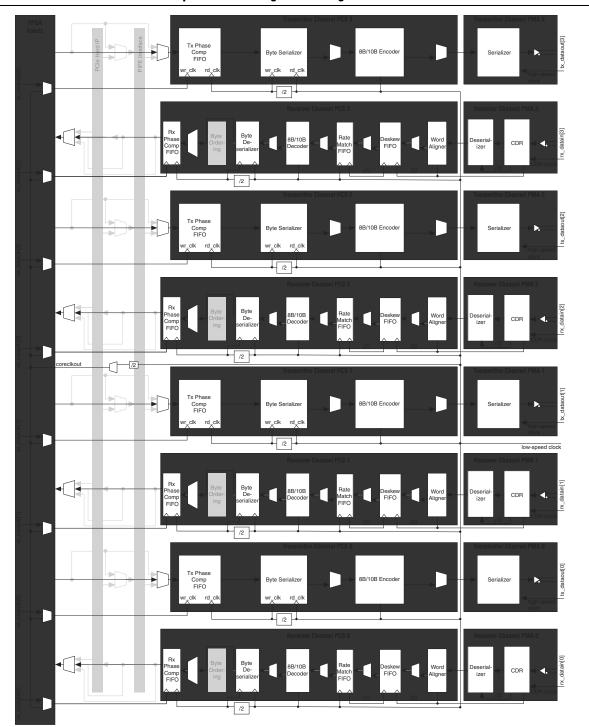

Figure 1–63 shows the transceiver channel datapath and clocking when configured in XAUI mode.

### Notes to Figure 1-63:

- (1) Channel 1 low-speed recovered clock.

- (2) Low-speed recovered clock.

- (3) High-speed recovered clock.

| Port Name           | Input/<br>Output | Clock Domain | Description                                                                              |

|---------------------|------------------|--------------|------------------------------------------------------------------------------------------|

|                     |                  |              | PIPE receiver status port.                                                               |

|                     |                  |              | <ul> <li>Signal is 3 bits wide and is encoded as follows:</li> </ul>                     |

|                     |                  |              | <ul> <li>3'b000: Received data OK</li> </ul>                                             |

|                     |                  |              | <ul> <li>3'b001: one SKP symbol added</li> </ul>                                         |

|                     | Output           | N1/A         | <ul> <li>3'b010: one SKP symbol removed</li> </ul>                                       |

| pipestatus          |                  | N/A          | <ul> <li>3'b011: Receiver detected</li> </ul>                                            |

|                     |                  |              | <ul> <li>3'b100: 8B/10B decoder error</li> </ul>                                         |

|                     |                  |              | <ul> <li>3'b101: Elastic buffer overflow</li> </ul>                                      |

|                     |                  |              | <ul> <li>3'b110: Elastic buffer underflow</li> </ul>                                     |

|                     |                  |              | <ul> <li>3'b111: Received disparity error</li> </ul>                                     |

| rx_elecidleinfersel | Input            | N/A          | Controls the electrical idle inference mechanism as specified in Table 1–17 on page 1–57 |

### Table 1–28. PIPE Interface Ports in ALTGX Megafunction for Cyclone IV GX <sup>(1)</sup> (Part 2 of 2)

### Note to Table 1-28:

(1) For equivalent signals defined in PIPE 2.00 specification, refer to Table 1–15 on page 1–54.

| Table 1-29. Multipurpose PLL, General Purpose PLL and Miscellaneous Ports in ALTGX Megafunction for |  |

|-----------------------------------------------------------------------------------------------------|--|

| Cyclone IV GX (Part 1 of 2)                                                                         |  |

| Block | Port Name  | Input/<br>Output | Clock Domain         | Description                                                                                                                                                                                                                                                                         |

|-------|------------|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |            |                  |                      | Input reference clock for the PLL (multipurpose PLL or<br>general purpose PLL) used by the transceiver instance. When<br>configured with the transmitter and receiver channel<br>configuration in Deterministic Latency mode, multiple<br>pll_inclk ports are available as follows. |

|       |            |                  |                      | Configured with PLL PFD feedback—x is the number of<br>channels selected:                                                                                                                                                                                                           |

|       | pll_inclk  | Input            | Clock signal         | pll_inclk[x-10] are input reference clocks for each transmitter in the transceiver instance                                                                                                                                                                                         |

|       |            |                  |                      | pll_inclk[x+1x] are input reference clocks for<br>receivers in the transceiver instance                                                                                                                                                                                             |

| PLL   |            |                  |                      | Configured without PLL PFD feedback:                                                                                                                                                                                                                                                |

|       |            |                  |                      | pll_inclk[0] is input reference clock for transmitters in<br>the transceiver instance                                                                                                                                                                                               |

|       |            |                  |                      | pll_inclk[1] is input reference clock for receivers in the transceiver instance                                                                                                                                                                                                     |

|       | pll_locked | Output           | Asynchronous signal  | PLL (used by the transceiver instance) lock indicator.                                                                                                                                                                                                                              |

|       |            |                  |                      | PLL (used by the transceiver instance) reset.                                                                                                                                                                                                                                       |

|       | pll_areset | Input            | Asynchronous signal  | <ul> <li>When asserted, the PLL is kept in reset state.</li> </ul>                                                                                                                                                                                                                  |

|       |            |                  | risynsmonodo orginal | <ul> <li>When deasserted, the PLL is active and locks to the input<br/>reference clock.</li> </ul>                                                                                                                                                                                  |

|       | coreclkout | Output           | Clock signal         | FPGA fabric-transceiver interface clock in bonded modes.                                                                                                                                                                                                                            |

1–91

### **Transmitter Only Channel**

This configuration contains only a transmitter channel. If you create a **Transmitter Only** instance in the ALTGX MegaWizard Plug-In Manager, use the same reset sequence shown in Figure 2–3 on page 2–7.

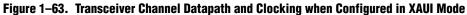

### **Receiver Only Channel—Receiver CDR in Automatic Lock Mode**

This configuration contains only a receiver channel. If you create a **Receiver Only** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 2–6.

Figure 2–6. Sample Reset Sequence of Receiver Only Channel—Receiver CDR in Automatic Lock Mode

#### Notes to Figure 2-6:

- (1) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–6, perform the following reset procedure for the receiver in CDR automatic lock mode:

- 1. After power up, wait for the busy signal to be deasserted.

- 2. Keep the rx\_digitalreset and rx\_analogreset signals asserted during this time period.

- 3. After the busy signal is deasserted, wait for another two parallel clock cycles, then deassert the rx analogreset signal.

- 4. Wait for the rx\_freqlocked signal to go high.

- 5. When rx\_freqlocked goes high (marker 3), from that point onwards, wait for at least t<sub>LTD\_Auto</sub>, then de-assert the rx\_digitalreset signal (marker 4). At this point, the receiver is ready to receive data.

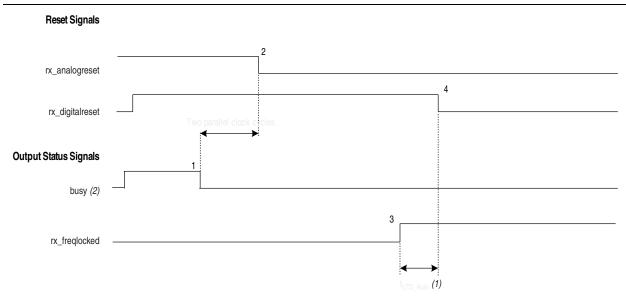

### **Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode**

This configuration contains both a transmitter and receiver channel. If you create a **Receiver and Transmitter** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in manual lock mode, use the reset sequence shown in Figure 2–9.

Figure 2–9. Sample Reset Sequence of Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode

### Notes to Figure 2-9:

- (1) For  $t_{LTR\_LTD\_Manual}$  duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) For t<sub>LTD Manual</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (3) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–9, perform the following reset procedure for the receiver in manual lock mode:

- 1. After power up, assert pll\_areset for a minimum period of 1 µs (the time between markers 1 and 2).

- Keep the tx\_digitalreset, rx\_analogreset, rx\_digitalreset, and rx\_locktorefclk signals asserted and the rx\_locktodata signal deasserted during this time period. After you deassert the pll\_areset signal, the multipurpose PLL starts locking to the transmitter input reference clock.

- 3. After the multipurpose PLL locks, as indicated by the pll\_locked signal going high (marker 3), deassert tx\_digitalreset (marker 4). For receiver operation, after deassertion of busy signal (marker 5), wait for two parallel clock cycles to deassert the rx\_analogreset signal (marker 6). After rx\_analogreset deassert, rx\_pll\_locked will assert.

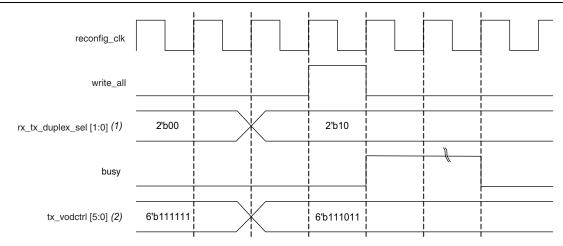

Figure 3–8 shows a write transaction waveform with the **Use the same control signal for all the channels** option disabled.

#### Notes to Figure 3-8:

- (1) In this waveform example, you want to write to only the transmitter portion of the channel.

- (2) In this waveform example, the number of channels controlled by the dynamic reconfiguration controller (the ALTGX\_RECONFIG instance) is two and that the tx\_vodctrl control port is enabled.

Simultaneous write and read transactions are not allowed.

### **Read Transaction**

The read transaction in Method 3 is identical to that in Method 2. Refer to "Read Transaction" on page 3–18.

<sup>></sup> This is the slowest method. You have to write all the PMA settings for all channels even if you may only be changing one parameter on the channel. Altera recommends using the logical\_channel\_address method for time-critical applications.

For each method, you can additionally reconfigure the PMA setting of both transmitter and receiver portion, transmitter portion only, or receiver portion only of the transceiver channel. For more information, refer to "Dynamic Reconfiguration Controller Port List" on page 3–4. You can enable the rx\_tx\_duplex\_sel port by selecting the Use 'rx\_tx\_duplex\_sel' port to enable RX only, TX only or duplex reconfiguration option on the Error checks tab of the ALTGX\_RECONFIG MegaWizard Plug-In Manager.

Figure 3–9 shows the ALTGX\_RECONFIG connection to the ALTGX instances when set in analog reconfiguration mode. For the port information, refer to the "Dynamic Reconfiguration Controller Port List" on page 3–4.

# **1. Cyclone IV Device Datasheet**

This chapter describes the electrical and switching characteristics for Cyclone<sup>®</sup> IV devices. Electrical characteristics include operating conditions and power consumption. Switching characteristics include transceiver specifications, core, and periphery performance. This chapter also describes I/O timing, including programmable I/O element (IOE) delay and programmable output buffer delay.

This chapter includes the following sections:

- "Operating Conditions" on page 1–1

- "Power Consumption" on page 1–16

- "Switching Characteristics" on page 1–16

- "I/O Timing" on page 1–37

- "Glossary" on page 1–37

## **Operating Conditions**

When Cyclone IV devices are implemented in a system, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of Cyclone IV devices, you must consider the operating requirements described in this chapter.

Cyclone IV devices are offered in commercial, industrial, extended industrial and, automotive grades. Cyclone IV E devices offer –6 (fastest), –7, –8, –8L, and –9L speed grades for commercial devices, –8L speed grades for industrial devices, and –7 speed grade for extended industrial and automotive devices. Cyclone IV GX devices offer –6 (fastest), –7, and –8 speed grades for commercial devices and –7 speed grade for industrial devices.

• For more information about the supported speed grades for respective Cyclone IV devices, refer to the *Cyclone IV FPGA Device Family Overview* chapter.

Cyclone IV E devices are offered in core voltages of 1.0 and 1.2 V. Cyclone IV E devices with a core voltage of 1.0 V have an 'L' prefix attached to the speed grade.

In this chapter, a prefix associated with the operating temperature range is attached to the speed grades; commercial with a "C" prefix, industrial with an "I" prefix, and automotive with an "A" prefix. Therefore, commercial devices are indicated as C6, C7, C8, C8L, or C9L per respective speed grade. Industrial devices are indicated as I7, I8, or I8L. Automotive devices are indicated as A7.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein exceept as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

### Internal Weak Pull-Up and Weak Pull-Down Resistor

Table 1–12 lists the weak pull-up and pull-down resistor values for Cyclone IV devices.

Table 1–12. Internal Weak Pull-Up and Weak Pull-Down Resistor Values for Cyclone IV Devices (1)

| Symbol           | Parameter                                                                                                                                                 | Conditions                                  | Min | Тур | Max | Unit |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

|                  |                                                                                                                                                           | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (2), (3) | 7   | 25  | 41  | kΩ   |

|                  | Value of the I/O pin pull-up resistor                                                                                                                     | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (2), (3) | 7   | 28  | 47  | kΩ   |

| R                | before and during configuration, as                                                                                                                       | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (2), (3) | 8   | 35  | 61  | kΩ   |

| R_ <sub>PU</sub> | well as user mode if you enable the<br>programmable pull-up resistor option<br>Value of the I/O pin pull-down resistor<br>before and during configuration | $V_{CCIO} = 1.8 \text{ V} \pm 5\%$ (2), (3) | 10  | 57  | 108 | kΩ   |

|                  |                                                                                                                                                           | $V_{CCIO} = 1.5 \text{ V} \pm 5\%$ (2), (3) | 13  | 82  | 163 | kΩ   |

|                  |                                                                                                                                                           | $V_{CCIO} = 1.2 \text{ V} \pm 5\%$ (2), (3) | 19  | 143 | 351 | kΩ   |

|                  |                                                                                                                                                           | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (4)      | 6   | 19  | 30  | kΩ   |

|                  |                                                                                                                                                           | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (4)      | 6   | 22  | 36  | kΩ   |

| $R_{PD}$         |                                                                                                                                                           | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (4)      | 6   | 25  | 43  | kΩ   |

|                  |                                                                                                                                                           | $V_{CCIO} = 1.8 \text{ V} \pm 5\%$ (4)      | 7   | 35  | 71  | kΩ   |

|                  |                                                                                                                                                           | $V_{CCIO} = 1.5 V \pm 5\%$ (4)              | 8   | 50  | 112 | kΩ   |

### Notes to Table 1-12:

- (1) All I/O pins have an option to enable weak pull-up except the configuration, test, and JTAG pins. The weak pull-down feature is only available for JTAG TCK.

- (2) Pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (3)  $R_{PU} = (V_{CCIO} V_I)/I_{R_PU}$ Minimum condition: -40°C;  $V_{CCIO} = V_{CC} + 5\%$ ,  $V_I = V_{CC} + 5\% - 50$  mV; Typical condition: 25°C;  $V_{CCIO} = V_{CC}$ ,  $V_I = 0$  V; Maximum condition: 100°C;  $V_{CCIO} = V_{CC} - 5\%$ ,  $V_I = 0$  V; in which  $V_I$  refers to the input voltage at the I/O pin.

- $\begin{array}{ll} (4) & R_{\_PD} = V_I/I_{R\_PD} \\ & \text{Minimum condition:} -40^{\circ}\text{C}; \ V_{CCIO} = V_{CC} + 5\%, \ V_I = 50 \ \text{mV}; \\ & \text{Typical condition:} \ 25^{\circ}\text{C}; \ V_{CCIO} = V_{CC}, \ V_I = V_{CC} 5\%; \\ & \text{Maximum condition:} \ 100^{\circ}\text{C}; \ V_{CCIO} = V_{CC} 5\%, \ V_I = V_{CC} 5\%; \ \text{in which } V_I \ \text{refers to the input voltage at the I/O pin.} \end{array}$

### Hot-Socketing

Table 1–13 lists the hot-socketing specifications for Cyclone IV devices.

Table 1–13. Hot-Socketing Specifications for Cyclone IV Devices

| Symbol                  | Parameter                         | Maximum         |

|-------------------------|-----------------------------------|-----------------|

| I <sub>IOPIN(DC)</sub>  | DC current per I/O pin            | 300 μA          |

| I <sub>IOPIN(AC)</sub>  | AC current per I/O pin            | 8 mA <i>(1)</i> |

| I <sub>XCVRTX(DC)</sub> | DC current per transceiver TX pin | 100 mA          |

| I <sub>XCVRRX(DC)</sub> | DC current per transceiver RX pin | 50 mA           |

Note to Table 1-13:

(1) The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns, |IIOPIN| = C dv/dt, in which C is the I/O pin capacitance and dv/dt is the slew rate.

During hot-socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF.

### **Embedded Multiplier Specifications**

Table 1–26 lists the embedded multiplier specifications for Cyclone IV devices.

### Table 1–26. Embedded Multiplier Specifications for Cyclone IV Devices

| Mode                   | <b>Resources Used</b> |     | I          | Performance | )        |     | Unit |

|------------------------|-----------------------|-----|------------|-------------|----------|-----|------|

|                        | Number of Multipliers | C6  | C7, I7, A7 | C8          | C8L, 18L | C9L | Unit |

| 9 × 9-bit multiplier   | 1                     | 340 | 300        | 260         | 240      | 175 | MHz  |

| 18 × 18-bit multiplier | 1                     | 287 | 250        | 200         | 185      | 135 | MHz  |

### **Memory Block Specifications**

Table 1–27 lists the M9K memory block specifications for Cyclone IV devices.

|           | Mode                               | <b>Resources Used</b> |               | Performance |            |     |          |     |      |

|-----------|------------------------------------|-----------------------|---------------|-------------|------------|-----|----------|-----|------|

| Memory    |                                    | LEs                   | M9K<br>Memory | C6          | C7, I7, A7 | C8  | C8L, 18L | C9L | Unit |

| M9K Block | FIFO 256 × 36                      | 47                    | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | Single-port 256 × 36               | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | Simple dual-port 256 × 36 CLK      | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

|           | True dual port 512 × 18 single CLK | 0                     | 1             | 315         | 274        | 238 | 200      | 157 | MHz  |

### **Configuration and JTAG Specifications**

Table 1–28 lists the configuration mode specifications for Cyclone IV devices.

### Table 1–28. Passive Configuration Mode Specifications for Cyclone IV Devices (1)

| Programming Mode                | V <sub>CCINT</sub> Voltage Level (V) | DCLK f <sub>max</sub> | Unit |

|---------------------------------|--------------------------------------|-----------------------|------|

| Passive Serial (PS)             | 1.0 <i>(3</i> )                      | 66                    | MHz  |

| rassive Sellai (rS)             | 1.2                                  | 133                   | MHz  |

| Fast Passive Parallel (FPP) (2) | 1.0 <i>(3)</i>                       | 66                    | MHz  |

|                                 | 1.2 (4)                              | 100                   | MHz  |

### Notes to Table 1-28:

- (1) For more information about PS and FPP configuration timing parameters, refer to the *Configuration and Remote System Upgrades in Cyclone IV Devices* chapter.

- (2) FPP configuration mode supports all Cyclone IV E devices (except for E144 package devices) and EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 only.

- (3) V<sub>CCINT</sub> = 1.0 V is only supported for Cyclone IV E 1.0 V core voltage devices.

- (4) Cyclone IV E devices support 1.2 V V<sub>CCINT</sub>. Cyclone IV E 1.2 V core voltage devices support 133 MHz DCLK f<sub>MAX</sub> for EP4CE6, EP4CE10, EP4CE15, EP4CE22, EP4CE30, and EP4CE40 only.