## Intel - EP4CE75F23I8L Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 4713                                                     |

| Number of Logic Elements/Cells | 75408                                                    |

| Total RAM Bits                 | 2810880                                                  |

| Number of I/O                  | 292                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 0.97V ~ 1.03V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce75f23i8l |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section I. Device Core**

This section provides a complete overview of all features relating to the Cyclone<sup>®</sup> IV device family, which is the most architecturally advanced, high-performance, low-power FPGA in the marketplace. This section includes the following chapters:

- Chapter 1, Cyclone IV FPGA Device Family Overview

- Chapter 2, Logic Elements and Logic Array Blocks in Cyclone IV Devices

- Chapter 3, Memory Blocks in Cyclone IV Devices

- Chapter 4, Embedded Multipliers in Cyclone IV Devices

- Chapter 5, Clock Networks and PLLs in Cyclone IV Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information about when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

# 1. Cyclone IV FPGA Device Family Overview

Altera's new Cyclone<sup>®</sup> IV FPGA device family extends the Cyclone FPGA series leadership in providing the market's lowest-cost, lowest-power FPGAs, now with a transceiver variant. Cyclone IV devices are targeted to high-volume, cost-sensitive applications, enabling system designers to meet increasing bandwidth requirements while lowering costs.

Built on an optimized low-power process, the Cyclone IV device family offers the following two variants:

- Cyclone IV E—lowest power, high functionality with the lowest cost

- Cyclone IV GX—lowest power and lowest cost FPGAs with 3.125 Gbps transceivers

Cyclone IV E devices are offered in core voltage of 1.0 V and 1.2 V.

**To** For more information, refer to the *Power Requirements for Cyclone IV Devices* chapter.

Providing power and cost savings without sacrificing performance, along with a low-cost integrated transceiver option, Cyclone IV devices are ideal for low-cost, small-form-factor applications in the wireless, wireline, broadcast, industrial, consumer, and communications industries.

# **Cyclone IV Device Family Features**

The Cyclone IV device family offers the following features:

- Low-cost, low-power FPGA fabric:

- 6K to 150K logic elements

- Up to 6.3 Mb of embedded memory

- Up to 360 18 × 18 multipliers for DSP processing intensive applications

- Protocol bridging applications for under 1.5 W total power

<sup>© 2016</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera asumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 1–2 lists Cyclone IV GX device resources.

| Resources                            | EP4CGX15 | EP4CGX22         | EP4CGX30 | EP4CGX30<br>(2)   | EP4CGX50          | EP4CGX75          | EP4CGX110         | EP4CGX150     |

|--------------------------------------|----------|------------------|----------|-------------------|-------------------|-------------------|-------------------|---------------|

| Logic elements (LEs)                 | 14,400   | 21,280           | 29,440   | 29,440            | 49,888            | 73,920            | 109,424           | 149,760       |

| Embedded memory (Kbits)              | 540      | 756              | 1,080    | 1,080             | 2,502             | 4,158             | 5,490             | 6,480         |

| Embedded 18 × 18 multipliers         | 0        | 40               | 80       | 80                | 140               | 198               | 280               | 360           |

| General purpose PLLs                 | 1        | 2                | 2        | 4 (4)             | 4 (4)             | 4 (4)             | 4 (4)             | 4 <i>(4)</i>  |

| Multipurpose PLLs                    | 2 (5)    | 2 <sup>(5)</sup> | 2 (5)    | 2 <sup>(5)</sup>  | 4 (5)             | 4 (5)             | 4 (5)             | 4 (5)         |

| Global clock networks                | 20       | 20               | 20       | 30                | 30                | 30                | 30                | 30            |

| High-speed transceivers (6)          | 2        | 4                | 4        | 4                 | 8                 | 8                 | 8                 | 8             |

| Transceiver maximum data rate (Gbps) | 2.5      | 2.5              | 2.5      | 3.125             | 3.125             | 3.125             | 3.125             | 3.125         |

| PCIe (PIPE) hard IP blocks           | 1        | 1                | 1        | 1                 | 1                 | 1                 | 1                 | 1             |

| User I/O banks                       | g (7)    | g (7)            | g (7)    | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <i>(8)</i> |

| Maximum user I/O <sup>(9)</sup>      | 72       | 150              | 150      | 290               | 310               | 310               | 475               | 475           |

Table 1–2. Resources for the Cyclone IV GX Device Family

Notes to Table 1-2:

(1) Applicable for the F169 and F324 packages.

(2) Applicable for the F484 package.

(3) Only two multipurpose PLLs for F484 package.

(4) Two of the general purpose PLLs are able to support transceiver clocking. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(5) You can use the multipurpose PLLs for general purpose clocking when they are not used to clock the transceivers. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(6) If PCIe ×1, you can use the remaining transceivers in a quad for other protocols at the same or different data rates.

(7) Including one configuration I/O bank and two dedicated clock input I/O banks for HSSI reference clock input.

(8) Including one configuration I/O bank and four dedicated clock input I/O banks for HSSI reference clock input.

(9) The user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins are not included in the pin count.

| GCLK Network Clock              |              |   |              |              |              |              |              |              |              |              |              |              |              | GC           | LK N         | etwo         | rks          |              |              |              |              |              |              |              |              |              |              |              |              |              |

|---------------------------------|--------------|---|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Sources                         | 0            | 1 | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           | 20           | 21           | 22           | 23           | 24           | 25           | 26           | 27           | 28           | 29           |

| CLKIO4/DIFFCLK_2n               | —            | — | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | $\checkmark$ |              | —            | —            | _            | —            | —            | _            |              |              | —            |              |              |              |

| CLKIO5/DIFFCLK_2p               | —            | _ | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | —            | —            | $\checkmark$ | —            |              |              | —            | —            |              | —            | —            | —            | —            |              | —            |

| CLKIO6/DIFFCLK_3n               | —            |   | —            | —            | —            | —            | —            | —            | —            |              | —            | —            | —            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              |              | _            | _            |              | —            | _            |              |              |              |              | —            | —            |

| CLKIO7/DIFFCLK_3p               | —            |   | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | ~            | —            |              | $\checkmark$ | —            | $\checkmark$ |              |              | —            |              | —            | —            |              |              |              |              | —            | —            |

| CLKIO8/DIFFCLK_5n               | _            | _ | —            |              | —            |              | —            | —            |              |              | —            |              | —            | —            |              |              | —            |              | $\checkmark$ | _            | $\checkmark$ |              | $\checkmark$ | _            |              |              |              |              | —            | —            |

| CLKIO9/DIFFCLK_5p               | —            | _ | —            | —            | —            | —            | —            | —            | —            |              | —            | —            | —            | —            |              |              | —            |              |              | $\checkmark$ | $\checkmark$ |              | —            | $\checkmark$ |              |              |              |              | —            | —            |

| CLKIO10/DIFFCLK_4n/RE<br>FCLK3n |              |   | _            | _            |              | _            | _            |              | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | ~            | _            | ~            | ~            |              | _            | _            | _            | _            |              | —            |

| CLKIO11/DIFFCLK_4p/RE<br>FCLK3p | —            |   | _            | —            | _            | _            | —            | _            | _            | —            | _            | _            | —            | _            | _            | —            | —            | _            | ~            |              | _            | ~            | —            | ~            | _            | _            | —            | _            |              | —            |

| CLKIO12/DIFFCLK_7p/RE<br>FCLK2p | —            | _ | _            | _            | —            | —            | _            | —            | —            | _            | _            | —            | _            | -            | _            | —            | _            | _            | —            | _            |              | —            | _            |              | ~            | _            | ~            | —            | ~            | —            |

| CLKIO13/DIFFCLK_7n/RE<br>FCLK2n | —            |   | _            | _            |              | _            | _            |              | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | ~            | ~            | _            |              | ~            |

| CLKIO14/DIFFCLK_6p              | —            |   | —            | _            | —            |              | —            | —            |              | —            | —            |              | —            | —            |              | —            | —            |              |              | _            | _            |              | —            | _            |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | —            |

| CLKIO15/DIFFCLK_6n              | —            |   | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            |              | —            | —            |              |              |              | —            |              | —            | —            | $\checkmark$ |              |              | $\checkmark$ | —            | $\checkmark$ |

| PLL_1_C0                        | $\checkmark$ |   | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            |              | —            | —            |              | —            | —            |              | —            | —            |              |              | _            | _            |              | —            | _            | $\checkmark$ |              |              | $\checkmark$ | —            | $\checkmark$ |

| PLL_1_C1                        | _            | > | —            |              | $\checkmark$ |              | —            | —            |              |              | —            |              | —            | —            |              |              | _            |              |              | _            |              |              | _            |              | _            | ~            |              |              | $\checkmark$ | —            |

| PLL_1_C2                        | $\checkmark$ |   | $\checkmark$ | _            | —            | _            | _            | —            | —            |              | —            | —            | _            | —            |              | _            | —            |              | _            |              |              | _            | —            |              | $\checkmark$ |              | $\checkmark$ |              | —            | —            |

| PLL_1_C3                        | _            | > | —            | $\checkmark$ | —            |              | —            | —            |              |              | —            |              | —            | —            |              |              | _            |              |              | _            |              |              | _            |              | _            | ~            |              | ~            | —            | —            |

| PLL_1_C4                        | -            | — | $\checkmark$ |              | ~            | ~            | —            | _            |              |              | —            |              | —            | —            |              |              | _            |              |              | _            |              |              | _            |              |              |              | ~            |              | ~            | $\checkmark$ |

| PLL_2_C0                        | -            | _ | —            | _            | —            |              | $\checkmark$ | —            |              | ~            | —            | $\checkmark$ | —            | —            | _            |              | _            |              | ~            | _            |              | ~            | _            | <            | -            |              |              | -            |              | —            |

| PLL_2_C1                        | -            | — | —            |              | _            |              | —            | ~            |              |              | $\checkmark$ |              | —            | —            |              |              | _            |              |              | ~            |              |              | ~            |              |              |              |              |              | —            | —            |

| PLL_2_C2                        | —            | — | —            | _            | —            | _            | $\checkmark$ | —            | $\checkmark$ | —            | —            | _            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | _            | —            | —            | —            | —            | _            | —            | _            | —            |

| PLL_2_C3                        |              | _ | _            | _            |              |              |              | $\checkmark$ |              | $\checkmark$ | _            | _            |              | _            |              | —            |              |              | —            | $\checkmark$ |              | $\checkmark$ |              |              | —            |              |              | —            | —            | —            |

| PLL_2_C4                        | —            | _ | —            | _            | —            | _            | —            | —            | $\checkmark$ | _            | $\checkmark$ | $\checkmark$ | —            | —            | —            | _            | —            |              | _            | —            | $\checkmark$ | _            | $\checkmark$ | $\checkmark$ | —            |              | _            | —            |              | —            |

## Table 5–2. GCLK Network Connections for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices <sup>(1), (2)</sup> (Part 1 of 4)

October 2012 Altera Corporation

## Table 5–2. GCLK Network Connections for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices <sup>(1), (2)</sup> (Part 4 of 4)

| GCLK Network Clock |   |   |   |   |   |   |   |   |   |   |    |    |    | GC | LK N | etwo | rks |    |    |              |    |    |    |    |    |    |    |    |    |    |

|--------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|------|------|-----|----|----|--------------|----|----|----|----|----|----|----|----|----|----|

| Sources            | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15   | 16  | 17 | 18 | 19           | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| DPCLK17            | — | — | — |   | — | — | — | — | — |   | —  | —  | —  | —  | _    |      | —   |    | —  | $\checkmark$ | —  | —  | —  | —  | —  | —  |    | —  |    | —  |

#### Notes to Table 5-2:

(1) EP4CGX30 information in this table refers to only EP4CGX30 device in F484 package.

(2) PLL\_1, PLL\_2, PLL\_3, and PLL\_4 are general purpose PLLs while PLL\_5, PLL\_6, PLL\_7, and PLL\_8 are multipurpose PLLs.

(3) PLL\_7 and PLL\_8 are not available in EP4CXGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

| GCLK Network Clock              |              |              |              |              | -            |              |              |              | GC           | LK N         | etwo         | rks          |              |    |              |    |    |              |              |    |

|---------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----|--------------|----|----|--------------|--------------|----|

| Sources                         | 0            | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13 | 14           | 15 | 16 | 17           | 18           | 19 |

| CLK1                            | —            | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —  | —            | —  | —  | —            | —            | —  |

| CLK2/DIFFCLK_1p                 | —            | $\checkmark$ | —            | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | —  | —            | —  | —  | —            | _            | —  |

| CLK3/DIFFCLK_1n                 | $\checkmark$ |              | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | _            | —            |              | _  |              | —  | _  |              |              | —  |

| CLK4/DIFFCLK_2p                 | —            |              | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —  | —            | —  | —  | —            | _            | —  |

| CLK5/DIFFCLK_2n                 | —            |              | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            | _            | —  | _            | —  | —  | _            |              | —  |

| CLK6/DIFFCLK_3p                 | —            |              | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | $\checkmark$ | _            | —            |              | _  |              | —  | _  |              |              | —  |

| CLK7/DIFFCLK_3n                 | —            |              | —            | —            | —            | $\checkmark$ | —            | —            | $\checkmark$ | —            | —            | —            | —            | —  | —            | —  | —  | —            | _            | —  |

| CLK8/DIFFCLK_5n (2)             | —            |              | —            | _            | _            | —            | —            | —            | —            | _            | $\checkmark$ | —            | $\checkmark$ |    | $\checkmark$ | —  |    | _            |              | —  |

| CLK9/DIFFCLK_5p (2)             | —            |              | —            | _            | _            | —            | —            | —            | —            | _            |              | $\checkmark$ | $\checkmark$ |    | _            | —  |    | _            |              | —  |

| CLK10/DIFFCLK_4n (2)            | _            | _            | _            | _            | _            | _            | —            |              | _            | _            |              | ~            | _            | ~  | ~            | _  |    | _            |              |    |

| CLK11/DIFFCLK_4p (2)            | —            | _            | _            | _            | _            | —            | —            | —            | _            | _            | ~            | _            | —            | ~  | —            | —  | _  | —            |              |    |

| CLK12/DIFFCLK_7n<br><i>(</i> 2) | —            | —            | _            | _            | _            | —            | —            | —            | _            | _            | _            | _            | —            | _  | —            | ~  | _  | ~            |              | ~  |

| CLK13/DIFFCLK_7p<br>(2)         | _            | —            | —            | —            | —            | _            | _            | —            | —            | —            | _            | —            | —            | _  | —            | _  | ~  | $\checkmark$ | _            |    |

| CLK14/DIFFCLK_6n<br><i>(2)</i>  | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _  | _            | _  | ~  | _            | $\checkmark$ | ~  |

## Table 5-3. GCLK Network Connections for Cyclone IV E Devices (1) (Part 1 of 3)

## **Designing with LVDS**

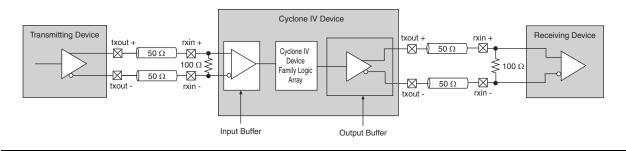

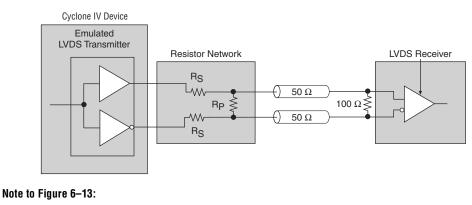

Cyclone IV I/O banks support the LVDS I/O standard. The Cyclone IV GX right I/O banks support true LVDS transmitters while the Cyclone IV E left and right I/O banks support true LVDS transmitters. On the top and bottom I/O banks, the emulated LVDS transmitters are supported using two single-ended output buffers with external resistors. One of the single-ended output buffers is programmed to have opposite polarity. The LVDS receiver requires an external 100- $\Omega$  termination resistor between the two signals at the input buffer.

Figure 6–12 shows a point-to-point LVDS interface using Cyclone IV devices true LVDS output and input buffers.

Figure 6–12. Cyclone IV Devices LVDS Interface with True Output Buffer on the Right I/O Banks

Figure 6–13 shows a point-to-point LVDS interface with Cyclone IV devices LVDS using two single-ended output buffers and external resistors.

Figure 6–13. LVDS Interface with External Resistor Network on the Top and Bottom I/O Banks (1)

# (1) $R_{\rm S} = 120 \ \Omega$ . $R_{\rm P} = 170 \ \Omega$ .

## **BLVDS I/O Standard Support in Cyclone IV Devices**

The BLVDS I/O standard is a high-speed differential data transmission technology that extends the benefits of standard point-to-point LVDS to multipoint configuration that supports bidirectional half-duplex communication. BLVDS differs from standard LVDS by providing a higher drive to achieve similar signal swings at the receiver while loaded with two terminations at both ends of the bus.

# 7. External Memory Interfaces in Cyclone IV Devices

This chapter describes the memory interface pin support and the external memory interface features of Cyclone<sup>®</sup> IV devices.

In addition to an abundant supply of on-chip memory, Cyclone IV devices can easily interface with a broad range of external memory devices, including DDR2 SDRAM, DDR SDRAM, and QDR II SRAM. External memory devices are an important system component of a wide range of image processing, storage, communications, and general embedded applications.

Altera recommends that you construct all DDR2 or DDR SDRAM external memory interfaces using the Altera<sup>®</sup> ALTMEMPHY megafunction. You can implement the controller function using the Altera DDR2 or DDR SDRAM memory controllers, third-party controllers, or a custom controller for unique application needs. Cyclone IV devices support QDR II interfaces electrically, but Altera does not supply controller or physical layer (PHY) megafunctions for QDR II interfaces.

This chapter includes the following sections:

- "Cyclone IV Devices Memory Interfaces Pin Support" on page 7–2

- "Cyclone IV Devices Memory Interfaces Features" on page 7–12

- For more information about supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to the *External Memory Interface Handbook*.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

|               | Device    | Data Size (bits)          |

|---------------|-----------|---------------------------|

|               | EP4CGX15  | 3,805,568                 |

|               | EP4CGX22  | 7,600,040                 |

|               | EP4CGX30  | 7,600,040                 |

| Cyclone IV GX |           | 22,010,888 <sup>(1)</sup> |

|               | EP4CGX50  | 22,010,888                |

|               | EP4CGX75  | 22,010,888                |

|               | EP4CGX110 | 39,425,016                |

|               | EP4CGX150 | 39,425,016                |

#### Table 8-2. Uncompressed Raw Binary File (.rbf) Sizes for Cyclone IV Devices (Part 2 of 2)

Note to Table 8-2:

(1) Only for the F484 package.

Use the data in Table 8–2 to estimate the file size before design compilation. Different configuration file formats, such as Hexadecimal (.hex) or Tabular Text File (.ttf) formats, have different file sizes. However, for any specific version of the Quartus II software, any design targeted for the same device has the same uncompressed configuration file size. If you use compression, the file size varies after each compilation, because the compression ratio depends on the design.

For more information about setting device configuration options or creating configuration files, refer to the *Software Settings* section in volume 2 of the *Configuration Handbook*.

## **Configuration and JTAG Pin I/O Requirements**

Cyclone IV devices are manufactured using the TSMC 60-nm low-k dielectric process. Although Cyclone IV devices use TSMC 2.5-V transistor technology in the I/O buffers, the devices are compatible and able to interface with 2.5, 3.0, and 3.3-V configuration voltage standards by following specific requirements.

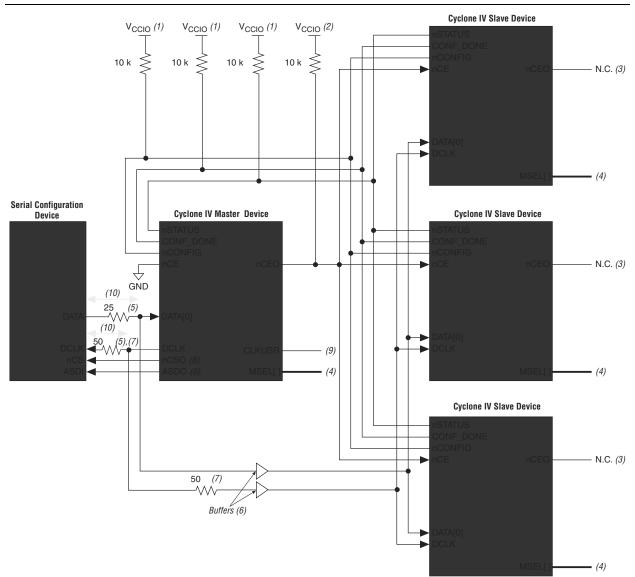

All I/O inputs must maintain a maximum AC voltage of 4.1 V. When using a serial configuration device in an AS configuration scheme, you must connect a 25- $\Omega$  series resistor for the DATA[0] pin. When cascading the Cyclone IV device family in a multi-device configuration for AS, AP, FPP, and PS configuration schemes, you must connect the repeater buffers between the master and slave devices for the DATA and DCLK pins. When using the JTAG configuration scheme in a multi-device configuration, connect 25- $\Omega$  resistors on both ends of the TDO-TDI path if the TDO output driver is a non-Cyclone IV device.

The output resistance of the repeater buffers and the TDO path for all cases must fit the maximum overshoot equation shown in Equation 8–1.

Equation 8–1. <sup>(1)</sup>

$0.8Z_O \le R_E \le 1.8Z_O$

### Note to Equation 8–1:

(1)  $Z_0$  is the transmission line impedance and  $R_E$  is the equivalent resistance of the output buffer.

### Figure 8-4. Multi-Device AS Configuration in Which Devices Receive the Same Data with Multiple .sof

#### Notes to Figure 8-4:

- (1) Connect the pull-up resistors to the V<sub>CCIO</sub> supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device in AS mode and the slave devices in PS mode. To connect the MSEL pins for the master device in AS mode and the slave devices in PS mode, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) Connect the series resistor at the near end of the serial configuration device.

- (6) Connect the repeater buffers between the master and slave devices for DATA[0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (7) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

- (8) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (9) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- (10) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration device to the junction-split on both DCLK and Data0 line is 3.5 inches.

Actual lock time depends on the transition density of the incoming data and the ppm difference between the receiver input reference clock and the upstream transmitter reference clock.

Transition from the LTD state to the LTR state occurs when either of the following conditions is met:

- Signal detection circuitry indicates the absence of valid signal levels at the receiver input buffer. This condition is valid for PCI Express (PIPE) mode only. CDR transitions are not dependent on signal detection circuitry in other modes.

- The recovered clock is not within the configured ppm frequency threshold setting with respect to CDR clocks from multipurpose PLLs.

In automatic lock mode, the switch from LTR to LTD states is indicated by the assertion of the rx\_freqlocked signal and the switch from LTD to LTR states indicated by the de-assertion of the rx\_freqlocked signal.

## **Manual Lock Mode**

State transitions are controlled manually by using rx\_locktorefclk and rx\_locktodata ports. The LTR/LTD controller sets the CDR state depending on the logic level on the rx\_locktorefclk and rx\_locktodata ports. This mode provides the flexibility to control the CDR for a reduced lock time compared to the automatic lock mode. In automatic lock mode, the LTR/LTD controller relies on the ppm detector and the phase relationship detector to set the CDR in LTR or LTD mode. The ppm detector and phase relationship detector reaction times can be too long for some applications that require faster CDR lock time.

In manual lock mode, the rx\_freqlocked signal is asserted when the CDR is in LTD state and de-asserted when CDR is in LTR state. For descriptions of rx\_locktorefclk and rx\_locktodata port controls, refer to Table 1–27 on page 1–87.

IF you do not enable the optional rx\_locktorefclk and rx\_locktodata ports, the Quartus II software automatically configures the LTR/LTD controller in automatic lock mode.

The recommended transceiver reset sequence varies depending on the CDR lock mode. For more information about the reset sequence recommendations, refer to the *Reset Control and Power Down for Cyclone IV GX Devices* chapter.

## Deserializer

The deserializer converts received serial data from the receiver input buffer to parallel 8- or 10-bit data. Serial data is assumed to be received from the LSB to the MSB. The deserializer operates with the high-speed recovered clock from the CDR with the frequency at half of the serial data rate.

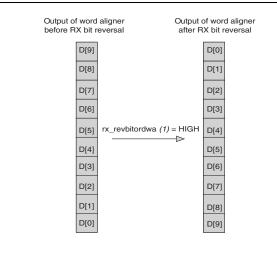

synchronization state machine mode. In bit-slip mode, you can dynamically enable the receiver bit reversal using the rx\_revbitorderwa port. When enabled, the 8-bit or 10-bit data D[7..0] or D[9..0] at the output of the word aligner is rewired to D[0..7] or D[0..9] respectively. Figure 1–20 shows the receiver bit reversal feature.

#### Note to Figure 1-20:

(1) The rx\_revbitordwa port is dynamic and is only available when the word aligner is configured in bit-slip mode.

- When using the receiver bit reversal feature to receive MSB-to-LSB transmission, reversal of the word alignment pattern is required.

- Receiver bit-slip indicator—provides the number of bits slipped in the word aligner for synchronization with rx\_bitslipboundaryselectout signal. For usage details, refer to "Receive Bit-Slip Indication" on page 1–76.

## **Deskew FIF0**

This module is only available when used for the XAUI protocol and is used to align all four channels to meet the maximum skew requirement of 40 UI (12.8 ns) as seen at the receiver of the four lanes. The deskew operation is compliant to the PCS deskew state machine diagram specified in clause 48 of the IEEE P802.3ae specification.

The deskew circuitry consists of a 16-word deep deskew FIFO in each of the four channels, and control logics in the central control unit of the transceiver block that controls the deskew FIFO write and read operations in each channel.

For details about the deskew FIFO operations for channel deskewing, refer to "XAUI Mode" on page 1–67.

## **PIPE Interface**

The PIPE interface provides a standard interface between the PCIe-compliant PHY and MAC layer as defined by the version 2.00 of the PIPE Architecture specification for Gen1 (2.5 Gbps) signaling rate. Any core or IP implementing the PHY MAC, data link, and transaction layers that supports PIPE 2.00 can be connected to the Cyclone IV GX transceiver configured in PIPE mode. Table 1–15 lists the PIPE-specific ports available from the Cyclone IV GX transceiver configured in PIPE mode and the corresponding port names in the PIPE 2.00 specification.

| Transceiver Port Name                       | PIPE 2.00 Port Name |  |

|---------------------------------------------|---------------------|--|

| tx_datain[150] <sup>(1)</sup>               | TxData[150]         |  |

| <pre>tx_ctrlenable[10] <sup>(1)</sup></pre> | TxDataK[10]         |  |

| rx_dataout[150] <sup>(1)</sup>              | RxData[150]         |  |

| <pre>rx_ctrldetect[10] (1)</pre>            | RxDataK[10]         |  |

| tx_detectrxloop                             | TxDetectRx/Loopback |  |

| tx_forceelecidle                            | TxElecIdle          |  |

| tx_forcedispcompliance                      | TxCompliance        |  |

| pipe8b10binvpolarity                        | RxPolarity          |  |

| powerdn[10] <sup>(2)</sup>                  | PowerDown[10]       |  |

| pipedatavalid                               | RxValid             |  |

| pipephydonestatus                           | PhyStatus           |  |

| pipeelecidle                                | RxElecIdle          |  |

| pipestatus                                  | RxStatus[20]        |  |

Table 1–15. Transceiver-FPGA Fabric Interface Ports in PIPE Mode

#### Notes to Table 1-15:

(1) When used with PCIe hard IP block, the byte SERDES is not used. In this case, the data ports are 8 bits wide and control identifier is 1 bit wide.

(2) Cyclone IV GX transceivers do not implement power saving measures in lower power states (P0s, P1, and P2), except when putting the transmitter buffer in electrical idle in the lower power states.

## **Receiver Detection Circuitry**

In PIPE mode, the transmitter supports receiver detection function with a built-in circuitry in the transmitter PMA. The PCIe protocol requires the transmitter to detect if a receiver is present at the far end of each lane as part of the link training and synchronization state machine sequence. This feature requires the following conditions:

- transmitter output buffer to be tri-stated

- have OCT utilization

- 125 MHz clock on the fixedclk port

The circuit works by sending a pulse on the common mode of the transmitter. If an active PCIe receiver is present at the far end, the time constant of the step voltage on the trace is higher compared to when the receiver is not present. The circuitry monitors the time constant of the step signal seen on the trace to decide if a receiver was detected.

Cyclone IV GX transceivers do not have built-in support for some PCS functions such as auto-negotiation state machine, collision-detect, and carrier-sense. If required, you must implement these functions in a user logic or external circuits.

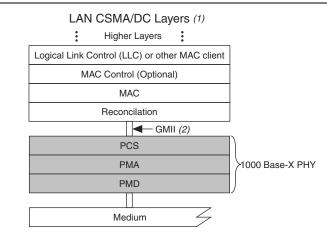

The 1000 Base-X PHY is defined by IEEE 802.3 standard as an intermediate or transition layer that interfaces various physical media with the media access control (MAC) in a GbE system. The 1000 Base-X PHY, which has a physical interface data rate of 1.25 Gbps consists of the PCS, PMA, and physical media dependent (PMD) layers. Figure 1–54 shows the 1000 Base-X PHY in LAN layers.

## Figure 1–54. 1000 Base-X PHY in a GbE OSI Reference Model

### Notes to Figure 1–54:

- (1) CSMA/CD = Carrier-Sense Multiple Access with Collision Detection

- (2) GMII = gigabit medium independent interface

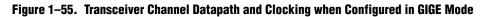

Figure 1–55 shows the transceiver channel datapath and clocking when configured in GIGE mode.

### Notes to Figure 1-55:

- (1) Low-speed recovered clock.

- (2) High-speed recovered clock.

(3) Optional rx\_recovclkout port from CDR low-speed recovered clock is available for applications such as Synchronous Ethernet.

cancellation process on the receiver channel.

The deassertion of the busy signal indicates proper completion of the offset

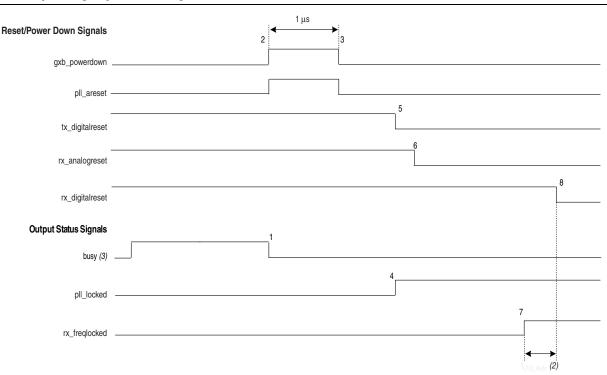

# Figure 2–13. Sample Reset Sequence of a Receiver and Transmitter Channels-Receiver CDR in Automatic Lock Mode with the Optional gxb\_powerdown Signal <sup>(1)</sup>

### Notes to Figure 2-13:

- (1) The  $gxb\_powerdown$  signal must not be asserted during the offset cancellation sequence.

- (2) For  $t_{LTD\_Auto}$  duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (3) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

# **Simulation Requirements**

The following are simulation requirements:

- The gxb\_powerdown port is optional. In simulation, if the gxb\_powerdown port is not instantiated, you must assert the tx\_digitalreset, rx\_digitalreset, and rx\_analogreset signals appropriately for correct simulation behavior.

- If the gxb\_powerdown port is instantiated, and the other reset signals are not used, you must assert the gxb\_powerdown signal for at least 1 µs for correct simulation behavior.

- You can deassert the rx\_digitalreset signal immediately after the rx\_freqlocked signal goes high to reduce the simulation run time. It is not necessary to wait for t<sub>LTD\_Auto</sub> (as suggested in the actual reset sequence).

- The busy signal is deasserted after about 20 parallel reconfig\_clk clock cycles in order to reduce simulation run time. For silicon behavior in hardware, you can follow the reset sequences described in the previous pages.

| Port Name                    | Input/<br>Output |                                            | Description                                                                                                                                      |                                                                           |

|------------------------------|------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                              |                  |                                            | nput, the controller dynamically v                                                                                                               | ransmit buffer. Depending on what<br>vrites the value to the pre-emphasis |

|                              |                  | 'logical_channel_ad<br>same control signal | al is fixed to 5 bits if you enable e<br>dress' port for Analog controls re<br>for all the channels option in the<br>al is 5 bits per channel.   |                                                                           |

|                              |                  | <pre>tx_preemp[40]</pre>                   | Corresponding ALTGX<br>instance settings                                                                                                         | Corresponding pre-<br>emphasis setting (mA)                               |

|                              |                  | 00000                                      | 0                                                                                                                                                | Disabled                                                                  |

|                              |                  | 00001                                      | 1                                                                                                                                                | 0.5                                                                       |

| tx preemp[40] (1)            | Input            | 00101                                      | 5                                                                                                                                                | 1.0                                                                       |

|                              |                  | 01001                                      | 9                                                                                                                                                | 1.5                                                                       |

|                              |                  | 01101                                      | 13                                                                                                                                               | 2.0                                                                       |

|                              |                  | 10000                                      | 16                                                                                                                                               | 2.375                                                                     |

|                              |                  | 10001                                      | 17                                                                                                                                               | 2.5                                                                       |

|                              |                  | 10010                                      | 18                                                                                                                                               | 2.625                                                                     |

|                              |                  | 10011                                      | 19                                                                                                                                               | 2.75                                                                      |

|                              |                  | 10100                                      | 20                                                                                                                                               | 2.875                                                                     |

|                              |                  | 10101                                      | 21                                                                                                                                               | 3.0                                                                       |

|                              |                  | All other values => N/                     | Ά                                                                                                                                                |                                                                           |

|                              |                  | This is an optional wr<br>the PMA.         | ite control to write an equalization                                                                                                             | n control value for the receive side of                                   |

|                              |                  | 'logical_channel_ad<br>same control signal | nal is fixed to 4 bits if you enable of<br>dress' port for Analog controls re<br>for all the channels option in the<br>al is 4 bits per channel. |                                                                           |

| rx_eqctr1[30] <sup>(1)</sup> | Input            | <pre>rx_eqctrl[30]</pre>                   | Corresponding ALTGX instance                                                                                                                     | settings                                                                  |

|                              |                  | 0001                                       | Low                                                                                                                                              |                                                                           |

|                              |                  | 0101                                       | Medium Low                                                                                                                                       |                                                                           |

|                              |                  | 0100                                       | Medium High                                                                                                                                      |                                                                           |

|                              |                  | 0111                                       | High                                                                                                                                             |                                                                           |

|                              |                  | All other values $=> N/$                   | Ά                                                                                                                                                |                                                                           |

Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 5 of 7)

| FPGA Fabric-Transceiver Channel<br>Interface Description | Receive Signal Description (Based on Cyclone IV GX Supported FPGA<br>Fabric-Transceiver Channel Interface Widths)                                                       |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                          | Two 10-bit Data (rx_dataout)                                                                                                                                            |

|                                                          | <pre>rx_dataoutfull[9:0] - rx_dataout (LSByte) and rx_dataoutfull[25:16] - rx_dataout (MSByte)</pre>                                                                    |

|                                                          | wo Receiver Sync Status Bits                                                                                                                                            |

|                                                          | <pre>rx_dataoutfull[10] - rx_syncstatus (LSB) and rx_dataoutfull[26] - rx_syncstatus (MSB)</pre>                                                                        |

| 20-bit FPGA fabric-Transceiver                           | <pre>rx_dataoutfull[11] and rx_dataoutfull[27]: 8B/10B disparity error indicator (rx_disperr)</pre>                                                                     |

| Channel Interface with PCS-PMA                           | Two Receiver Pattern Detect Bits                                                                                                                                        |

| set to 10 bits                                           | <pre>rx_dataoutfull[12] - rx_patterndetect (LSB) and rx_dataoutfull[28] - rx_patterndetect (MSB)</pre>                                                                  |

|                                                          | <pre>rx_dataoutfull[13] and rx_dataoutfull[29]: Rate Match FIFO deletion status<br/>indicator (rx_rmfifodatadeleted) in non-PCI Express (PIPE) functional modes</pre>   |

|                                                          | <pre>rx_dataoutfull[14] and rx_dataoutfull[30]: Rate Match FIFO insertion status<br/>indicator (rx_rmfifodatainserted) in non-PCI Express (PIPE) functional modes</pre> |

|                                                          | <pre>rx_dataoutfull[15] and rx_dataoutfull[31]: 8B/10B running disparity indicator (rx_runningdisp)</pre>                                                               |

## Table 3–5. rx\_dataoutfull[31..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions (Part 3 of 3)

## **Data Rate Reconfiguration Mode Using RX Local Divider**

The RX local divider resides in the RX PMA block for every channels. This is a hardware feature where a /2 divider is available in each of the receiver channel for the supported device. You can use this RX local divider to reconfigure the data rate at the receiver channel. This can be used for protocols such as SDI that has data rates in divisions of 2.

By using this RX local divider, you can support two different data rates without using additional transceiver PLLs. This dynamic reconfiguration mode is available only for the receiver and not applicable to the transmitter. This reconfiguration mode using the RX local divider (/2) is only supported and available in EP4CGX30 (F484 package), EP4CGX50, and EP4CGX75 devices.

**The Second Provided Formula Control C**

# Cyclone IV Device Handbook,

# Volume 3

101 Innovation Drive San Jose, CA 95134 www.altera.com

CYIV-5V3-2.1

| Symbol/                                                                                        | 0                                                                              |      | <b>C6</b>    |                                                      |        | C7, I7                 |                                  |      | <b>C</b> 8   |                                  |      |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|--------------|------------------------------------------------------|--------|------------------------|----------------------------------|------|--------------|----------------------------------|------|

| Description                                                                                    | Conditions                                                                     | Min  | Тур          | Max                                                  | Min    | Тур                    | Max                              | Min  | Тур          | Max                              | Unit |

| Receiver                                                                                       |                                                                                |      |              |                                                      |        |                        |                                  |      | •            |                                  |      |

| Supported I/O<br>Standards                                                                     | 1.4 V PCML,<br>1.5 V PCML,<br>2.5 V PCML,<br>LVPECL, LVDS                      |      |              |                                                      |        |                        |                                  |      |              |                                  |      |

| Data rate (F324 and smaller package) <sup>(15)</sup>                                           |                                                                                | 600  | _            | 2500                                                 | 600    | _                      | 2500                             | 600  | _            | 2500                             | Mbps |

| Data rate (F484 and<br>larger package) <sup>(15)</sup>                                         | _                                                                              | 600  | _            | 3125                                                 | 600    | _                      | 3125                             | 600  | _            | 2500                             | Mbps |

| Absolute V <sub>MAX</sub> for a receiver pin <i>(3)</i>                                        | _                                                                              | _    | _            | 1.6                                                  | _      | _                      | 1.6                              | _    | _            | 1.6                              | V    |

| Operational V <sub>MAX</sub> for a receiver pin                                                | _                                                                              | _    | _            | 1.5                                                  | _      | _                      | 1.5                              | _    | _            | 1.5                              | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                   | _                                                                              | -0.4 | _            | _                                                    | -0.4   | _                      | _                                | -0.4 | _            | _                                | V    |

| Peak-to-peak<br>differential input<br>voltage V <sub>ID</sub> (diff p-p)                       | V <sub>ICM</sub> = 0.82 V<br>setting, Data Rate<br>= 600 Mbps to<br>3.125 Gbps | 0.1  | _            | 2.7                                                  | 0.1    | _                      | 2.7                              | 0.1  | _            | 2.7                              | V    |

| V <sub>ICM</sub>                                                                               | V <sub>ICM</sub> = 0.82 V<br>setting                                           | _    | 820 ±<br>10% | _                                                    | _      | 820 ±<br>10%           | _                                | _    | 820 ±<br>10% | _                                | mV   |

| Differential on-chip                                                                           | 100– $\Omega$ setting                                                          |      | 100          | _                                                    |        | 100                    |                                  |      | 100          | _                                | Ω    |

| termination resistors                                                                          | 150– $\Omega$ setting                                                          | —    | 150          | _                                                    | _      | 150                    |                                  | —    | 150          | _                                | Ω    |

| Differential and<br>common mode<br>return loss                                                 | PIPE, Serial<br>Rapid I/O SR,<br>SATA, CPRI LV,<br>SDI, XAUI                   |      |              |                                                      |        | Compliant              | :                                |      |              |                                  | _    |

| Programmable ppm<br>detector <sup>(4)</sup>                                                    | _                                                                              |      |              |                                                      | ± 62.5 | , 100, 128<br>250, 300 |                                  |      |              |                                  | ppm  |

| Clock data recovery<br>(CDR) ppm<br>tolerance (without<br>spread-spectrum<br>clocking enabled) | _                                                                              |      |              | ±300 <i>(5)</i> ,<br>±350<br><i>(6)</i> , <i>(7)</i> | _      |                        | ±300<br>(5),<br>±350<br>(6), (7) |      | _            | ±300<br>(5),<br>±350<br>(6), (7) | ppm  |

| CDR ppm tolerance<br>(with synchronous<br>spread-spectrum<br>clocking enabled) <sup>(8)</sup>  | _                                                                              | _    | _            | 350 to –<br>5350<br>(7), (9)                         | _      | _                      | 350 to<br>5350<br>(7), (9)       | _    | _            | 350 to –<br>5350<br>(7), (9)     | ppm  |

| Run length                                                                                     |                                                                                |      | 80           | —                                                    |        | 80                     |                                  |      | 80           |                                  | UI   |

|                                                                                                | No Equalization                                                                | _    | —            | 1.5                                                  | —      | _                      | 1.5                              |      | _            | 1.5                              | dB   |

| Programmable                                                                                   | Medium Low                                                                     | —    | _            | 4.5                                                  |        | _                      | 4.5                              |      |              | 4.5                              | dB   |

| equalization                                                                                   | Medium High                                                                    |      | —            | 5.5                                                  |        |                        | 5.5                              |      |              | 5.5                              | dB   |

|                                                                                                | High                                                                           |      |              | 7                                                    |        |                        | 7                                |      |              | 7                                | dB   |

| Symbol                       | Modes  |     | C6  |     |     | C7, 17 |     |     | C8, A7 | 1   | (   | C8L, 18 | L   |     |     | Unit |      |

|------------------------------|--------|-----|-----|-----|-----|--------|-----|-----|--------|-----|-----|---------|-----|-----|-----|------|------|

| Symbol                       | WIUUES | Min | Тур | Max | Min | Тур    | Max | Min | Тур    | Max | Min | Тур     | Max | Min | Тур | Max  | Unit |

| t <sub>LOCK</sub> <i>(2)</i> |        |     |     | 1   |     |        | 1   | _   |        | 1   |     | _       | 1   |     |     | 1    | ms   |

## Table 1–32. Emulated RSDS\_E\_1R Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

Notes to Table 1-32:

(1) Emulated RSDS\_E\_1R transmitter is supported at the output pin of all I/O Banks of Cyclone IV E devices and I/O Banks 3, 4, 5, 6, 7, 8, and 9 of Cyclone IV GX devices.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                                           | Modes                                    | C6  |     |     | C7, I7 |     |       | C8, A7 |     |       | C8L, 18L |     |       | C9L |     |       |      |

|--------------------------------------------------|------------------------------------------|-----|-----|-----|--------|-----|-------|--------|-----|-------|----------|-----|-------|-----|-----|-------|------|

|                                                  |                                          | Min | Тур | Max | Min    | Тур | Max   | Min    | Тур | Max   | Min      | Тур | Max   | Min | Тур | Max   | Unit |

| f <sub>HSCLK</sub> (input<br>clock<br>frequency) | ×10                                      | 5   |     | 200 | 5      |     | 155.5 | 5      |     | 155.5 | 5        | —   | 155.5 | 5   |     | 132.5 | MHz  |

|                                                  | ×8                                       | 5   |     | 200 | 5      | —   | 155.5 | 5      | —   | 155.5 | 5        | —   | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×7                                       | 5   | _   | 200 | 5      | _   | 155.5 | 5      | _   | 155.5 | 5        | —   | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×4                                       | 5   |     | 200 | 5      | _   | 155.5 | 5      | _   | 155.5 | 5        | —   | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×2                                       | 5   |     | 200 | 5      | —   | 155.5 | 5      | —   | 155.5 | 5        | —   | 155.5 | 5   | _   | 132.5 | MHz  |

|                                                  | ×1                                       | 5   | _   | 400 | 5      | _   | 311   | 5      | _   | 311   | 5        | —   | 311   | 5   | _   | 265   | MHz  |

| Device<br>operation in<br>Mbps                   | ×10                                      | 100 |     | 400 | 100    |     | 311   | 100    |     | 311   | 100      | _   | 311   | 100 |     | 265   | Mbps |

|                                                  | ×8                                       | 80  |     | 400 | 80     | _   | 311   | 80     | —   | 311   | 80       | —   | 311   | 80  | _   | 265   | Mbps |

|                                                  | ×7                                       | 70  | _   | 400 | 70     | _   | 311   | 70     | _   | 311   | 70       | —   | 311   | 70  | _   | 265   | Mbps |

|                                                  | ×4                                       | 40  |     | 400 | 40     |     | 311   | 40     |     | 311   | 40       | _   | 311   | 40  |     | 265   | Mbps |

|                                                  | ×2                                       | 20  |     | 400 | 20     | _   | 311   | 20     | —   | 311   | 20       | —   | 311   | 20  | _   | 265   | Mbps |

|                                                  | ×1                                       | 10  |     | 400 | 10     | _   | 311   | 10     | —   | 311   | 10       | —   | 311   | 10  | _   | 265   | Mbps |

| t <sub>DUTY</sub>                                | —                                        | 45  |     | 55  | 45     |     | 55    | 45     |     | 55    | 45       | _   | 55    | 45  |     | 55    | %    |

| TCCS                                             | —                                        | —   |     | 200 | —      | _   | 200   | _      | —   | 200   | —        | —   | 200   | —   | _   | 200   | ps   |

| Output jitter<br>(peak to peak)                  | —                                        | _   | _   | 500 | _      | _   | 500   | _      | _   | 550   | _        | _   | 600   | _   | _   | 700   | ps   |

| t <sub>RISE</sub>                                | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _      | 500 | _     |        | 500 | _     | _        | 500 | _     | _   | 500 |       | ps   |

| t <sub>FALL</sub>                                | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _      | 500 | _     |        | 500 | _     | _        | 500 |       | _   | 500 | _     | ps   |

| t <sub>LOCK</sub> (3)                            | —                                        | —   | —   | 1   | —      | —   | 1     |        | —   | 1     | —        | _   | 1     | —   | —   | 1     | ms   |

Table 1–33. Mini-LVDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4)

Notes to Table 1-33:

(1) Applicable for true and emulated mini-LVDS transmitter.

(2) Cyclone IV E—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 1, 2, 5, and 6. Emulated mini-LVDS transmitter is supported at the output pin of all I/O banks.

Cyclone IV GY—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5.

Cyclone IV GX—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(3)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(4) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.