Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

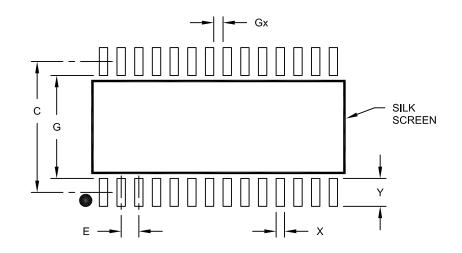

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs502-e-2n |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TADLE       | TABLE 4-19: PERIPHERAL PIN SELEC |        |        |         |         |         | JUTPUT REGISTER MAP FOR ASPIC33EPXXGS306 DEVICES |         |         |       |       |         |         |         |         |         |         |               |

|-------------|----------------------------------|--------|--------|---------|---------|---------|--------------------------------------------------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| SFR<br>Name | Addr.                            | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10                                           | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| RPOR0       | 0670                             | _      | —      | RP33R5  | RP33R4  | RP33R3  | RP33R2                                           | RP33R1  | RP33R0  | _     | _     | RP32R5  | RP32R4  | RP32R3  | RP32R2  | RP32R1  | RP32R0  | 0000          |

| RPOR1       | 0672                             | Ι      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2                                           | RP35R1  | RP35R0  | _     | —     | RP34R5  | RP34R4  | RP34R3  | RP34R2  | RP34R1  | RP34R0  | 0000          |

| RPOR2       | 0674                             | Ι      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2                                           | RP37R1  | RP37R0  | _     | —     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR3       | 0676                             | _      | _      | RP39R5  | RP39R4  | RP39R3  | RP39R2                                           | RP39R1  | RP39R0  | _     | _     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR4       | 0678                             | Ι      | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2                                           | RP41R1  | RP41R0  | _     | —     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR5       | 067A                             | Ι      | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2                                           | RP43R1  | RP43R0  | _     | —     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR6       | 067C                             | _      | —      | RP45R5  | RP45R4  | RP45R3  | RP45R2                                           | RP45R1  | RP45R0  | _     | _     | RP44R5  | RP44R4  | RP44R3  | RP44R2  | RP44R1  | RP44R0  | 0000          |

| RPOR7       | 067E                             | _      | _      | RP47R5  | RP47R4  | RP47R3  | RP47R2                                           | RP47R1  | RP47R0  | _     | _     | RP46R5  | RP46R4  | RP46R3  | RP46R2  | RP46R1  | RP46R0  | 0000          |

| RPOR8       | 0680                             | Ι      | _      | RP49R5  | RP49R4  | RP49R3  | RP49R2                                           | RP49R1  | RP49R0  | _     | —     | RP48R5  | RP48R4  | RP48R3  | RP48R2  | RP48R1  | RP48R0  | 0000          |

| RPOR9       | 0682                             | Ι      | _      | RP51R5  | RP51R4  | RP51R3  | RP51R2                                           | RP51R1  | RP51R0  | _     | —     | RP50R5  | RP50R4  | RP50R3  | RP50R2  | RP50R1  | RP50R0  | 0000          |

| RPOR10      | 0684                             | Ι      | _      | RP53R5  | RP53R4  | RP53R3  | RP53R2                                           | RP53R1  | RP53R0  | _     | —     | RP52R5  | RP52R4  | RP52R3  | RP52R2  | RP52R1  | RP52R0  | 0000          |

| RPOR11      | 0686                             | Ι      | _      | RP55R5  | RP55R4  | RP55R3  | RP55R2                                           | RP55R1  | RP55R0  | _     | —     | RP54R5  | RP54R4  | RP54R3  | RP54R2  | RP54R1  | RP54R0  | 0000          |

| RPOR12      | 0688                             | Ι      | _      | RP57R5  | RP57R4  | RP57R3  | RP57R2                                           | RP57R1  | RP57R0  | _     | —     | RP56R5  | RP56R4  | RP56R3  | RP56R2  | RP56R1  | RP56R0  | 0000          |

| RPOR13      | 068A                             | Ι      | _      | RP59R5  | RP59R4  | RP59R3  | RP59R2                                           | RP59R1  | RP59R0  | _     | —     | RP58R5  | RP58R4  | RP58R3  | RP58R2  | RP58R1  | RP58R0  | 0000          |

| RPOR14      | 068C                             | Ι      | _      | RP61R5  | RP61R4  | RP61R3  | RP61R2                                           | RP61R1  | RP61R0  | _     | —     | RP60R5  | RP60R4  | RP60R3  | RP60R2  | RP60R1  | RP60R0  | 0000          |

| RPOR15      | 068E                             | Ι      | _      | RP63R5  | RP63R4  | RP63R3  | RP63R2                                           | RP63R1  | RP63R0  | _     | —     | RP62R5  | RP62R4  | RP62R3  | RP62R2  | RP62R1  | RP62R0  | 0000          |

| RPOR16      | 0690                             | _      | -      | RP177R5 | RP177R4 | RP177R3 | RP177R2                                          | RP177R1 | RP177R0 | —     | _     | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 | 0000          |

| RPOR17      | 0692                             | _      | -      | RP179R5 | RP179R4 | RP179R3 | RP179R2                                          | RP179R1 | RP179R0 | —     | _     | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | 0000          |

| RPOR18      | 0694                             | _      | -      | RP181R5 | RP181R4 | RP181R3 | RP181R2                                          | RP181R1 | RP181R0 | _     | _     | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | 0000          |

#### TABLE 4-19: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXGS506 DEVICES

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-20: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SFR<br>Name | Addr. | Bit 15              | Bit 14     | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7                                                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|---------------------|------------|----------|----------|----------|----------|----------|----------|--------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------|

| RPINR0      | 06A0  |                     | INT1R<7:0> |          |          |          |          |          |          | _                                                            | _      | _      | _      | —      | _      |        |        | 0000          |

| RPINR1      | 06A2  | _                   | _          | _        | _        | _        | _        | _        | _        |                                                              |        |        | INT2   | R<7:0> |        |        |        | 0000          |

| RPINR2      | 06A4  |                     |            |          | T1CKF    | R<7:0>   |          |          |          | _                                                            | _      | _      | _      | _      | _      | —      | _      | 0000          |

| RPINR3      | 06A6  | T3CKR7              | T3CKR6     | T3CKR5   | T3CKR4   | T3CKR3   | T3CKR2   | T3CKR1   | T3CKR0   | T2CKR7                                                       | T2CKR6 | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 | 0000          |

| RPINR7      | 06AE  | IC2R7               | IC2R6      | IC2R5    | IC2R4    | IC2R3    | IC2R2    | IC2R1    | IC2R0    | IC1R7                                                        | IC1R6  | IC1R5  | IC1R4  | IC1R3  | IC1R2  | IC1R1  | IC1R0  | 0000          |

| RPINR8      | 06B0  | IC4R7               | IC4R6      | IC4R5    | IC4R4    | IC4R3    | IC4R2    | IC4R1    | IC4R0    | IC3R7                                                        | IC3R6  | IC3R5  | IC3R4  | IC3R3  | IC3R2  | IC3R1  | IC3R0  | 0000          |

| RPINR11     | 06B6  | B6 OCFAR<7:0>       |            |          |          |          |          |          | 0000     |                                                              |        |        |        |        |        |        |        |               |

| RPINR12     | 06B8  | FLT2R7              | FLT2R6     | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | FLT1R7                                                       | FLT1R6 | FLT1R5 | FLT1R4 | FLT1R3 | FLT1R2 | FLT1R1 | FLT1R0 | 0000          |

| RPINR13     | 06BA  | FLT4R7              | FLT4R6     | FLT4R5   | FLT4R4   | FLT4R3   | FLT4R2   | FLT4R1   | FLT4R0   | FLT3R7                                                       | FLT3R6 | FLT3R5 | FLT3R4 | FLT3R3 | FLT3R2 | FLT3R1 | FLT3R0 | 0000          |

| RPINR18     | 06C4  | U1CTSR7             | U1CTSR6    | U1CTSR5  | U1CTSR4  | U1CTSR3  | U1CTSR2  | U1CTSR1  | U1CTS0   | U1RXR7                                                       | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 | 0000          |

| RPINR19     | 06C6  | U2CTSR7             | U2CTSR6    | U2CTSR5  | U2CTSR4  | U2CTSR3  | U2CTSR2  | U2CTSR1  | U2CTSR0  | U2RXR7                                                       | U2RXR6 | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 | 0000          |

| RPINR20     | 06C8  | SCK1INR7            | SCK1INR6   | SCK1INR5 | SCK1INR4 | SCK1INR3 | SCK1INR2 | SCK1INR1 | SCK1INR0 | SDI1R7                                                       | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 | 0000          |

| RPINR21     | 06CA  | _                   | _          | _        | _        | _        | _        | _        | _        |                                                              |        |        | SS1F   | R<7:0> |        |        |        | 0000          |

| RPINR22     | 06CC  | SCK2INR7            | SCK2INR6   | SCK2INR5 | SCK2INR4 | SCK2INR3 | SCK2INR2 | SCK2INR1 | SCK2INR0 | SDI2R7                                                       | SDI2R6 | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 | 0000          |

| RPINR23     | 06CE  | _                   | _          | _        | _        | _        | _        | _        | _        |                                                              |        |        | SS2F   | R<7:0> |        |        |        | 0000          |

| RPINR37     | 06EA  | 6EA SYNCI1R<7:0> 00 |            |          |          |          |          | 0000     |          |                                                              |        |        |        |        |        |        |        |               |

| RPINR38     | 06EC  | 06EC SYNCI2R<7:0>   |            |          |          |          |          |          | 0000     |                                                              |        |        |        |        |        |        |        |               |

| RPINR42     | 06F4  | FLT6R7              | FLT6R6     | FLT6R5   | FLT6R4   | FLT6R3   | FLT6R2   | FLT6R1   | FLT6R0   | ELT6R0 FLT5R7 FLT5R6 FLT5R5 FLT5R4 FLT5R3 FLT5R2 FLT5R1 FLT5 |        |        |        |        |        | FLT5R0 | 0000   |               |

| RPINR43     | 06F6  | FLT8R7              | FLT8R6     | FLT8R5   | FLT8R4   | FLT8R3   | FLT8R2   | FLT8R1   | FLT8R0   | FLT7R7                                                       | FLT7R6 | FLT7R5 | FLT7R4 | FLT7R3 | FLT7R2 | FLT7R1 | FLT7R0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS7000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXGS50X family CPU.

The interrupt controller has the following features:

- Six processor exceptions and software traps

- · Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

- Alternate Interrupt Vector Table (AIVT) for debug support

## 7.1 Interrupt Vector Table

The dsPIC33EPXXGS50X family Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to 246 sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-2, is available only when the Boot Segment is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least 2 pages to enable the AIVT.

Note: Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXGS50X family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2

STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred

0 = Stack error trap has not occurred

bit 1

OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred

0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

## 8.5 Oscillator Control Registers

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | R/W-0  | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|--------|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | IOLOCK | LOCK | —   | CF <sup>(3)</sup> | —   | —   | OSWEN |

| bit 7   |        |      |     |                   |     |     | bit 0 |

| Legend:           | Legend:y = Value set from Configuration bits on POR |                       |                    |  |  |  |  |  |

|-------------------|-----------------------------------------------------|-----------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit | t, read as '0'     |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | <b>COSC&lt;2:0&gt;:</b> Current Oscillator Selection bits (read-only)<br>111 = Fast RC Oscillator (FRC) with Divide-by-n<br>110 = Fast RC Oscillator (FRC) with Divide-by-16                  |

|           | 101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved                                                                                                                                        |

|           | 011 = Primary Oscillator (XT, HS, EC) with PLL<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                    |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                                                                                                                       |

|           | 111 = Fast RC Oscillator (FRC) with Divide-by-n                                                                                                                                               |

|           | 110 = Fast RC Oscillator (FRC) with Divide-by-16<br>101 = Low-Power RC Oscillator (LPRC)                                                                                                      |

|           | 100 = Reserved                                                                                                                                                                                |

|           | 011 = Primary Oscillator (XT, HS, EC) with PLL                                                                                                                                                |

|           | 010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)                                                                                     |

|           | 000 = Fast RC Oscillator (FRC)                                                                                                                                                                |

| bit 7     | CLKLOCK: Clock Lock Enable bit                                                                                                                                                                |

|           | 1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and<br>PLL configurations may be modified                                                      |

|           | <ul> <li>0 = Clock and PLL selections are not locked, configurations may be modified</li> </ul>                                                                                               |

| bit 6     | IOLOCK: I/O Lock Enable bit                                                                                                                                                                   |

|           | 1 = I/O lock is active                                                                                                                                                                        |

| hit E     | 0 = I/O lock is not active                                                                                                                                                                    |

| bit 5     | <b>LOCK:</b> PLL Lock Status bit (read-only)<br>1 = Indicates that PLL is in lock or PLL start-up timer is satisfied                                                                          |

|           | 0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled                                                                                                       |

| Note 1:   | Writes to this register require an unlock sequence.                                                                                                                                           |

| 2:        | Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.                                                                                         |

|           | This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.                     |

| 3:        | This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an                                                                                |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

#### REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

bit 4-0

**PLLPRE<4:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler) 11111 = Input divided by 33

•

00001 = Input divided by 3

00000 = Input divided by 2 (default)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- **2:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0          | U-0           | U-0              | U-0              | U-0              | U-0              | U-0             | R/W-0   |

|--------------|---------------|------------------|------------------|------------------|------------------|-----------------|---------|

| _            | —             | _                | —                | —                | —                | _               | PLLDIV8 |

| bit 15       |               |                  |                  |                  |                  |                 | bit 8   |

|              |               |                  |                  |                  |                  |                 |         |

| R/W-0        | R/W-0         | R/W-1            | R/W-1            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|              |               |                  | PLLDI            | V<7:0>           |                  |                 |         |

| bit 7        |               |                  |                  |                  |                  |                 | bit 0   |

|              |               |                  |                  |                  |                  |                 |         |

| Legend:      |               |                  |                  |                  |                  |                 |         |

| R = Reada    | ble bit       | W = Writable     | bit              | U = Unimplen     | nented bit, read | d as '0'        |         |

| -n = Value a | at POR        | '1' = Bit is set |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|              |               |                  |                  |                  |                  |                 |         |

| bit 15-9     | Unimplemen    | ted: Read as '   | )'               |                  |                  |                 |         |

| bit 8-0      | PLLDIV<8:0>   | -: PLL Feedbac   | k Divisor bits ( | also denoted a   | is 'M', PLL mul  | tiplier)        |         |

|              | 111111111     | = 513            |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | 000110000=    | = 50 (default)   |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | • 000000010 = | = 4              |                  |                  |                  |                 |         |

|              | 00000010-     | <b>– –</b>       |                  |                  |                  |                 |         |

### REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

000000001 = 3 000000000 = 2

#### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| R/W-0           | U-0                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON            |                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                           | ROSEL                                                                                                                                                                                                | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15          |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       | bit 8                 |

| U-0             | U-0                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                  | U-0                   | U-0                   | U-0                   | U-0                   |

| _               | _                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                    |                       | —                     | —                     | _                     |

| bit 7           |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       | bit C                 |

| Legend:         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |

| R = Readable    | bit                                                                                                                                                                                                          | W = Writable b                                                                                                                                                                                                                                                                                                                                   | bit                                                                                                                                                                                                  | U = Unimplem          | nented bit, read      | l as '0'              |                       |

| -n = Value at F |                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                      | '0' = Bit is clea     |                       | x = Bit is unkr       | nown                  |

|                 |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |

| bit 15          | 1 = Reference                                                                                                                                                                                                | ence Oscillator<br>e oscillator outp<br>e oscillator outp                                                                                                                                                                                                                                                                                        | ut is enabled of                                                                                                                                                                                     |                       | 2)                    |                       |                       |

| bit 14          | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                    |                       |                       |                       |                       |

| bit 13          | ROSSLP: Re                                                                                                                                                                                                   | ference Oscillat                                                                                                                                                                                                                                                                                                                                 | or Run in Slee                                                                                                                                                                                       | ep bit                |                       |                       |                       |

|                 |                                                                                                                                                                                                              | e oscillator outp<br>e oscillator outp                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      |                       |                       |                       |                       |

| bit 12          | ROSEL: Refe                                                                                                                                                                                                  | erence Oscillato                                                                                                                                                                                                                                                                                                                                 | r Source Sele                                                                                                                                                                                        | ct bit                |                       |                       |                       |

|                 |                                                                                                                                                                                                              | crystal is used ock is used as                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                      |                       |                       |                       |                       |

| bit 11-8        | •                                                                                                                                                                                                            | Reference Osc                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                      |                       |                       |                       |                       |

|                 | 1110 = Refer<br>1101 = Refer<br>1100 = Refer<br>1011 = Refer<br>1010 = Refer<br>1000 = Refer<br>0111 = Refer<br>0110 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0101 = Refer<br>0011 = Refer | ence clock divic<br>ence clock divic | led by 16,384<br>led by 8,192<br>led by 4,096<br>led by 2,048<br>led by 1,024<br>led by 512<br>led by 512<br>led by 256<br>led by 128<br>led by 64<br>led by 32<br>led by 16<br>led by 8<br>led by 4 |                       |                       |                       |                       |

| bit 7-0         | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                    |                       |                       |                       |                       |

|                 | •                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

## 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control x register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 26-11 for the maximum VIH specification for each pin.

### 10.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

#### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP, as shown in Example 10-1.

## **10.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the ICN functionality of each I/O port. The CNENx registers contain the ICN interrupt enable control bits for each of the input pins. Setting any of these bits enables an ICN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source, or sink source, connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on Input Change Notification pins should always be disabled when the port pin is configured as a digital output.

#### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

## 11.2 Timer1 Control Register

| REGISTER           | 11-1: T1CO                             | N: TIMER1 C                              | ONTROL RE                 | GISTER           |                          |                    |                    |

|--------------------|----------------------------------------|------------------------------------------|---------------------------|------------------|--------------------------|--------------------|--------------------|

| R/W-0              | U-0                                    | R/W-0                                    | U-0                       | U-0              | U-0                      | U-0                | U-0                |

| TON <sup>(1)</sup> | —                                      | TSIDL                                    |                           | _                | —                        | —                  | _                  |

| bit 15             |                                        |                                          |                           |                  |                          |                    | bit 8              |

|                    |                                        |                                          |                           |                  |                          |                    |                    |

| U-0                | R/W-0                                  | R/W-0                                    | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0                |

|                    | TGATE                                  | TCKPS1                                   | TCKPS0                    |                  | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> | —                  |

| bit 7              |                                        |                                          |                           |                  |                          |                    | bit 0              |

| Legend:            |                                        |                                          |                           |                  |                          |                    |                    |

| R = Readab         | le bit                                 | W = Writable                             | bit                       | U = Unimplei     | mented bit, read         | l as '0'           |                    |

| -n = Value a       | t POR                                  | '1' = Bit is set                         |                           | '0' = Bit is cle |                          | x = Bit is unkno   | own                |

|                    |                                        |                                          |                           |                  |                          |                    |                    |

| bit 15             | TON: Timer1                            | On bit <sup>(1)</sup>                    |                           |                  |                          |                    |                    |

|                    | 1 = Starts 16-<br>0 = Stops 16-        |                                          |                           |                  |                          |                    |                    |

| bit 14             | Unimplemen                             | ted: Read as '                           | 0'                        |                  |                          |                    |                    |

| bit 13             | TSIDL: Timer                           | 1 Stop in Idle N                         | Node bit                  |                  |                          |                    |                    |

|                    |                                        | ues module op<br>s module opera          |                           |                  | dle mode                 |                    |                    |

| bit 12-7           | Unimplemen                             | ted: Read as '                           | 0'                        |                  |                          |                    |                    |

| bit 6              | TGATE: Time                            | er1 Gated Time                           | Accumulation              | n Enable bit     |                          |                    |                    |

|                    | When TCS =<br>This bit is ign          |                                          |                           |                  |                          |                    |                    |

|                    |                                        | 0:<br>ne accumulation<br>ne accumulation |                           |                  |                          |                    |                    |

| bit 5-4            | TCKPS<1:0>                             | : Timer1 Input                           | Clock Prescal             | le Select bits   |                          |                    |                    |

|                    | 11 = 1:256<br>10 = 1:64                | ·                                        |                           |                  |                          |                    |                    |

|                    | 01 = 1:8<br>00 = 1:1                   |                                          |                           |                  |                          |                    |                    |

| bit 3              | Unimplemen                             | ted: Read as '                           | 0'                        |                  |                          |                    |                    |

| bit 2              | TSYNC: Time                            | er1 External Cl                          | ock Input Synd            | chronization Se  | elect bit <sup>(1)</sup> |                    |                    |

|                    | When TCS =                             |                                          |                           |                  |                          |                    |                    |

|                    |                                        | izes external c<br>synchronize ex        |                           | tuar             |                          |                    |                    |

|                    | When TCS =                             | -                                        |                           | iput             |                          |                    |                    |

|                    | This bit is ign                        |                                          |                           |                  |                          |                    |                    |

| bit 1              | TCS: Timer1                            | Clock Source                             | Select bit <sup>(1)</sup> |                  |                          |                    |                    |

|                    | 1 = External o<br>0 = Internal c       | clock is from pi<br>lock (FP)            | n, T1CK (on th            | ne rising edge)  |                          |                    |                    |

| bit 0              | Unimplemen                             | ted: Read as '                           | 0'                        |                  |                          |                    |                    |

|                    | Vhen Timer1 is er<br>ttempts by user s |                                          |                           |                  |                          | SYNC = 1, TON      | <b>l =</b> 1), any |

## REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

#### REGISTER 15-8: SSEVTCMP: PWMx SECONDARY SPECIAL EVENT COMPARE REGISTER<sup>(1)</sup>

| R/W-0            | R/W-0 | R/W-0            | R/W-0  | R/W-0         | R/W-0          | R/W-0     | R/W-0 |

|------------------|-------|------------------|--------|---------------|----------------|-----------|-------|

|                  |       |                  | SSEVTC | /IP<12:5>     |                |           |       |

| bit 15           |       |                  |        |               |                |           | bit 8 |

|                  |       |                  |        |               |                |           |       |

| R/W-0            | R/W-0 | R/W-0            | R/W-0  | R/W-0         | U-0            | U-0       | U-0   |

|                  | S     | SEVTCMP<4:0>     |        |               | —              | —         | —     |

| bit 7            |       |                  |        |               |                |           | bit 0 |

|                  |       |                  |        |               |                |           |       |

| Legend:          |       |                  |        |               |                |           |       |

| R = Readable bit |       | W = Writable bit |        | II = Unimplen | nented hit rea | nd as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-3 SSEVTCMP<12:0>: Special Event Compare Count Value bits

bit 2-0 Unimplemented: Read as '0'

**Note 1:** One LSB = 1.04 ns (at fastest auxiliary clock rate); therefore, the minimum SEVTCMP resolution is 8.32 ns.

### **REGISTER 15-9:** CHOP: PWMx CHOP CLOCK GENERATOR REGISTER<sup>(1)</sup>

| R/W-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    |

|----------|-----|-----|-----|-----|-----|----------|----------|

| CHPCLKEN | —   | —   | —   | —   | —   | CHOPCLK6 | CHOPCLK5 |

| bit 15   |     |     |     |     |     |          | bit 8    |

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0 | U-0 |

|----------|----------|----------|----------|----------|-----|-----|-----|

| CHOPCLK4 | CHOPCLK3 | CHOPCLK2 | CHOPCLK1 | CHOPCLK0 | _   | —   | —   |

| bit 7    |          |          |          |          |     |     |     |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15CHPCLKEN: Enable Chop Clock Generator bit<br/>1 = Chop clock generator is enabled<br/>0 = Chop clock generator is disabledbit 14-10Unimplemented: Read as '0'bit 9-3CHOPCLK<6:0>: Chop Clock Divider bits<br/>Value is in 8.32 ns increments. The frequency of the chop clock signal is given by:<br/>Chop Frequency = 1/(16.64 \* (CHOP<7:3> + 1) \* Primary Master PWM Input Clock Period)bit 2-0Unimplemented: Read as '0'

**Note 1:** The chop clock generator operates with the primary PWMx clock prescaler (PCLKDIV<2:0>) in the PTCON2 register (Register 15-2).

#### REGISTER 19-5: ADCON3L: ADC CONTROL REGISTER 3 LOW

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R-0, HSC | R/W-0   | R-0, HSC |

|---------|---------|---------|---------|---------|----------|---------|----------|

| REFSEL2 | REFSEL1 | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY  | SHRSAMP | CNVRTCH  |

| bit 15  |         |         |         |         |          |         | bit 8    |

| R/W-0     | R/W-0, HSC | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|-----------|------------|-----------|-----------|-----------|-----------|-----------|-----------|

| SWLCTRG   | SWCTRG     | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2 | CNVCHSEL1 | CNVCHSEL0 |

| bit 7 bit |            |           |           |           |           |           | bit 0     |

| Legend:           | U = Unimplemented bit, read | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | HSC = Hardware Settable/C          | learable bit       |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 15-13 **REFSEL<2:0>:** ADC Reference Voltage Selection bits

| Value | VREFH | VREFL |

|-------|-------|-------|

| 000   | AVdd  | AVss  |

001-111 = Unimplemented: Do not use bit 12 SUSPEND: All ADC Cores Triggers Disable bit 1 = All new trigger events for all ADC cores are disabled 0 = All ADC cores can be triggered bit 11 SUSPCIE: Suspend All ADC Cores Common Interrupt Enable bit 1 = Common interrupt will be generated when ADC core triggers are suspended (SUSPEND bit = 1) and all previous conversions are finished (SUSPRDY bit becomes set) 0 = Common interrupt is not generated for suspend ADC cores event bit 10 SUSPRDY: All ADC Cores Suspended Flag bit 1 = All ADC cores are suspended (SUSPEND bit = 1) and have no conversions in progress 0 = ADC cores have previous conversions in progress bit 9 SHRSAMP: Shared ADC Core Sampling Direct Control bit This bit should be used with the individual channel conversion trigger controlled by the CNVRTCH bit. It connects an analog input, specified by the CNVCHSEL<5:0> bits, to the shared ADC core and allows extending the sampling time. This bit is not controlled by hardware and must be cleared before the conversion starts (setting CNVRTCH to '1'). 1 = Shared ADC core samples an analog input specified by the CNVCHSEL<5:0> bits 0 = Sampling is controlled by the shared ADC core hardware bit 8 **CNVRTCH:** Software Individual Channel Conversion Trigger bit 1 = Single trigger is generated for an analog input specified by the CNVCHSEL<5:0> bits; when the bit is set, it is automatically cleared by hardware on the next instruction cycle 0 = Next individual channel conversion trigger can be generated bit 7 SWLCTRG: Software Level-Sensitive Common Trigger bit 1 = Triggers are continuously generated for all channels with the software, level-sensitive common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers 0 = No software, level-sensitive common triggers are generated SWCTRG: Software Common Trigger bit bit 6 1 = Single trigger is generated for all channels with the software, common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers; when the bit is set, it is automatically cleared by hardware on the next instruction cycle 0 = Ready to generate the next software, common trigger CNVCHSEL <5:0>: Channel Number Selection for Software Individual Channel Conversion Trigger bits bit 5-0

These bits define a channel to be converted when the CNVRTCH bit is set.

### REGISTER 19-8: ADCON4H: ADC CONTROL REGISTER 4 HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| C3CHS1 | C3CHS0 | C2CHS1 | C2CHS0 | C1CHS1 | C1CHS0 | C0CHS1 | C0CHS0 |

| bit 7  | •      |        |        |        |        |        | bit 0  |

| Legend:    |                                    |                           |                                                             |                    |

|------------|------------------------------------|---------------------------|-------------------------------------------------------------|--------------------|

| R = Reada  | ble bit                            | W = Writable bit          | U = Unimplemented bit                                       | , read as '0'      |

| -n = Value | -n = Value at POR '1' = Bit is set |                           | '0' = Bit is cleared                                        | x = Bit is unknown |

| bit 15-8   | Unimplen                           | nented: Read as '0'       |                                                             |                    |

| bit 7-6    | -                                  |                           | 3 Input Channel Selection bits                              |                    |

|            | 1x = Rese<br>01 = AN15<br>00 = AN3 |                           | when DIFF3 (ADMOD0L<7>)                                     | = 1)               |

| bit 5-4    | C2CHS<1                            | :0>: Dedicated ADC Core 2 | 2 Input Channel Selection bits                              |                    |

|            |                                    | Band Gap                  | when DIFF2 (ADMOD0L<5>)                                     | = 1)               |

| bit 3-2    | 11 = AN1/<br>10 = PGA              | ALT<br>2                  | I Input Channel Selection bits when DIFF1 (ADMOD0L<3>)      | = 1)               |

| bit 1-0    | 11 = AN0/<br>10 = PGA              | ALT<br>1                  | ) Input Channel Selection bits<br>when DIFF0 (ADMOD0L<1>) = | = 1)               |

## 21.2 PGA Resources

Many useful resources are provided on the main product page of the Microchip website for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 21.2.1 KEY RESOURCES

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 21-1: PGAxCON: PGAx CONTROL REGISTER

| R/W-0         | R/W-0                                                                                                                               | R/W-0                                                 | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|

| PGAEN         | PGAOEN                                                                                                                              | SELPI2                                                | SELPI1        | SELPI0           | SELNI2           | SELNI1          | SELNI0 |

| bit 15        |                                                                                                                                     | ·                                                     |               | -                |                  | ·               | bit 8  |

| U-0           | U-0                                                                                                                                 | U-0                                                   | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0  |

| _             | _                                                                                                                                   | _                                                     | _             | _                | GAIN2            | GAIN1           | GAIN0  |

| bit 7         |                                                                                                                                     |                                                       |               |                  |                  |                 | bit 0  |

| Legend:       |                                                                                                                                     |                                                       |               |                  |                  |                 |        |

| R = Readabl   | e bit                                                                                                                               | W = Writable                                          | bit           | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at | POR                                                                                                                                 | '1' = Bit is set                                      |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|               |                                                                                                                                     |                                                       |               |                  |                  |                 |        |

| bit 15        |                                                                                                                                     | Ax Enable bit<br>odule is enableo<br>odule is disable |               | ower consumpti   | on)              |                 |        |

| bit 14        | 1 = PGAx ou                                                                                                                         | GAx Output En<br>tput is connecte<br>tput is not conn | ed to the DAC |                  |                  |                 |        |

| bit 13-11     | SELPI<2:0>:<br>111 = Resen<br>110 = Resen<br>101 = Resen<br>100 = Resen<br>011 = PGAxt<br>010 = PGAxt<br>001 = PGAxt<br>000 = PGAxt | ved<br>ved<br>>4<br>>3<br>>2                          | Input Selecti | ion bits         |                  |                 |        |

| bit 10-8      |                                                                                                                                     | : PGAx Negativ                                        | e Input Selec | tion bits        |                  |                 |        |

|               | 111 = Resen<br>110 = Resen<br>101 = Resen<br>100 = Resen<br>011 = Groun<br>010 = PGAxt<br>001 = PGAxt                               | ved<br>ved<br>ved<br>ved<br>d (Single-Ende<br>N3      | d mode)       |                  |                  |                 |        |

| bit 7-3       |                                                                                                                                     | nted: Read as '                                       | -             |                  |                  |                 |        |

|               |                                                                                                                                     |                                                       |               |                  |                  |                 |        |

### 26.1 DC Characteristics

#### TABLE 26-1: OPERATING MIPS vs. VOLTAGE

| Characteristic | VDD Range                   | Temperature Range | Maximum MIPS            |

|----------------|-----------------------------|-------------------|-------------------------|

| Gharacteristic | (in Volts)                  | (in °C)           | dsPIC33EPXXGS50X Family |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +85°C    | 70                      |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +125°C   | 60                      |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, PGAs and comparators) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 26-13 for the minimum and maximum BOR values.

#### TABLE 26-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min.        | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +85  | °C   |

| Extended Temperature Devices                                                                |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ |        | Pint + Pi/o |             | W    |      |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                           | Pdmax  | (           | TJ — TA)/θJ | IA   | W    |

#### TABLE 26-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                      | Symbol | Тур. | Max. | Unit | Notes |

|-----------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-Pin TQFP 10x10x1 mm  | θJA    | 49.0 |      | °C/W | 1     |

| Package Thermal Resistance, 48-Pin TQFP 7x7x1.0 mm  | θJA    | 63.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN 8x8 mm       | θJA    | 29.0 | -    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP 10x10x1 mm  | θJA    | 50.0 | _    | °C/W | 1     |