Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs502-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

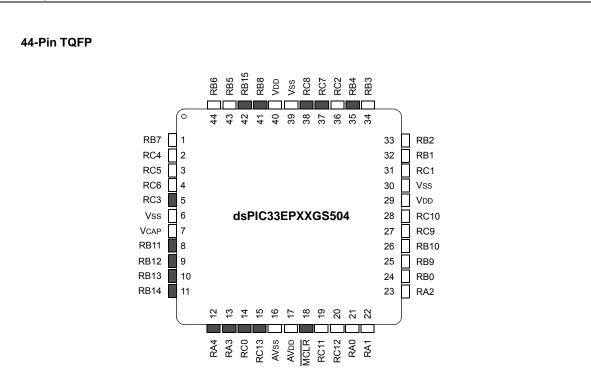

### **Pin Diagrams (Continued)**

| Pin | Pin Function                      | Pin | Pin Function                              |

|-----|-----------------------------------|-----|-------------------------------------------|

| 1   | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7 | 23  | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         |

| 2   | AN1ALT/ <b>RP52</b> /RC4          | 24  | AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0           |

| 3   | AN0ALT/RP53/RC5                   | 25  | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            |

| 4   | AN17/ <b>RP54</b> /RC6            | 26  | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10           |

| 5   | RP51/RC3                          | 27  | AN11/PGA1N3/ <b>RP57</b> /RC9             |

| 6   | Vss                               | 28  | AN10/PGA1P4/EXTREF2/RP58/RC10             |

| 7   | VCAP                              | 29  | VDD                                       |

| 8   | TMS/PWM3H/RP43/RB11               | 30  | Vss                                       |

| 9   | TCK/PWM3L/ <b>RP44</b> /RB12      | 31  | AN8/PGA2P4/CMP4C/RP49/RC1                 |

| 10  | PWM2H/ <b>RP45</b> /RB13          | 32  | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  |

| 11  | PWM2L/ <b>RP46</b> /RB14          | 33  | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/RP34/RB2 |

| 12  | PWM1H/RA4                         | 34  | PGED2/AN18/DACOUT1/INT0/RP35/RB3          |

| 13  | PWM1L/RA3                         | 35  | PGEC2/ADTRG31/ <b>RP36</b> /RB4           |

| 14  | FLT12/ <b>RP48</b> /RC0           | 36  | AN9/CMP4D/EXTREF1/RP50 /RC2               |

| 15  | FLT11/ <b>RP61</b> /RC13          | 37  | ASDA1/ <b>RP55</b> /RC7                   |

| 16  | AVss                              | 38  | ASCL1/RP56/RC8                            |

| 17  | AVDD                              | 39  | Vss                                       |

| 18  | MCLR                              | 40  | VDD                                       |

| 19  | AN12/ISRC1/ <b>RP59</b> /RC11     | 41  | PGED3/SDA2/FLT31/RP40/RB8                 |

| 20  | AN14/PGA2N3/ <b>RP60</b> /RC12    | 42  | PGEC3/SCL2/RP47/RB15                      |

| 21  | AN0/PGA1P1/CMP1A/RA0              | 43  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         |

| 22  | AN1/PGA1P2/PGA2P1/CMP1B/RA1       | 44  | PGED1/TDI/AN20/SCL1/RP38/RB6              |

Legend: Shaded pins are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

| TADLE       | 4-J.  |                                                                         |        | IONEI  | THINOU  |         |         | INFUT CAFTURE I THROUGH INFUT CAFTURE 4 REGISTER MAP |            |              |             |       |          |          |          |          |          |               |

|-------------|-------|-------------------------------------------------------------------------|--------|--------|---------|---------|---------|------------------------------------------------------|------------|--------------|-------------|-------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15                                                                  | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9                                                | Bit 8      | Bit 7        | Bit 6       | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| IC1CON1     | 0140  | —                                                                       | _      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |                                                      | —          | —            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2     | 0142  | _                                                                       | _      | _      | _       | _       | _       | _                                                    | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF      | 0144  |                                                                         |        |        |         |         |         |                                                      | Input Capt | ture 1 Buffe | er Register |       |          |          |          |          |          | xxxx          |

| IC1TMR      | 0146  |                                                                         |        |        |         |         |         |                                                      | Input Cap  | ture 1 Time  | er Register |       |          |          |          |          |          | 0000          |

| IC2CON1     | 0148  | _                                                                       | _      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _                                                    | _          | _            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC2CON2     | 014A  | IC32 ICTRIG TRIGSTAT - SYNCSEL4 SYNCSEL3 SYNCSEL2 SYNCSEL1 SYNCSEL0 000 |        |        |         |         |         |                                                      | 000D       |              |             |       |          |          |          |          |          |               |

| IC2BUF      | 014C  | Input Capture 2 Buffer Register xxx                                     |        |        |         |         |         | xxxx                                                 |            |              |             |       |          |          |          |          |          |               |

| IC2TMR      | 014E  |                                                                         |        |        |         |         |         |                                                      | Input Cap  | ture 2 Time  | er Register |       |          |          |          |          |          | 0000          |

| IC3CON1     | 0150  | _                                                                       | _      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _                                                    | _          | _            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2     | 0152  | —                                                                       | —      | _      | -       | _       | _       | _                                                    | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC3BUF      | 0154  |                                                                         |        |        |         |         |         |                                                      | Input Capt | ture 3 Buffe | er Register |       |          |          |          |          |          | xxxx          |

| IC3TMR      | 0156  |                                                                         |        |        |         |         |         |                                                      | Input Cap  | ture 3 Time  | er Register |       |          |          |          |          |          | 0000          |

| IC4CON1     | 0158  | ICSIDL ICTSEL2 ICTSEL1 ICTSEL0 ICI1 ICI0 ICOV ICBNE ICM2 ICM1 ICM0 000  |        |        |         |         |         |                                                      | 0000       |              |             |       |          |          |          |          |          |               |

| IC4CON2     | 015A  | _                                                                       | _      | _      | —       | _       | _       | _                                                    | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4BUF      | 015C  | Input Capture 4 Buffer Register xxx                                     |        |        |         |         | xxxx    |                                                      |            |              |             |       |          |          |          |          |          |               |

| IC4TMR      | 015E  |                                                                         |        |        |         |         |         |                                                      | Input Cap  | ture 4 Time  | er Register |       |          |          |          |          |          | 0000          |

#### TABLE 4-5: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 4 REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: I2C1 AND I2C2 REGISTER MAP

| SFR<br>Name | Addr.  | Bit 15    | Bit 14      | Bit 13    | Bit 12      | Bit 11     | Bit 10  | Bit 9                        | Bit 8 | Bit 7 | Bit 6                                                        | Bit 5      | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|--------|-----------|-------------|-----------|-------------|------------|---------|------------------------------|-------|-------|--------------------------------------------------------------|------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1CONL    | 0200   | I2CEN     | _           | I2CSIDL   | SCLREL      | STRICT     | A10M    | DISSLW                       | SMEN  | GCEN  | STREN                                                        | ACKDT      | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1CONH    | 0202   | —         | _           | —         | _           | _          | _       | —                            | _     | _     | PCIE                                                         | SCIE       | BOEN         | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C1STAT    | 0204   | ACKSTAT   | TRSTAT      | ACKTIM    | _           | _          | BCL     | GCSTAT                       | ADD10 | IWCOL | I2COV                                                        | D_A        | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 0206   | _         | —           | _         | _           | —          | _       |                              |       |       |                                                              | I2C1 Addr  | ess Register |              |       |       |       | 0000          |

| I2C1MSK     | 0208   | _         | —           | _         | _           | —          | _       |                              |       |       | I2C1 SI                                                      | ave Mode A | ddress Mask  | Register     |       |       |       | 0000          |

| I2C1BRG     | 020A   |           |             |           |             |            |         | Baud Rate Generator Register |       |       |                                                              |            |              | 0000         |       |       |       |               |

| I2C1TRN     | 020C   | _         | —           | _         | _           | —          | _       | I2C1 Transmit Register       |       |       |                                                              |            | OOFF         |              |       |       |       |               |

| I2C1RCV     | 020E   | _         | —           | _         | _           | —          | _       | —                            | _     |       |                                                              |            | I2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2CON1    | 0210   | I2CEN     | —           | I2CSIDL   | SCLREL      | STRICT     | A10M    | DISSLW                       | SMEN  | GCEN  | STREN                                                        | ACKDT      | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2CON2    | 0212   | _         | _           | _         | _           | _          | _       | _                            | _     | _     | PCIE                                                         | SCIE       | BOEN         | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C2STAT    | 0214   | ACKSTAT   | TRSTAT      | ACKTIM    | _           | _          | BCL     | GCSTAT                       | ADD10 | IWCOL | I2COV                                                        | D_A        | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD     | 0216   | _         | _           | _         | _           | _          | _       |                              |       |       |                                                              | I2C2 Addr  | ess Register |              |       |       |       | 0000          |

| I2C2MSK     | 0218   | _         | —           | _         | _           | —          | _       |                              |       |       | 12C2 SI                                                      | ave Mode A | ddress Mask  | Register     |       |       |       | 0000          |

| I2C2BRG     | 021A   |           |             |           |             |            |         | Baud Rate Generator Register |       |       |                                                              |            | 0000         |              |       |       |       |               |

| I2C2TRN     | 021C   | _         | —           | _         | _           | —          | _       | —                            | _     |       |                                                              |            | I2C2 Transr  | nit Register |       |       |       | OOFF          |

| I2C2RCV     | 021E   | _         | _           | -         | —           | —          | _       | —                            | —     |       |                                                              |            | I2C2 Receiv  | ve Register  |       |       |       | 0000          |

| Legend:     | – unim | nlamontad | road as '0' | Peact val | uoo oro obc | we in hove | dooimal | •                            | -     |       | -     -     -     -     -     I2C2 Receive Register     0000 |            |              |              |       |       |       | •             |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14                                                                                 | Bit 13   | Bit 12                      | Bit 11 | Bit 10 | Bit 9                                      | Bit 8      | Bit 7        | Bit 6    | Bit 5 | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|----------------------------------------------------------------------------------------|----------|-----------------------------|--------|--------|--------------------------------------------|------------|--------------|----------|-------|--------|-------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | _                                                                                      | USIDL    | IREN                        | RTSMD  | _      | UEN1                                       | UEN0       | WAKE         | LPBACK   | ABAUD | URXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV                                                                                 | UTXISEL0 | _                           | UTXBRK | UTXEN  | UTXBF                                      | TRMT       | URXISEL1     | URXISEL0 | ADDEN | RIDLE  | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        | —         —         —         —         —         UART1 Transmit Register         xxxx |          |                             |        |        |                                            |            | xxxx         |          |       |        |       |        |        |       |               |

| U1RXREG     | 0226  | _        | _                                                                                      | _        | UART1 Receive Register 0000 |        |        |                                            |            | 0000         |          |       |        |       |        |        |       |               |

| U1BRG       | 0228  |          |                                                                                        |          |                             |        |        | Baud Rate                                  | e Generate | or Prescaler | Register |       |        |       |        |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | _                                                                                      | USIDL    | IREN                        | RTSMD  | _      | UEN1                                       | UEN0       | WAKE         | LPBACK   | ABAUD | URXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV                                                                                 | UTXISEL0 | _                           | UTXBRK | UTXEN  | UTXBF                                      | TRMT       | URXISEL1     | URXISEL0 | ADDEN | RIDLE  | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _                                                                                      | _        | _                           | _      | —      | UART2 Transmit Register                    |            |              |          |       |        | xxxx  |        |        |       |               |

| U2RXREG     | 0236  | _        | -         -         -         -         UART2 Receive Register         000             |          |                             |        |        |                                            | 0000       |              |          |       |        |       |        |        |       |               |

| U2BRG       | 0238  |          |                                                                                        |          |                             |        |        | Baud Rate Generator Prescaler Register 000 |            |              |          |       |        | 0000  |        |        |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Function     | RPnR<5:0> | Output Name                                                 |  |  |  |

|--------------|-----------|-------------------------------------------------------------|--|--|--|

| Default PORT | 000000    | RPn tied to Default Pin                                     |  |  |  |

| U1TX         | 000001    | RPn tied to UART1 Transmit                                  |  |  |  |

| U1RTS        | 000010    | RPn tied to UART1 Request-to-Send                           |  |  |  |

| U2TX         | 000011    | RPn tied to UART2 Transmit                                  |  |  |  |

| U2RTS        | 000100    | RPn tied to UART2 Request-to-Send                           |  |  |  |

| SDO1         | 000101    | RPn tied to SPI1 Data Output                                |  |  |  |

| SCK1         | 000110    | RPn tied to SPI1 Clock Output                               |  |  |  |

| SS1          | 000111    | RPn tied to SPI1 Slave Select                               |  |  |  |

| SDO2         | 001000    | RPn tied to SPI2 Data Output                                |  |  |  |

| SCK2         | 001001    | RPn tied to SPI2 Clock Output                               |  |  |  |

| SS2          | 001010    | RPn tied to SPI2 Slave Select                               |  |  |  |

| OC1          | 010000    | RPn tied to Output Compare 1 Output                         |  |  |  |

| OC2          | 010001    | RPn tied to Output Compare 2 Output                         |  |  |  |

| OC3          | 010010    | RPn tied to Output Compare 3 Output                         |  |  |  |

| OC4          | 010011    | RPn tied to Output Compare 4 Output                         |  |  |  |

| ACMP1        | 011000    | RPn tied to Analog Comparator 1 Output                      |  |  |  |

| ACMP2        | 011001    | RPn tied to Analog Comparator 2 Output                      |  |  |  |

| ACMP3        | 011010    | RPn tied to Analog Comparator 3 Output                      |  |  |  |

| SYNCO1       | 101101    | RPn tied to PWM Primary Master Time Base Sync Output        |  |  |  |

| SYNCO2       | 101110    | RPn tied to PWM Secondary Master Time Base Sync Output      |  |  |  |

| REFCLKO      | 110001    | RPn tied to Reference Clock Output                          |  |  |  |

| ACMP4        | 110010    | RPn tied to Analog Comparator 4 Output                      |  |  |  |

| PWM4H        | 110011    | RPn tied to PWM Output Pins Associated with PWM Generator 4 |  |  |  |

| PWM4L        | 110100    | RPn tied to PWM Output Pins Associated with PWM Generator 4 |  |  |  |

| PWM5H        | 110101    | RPn tied to PWM Output Pins Associated with PWM Generator 5 |  |  |  |

| PWM5L        | 110110    | RPn tied to PWM Output Pins Associated with PWM Generator 5 |  |  |  |

#### TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

#### REGISTER 10-17: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SYNCI2R7 | SYNCI2R6 | SYNCI2R5 | SYNCI2R4 | SYNCI2R3 | SYNCI2R2 | SYNCI2R1 | SYNCI2R0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 SYNCI2R<7:0>: Assign PWM Synchronization Input 2 to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180 •

• 00000001 = Input tied to RP1 00000000 = Input tied to Vss

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP45R5 | RP45R4 | RP45R3 | RP45R2 | RP45R1 | RP45R0 |

| bit 15 | ·   |        | •      |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| _      |     | RP44R5 | RP44R4 | RP44R3 | RP44R2 | RP44R1 | RP44R0 |

| bit 0 |

|-------|

|-------|

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP45R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP45 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP44R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP44 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-27: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | RP47R5 | RP47R4 | RP47R3 | RP47R2 | RP47R1 | RP47R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP46R5 | RP46R4 | RP46R3 | RP46R2 | RP46R1 | RP46R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

|         |     |        |        |        |        |        |        |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 13-8 **RP47R<5:0>:** Peripheral Output Function is Assigned to RP47 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP46R<5:0>:** Peripheral Output Function is Assigned to RP46 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = OCxRS compare event is used for synchronization

- 11110 = INT2 pin synchronizes or triggers OCx

- 11101 = INT1 pin synchronizes or triggers OCx

- 11100 = Reserved

- 11011 = CMP4 module synchronizes or triggers OCx

- 11010 = CMP3 module synchronizes or triggers OCx

- 11001 = CMP2 module synchronizes or triggers OCx

- 11000 = CMP1 module synchronizes or triggers OCx

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 input capture interrupt event synchronizes or triggers OCx

- 10010 = IC3 input capture interrupt event synchronizes or triggers OCx

- 10001 = IC2 input capture interrupt event synchronizes or triggers OCx

- 10000 = IC1 input capture interrupt event synchronizes or triggers OCx

- 01111 = Timer5 synchronizes or triggers OCx

- 01110 = Timer4 synchronizes or triggers OCx

- 01101 = Timer3 synchronizes or triggers OCx

- 01100 = Timer2 synchronizes or triggers OCx (default)

- 01011 = Timer1 synchronizes or triggers OCx

- 01010 = Reserved

- 01001 = Reserved

- 01000 = IC4 input capture event synchronizes or triggers OCx

- 00111 = IC3 input capture event synchronizes or triggers OCx

- 00110 = IC2 input capture event synchronizes or triggers OCx

- 00101 = IC1 input capture event synchronizes or triggers OCx

- 00100 = OC4 module synchronizes or triggers  $OCx^{(1,2)}$

- 00011 = OC3 module synchronizes or triggers  $OCx^{(1,2)}$

- 00010 = OC2 module synchronizes or triggers  $OCx^{(1,2)}$

- 00001 = OC1 module synchronizes or triggers  $OCx^{(1,2)}$

- 00000 = No sync or trigger source for OCx

- Note 1: Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

#### R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 **HRPDIS HRDDIS** \_\_\_ BLANKSEL3 BLANKSEL2 BLANKSEL1 **BLANKSEL0** \_ bit 15 bit 8 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 CHOPSEL3 CHOPSEL2 CHOPSEL1 CHOPSEL0 CHOPHEN CHOPLEN bit 7 bit 0 Leaend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 HRPDIS: High-Resolution PWMx Period Disable bit 1 = High-resolution PWMx period is disabled to reduce power consumption 0 = High-resolution PWMx period is enabled bit 14 HRDDIS: High-Resolution PWMx Duty Cycle Disable bit 1 = High-resolution PWMx duty cycle is disabled to reduce power consumption 0 = High-resolution PWMx duty cycle is enabled bit 13-12 Unimplemented: Read as '0' bit 11-8 BLANKSEL<3:0>: PWMx State Blank Source Select bits The selected state blank signal will block the current-limit and/or Fault input signals (if enabled via the BCH and BCL bits in the LEBCONx register). 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM5H is selected as the state blank source 0100 = PWM4H is selected as the state blank source 0011 = PWM3H is selected as the state blank source 0010 = PWM2H is selected as the state blank source 0001 = PWM1H is selected as the state blank source 0000 = No state blanking bit 7-6 Unimplemented: Read as '0' bit 5-2 CHOPSEL<3:0>: PWMx Chop Clock Source Select bits The selected signal will enable and disable (chop) the selected PWMx outputs. 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM5H is selected as the chop clock source 0100 = PWM4H is selected as the chop clock source 0011 = PWM3H is selected as the chop clock source 0010 = PWM2H is selected as the chop clock source 0001 = PWM1H is selected as the chop clock source 0000 = Chop clock generator is selected as the chop clock source bit 1 **CHOPHEN:** PWMxH Output Chopping Enable bit 1 = PWMxH chopping function is enabled 0 = PWMxH chopping function is disabled bit 0 CHOPLEN: PWMxL Output Chopping Enable bit 1 = PWMxL chopping function is enabled 0 = PWMxL chopping function is disabled

**REGISTER 15-26:** AUXCONx: PWMx AUXILIARY CONTROL REGISTER (x = 1 to 5)

| -                           | R/W-0                                                                                                                                                                    | R/W-0                                                                                                                                                                                           | U-0                                                                                                                                         | U-0                     | U-0             | U-0               | U-0                                                                                                     |  |  |  |  |  |  |  |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| FRMEN                       | SPIFSD                                                                                                                                                                   | FRMPOL                                                                                                                                                                                          | _                                                                                                                                           | —                       | _               | —                 | _                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| bit 15                      | ·                                                                                                                                                                        |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   | bit 8                                                                                                   |  |  |  |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| U-0                         | U-0                                                                                                                                                                      | U-0                                                                                                                                                                                             | U-0                                                                                                                                         | U-0                     | U-0             | R/W-0             | R/W-0                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| —                           | — — — — FRMDLY SP                                                                                                                                                        |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 7                       |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   | bit 0                                                                                                   |  |  |  |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| Legend:                     |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| R = Readab                  | ole bit                                                                                                                                                                  | W = Writable b                                                                                                                                                                                  | oit                                                                                                                                         | U = Unimplen            | nented bit, rea | id as '0'         |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| -n = Value a                | at POR                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                                                |                                                                                                                                             | '0' = Bit is cle        | ared            | x = Bit is unkn   | nown                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 15                      | FRMEN: Fran                                                                                                                                                              | med SPIx Suppo                                                                                                                                                                                  | ort bit                                                                                                                                     |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                          |                                                                                                                                                                                                 | •                                                                                                                                           | pin is used as          | the frame syn   | c pulse input/out | 1 = Framed SPIx support is enabled ( $\overline{SSx}$ pin is used as the frame sync pulse input/output) |  |  |  |  |  |  |  |  |  |  |

|                             | 0 = Framed S                                                                                                                                                             | 0 = Framed SPIx support is disabled                                                                                                                                                             |                                                                                                                                             |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|                             | SPIFSD: Frame Sync Pulse Direction Control bit                                                                                                                           |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 14                      | SPIFSD: Fran                                                                                                                                                             | me Sync Pulse [                                                                                                                                                                                 | Direction Co                                                                                                                                | ntrol bit               |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 14                      | <b>SPIFSD:</b> Fran<br>1 = Frame sy                                                                                                                                      | ••                                                                                                                                                                                              | Direction Co<br>slave)                                                                                                                      | ntrol bit               |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 14<br>bit 13            | <b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy                                                                                                                      | me Sync Pulse I<br>nc pulse input (s                                                                                                                                                            | Direction Co<br>slave)<br>(master)                                                                                                          | ntrol bit               |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|                             | <b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy<br><b>FRMPOL:</b> Fra<br>1 = Frame sy                                                                                | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output                                                                                                                                         | Direction Co<br>slave)<br>(master)<br>Polarity bit<br>e-high                                                                                | ntrol bit               |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|                             | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fra<br>1 = Frame sy<br>0 = Frame sy                                                                              | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ                                                                                                  | Direction Col<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low                                                                      | ntrol bit               |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 13                      | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fran<br>1 = Frame sy<br>0 = Frame sy<br>Unimplemen                                                               | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ                                                                             | Direction Col<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low                                                                      |                         |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 13<br>bit 12-2          | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fra<br>1 = Frame sy<br>0 = Frame sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame sy                                 | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ<br>ted: Read as '0                                                          | Direction Col<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low<br>,<br>Edge Select<br>les with the f                                | t bit<br>îrst bit clock |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 13<br>bit 12-2<br>bit 1 | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fra<br>1 = Frame sy<br>0 = Frame sy<br>Unimplement<br>FRMDLY: Fra<br>1 = Frame sy<br>0 = Frame sy                | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ<br>ted: Read as '0<br>ame Sync Pulse<br>nc pulse coincid                    | Direction Col<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low<br>,<br>Edge Select<br>les with the f<br>es the first b              | t bit<br>îrst bit clock |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| bit 13<br>bit 12-2          | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fra<br>1 = Frame sy<br>0 = Frame sy<br>Unimplement<br>FRMDLY: Fra<br>1 = Frame sy<br>0 = Frame sy<br>SPIBEN: Ent | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ<br>ted: Read as '0<br>ame Sync Pulse<br>nc pulse coincid<br>nc pulse preced | Direction Con<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low<br>,<br>Edge Select<br>les with the f<br>es the first b<br>nable bit | t bit<br>îrst bit clock |                 |                   |                                                                                                         |  |  |  |  |  |  |  |  |  |  |

#### REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

#### REGISTER 19-5: ADCON3L: ADC CONTROL REGISTER 3 LOW

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R-0, HSC | R/W-0   | R-0, HSC |

|---------|---------|---------|---------|---------|----------|---------|----------|

| REFSEL2 | REFSEL1 | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY  | SHRSAMP | CNVRTCH  |

| bit 15  |         |         |         |         |          |         | bit 8    |

| R/W-0   | R/W-0, HSC | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|---------|------------|-----------|-----------|-----------|-----------|-----------|-----------|

| SWLCTRG | SWCTRG     | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2 | CNVCHSEL1 | CNVCHSEL0 |

| bit 7   |            |           |           |           |           |           | bit 0     |

| Legend:           | U = Unimplemented bit, read                            | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|--------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 15-13 **REFSEL<2:0>:** ADC Reference Voltage Selection bits

| Value | VREFH | VREFL |

|-------|-------|-------|

| 000   | AVdd  | AVss  |

001-111 = Unimplemented: Do not use bit 12 SUSPEND: All ADC Cores Triggers Disable bit 1 = All new trigger events for all ADC cores are disabled 0 = All ADC cores can be triggered bit 11 SUSPCIE: Suspend All ADC Cores Common Interrupt Enable bit 1 = Common interrupt will be generated when ADC core triggers are suspended (SUSPEND bit = 1) and all previous conversions are finished (SUSPRDY bit becomes set) 0 = Common interrupt is not generated for suspend ADC cores event bit 10 SUSPRDY: All ADC Cores Suspended Flag bit 1 = All ADC cores are suspended (SUSPEND bit = 1) and have no conversions in progress 0 = ADC cores have previous conversions in progress bit 9 SHRSAMP: Shared ADC Core Sampling Direct Control bit This bit should be used with the individual channel conversion trigger controlled by the CNVRTCH bit. It connects an analog input, specified by the CNVCHSEL<5:0> bits, to the shared ADC core and allows extending the sampling time. This bit is not controlled by hardware and must be cleared before the conversion starts (setting CNVRTCH to '1'). 1 = Shared ADC core samples an analog input specified by the CNVCHSEL<5:0> bits 0 = Sampling is controlled by the shared ADC core hardware bit 8 **CNVRTCH:** Software Individual Channel Conversion Trigger bit 1 = Single trigger is generated for an analog input specified by the CNVCHSEL<5:0> bits; when the bit is set, it is automatically cleared by hardware on the next instruction cycle 0 = Next individual channel conversion trigger can be generated bit 7 SWLCTRG: Software Level-Sensitive Common Trigger bit 1 = Triggers are continuously generated for all channels with the software, level-sensitive common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers 0 = No software, level-sensitive common triggers are generated SWCTRG: Software Common Trigger bit bit 6 1 = Single trigger is generated for all channels with the software, common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers; when the bit is set, it is automatically cleared by hardware on the next instruction cycle 0 = Ready to generate the next software, common trigger CNVCHSEL <5:0>: Channel Number Selection for Software Individual Channel Conversion Trigger bits bit 5-0

These bits define a channel to be converted when the CNVRTCH bit is set.

| U-0                   | U-0       | U-0                                   | U-0            | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-----------------------|-----------|---------------------------------------|----------------|----------------------------|-----------------|-----------------|-----------------|

| —                     | —         | —                                     |                | SYNCTRG3                   | SYNCTRG2        | SYNCTRG1        | SYNCTRGO        |

| bit 15                |           |                                       |                |                            |                 |                 | bit 8           |

| U-0                   | U-0       | U-0                                   | U-0            | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

| _                     | _         |                                       | _              | SAMC3EN                    | SAMC2EN         | SAMC1EN         | SAMCOEN         |

| oit 7                 |           |                                       |                |                            |                 |                 | bit (           |

| _egend:               |           |                                       |                |                            |                 |                 |                 |

| -egend.<br>R = Readab | le hit    | W = Writable                          | hit            | II = I Inimplem            | ented bit, read | l as 'N'        |                 |

| n = Value a           |           | '1' = Bit is set                      |                | 0' = Bit is clea           |                 | x = Bit is unkr | own             |

|                       |           |                                       |                |                            |                 |                 |                 |

| oit 15-12             | Unimpleme | ented: Read as '                      | 0'             |                            |                 |                 |                 |

| pit 11                | SYNCTRG3  | : Dedicated AD                        | C Core 3 Trigg | ger Synchronizat           | ion bit         |                 |                 |

|                       |           |                                       |                | core source cloc           | k (TCORESRC)    |                 |                 |

|                       |           | C core triggers a                     | -              |                            |                 |                 |                 |

| bit 10                |           |                                       |                | ger Synchronizat           |                 |                 |                 |

|                       |           | ers are synchror<br>C core triggers a |                | core source cloc<br>onized | K (ICORESRC)    |                 |                 |

| oit 9                 |           |                                       | -              | ger Synchronizat           | ion bit         |                 |                 |

|                       |           |                                       |                | core source cloc           |                 |                 |                 |

|                       |           | C core triggers a                     |                |                            | . ,             |                 |                 |

| oit 8                 | SYNCTRG   | : Dedicated AD                        | C Core 0 Trigg | ger Synchronizat           | ion bit         |                 |                 |

|                       |           | ers are synchror<br>C core triggers a |                | core source cloc<br>onized | k (TCORESRC)    |                 |                 |

| oit 7-4               |           | ented: Read as '                      | -              |                            |                 |                 |                 |

| oit 3                 | SAMC3EN:  | Dedicated ADC                         | Core 3 Conve   | ersion Delay Ena           | ble bit         |                 |                 |

|                       |           |                                       |                | elayed and the             |                 | continue samp   | ling during the |

|                       |           |                                       |                | s in the ADCORE            |                 |                 | -4              |

|                       |           | gger, the sampli<br>re clock cycle    | ng will be sto | pped immediatel            | y and the conv  | version will be | started on the  |

| oit 2                 | SAMC2EN:  | Dedicated ADC                         | Core 2 Conve   | ersion Delay Ena           | ble bit         |                 |                 |

|                       |           |                                       |                | elayed and the A           |                 | continue samp   | ling during the |

|                       |           |                                       |                | s in the ADCORE            |                 | eraion will be  | atartad an the  |

|                       |           | re clock cycle                        | ng will be sto | pped immediatel            | y and the com   |                 | started on the  |

| oit 1                 |           | -                                     | Core 1 Conve   | ersion Delay Ena           | ble bit         |                 |                 |

|                       |           |                                       |                | elayed and the A           |                 | continue samp   | ling during the |

|                       |           |                                       |                | s in the ADCORE            |                 |                 |                 |

|                       |           | gger, the sampli<br>re clock cycle    | ng will be sto | pped immediatel            | y and the conv  | version will be | started on the  |

| oit O                 |           | -                                     | Core 0 Conve   | ersion Delay Ena           | ble bit         |                 |                 |

|                       |           |                                       |                | elayed and the A           |                 | continue samp   | ling during the |

|                       |           |                                       |                | s in the ADCORE            |                 | -               | -               |

|                       |           |                                       |                | pped immediatel            |                 |                 |                 |

#### REGISTER 19-13: ADLVLTRGL: ADC LEVEL-SENSITIVE TRIGGER CONTROL REGISTER LOW

| R/W-0                                                                    | R/W-0 | U-0              | U-0   | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|--------------------------------------------------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                                                                          |       |                  | LVLE  | N<15:8>                                 |       |       |       |

| bit 15                                                                   |       |                  |       |                                         |       |       | bit 8 |

| R/W-0                                                                    | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                                                          |       |                  | LVL   | EN<7:0>                                 |       |       |       |

| bit 7                                                                    |       |                  |       |                                         |       |       | bit 0 |

| Legend:                                                                  |       |                  |       |                                         |       |       |       |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0' |       |                  |       |                                         |       |       |       |

| -n = Value at I                                                          |       | '1' = Bit is set |       | (0) = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 LVLEN<15:0>: Level Trigger for Corresponding Analog Input Enable bits

1 = Input trigger is level-sensitive

0 = Input trigger is edge-sensitive

#### REGISTER 19-14: ADLVLTRGH: ADC LEVEL-SENSITIVE TRIGGER CONTROL REGISTER HIGH

| <u>– – – – – – – –</u><br>bit 15 bit 8 | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|----------------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8                           | —      | _   | —   | —   | —   | —   | —   | —     |

|                                        | bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|--------|---------|-------|-------|

| —     | —   |       |       | LVLEN• | <21:16> |       |       |

| bit 7 |     |       |       |        |         |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 LVLEN<21:16>: Level Trigger for Corresponding Analog Input Enable bits

1 = Input trigger is level-sensitive

0 = Input trigger is edge-sensitive

### REGISTER 19-26: ADTRIGXL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5) (CONTINUED)

bit 4-0 TRGSRC(4x)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

- 11111 = ADTRG31

- 11110 = Reserved

- 11101 = Reserved

- 11100 = PWM Generator 5 current-limit trigger

- 11011 = PWM Generator 4 current-limit trigger

- 11010 = PWM Generator 3 current-limit trigger

- 11001 = PWM Generator 2 current-limit trigger

- 11000 = PWM Generator 1 current-limit trigger

- 10111 = Output Compare 2 trigger

- 10110 = Output Compare 1 trigger 10101 = Reserved

- 10100 = Reserved

- 10011 = PWM Generator 5 secondary trigger

- 10010 = PWM Generator 4 secondary trigger

- 10001 = PWM Generator 3 secondary trigger

- 10000 = PWM Generator 2 secondary trigger

- 01111 = PWM Generator 1 secondary trigger

- 01110 = PWM secondary Special Event Trigger

- 01101 = Timer2 period match

- 01100 = Timer1 period match

- 01011 = Reserved

- 01010 = Reserved

- 01001 = PWM Generator 5 primary trigger

- 01000 = PWM Generator 4 primary trigger

- 00111 = PWM Generator 3 primary trigger

- 00110 = PWM Generator 2 primary trigger

- 00101 = PWM Generator 1 primary trigger

- 00100 = PWM Special Event Trigger

- 00011 = Reserved

- 00010 = Level software trigger

- 00001 = Common software trigger

- 00000 = No trigger is enabled

#### REGISTER 19-29: ADCAL0H: ADC CALIBRATION REGISTER 0 HIGH

| R-0, HSC      | U-0                                                                                                         | U-0                                                                                                                           | U-0              | r-0              | R/W-0            | R/W-0           | R/W-0            |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|------------------|--|--|--|--|

| CAL3RDY       | —                                                                                                           | —                                                                                                                             | _                | _                | CAL3DIFF         | CAL3EN          | CAL3RUN          |  |  |  |  |

| bit 15        |                                                                                                             |                                                                                                                               |                  |                  |                  | 1               | bit 8            |  |  |  |  |

|               |                                                                                                             |                                                                                                                               |                  |                  |                  |                 |                  |  |  |  |  |

| R-0, HSC      | U-0                                                                                                         | U-0                                                                                                                           | U-0              | r-0              | R/W-0            | R/W-0           | R/W-0            |  |  |  |  |

| CAL2RDY       |                                                                                                             | —                                                                                                                             |                  |                  | CAL2DIFF         | CAL2EN          | CAL2RUN          |  |  |  |  |

| bit 7         | •                                                                                                           | ·                                                                                                                             | •                |                  | ·                | •               | bit 0            |  |  |  |  |

|               |                                                                                                             |                                                                                                                               |                  |                  |                  |                 |                  |  |  |  |  |

| Legend:       |                                                                                                             | r = Reserved                                                                                                                  | bit              | U = Unimpler     | nented bit, read | l as '0'        |                  |  |  |  |  |

| R = Readabl   | = Readable bit W = Writable bit                                                                             |                                                                                                                               |                  |                  | vare Settable/C  | learable bit    |                  |  |  |  |  |

| -n = Value at | n = Value at POR '1' = Bit is set                                                                           |                                                                                                                               |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown             |  |  |  |  |

|               |                                                                                                             |                                                                                                                               |                  |                  |                  |                 |                  |  |  |  |  |

| bit 15        |                                                                                                             | Dedicated ADC                                                                                                                 |                  |                  | g bit            |                 |                  |  |  |  |  |

|               |                                                                                                             | ed ADC Core 3 o                                                                                                               |                  |                  |                  |                 |                  |  |  |  |  |

| bit 14-12     | <ul> <li>0 = Dedicated ADC Core 3 calibration is in progress</li> <li>Unimplemented: Read as '0'</li> </ul> |                                                                                                                               |                  |                  |                  |                 |                  |  |  |  |  |

| bit 11        | -                                                                                                           | Aust be written a                                                                                                             |                  |                  |                  |                 |                  |  |  |  |  |

| bit 10        | CAL3DIFF: Dedicated ADC Core 3 Differential-Mode Calibration bit                                            |                                                                                                                               |                  |                  |                  |                 |                  |  |  |  |  |

| bit to        | 1 = Dedicated ADC Core 3 will be calibrated in Differential Input mode                                      |                                                                                                                               |                  |                  |                  |                 |                  |  |  |  |  |

|               |                                                                                                             | ed ADC Core 3 v                                                                                                               |                  | •                |                  |                 |                  |  |  |  |  |

| bit 9         | CAL3EN: De                                                                                                  | edicated ADC C                                                                                                                | ore 3 Calibratio | on Enable bit    |                  |                 |                  |  |  |  |  |

|               |                                                                                                             | ed ADC Core 3 o                                                                                                               | calibration bits | (CALxRDY, CA     | LxDIFF and CA    | LxRUN) can b    | e accessed by    |  |  |  |  |

|               | software                                                                                                    | ed ADC Core 3                                                                                                                 | calibration bite | are disabled     |                  |                 |                  |  |  |  |  |

| bit 8         |                                                                                                             | Dedicated ADC                                                                                                                 |                  |                  |                  |                 |                  |  |  |  |  |

| DILO          |                                                                                                             | it is set by soft                                                                                                             |                  |                  | ore 3 calibratio | n cycle is star | ted: this hit is |  |  |  |  |

|               |                                                                                                             | tically cleared by                                                                                                            |                  |                  |                  |                 |                  |  |  |  |  |