Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs502-i-2n |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2   | SFA: Stack Frame Active Status bit                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG</li> <li>0 = Stack frame is not active; W14 and W15 address the base Data Space</li> </ul> |

| bit 1   | RND: Rounding Mode Select bit                                                                                                                                                             |

|         | <ul><li>1 = Biased (conventional) rounding is enabled</li><li>0 = Unbiased (convergent) rounding is enabled</li></ul>                                                                     |

| bit 0   | IF: Integer or Fractional Multiplier Mode Select bit                                                                                                                                      |

|         | <ul> <li>1 = Integer mode is enabled for DSP multiply</li> <li>0 = Fractional mode is enabled for DSP multiply</li> </ul>                                                                 |

| Note 1: | This bit is always read as '0'.                                                                                                                                                           |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### REGISTER 3-3: CTXTSTAT: CPU W REGISTER CONTEXT STATUS REGISTER

| U-0             | U-0 | U-0              | U-0 | U-0              | R-0                          | R-0    | R-0    |  |  |  |

|-----------------|-----|------------------|-----|------------------|------------------------------|--------|--------|--|--|--|

| —               | —   | —                | —   | —                | CCTXI2                       | CCTXI1 | CCTXI0 |  |  |  |

| bit 15 bit      |     |                  |     |                  |                              |        |        |  |  |  |

|                 |     |                  |     |                  |                              |        |        |  |  |  |

| U-0             | U-0 | U-0              | U-0 | U-0              | R-0                          | R-0    | R-0    |  |  |  |

|                 | —   | —                | _   | —                | MCTXI2                       | MCTXI1 | MCTXI0 |  |  |  |

| bit 7           |     |                  |     |                  |                              |        | bit 0  |  |  |  |

|                 |     |                  |     |                  |                              |        |        |  |  |  |

| Legend:         |     |                  |     |                  |                              |        |        |  |  |  |

| R = Readable I  | bit | W = Writable     | bit | U = Unimpler     | nented bit, read             | as '0' |        |  |  |  |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cle | s cleared x = Bit is unknown |        |        |  |  |  |

| bit 15-11 | Unimplemented: Read as '0'                                                 |

|-----------|----------------------------------------------------------------------------|

| bit 10-8  | CCTXI<2:0>: Current (W Register) Context Identifier bits                   |

|           | 111 = Reserved                                                             |

|           | •                                                                          |

|           | •                                                                          |

|           | •                                                                          |

|           | 011 = Reserved                                                             |

|           | 010 = Alternate Working Register Set 2 is currently in use                 |

|           | 001 = Alternate Working Register Set 1 is currently in use                 |

|           | 000 = Default register set is currently in use                             |

| bit 7-3   | Unimplemented: Read as '0'                                                 |

| bit 2-0   | MCTXI<2:0>: Manual (W Register) Context Identifier bits                    |

|           | 111 = Reserved                                                             |

|           | •                                                                          |

|           | •                                                                          |

|           | •                                                                          |

|           | 011 = Reserved                                                             |

|           | 010 = Alternate Working Register Set 2 was most recently manually selected |

|           | 001 = Alternate Working Register Set 1 was most recently manually selected |

|           | 000 = Default register set was most recently manually selected             |

### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

| 7                          | GOTO Instruction                                      | 0x000000                         |

|----------------------------|-------------------------------------------------------|----------------------------------|

|                            | Reset Address                                         | 0x000002                         |

| Ð                          | Interrupt Vector Table                                | 0x000004<br>0x0001FE             |

| User Memory Space          | User Program<br>Flash Memory<br>(22,207 instructions) | 0x000200<br>0x00AF7E             |

| er Mem                     | Device Configuration                                  | 0x00AF80<br>0x00AFFE             |

| Use                        |                                                       | 0x00B000                         |

|                            | Unimplemented                                         |                                  |

|                            | (Read '0's)                                           |                                  |

|                            | Reserved                                              | 0x7FFFFE<br>0x800000<br>0x800E46 |

|                            | Calibration Data                                      | 0x800E48                         |

|                            | Reserved                                              | 0x800E78<br>0x800E7A<br>0x800EFE |

| Configuration Memory Space | UDID                                                  | 0x800F00<br>0x800F08<br>0x800F0A |

| nory S                     | Reserved                                              | 0x800F7E                         |

| n Mer                      | User OTP Memory                                       | 0x800F80<br>0x800FFC             |

| Iratio                     | Reserved                                              | 0x801000                         |

| onfigu                     | Write Latches                                         | 0xF9FFFE<br>0xFA0000             |

| ŏ                          |                                                       | 0xFA0002<br>0xFA0004             |

|                            | Reserved                                              |                                  |

|                            | DEVID                                                 | 0xFEFFFE<br>0xFF0000             |

|                            | Reserved                                              | 0xFF0002<br>0xFF0004             |

| _                          |                                                       | 0xFFFFFE                         |

Note: Memory areas are not shown to scale.

| TABLE 4-6:       OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP |       |        |                             |          |         |         |         |       |            |              |              |        |          |          |          |          |          |               |

|-------------------------------------------------------------------------|-------|--------|-----------------------------|----------|---------|---------|---------|-------|------------|--------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name                                                             | Addr. | Bit 15 | Bit 14                      | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8      | Bit 7        | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| OC1CON1                                                                 | 0900  | _      | _                           | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | —          | ENFLTA       | —            | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2                                                                 | 0902  | FLTMD  | FLTOUT                      | FLTTRIEN | OCINV   |         | —       | _     | OC32       | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS                                                                   | 0904  |        |                             |          |         |         |         | 0     | utput Comp | are 1 Seco   | ndary Regist | er     |          |          |          |          |          | xxxx          |

| OC1R                                                                    | 0906  |        |                             |          |         |         |         |       | Output     | Compare 1    | Register     |        |          |          |          |          |          | xxxx          |

| OC1TMR                                                                  | 0908  |        |                             |          |         |         |         |       | Time       | r Value 1 Re | egister      |        |          |          |          |          |          | xxxx          |

| OC2CON1                                                                 | 090A  |        | —                           | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 |       | —          | ENFLTA       |              | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2                                                                 | 090C  | FLTMD  | FLTOUT                      | FLTTRIEN | OCINV   |         | —       |       | OC32       | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS                                                                   | 090E  |        |                             |          |         |         |         | 0     | utput Comp | are 2 Seco   | ndary Regist | er     |          |          |          |          |          | xxxx          |

| OC2R                                                                    | 0910  |        |                             |          |         |         |         |       | Output     | Compare 2    | Register     |        |          |          |          |          |          | xxxx          |

| OC2TMR                                                                  | 0912  |        |                             |          |         |         |         |       | Time       | r Value 2 Re | egister      |        |          |          |          |          |          | xxxx          |

| OC3CON1                                                                 | 0914  |        | —                           | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 |       | —          | ENFLTA       |              | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2                                                                 | 0916  | FLTMD  | FLTOUT                      | FLTTRIEN | OCINV   |         | —       |       | OC32       | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS                                                                   | 0918  |        |                             |          |         |         |         | 0     | utput Comp | are 3 Seco   | ndary Regist | er     |          |          |          |          |          | xxxx          |

| OC3R                                                                    | 091A  |        |                             |          |         |         |         |       | Output     | Compare 3    | Register     |        |          |          |          |          |          | xxxx          |

| OC3TMR                                                                  | 091C  |        |                             |          |         |         |         |       | Time       | r Value 3 Re | egister      |        |          |          |          |          |          | xxxx          |

| OC4CON1                                                                 | 091E  |        | —                           | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 |       | —          | ENFLTA       |              | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2                                                                 | 0920  | FLTMD  | FLTOUT                      | FLTTRIEN | OCINV   |         | -       |       | OC32       | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS                                                                   | 0922  |        |                             |          |         |         |         | 0     | utput Comp | are 4 Seco   | ndary Regist | er     |          |          |          |          |          | xxxx          |

| OC4R                                                                    | 0924  |        |                             |          |         |         |         |       | Output     | Compare 4    | Register     |        |          |          |          |          |          | xxxx          |

| OC4TMR                                                                  | 0926  |        | Timer Value 4 Register xxxx |          |         |         |         |       |            |              |              | xxxx   |          |          |          |          |          |               |

-

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

When a PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the PSV pages can occur at the page boundaries when:

- The initial address, prior to modification, addresses the PSV page

- The EA calculation uses Pre- or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSRPAG register is incremented and the EA<15> bit is set to keep the base address within the PSV window. When an underflow is detected, the DSRPAG register is decremented and the EA<15> bit is set to keep the base

address within the PSV window. This creates a linear PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0 and PSV spaces. Table 4-37 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSRPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- Register Indirect with Register Offset Addressing

- Modulo Addressing

- Bit-Reversed Addressing

| TABLE 4-37: | OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0 AND |

|-------------|------------------------------------------------|

|             | PSV SPACE BOUNDARIES <sup>(2,3,4)</sup>        |

| O/U,        |                    |                | Before       |                        | After          |              |                        |  |

|-------------|--------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|

| 0/0,<br>R/W | Operation          | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |

| O,<br>Read  | [++Wn]             | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |

| O,<br>Read  | Or<br>[Wn++]       | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |

| U,<br>Read  |                    | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn] | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |

| U,<br>Read  |                    | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x7FFF).

2: An EDS access, with DSRPAG = 0x000, will generate an address error trap.

3: Only reads from PS are supported using DSRPAG.

4: Pseudolinear Addressing is not supported for large offsets.

### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0            | U-0 | U-0              | U-0  | U-0          | U-0              | U-0      | U-0   |

|----------------|-----|------------------|------|--------------|------------------|----------|-------|

| —              | _   | —                | _    | —            | —                | —        | _     |

| bit 15         |     | · · ·            |      |              | •                |          | bit 8 |

|                |     |                  |      |              |                  |          |       |

| W-0            | W-0 | W-0              | W-0  | W-0          | W-0              | W-0      | W-0   |

|                |     |                  | NVMK | EY<7:0>      |                  |          |       |

| bit 7          |     |                  |      |              |                  |          | bit 0 |

|                |     |                  |      |              |                  |          |       |

| Legend:        |     |                  |      |              |                  |          |       |

| R = Readable b | oit | W = Writable bit | t    | U = Unimpler | mented bit, read | l as '0' |       |

|                |     |                  |      |              |                  |          |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** NVM Key Register bits (write-only)

### REGISTER 5-5: NVMSRCADR: NVM SOURCE DATA ADDRESS REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |  |

|-----------------|-------|------------------|--------|------------------|-----------------|--------------------|-------|--|--|

|                 |       |                  | NVMSRC | CADR<15:8>       |                 |                    |       |  |  |

| bit 15          |       |                  |        |                  |                 |                    |       |  |  |

|                 |       |                  |        |                  |                 |                    |       |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |  |

|                 |       |                  | NVMSR  | CADR<7:0>        |                 |                    |       |  |  |

| bit 7           |       |                  |        |                  |                 |                    | bit 0 |  |  |

|                 |       |                  |        |                  |                 |                    |       |  |  |

| Legend:         |       |                  |        |                  |                 |                    |       |  |  |

| R = Readable    | bit   | W = Writable b   | it     | U = Unimplen     | nented bit, rea | d as '0'           |       |  |  |

| -n = Value at P | POR   | '1' = Bit is set |        | '0' = Bit is cle | ared            | x = Bit is unknown |       |  |  |

#### bit 15-0 NVMSRCADR<15:0>: NVM Source Data Address bits

The RAM address of the data to be programmed into Flash when the NVMOP<3:0> bits are set to row programming.

# TABLE 7-1: INTERRUPT VECTOR DETAILS

|                                      | Vector | IRQ       |                     | Inte     | errupt Bit Lo | cation      |

|--------------------------------------|--------|-----------|---------------------|----------|---------------|-------------|

| Interrupt Source                     | #      | #         | IVT Address         | Flag     | Enable        | Priority    |

|                                      | Hi     | ghest Nat | ural Order Priority | •        |               |             |

| INT0 – External Interrupt 0          | 8      | 0         | 0x000014            | IFS0<0>  | IEC0<0>       | IPC0<2:0>   |

| IC1 – Input Capture 1                | 9      | 1         | 0x000016            | IFS0<1>  | IEC0<1>       | IPC0<6:4>   |

| OC1 – Output Compare 1               | 10     | 2         | 0x000018            | IFS0<2>  | IEC0<2>       | IPC0<10:8>  |

| T1 – Timer1                          | 11     | 3         | 0x00001A            | IFS0<3>  | IEC0<3>       | IPC0<14:12> |

| Reserved                             | 12     | 4         | 0x00001C            | _        |               | _           |

| IC2 – Input Capture 2                | 13     | 5         | 0x00001E            | IFS0<5>  | IEC0<5>       | IPC1<6:4>   |

| OC2 – Output Compare 2               | 14     | 6         | 0x000020            | IFS0<6>  | IEC0<6>       | IPC1<10:8>  |

| T2 – Timer2                          | 15     | 7         | 0x000022            | IFS0<7>  | IEC0<7>       | IPC1<14:12> |

| T3 – Timer3                          | 16     | 8         | 0x000024            | IFS0<8>  | IEC0<8>       | IPC2<2:0>   |

| SPI1E – SPI1 Error                   | 17     | 9         | 0x000026            | IFS0<9>  | IEC0<9>       | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done            | 18     | 10        | 0x000028            | IFS0<10> | IEC0<10>      | IPC2<10:8>  |

| U1RX – UART1 Receiver                | 19     | 11        | 0x00002A            | IFS0<11> | IEC0<11>      | IPC2<14:12> |

| U1TX – UART1 Transmitter             | 20     | 12        | 0x00002C            | IFS0<12> | IEC0<12>      | IPC3<2:0>   |

| ADC – ADC Global Convert Done        | 21     | 13        | 0x00002E            | IFS0<13> | IEC0<13>      | IPC3<6:4>   |

| Reserved                             | 22     | 14        | 0x000030            | _        | _             | _           |

| NVM – NVM Write Complete             | 23     | 15        | 0x000032            | IFS0<15> | IEC0<15>      | IPC3<14:12> |

| SI2C1 – I2C1 Slave Event             | 24     | 16        | 0x000034            | IFS1<0>  | IEC1<0>       | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event            | 25     | 17        | 0x000036            | IFS1<1>  | IEC1<1>       | IPC4<6:4>   |

| CMP1 – Analog Comparator 1 Interrupt | 26     | 18        | 0x000038            | IFS1<2>  | IEC1<2>       | IPC4<10:8>  |

| CN – Input Change Interrupt          | 27     | 19        | 0x00003A            | IFS1<3>  | IEC1<3>       | IPC4<14:12> |

| INT1 – External Interrupt 1          | 28     | 20        | 0x00003C            | IFS1<4>  | IEC1<4>       | IPC5<2:0>   |

| Reserved                             | 29-32  | 21-24     | 0x00003E-0x000044   | _        | _             | _           |

| OC3 – Output Compare 3               | 33     | 25        | 0x000046            | IFS1<9>  | IEC1<9>       | IPC6<6:4>   |

| OC4 – Output Compare 4               | 34     | 26        | 0x000048            | IFS1<10> | IEC1<10>      | IPC6<10:8>  |

| T4 – Timer4                          | 35     | 27        | 0x00004A            | IFS1<11> | IEC1<11>      | IPC6<14:12> |

| T5 – Timer5                          | 36     | 28        | 0x00004C            | IFS1<12> | IEC1<12>      | IPC7<2:0>   |

| INT2 – External Interrupt 2          | 37     | 29        | 0x00004E            | IFS1<13> | IEC1<13>      | IPC7<6:4>   |

| U2RX – UART2 Receiver                | 38     | 30        | 0x000050            | IFS1<14> | IEC1<14>      | IPC7<10:8>  |

| U2TX – UART2 Transmitter             | 39     | 31        | 0x000052            | IFS1<15> | IEC1<15>      | IPC7<14:12> |

| SPI2E – SPI2 Error                   | 40     | 32        | 0x000054            | IFS2<0>  | IEC2<0>       | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done            | 41     | 33        | 0x000056            | IFS2<1>  | IEC2<1>       | IPC8<6:4>   |

| Reserved                             | 42-44  | 34-36     | 0x000058-0x00005C   | —        | _             | _           |

| IC3 – Input Capture 3                | 45     | 37        | 0x00005E            | IFS2<5>  | IEC2<5>       | IPC9<6:4>   |

| IC4 – Input Capture 4                | 46     | 38        | 0x000060            | IFS2<6>  | IEC2<6>       | IPC9<10:8>  |

| Reserved                             | 47-56  | 39-48     | 0x000062-0x000074   | _        | _             | _           |

| SI2C2 – I2C2 Slave Event             | 57     | 49        | 0x000076            | IFS3<1>  | IEC3<1>       | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event            | 58     | 50        | 0x000078            | IFS3<2>  | IEC3<2>       | IPC12<10:8> |

| Reserved                             | 59-61  | 51-53     | 0x00007A-0x00007E   | _        | _             | _           |

| INT4 – External Interrupt 4          | 62     | 54        | 0x000080            | IFS3<6>  | IEC3<6>       | IPC13<10:8> |

| Reserved                             | 63-64  | 55-54     | 0x000082-0x000084   | —        |               | _           |

| PSEM – PWM Special Event Match       | 65     | 57        | 0x000086            | IFS3<9>  | IEC3<9>       | IPC14<6:4>  |

| Reserved                             | 66-72  | 58-64     | 0x000088-0x000094   | —        |               | _           |

| U1E – UART1 Error Interrupt          | 73     | 65        | 0x000096            | IFS4<1>  | IEC4<1>       | IPC16<6:4>  |

| U2E – UART2 Error Interrupt          | 74     | 66        | 0x000098            | IFS4<2>  | IEC4<2>       | IPC16<10:8> |

| Reserved                             | 75-80  | 67-72     | 0x00009A-0x0000A4   | —        |               | _           |

## REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

bit 4-0

**PLLPRE<4:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler) 11111 = Input divided by 33

•

00001 = Input divided by 3

00000 = Input divided by 2 (default)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- **2:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0          | U-0           | U-0              | U-0              | U-0               | U-0              | U-0                | R/W-0   |  |

|--------------|---------------|------------------|------------------|-------------------|------------------|--------------------|---------|--|

| _            | —             | _                | —                | —                 | —                | _                  | PLLDIV8 |  |

| bit 15       |               |                  |                  |                   |                  |                    | bit 8   |  |

|              |               |                  |                  |                   |                  |                    |         |  |

| R/W-0        | R/W-0         | R/W-1            | R/W-1            | R/W-0             | R/W-0            | R/W-0              | R/W-0   |  |

|              |               |                  | PLLDI            | V<7:0>            |                  |                    |         |  |

| bit 7        |               |                  |                  |                   |                  |                    | bit 0   |  |

|              |               |                  |                  |                   |                  |                    |         |  |

| Legend:      |               |                  |                  |                   |                  |                    |         |  |

| R = Reada    | ble bit       | W = Writable     | bit              | U = Unimplen      | nented bit, read | d as '0'           |         |  |

| -n = Value a | at POR        | '1' = Bit is set |                  | '0' = Bit is clea | ared             | x = Bit is unknown |         |  |

|              |               |                  |                  |                   |                  |                    |         |  |

| bit 15-9     | Unimplemen    | ted: Read as '   | )'               |                   |                  |                    |         |  |

| bit 8-0      | PLLDIV<8:0>   | -: PLL Feedbac   | k Divisor bits ( | also denoted a    | is 'M', PLL mul  | tiplier)           |         |  |

|              | 111111111     | = 513            |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | 000110000=    | = 50 (default)   |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | • 000000010 = | = 4              |                  |                   |                  |                    |         |  |

|              | 00000010-     | <b>– –</b>       |                  |                   |                  |                    |         |  |

## REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

000000001 = 3 000000000 = 2

| U-0          | U-0                                      | U-0              | U-0            | U-0                                     | R/W-0 | U-0    | U-0   |  |

|--------------|------------------------------------------|------------------|----------------|-----------------------------------------|-------|--------|-------|--|

| _            | —                                        | —                | —              | —                                       | CMPMD | —      | _     |  |

| bit 15       | bit 15                                   |                  |                |                                         |       |        | bit 8 |  |

|              |                                          |                  |                |                                         |       |        |       |  |

| U-0          | U-0                                      | U-0              | U-0            | U-0                                     | U-0   | R/W-0  | U-0   |  |

| _            | _                                        | —                | —              | _                                       | —     | I2C2MD | —     |  |

| bit 7        |                                          |                  |                |                                         |       |        | bit 0 |  |

|              |                                          |                  |                |                                         |       |        |       |  |

| Legend:      |                                          |                  |                |                                         |       |        |       |  |

| R = Readab   | ole bit                                  | W = Writable     | bit            | U = Unimplemented bit, read as '0'      |       |        |       |  |

| -n = Value a | at POR                                   | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |       |        | own   |  |

|              |                                          |                  |                |                                         |       |        |       |  |

| bit 15-11    | Unimplement                              | ted: Read as '   | כ'             |                                         |       |        |       |  |

| bit 10       | CMPMD: Con                               | nparator Modul   | le Disable bit |                                         |       |        |       |  |

|              | 1 = Comparat                             | or module is di  | sabled         |                                         |       |        |       |  |

|              | 0 = Comparat                             | or module is ei  | nabled         |                                         |       |        |       |  |

| bit 9-2      | Unimplement                              | ted: Read as '   | כי             |                                         |       |        |       |  |

| bit 1        | 1 <b>I2C2MD:</b> I2C2 Module Disable bit |                  |                |                                         |       |        |       |  |

|              |                                          | ule is disabled  |                |                                         |       |        |       |  |

|              | 0 = I2C2 mod                             | ule is enabled   |                |                                         |       |        |       |  |

#### REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 0 | Unimplemented: Read as '0' |

|-------|----------------------------|

|       |                            |

## REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0  | U-0  | U-0 | U-0  | U-0  | U-0   |

|--------|-----|------|------|-----|------|------|-------|

| —      | —   | —    | —    | —   | —    | —    | —     |

| bit 15 |     |      |      |     |      |      | bit 8 |

|        |     |      |      |     |      |      |       |

| 11.0   |     | 11.0 | 11.0 |     | 11.0 | 11.0 | 11.0  |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                        |

|----------|---------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit |

|          | 1 = Reference clock module is disabled            |

|          | 0 = Reference clock module is enabled             |

| bit 2-0  | Unimplemented: Read as '0'                        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP37R5 | RP37R4 | RP37R3 | RP37R2 | RP37R1 | RP37R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      |     | RP36R5 | RP36R4 | RP36R3 | RP36R2 | RP36R1 | RP36R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-23: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0             | U-0                                                         | R/W-0        | R/W-0  | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |

|-----------------|-------------------------------------------------------------|--------------|--------|------------------------------------|--------|--------|--------|

| —               | —                                                           | RP39R5       | RP39R4 | RP39R3                             | RP39R2 | RP39R1 | RP39R0 |

| bit 15          |                                                             |              |        |                                    |        |        | bit 8  |

|                 |                                                             |              |        |                                    |        |        |        |

| U-0             | U-0                                                         | R/W-0        | R/W-0  | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |

| —               | —                                                           | RP38R5       | RP38R4 | RP38R3                             | RP38R2 | RP38R1 | RP38R0 |

| bit 7           |                                                             |              |        |                                    |        |        | bit 0  |

|                 |                                                             |              |        |                                    |        |        |        |

| Legend:         |                                                             |              |        |                                    |        |        |        |

| R = Readable    | bit                                                         | W = Writable | bit    | U = Unimplemented bit, read as '0' |        |        |        |

| -n = Value at P | OR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |              |        | nown                               |        |        |        |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP39R<5:0>:** Peripheral Output Function is Assigned to RP39 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP38R<5:0>:** Peripheral Output Function is Assigned to RP38 Output Pin bits (see Table 10-2 for peripheral function numbers)

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP45R5 | RP45R4 | RP45R3 | RP45R2 | RP45R1 | RP45R0 |

| bit 15 | ·   |        | •      |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| _      |     | RP44R5 | RP44R4 | RP44R3 | RP44R2 | RP44R1 | RP44R0 |

| bit 0 |

|-------|

|-------|

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP45R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP45 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP44R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP44 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-27: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | RP47R5 | RP47R4 | RP47R3 | RP47R2 | RP47R1 | RP47R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP46R5 | RP46R4 | RP46R3 | RP46R2 | RP46R1 | RP46R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

|         |     |        |        |        |        |        |        |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 13-8 **RP47R<5:0>:** Peripheral Output Function is Assigned to RP47 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP46R<5:0>:** Peripheral Output Function is Assigned to RP46 Output Pin bits (see Table 10-2 for peripheral function numbers)

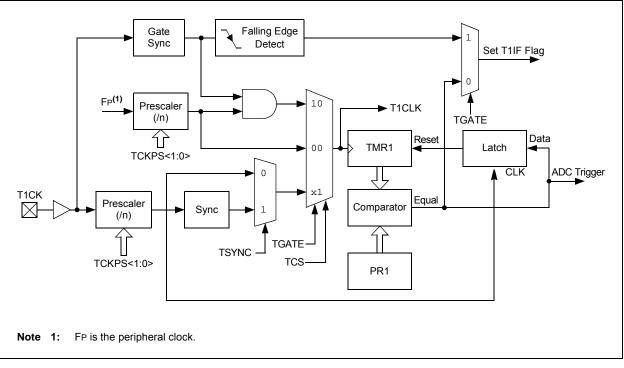

# 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be Operated in Asynchronous Counter mode from an External Clock Source

- The External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the Prescaler

- A block diagram of Timer1 is shown in Figure 11-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit settings for different operating modes are provided in Table 11-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|--|

| Timer                   | 0   | 0     | х     |  |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |  |

| Synchronous<br>Counter  | 1   | x     | 1     |  |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |  |

# TABLE 11-1: TIMER MODE SETTINGS

## **REGISTER 15-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)**

bit 3-0 SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits<sup>(1)</sup> 1111 = 1:16 Postscaler generates a Special Event Trigger on every sixteenth compare match event . . 0001 = 1:2 Postscaler generates a Special Event Trigger on every second compare match event 0000 = 1:1 Postscaler generates a Special Event Trigger on every compare match event

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

#### REGISTER 15-2: PTCON2: PWMx CLOCK DIVIDER SELECT REGISTER 2

| U-0           | U-0   | U-0              | U-0 | U-0                                     | U-0                         | U-0   | U-0   |

|---------------|-------|------------------|-----|-----------------------------------------|-----------------------------|-------|-------|

|               | —     | —                | —   | —                                       | —                           | —     | —     |

| bit 15        |       |                  |     |                                         |                             |       | bit 8 |

|               |       |                  |     |                                         |                             |       |       |

| U-0           | U-0   | U-0              | U-0 | U-0                                     | R/W-0                       | R/W-0 | R/W-0 |

| —             | —     | —                | —   | —                                       | PCLKDIV<2:0> <sup>(1)</sup> |       |       |

| bit 7         |       |                  |     |                                         |                             |       | bit 0 |

|               |       |                  |     |                                         |                             |       |       |

| Legend:       |       |                  |     |                                         |                             |       |       |

| R = Readable  | e bit | W = Writable b   | oit | U = Unimplemented bit, read as '0'      |                             |       |       |

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                             |       | nown  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

111 = Reserved

- 110 = Divide-by-64, maximum PWM timing resolution

- 101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# 20.0 HIGH-SPEED ANALOG COMPARATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed Analog Comparator Module" (DS70005128) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The high-speed analog comparator module monitors current and/or voltage transients that may be too fast for the CPU and ADC to capture.

# 20.1 Features Overview

The SMPS comparator module offers the following major features:

- Four Rail-to-Rail Analog Comparators

- Dedicated 12-Bit DAC for each Analog Comparator

- Up to Six Selectable Input Sources per Comparator:

- Four external inputs

- Two internal inputs from the PGAx module

- Programmable Comparator Hysteresis

- Programmable Output Polarity

- Up to Two DAC Outputs to Device Pins

- Multiple Voltage References for the DAC:

External References (EXTREF1 or

- EXTREF2) - AVDD

- Interrupt Generation Capability

- Functional Support for PWMx:

- PWMx duty cycle control

- PWMx period control

- PWMx Fault detected

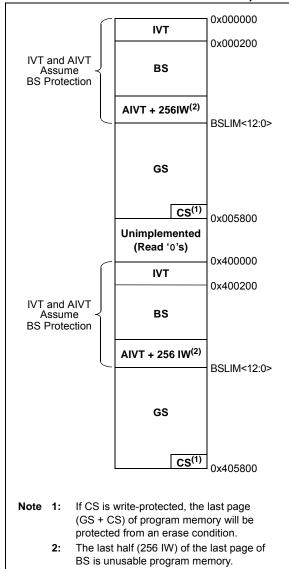

The different device security segments are shown in Figure 23-3. Here, all three segments are shown but are not required. If only basic code protection is required, then GS can be enabled independently or combined with CS, if desired.

| FIGURE 23-3:                            | SECURITY SI<br>EXAMPLE FC<br>dsPIC33EP64<br>DEVICES          | DR          |

|-----------------------------------------|--------------------------------------------------------------|-------------|

|                                         |                                                              | -0x000000   |

|                                         | IVT                                                          | 0x000200    |

| IVT and AIVT<br>Assume<br>BS Protection | BS                                                           |             |

|                                         | AIVT + 256 IW <sup>(2)</sup>                                 |             |

|                                         | GS                                                           | BSLIM<12:0> |

|                                         | CS <sup>(1)</sup>                                            | 0x00B000    |

| + CS) of                                | write-protected, the<br>program memory w<br>erase condition. |             |

|                                         | half (256 IW) of the usable program me                       | 1 0         |

dsPIC33EP64GS50X family devices can be operated in Dual Partition mode, where security is required for each partition. When operating in Dual Partition mode, the Active and Inactive Partitions both contain unique copies of the Reset vector, Interrupt Vector Tables (IVT and AIVT, if enabled) and the Flash Configuration Words. Both partitions have the three security segments described previously. Code may not be executed from the Inactive Partition, but it may be programmed by, and read from, the Active Partition, subject to defined code protection. Figure 23-4 shows the different security segments for a device operating in Dual Partition mode.

The device may also operate in a Protected Dual Partition mode or in Privileged Dual Partition mode. In Protected Dual Partition mode, Partition 1 is permanently erase/write-protected. This implementation allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1. For example, a fail-safe bootloader can be placed in Partition 1, along with a fail-safe backup code image, which can be used or rewritten into Partition 2 in the event of a failed Flash update to Partition 2.

Privileged Dual Partition mode performs the same function as Protected Dual Partition mode, except additional constraints are applied in an effort to prevent code in the Boot Segment and General Segment from being used against each other.

SECURITY SEGMENTS EXAMPLE FOR dsPIC33EP64GS50X DEVICES (DUAL PARTITION MODES)

# 26.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33EPXXGS50X family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXGS50X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                | 40°C to +125°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                            | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 3.0V^{(3)}$  | -0.3V to +5.5V       |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(3)}$    | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                   |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                |                      |

| Maximum current sunk by all ports <sup>(2)</sup>                              | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those, or any other conditions above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 26-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

# TABLE 26-23:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHARACTERISTICS |                                                                       |                                                                |            | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |    |                                                                                                             |  |  |

|--------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|-------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol Characteristic <sup>(1)</sup> Min Tyn <sup>(2)</sup> Max Units |                                                                | Conditions |                                                                                                                                                                                                                                                                                         |      |    |                                                                                                             |  |  |

| SY00               | Tpu                                                                   | Power-up Period                                                | _          | 400                                                                                                                                                                                                                                                                                     | 600  | μS |                                                                                                             |  |  |

| SY10               | Тоѕт                                                                  | Oscillator Start-up Time                                       | —          | 1024 Tosc                                                                                                                                                                                                                                                                               | _    | —  | Tosc = OSC1 period                                                                                          |  |  |

| SY12               | Twdt                                                                  | Watchdog Timer<br>Time-out Period                              | 0.81       | _                                                                                                                                                                                                                                                                                       | 1.22 | ms | WDTPRE = 0,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21 (see Table 26-21) at +85°C |  |  |

|                    |                                                                       |                                                                | 3.25       | _                                                                                                                                                                                                                                                                                       | 4.88 | ms | WDTPRE = 1,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21 (see Table 26-21) at +85°C |  |  |

| SY13               | Tioz                                                                  | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68       | 0.72                                                                                                                                                                                                                                                                                    | 1.2  | μS |                                                                                                             |  |  |

| SY20               | TMCLR                                                                 | MCLR Pulse Width (low)                                         | 2          | _                                                                                                                                                                                                                                                                                       |      | μS |                                                                                                             |  |  |

| SY30               | TBOR                                                                  | BOR Pulse Width (low)                                          | 1          |                                                                                                                                                                                                                                                                                         |      | μS |                                                                                                             |  |  |

| SY35               | TFSCM                                                                 | Fail-Safe Clock Monitor<br>Delay                               | _          | 500                                                                                                                                                                                                                                                                                     | 900  | μS | -40°C to +85°C                                                                                              |  |  |

| SY36               | Tvreg                                                                 | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time | —          | _                                                                                                                                                                                                                                                                                       | 30   | μS |                                                                                                             |  |  |

| SY37               | Toscdfrc                                                              | FRC Oscillator Start-up<br>Delay                               | _          | 48                                                                                                                                                                                                                                                                                      | _    | μS |                                                                                                             |  |  |

| SY38               | TOSCDLPRC                                                             | LPRC Oscillator Start-up<br>Delay                              | —          | —                                                                                                                                                                                                                                                                                       | 70   | μS |                                                                                                             |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

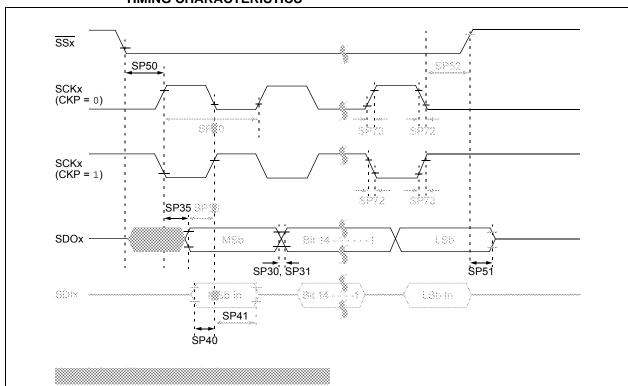

### FIGURE 26-18: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| AC/DC CHARACTERISTICS <sup>(1)</sup> |        |                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |             |            |            |                                                                |

|--------------------------------------|--------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|------------|----------------------------------------------------------------|

| Param<br>No.                         | Symbol | Characteris                                    | tic                                                                                                                                                                                                                                                                                     | Min.       | Тур.        | Max.       | Units      | Comments                                                       |

| PA01                                 | Vin    | Input Voltage Rang                             | е                                                                                                                                                                                                                                                                                       | AVss - 0.3 | _           | AVDD + 0.3 | V          |                                                                |

| PA02                                 | Vсм    | Common-Mode Inp<br>Voltage Range               | ut                                                                                                                                                                                                                                                                                      | AVss       | —           | AVDD - 1.6 | V          |                                                                |

| PA03                                 | Vos    | Input Offset Voltage                           | ;                                                                                                                                                                                                                                                                                       | -10        | _           | 10         | mV         |                                                                |

| PA04                                 | Vos    | Input Offset Voltage Drift<br>with Temperature |                                                                                                                                                                                                                                                                                         | —          | ±15         | —          | µV/∘C      |                                                                |

| PA05                                 | Rin+   | Input Impedance of<br>Positive Input           |                                                                                                                                                                                                                                                                                         | —          | >1M    7 pF | —          | Ω   pF     |                                                                |

| PA06                                 | Rin-   | Input Impedance of<br>Negative Input           |                                                                                                                                                                                                                                                                                         | —          | 10K    7 pF | —          | Ω   pF     |                                                                |

| PA07                                 |        | Gain Error                                     |                                                                                                                                                                                                                                                                                         | -2         | _           | 2          | %          | Gain = 4x, 8x                                                  |

|                                      |        |                                                | -3                                                                                                                                                                                                                                                                                      | —          | 3           | %          | Gain = 16x |                                                                |

|                                      |        |                                                |                                                                                                                                                                                                                                                                                         | -4         |             | 4          | %          | Gain = 32x, 64x                                                |

| PA08                                 | Lerr   | Gain Nonlinearity Error                        |                                                                                                                                                                                                                                                                                         | —          | —           | 0.5        | %          | % of full scale,<br>Gain = 16x                                 |

| PA09                                 | IDD    | Current Consumption                            | on                                                                                                                                                                                                                                                                                      | _          | 2.0         | —          | mA         | Module is enabled with<br>a 2-volt P-P output<br>voltage swing |

| PA10a                                | BW     | Small Signal                                   | G = 4x                                                                                                                                                                                                                                                                                  | _          | 10          | —          | MHz        |                                                                |

| PA10b                                |        | Bandwidth (-3 dB)                              | G = 8x                                                                                                                                                                                                                                                                                  | _          | 5           | —          | MHz        |                                                                |

| PA10c                                |        |                                                | G = 16x                                                                                                                                                                                                                                                                                 | —          | 2.5         | —          | MHz        |                                                                |

| PA10d                                |        |                                                | G = 32x                                                                                                                                                                                                                                                                                 | _          | 1.25        | —          | MHz        |                                                                |