Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs502t-e-2n |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

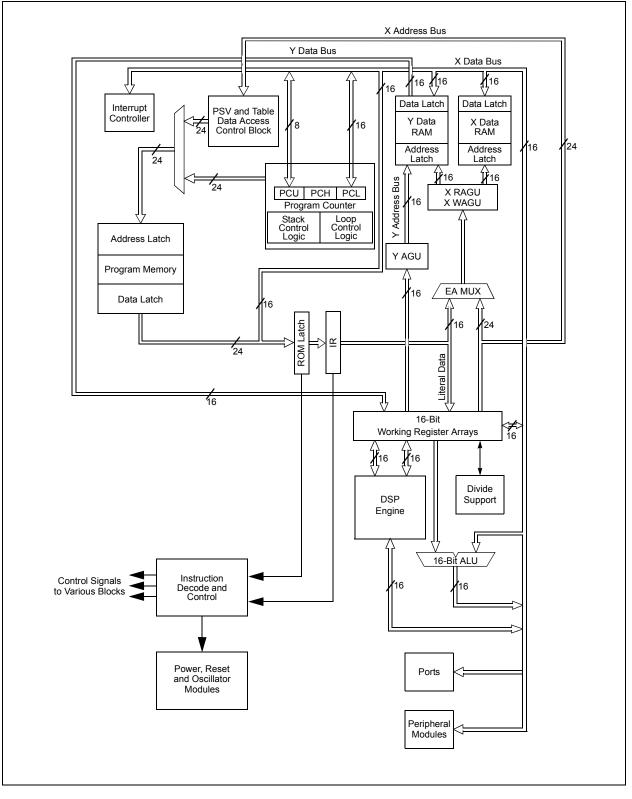

### FIGURE 3-1: dsPIC33EPXXGS50X FAMILY CPU BLOCK DIAGRAM

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP64GS50X DEVICES (DUAL PARTITION) 0x000000 GOTO Instruction 0x000002 Reset Address 0x000004 Interrupt Vector Table 0x0001FE 0x000200 Active Program Flash Memory (10,944 instructions) **Active Partition** 0x00577E 0x005780 **Device Configuration** 0x0057FE 0x005800 User Memory Space Unimplemented (Read '0's) 0x3FFFFE 0x400000 GOTO Instruction 0x400002 Reset Address 0x400004 Interrupt Vector Table 0x4001FE 0x400200 **Inactive Partition** Inactive Program Flash Memory (10,944 instructions) 0x40577E 0x405780 **Device Configuration** 0x4057FE 0x405800 Unimplemented (Read '0's) 0x7FFFFE 0x800000 Reserved 0x800E46 0x800E48 Calibration Data 0x800E78 0x800E7A Reserved 0x800EFE Configuration Memory Space 0x800F00 UDID 0x800F08 0x800F0A Reserved 0x800F7E 0x800F80 User OTP Memory 0x800FFC 0x801000 Reserved 0xF9FFFE 0xFA0000 Write Latches 0xFA0002 0xFA0004 Reserved **0xFEFFFE** 0xFF0000 DEVID 0xFF0002 0xFF0004 Reserved 0xFFFFFE Note: Memory areas are not shown to scale.

### TABLE 4-16: ADC REGISTER MAP (CONTINUED)

| SFR<br>Name | Addr. | Bit 15                 | Bit 14                | Bit 13                 | Bit 12                 | Bit 11                  | Bit 10                 | Bit 9                  | Bit 8                  | Bit 7       | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1                  | Bit 0                   | All<br>Resets |

|-------------|-------|------------------------|-----------------------|------------------------|------------------------|-------------------------|------------------------|------------------------|------------------------|-------------|---------|----------|----------|----------|----------|------------------------|-------------------------|---------------|

| ADLVLTRGL   | 03D0  | LVLEN15 <sup>(1)</sup> | LVLEN14               | LVLEN13 <sup>(1)</sup> | LVLEN12 <sup>(2)</sup> | LVLEN11 <sup>(2)</sup>  | LVLEN10 <sup>(2)</sup> | LVLEN9 <sup>(2)</sup>  | LVLEN8 <sup>(2)</sup>  | LVLEN7      | LVLEN6  | LVLEN5   | LVLEN4   | LVLEN3   | LVLEN2   | LVLEN1                 | LVLEN0                  | 0000          |

| ADLVLTRGH   | 03D2  | _                      |                       | -                      | _                      | _                       |                        | _                      | _                      | -           |         | LVLEN21  | LVLEN20  | LVLEN19  | LVLEN18  | LVLEN17 <sup>(2)</sup> | LVLEN16 <sup>(1)</sup>  | 0000          |

| ADCORE0L    | 03D4  | —                      |                       | _                      | _                      | _                       |                        |                        |                        |             |         | SAMO     | C<9:0>   |          |          |                        |                         | 0000          |

| ADCORE0H    | 03D6  | -                      | -                     | -                      | EISEL2                 | EISEL1                  | EISEL0                 | RES1                   | RES0                   | -           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                  | ADCS0                   | 0000          |

| ADCORE1L    | 03D8  | _                      |                       | -                      | _                      | _                       |                        |                        |                        |             |         | SAMO     | C<9:0>   |          |          |                        |                         | 0000          |

| ADCORE1H    | 03DA  | —                      |                       | _                      | EISEL2                 | EISEL1                  | EISEL0                 | RES1                   | RES0                   | _           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                  | ADCS0                   | 0000          |

| ADCORE2L    | 03DC  | -                      | -                     | -                      | _                      | -                       | _                      |                        |                        |             | _       | SAMO     | C<9:0>   |          |          |                        |                         | 0000          |

| ADCORE2H    | 03DE  | _                      |                       | -                      | EISEL2                 | EISEL1                  | EISEL0                 | RES1                   | RES0                   | -           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                  | ADCS0                   | 0000          |

| ADCORE3L    | 03E0  | —                      |                       | _                      | _                      | _                       |                        |                        |                        |             |         | SAMO     | C<9:0>   |          |          |                        |                         | 0000          |

| ADCORE3H    | 03E2  | -                      | -                     | -                      | EISEL2                 | EISEL1                  | EISEL0                 | RES1                   | RES0                   | -           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                  | ADCS0                   | 0000          |

| ADEIEL      | 03F0  | EIEN15 <sup>(1)</sup>  | EIEN14 <sup>(2)</sup> | EIEN13 <sup>(1)</sup>  | EIEN12 <sup>(2)</sup>  | EIEN11 <sup>(2)</sup>   | EIEN10 <sup>(2)</sup>  | EIEN9 <sup>(2)</sup>   | EIEN8 <sup>(2)</sup>   | EIEN7       | EIEN6   | EIEN5    | EIEN4    | EIEN3    | EIEN2    | EIEN1                  | EIEN0                   | 0000          |

| ADEIEH      | 03F2  | _                      | _                     | _                      | _                      | _                       | _                      | _                      | _                      | _           | _       | EIEN21   | EIEN20   | EIEN19   | EIEN18   | EIEN17 <sup>(2)</sup>  | EIEN16 <sup>(1)</sup>   | 0000          |

| ADEISTATL   | 03F8  | EISTAT15(1)            | EISTAT14(2)           | EISTAT13(1)            | EISTAT12(2)            | EISTAT11 <sup>(2)</sup> | EISTAT10(2)            | EISTAT9 <sup>(2)</sup> | EISTAT8 <sup>(2)</sup> | EISTAT7     | EISTAT6 | EISTAT5  | EISTAT4  | EISTAT3  | EISTAT2  | EISTAT1                | EISTAT0                 | 0000          |

| ADEISTATH   | 03FA  | _                      | _                     | _                      | _                      | _                       | _                      | _                      | _                      | _           | _       | EISTAT21 | EISTAT20 | EISTAT19 | EISTAT18 | EISTAT17(2)            | EISTAT16 <sup>(1)</sup> | 0000          |

| ADCON5L     | 0400  | SHRRDY                 | _                     | -                      | _                      | C3RDY                   | C2RDY                  | C1RDY                  | CORDY                  | SHRPWR      | _       | -        | -        | C3PWR    | C2PWR    | C1PWR                  | C0PWR                   | 0000          |

| ADCON5H     | 0402  | _                      | _                     | _                      | _                      | WARMTIME3               | WARMTIME2              | WARMTIME1              | WARMTIME0              | SHRCIE      | _       | _        | _        | C3CIE    | C2CIE    | C1CIE                  | C0CIE                   | 0000          |

| ADCALOL     | 0404  | CAL1RDY                | _                     | _                      | _                      | _                       | CAL1DIFF               | CAL1EN                 | CAL1RUN                | CALORDY     | _       | _        | _        | _        | CAL0DIFF | CAL0EN                 | CALORUN                 | 0000          |

| ADCAL0H     | 0406  | CAL3RDY                | _                     | _                      | _                      | _                       | CAL3DIFF               | CAL3EN                 | CAL3RUN                | CAL2RDY     | _       | _        | _        | _        | CAL2DIFF | CAL2EN                 | CAL2RUN                 | 0000          |

| ADCAL1H     | 040A  | CSHRRDY                | -                     | _                      | _                      | _                       | CSHRDIFF               | CSHREN                 | CSHRRUN                | —           | -       | _        | —        | _        | _        | _                      | —                       | 0000          |

| ADCBUF0     | 040C  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 0 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF1     | 040E  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 1 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF2     | 0410  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 2 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF3     | 0412  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 3 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF4     | 0414  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 4 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF5     | 0416  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 5 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF6     | 041B  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 6 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF7     | 041A  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 7 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF8     | 041C  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 8 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF9     | 041E  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 9 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF10    | 0420  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 10 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF11    | 0422  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 11 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF12    | 0424  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 12 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF13    | 0426  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 13 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF14    | 0428  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 14 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF15    | 042A  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 15 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF16    | 042C  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 16 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF17    | 042E  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 17 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF18    | 0430  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 18 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF19    | 0432  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 19 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF20    | 0434  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 20 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF21    | 0436  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 21 |         |          |          |          |          |                        |                         | 0000          |

dsPIC33EPXXGS50X FAMILY

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

Implemented on dsPIC33EPXXGS506 devices only.

Implemented on dsPIC33EPXXGS504/505 and dsPIC33EPXXGS506 devices only.

### TABLE 4-26: ANALOG COMPARATOR REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9   | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|---------|---------|---------|--------|---------|-------|--------|--------|--------|--------|---------|--------|--------|-------|---------------|

| CMP1CON     | 0540  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP1DAC     | 0542  | _      | —      | —       |         |         |        |         |       |        | CMREF  | <11:0> |        |         |        |        |       | 0000          |

| CMP2CON     | 0544  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP2DAC     | 0546  | -      | —      | _       | -       |         |        |         |       |        | CMREF  | <11:0> |        |         |        |        |       | 0000          |

| CMP3CON     | 0548  | CMPON  | _      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP3DAC     | 054A  | -      | _      | _       | _       |         |        |         |       |        | CMREF  | <11:0> |        |         |        |        |       | 0000          |

| CMP4CON     | 054C  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP4DAC     | 054E  | —      | —      | _       | _       |         |        |         |       |        | CMREF  | <11:0> |        |         |        |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-27: JTAG INTERFACE REGISTER MAP

| SFR<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|------|--------|--------|--------|--------|--------|--------|-------|-------|---------|-------|---------|-------|-------|-------|-------|-------|---------------|

| JDATAH      | 0FF0 | _      | _      | _      | —      |        |        |       |       |         | JDATA | H<11:0> |       |       |       |       |       | xxxx          |

| JDATAL      | 0FF2 |        |        |        |        |        |        |       | JDATA | L<15:0> |       |         |       |       |       |       |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-33: PORTA REGISTER MAP FOR dsPIC33EPXXGS506 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|------------|-------|------------|-----------|-------|---------------|

| TRISA       | 0E00  | _      |        | _      |        | _      |        |       |       | _     | _     | _     |            |       | TRISA<4:0> | •         |       | 001F          |

| PORTA       | 0E02  | _      |        | —      |        | —      |        |       |       |       | —     | —     |            |       | RA<4:0>    |           |       | 0000          |

| LATA        | 0E04  | _      |        | —      |        | —      |        |       |       |       | —     | —     |            |       | LATA<4:0>  |           |       | 0000          |

| ODCA        | 0E06  | _      |        | —      |        | —      |        |       |       |       | —     | —     |            |       | ODCA<4:0>  | •         |       | 0000          |

| CNENA       | 0E08  | _      |        | —      |        | —      |        |       |       |       | —     | —     |            | (     | CNIEA<4:0  | >         |       | 0000          |

| CNPUA       | 0E0A  | _      |        | —      |        | —      |        |       |       |       | —     | —     |            | C     | CNPUA<4:0  | >         |       | 0000          |

| CNPDA       | 0E0C  | _      |        | —      |        | —      |        |       |       |       | —     | —     | CNPDA<4:0> |       |            |           | 0000  |               |

| ANSELA      | 0E0E  | _      | _      | _      | -      | _      | -      | -     | -     | _     | —     | _     | _          | —     |            | ANSA<2:0> |       | 0007          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-34: PORTB REGISTER MAP FOR dsPIC33EPXXGS506 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|---------|-------|-----------|-------|-------|-------|-------|--------|-------|---------------|

| TRISB       | 0E10  |        |        |        |        |        |        |        | TRISB<1 | 5:0>  |           |       |       |       |       |        |       | FFFF          |

| PORTB       | 0E12  |        |        |        |        |        |        |        | RB<15   | :0>   |           |       |       |       |       |        |       | xxxx          |

| LATB        | 0E14  |        |        |        |        |        |        |        | LATB<1  | 5:0>  |           |       |       |       |       |        |       | xxxx          |

| ODCB        | 0E16  |        |        |        |        |        |        |        | ODCB<1  | 5:0>  |           |       |       |       |       |        |       | 0000          |

| CNENB       | 0E18  |        |        |        |        |        |        |        | CNIEB<1 | 5:0>  |           |       |       |       |       |        |       | 0000          |

| CNPUB       | 0E1A  |        |        |        |        |        |        |        | CNPUB<  | 15:0> |           |       |       |       |       |        |       | 0000          |

| CNPDB       | 0E1C  |        |        |        |        |        |        |        | CNPDB<  | 15:0> |           |       |       |       |       |        |       | 0000          |

| ANSELB      | 0E1E  |        | _      | —      | —      | —      | ANSB<  | :10:9> | —       |       | ANSB<7:5> | •     | _     |       | ANSE  | 3<3:0> |       | 06EF          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-35: PORTC REGISTER MAP FOR dsPIC33EPXXGS506 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|---------|-------|-------|-----------|-------|-------|-------|-----------|-------|---------------|

| TRISC       | 0E20  |        |        |        |        |        |        |       | TRISC<1 | 5:0>  |       |           |       |       |       |           |       | FFFF          |

| PORTC       | 0E22  |        |        |        |        |        |        |       | RC<15   | :0>   |       |           |       |       |       |           |       | xxxx          |

| LATC        | 0E24  |        |        |        |        |        |        |       | LATC<1  | 5:0>  |       |           |       |       |       |           |       | xxxx          |

| ODCC        | 0E26  |        |        |        |        |        |        |       | ODCC<1  | 5:0>  |       |           |       |       |       |           |       | 0000          |

| CNENC       | 0E28  |        |        |        |        |        |        |       | CNIEC<1 | 5:0>  |       |           |       |       |       |           |       | 0000          |

| CNPUC       | 0E2A  |        |        |        |        |        |        |       | CNPUC<  | 15:0> |       |           |       |       |       |           |       | 0000          |

| CNPDC       | 0E2C  |        |        |        |        |        |        |       | CNPDC<  | 15:0> |       |           |       |       |       |           |       | 0000          |

| ANSELC      | 0E2E  | _      | _      | —      |        | ANSC<  | :12:9> |       | _       | —     |       | ANSC<6:4> |       | —     | /     | ANSC<2:0> |       | 1E77          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

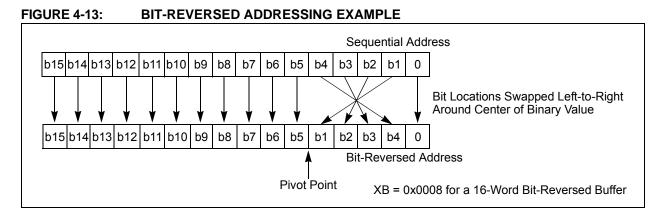

### TABLE 4-39: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| Reserved         Reserved         cillator Fail Trap Vector         dress Error Trap Vector         eneric Hard Trap Vector         tack Error Trap Vector         Math Error Trap Vector         Reserved         eneric Soft Trap Vector 0         Interrupt Vector 1         :         :         Interrupt Vector 52         Interrupt Vector 53         Interrupt Vector 54 | $\begin{array}{c} \text{BSLIM}{(12:0)}^{(1)} + 0x000000\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000002\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000004\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000006\\ \text{BSLIM}{(12:0)}^{(1)} + 0x00000A\\ \text{BSLIM}{(12:0)}^{(1)} + 0x00000C\\ \text{BSLIM}{(12:0)}^{(1)} + 0x00000C\\ \text{BSLIM}{(12:0)}^{(1)} + 0x00000C\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000010\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000012\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000014\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000016\\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | See Table 7-1 for        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| cillator Fail Trap Vector<br>dress Error Trap Vector<br>eneric Hard Trap Vector<br>tack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                      | BSLIM<12:0>(1) + 0x000004<br>BSLIM<12:0>(1) + 0x000006<br>BSLIM<12:0>(1) + 0x000008<br>BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br><br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                 | See Table 7-1 for        |

| dress Error Trap Vector<br>eneric Hard Trap Vector<br>tack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                   | BSLIM<12:0>(1) + 0x000006<br>BSLIM<12:0>(1) + 0x000008<br>BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br><br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                                              | See Table 7-1 for        |

| eneric Hard Trap Vector<br>tack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                              | BSLIM<12:0>(1) + 0x000008<br>BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br><br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C                                                                                                                                                                                                                                                                        | See Table 7-1 for        |

| tack Error Trap Vector<br>Nath Error Trap Vector<br>Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                                         | BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br>:<br>:<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C                                                                                                                                                                                                                                                                                               | See Table 7-1 for        |

| Math Error Trap Vector         Reserved         eneric Soft Trap Vector         Reserved         Interrupt Vector 0         Interrupt Vector 1         Interrupt Vector 52         Interrupt Vector 53                                                                                                                                                                          | BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br>:<br>:<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                                                                                                                                                            | See Table 7-1 for        |

| Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                                                                                             | BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br><br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                                                                                                                                                                                               | See Table 7-1 for        |

| eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                                                                                                         | BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br>:<br>:<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                      | See Table 7-1 for        |

| Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>                                                                                                                                                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000012<br>BSLIM<12:0> <sup>(1)</sup> + 0x000014<br>BSLIM<12:0> <sup>(1)</sup> + 0x000016<br>:<br>:<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                       | See Table 7-1 for        |

| Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                                                                                                                                                | BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br>:<br>:<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C                                                                                                                                                                                                                                                                                                                                                                                                                                                | See Table 7-1 for        |

| Interrupt Vector 1                                                                                                                                                                                                                                                                                                                                                              | BSLIM<12:0> <sup>(1)</sup> + 0x000016<br>:<br>:<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                         | See Table 7-1 for        |

| Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                                                                                                                                                                                                      | :<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | See Table 7-1 for        |

| Interrupt Vector 53                                                                                                                                                                                                                                                                                                                                                             | BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

| Interrupt Vector 53                                                                                                                                                                                                                                                                                                                                                             | BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

| Interrupt Vector 53                                                                                                                                                                                                                                                                                                                                                             | BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

| Interrupt Vector 53                                                                                                                                                                                                                                                                                                                                                             | BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | See Table 7-1 for        |

| Interrupt Vector 54                                                                                                                                                                                                                                                                                                                                                             | BSLIM<12:0> <sup>(1)</sup> + 0x000080                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

| -                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

| :                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interrupt Vector Details |

| :                                                                                                                                                                                                                                                                                                                                                                               | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| :                                                                                                                                                                                                                                                                                                                                                                               | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| Interrupt Vector 116                                                                                                                                                                                                                                                                                                                                                            | BSLIM<12:0> <sup>(1)</sup> + 0x0000FC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 117                                                                                                                                                                                                                                                                                                                                                            | BSLIM<12:0> <sup>(1)</sup> + 0x0000FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 118                                                                                                                                                                                                                                                                                                                                                            | BSLIM<12:0> <sup>(1)</sup> + 0x000100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 119                                                                                                                                                                                                                                                                                                                                                            | BSLIM<12:0> <sup>(1)</sup> + 0x000102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 120                                                                                                                                                                                                                                                                                                                                                            | BSLIM<12:0> <sup>(1)</sup> + 0x000104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| :                                                                                                                                                                                                                                                                                                                                                                               | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| :                                                                                                                                                                                                                                                                                                                                                                               | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| :                                                                                                                                                                                                                                                                                                                                                                               | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| Interrupt Vector 244                                                                                                                                                                                                                                                                                                                                                            | BSLIM<12:0> <sup>(1)</sup> + 0x0001FC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 245                                                                                                                                                                                                                                                                                                                                                            | BSLIM<12:0> <sup>(1)</sup> + 0x0001FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | y BSLIM<12:0>.           |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

### TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-n (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16                       | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### 8.2 Auxiliary Clock Generation

The auxiliary clock generation is used for peripherals that need to operate at a frequency unrelated to the system clock, such as PWM or ADC.

The primary oscillator and internal FRC oscillator sources can be used with an Auxiliary PLL (APLL) to obtain the auxiliary clock. The Auxiliary PLL has a fixed 16x multiplication factor.

The auxiliary clock has the following configuration restrictions:

- For proper PWM operation, auxiliary clock generation must be configured for 120 MHz (see Parameter OS56 in Section 26.0 "Electrical Characteristics"). If a slower frequency is desired, the PWM Input Clock Prescaler (Divider) Select bits (PCLKDIV<2:0>) should be used.

- To achieve 1.04 ns PWM resolution, the auxiliary clock must use the 16x Auxiliary PLL (APLL). All other clock sources will have a minimum PWM resolution of 8 ns.

- If the primary PLL is used as a source for the auxiliary clock, the primary PLL should be configured up to a maximum operation of 30 MIPS or less.

### 8.3 Reference Clock Generation

The reference clock output logic provides the user with the ability to output a clock signal based on the system clock or the crystal oscillator on a device pin. The user application can specify a wide range of clock scaling prior to outputting the reference clock.

### 8.4 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 8.4.1 KEY RESOURCES

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 8-5: ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER

| R/W-0         | R-0                            | R/W-1                                     | U-0            | U-0               | R/W-1            | R/W-1           | R/W-1     |

|---------------|--------------------------------|-------------------------------------------|----------------|-------------------|------------------|-----------------|-----------|

| ENAPLL        | APLLCK                         | SELACLK                                   | _              | _                 | APSTSCLR2        | APSTSCLR1       | APSTSCLR0 |

| bit 15        | •                              |                                           |                |                   |                  |                 | bit 8     |

|               |                                |                                           |                |                   |                  |                 |           |

| R/W-0         | R/W-0                          | U-0                                       | U-0            | U-0               | U-0              | U-0             | U-0       |

| ASRCSEL       | FRCSEL                         | —                                         | —              | —                 | _                | —               | —         |

| bit 7         |                                |                                           |                |                   |                  |                 | bit 0     |

| Legend:       |                                |                                           |                |                   |                  |                 |           |

| R = Readable  | e bit                          | W = Writable bit                          | ŀ              | U = Unimplen      | nented bit, read | l as '0'        |           |

| -n = Value at |                                | '1' = Bit is set                          | •              | '0' = Bit is clea |                  | x = Bit is unkr | lown      |

|               |                                |                                           |                | 0 21110 0101      |                  |                 |           |

| bit 15        | FNAPLI: AU                     | xiliary PLL Enable                        | e bit          |                   |                  |                 |           |

|               | 1 = APLL is e                  | -                                         |                |                   |                  |                 |           |

|               | 0 = APLL is d                  | lisabled                                  |                |                   |                  |                 |           |

| bit 14        | APLLCK: AP                     | LL Locked Status                          | s bit (read-or | ıly)              |                  |                 |           |

|               |                                | that Auxiliary PLI                        |                |                   |                  |                 |           |

|               |                                | that Auxiliary PLI                        |                |                   |                  |                 |           |

| bit 13        |                                | elect Auxiliary Cl                        |                | -                 |                  |                 |           |

|               |                                | oscillators provide<br>PLL (Fvco) provid  |                |                   |                  |                 |           |

| bit 12-11     | Unimplemen                     | ted: Read as '0'                          |                |                   |                  |                 |           |

| bit 10-8      | APSTSCLR<                      | 2:0>: Auxiliary C                         | lock Output    | Divider bits      |                  |                 |           |

|               | 111 = Divideo                  | d by 1                                    |                |                   |                  |                 |           |

|               | 110 = Divideo                  |                                           |                |                   |                  |                 |           |

|               | 101 = Divideo<br>100 = Divideo |                                           |                |                   |                  |                 |           |

|               | 011 = Divideo                  |                                           |                |                   |                  |                 |           |

|               | 010 = Divideo                  |                                           |                |                   |                  |                 |           |

|               | 001 = Divideo                  |                                           |                |                   |                  |                 |           |

|               | 000 = Divideo                  | •                                         |                |                   |                  |                 |           |

| bit 7         |                                | elect Reference                           |                | e for Auxiliary C | Clock bit        |                 |           |

|               |                                | scillator is the clo<br>input is selected | ock source     |                   |                  |                 |           |

| bit 6         | FRCSEL: Se                     | lect Reference Cl                         | ock Source     | for Auxiliary PL  | L bit            |                 |           |

|               |                                | he FRC clock for a                        |                |                   |                  |                 |           |

|               | 0 = Input cloc                 | k source is deter                         | mined by the   | e ASRCSEL bit     | setting          |                 |           |

|               | •                              | ted: Read as '0'                          | 5              |                   | 0                |                 |           |

### REGISTER 9-7: PMD8: PERIPHERAL MODULE DISABLE CONTROL REGISTER 8

| U-0          | U-0        | U-0               | U-0            | U-0               | R/W-0            | R/W-0            | U-0   |

|--------------|------------|-------------------|----------------|-------------------|------------------|------------------|-------|

| _            | _          | —                 | _              | _                 | PGA2MD           | ABGMD            | _     |

| bit 15       |            |                   |                |                   |                  |                  | bit 8 |

|              |            |                   |                |                   |                  |                  |       |

| U-0          | U-0        | U-0               | U-0            | U-0               | U-0              | R/W-0            | U-0   |

| —            | —          | —                 | —              | _                 | —                | CCSMD            | —     |

| bit 7        |            |                   |                |                   |                  |                  | bit 0 |

|              |            |                   |                |                   |                  |                  |       |

| Legend:      |            |                   |                |                   |                  |                  |       |

| R = Readab   | ole bit    | W = Writable b    | pit            | U = Unimplem      | nented bit, read | 1 as '0'         |       |

| -n = Value a | it POR     | '1' = Bit is set  |                | '0' = Bit is clea | ared             | x = Bit is unkno | own   |

|              |            |                   |                |                   |                  |                  |       |

| bit 15-11    | Unimplemer | nted: Read as '0  | ,              |                   |                  |                  |       |

| bit 10       | PGA2MD: P  | GA2 Module Dis    | able bit       |                   |                  |                  |       |

|              |            | odule is disabled | -              |                   |                  |                  |       |

|              | 0 = PGA2 m | odule is enabled  |                |                   |                  |                  |       |

| bit 9        | ABGMD: Ba  | nd Gap Referen    | ce Voltage Dis | able bit          |                  |                  |       |

|              |            | p reference volta |                |                   |                  |                  |       |

|              |            | p reference volta | -              |                   |                  |                  |       |

| bit 8-2      | Unimplemen | nted: Read as '0  | ,              |                   |                  |                  |       |

| bit 1        | CCSMD: Co  | nstant-Current S  | ource Module   | Disable bit       |                  |                  |       |

|              |            | t-current source  |                |                   |                  |                  |       |

| bit 0        |            |                   |                |                   |                  |                  |       |

| DILU         | Unimpiemer | nted: Read as '0  |                |                   |                  |                  |       |

| R/W-0        | R/W-0                                                          | R/W-0                                                                                       | R/W-0                              | R/W-0            | R/W-0           | R/W-0              | R/W-0  |  |