Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs502t-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

bit 2 SFA: Stack Frame Active Status bit

1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG

0 = Stack frame is not active; W14 and W15 address the base Data Space

bit 1 RND: Rounding Mode Select bit

1 = Biased (conventional) rounding is enabled

0 = Unbiased (convergent) rounding is enabled

IF: Integer or Fractional Multiplier Mode Select bit

1 = Integer mode is enabled for DSP multiply0 = Fractional mode is enabled for DSP multiply

Note 1: This bit is always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 3-3: CTXTSTAT: CPU W REGISTER CONTEXT STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    | R-0    |

|--------|-----|-----|-----|-----|--------|--------|--------|

| _      | _   | _   | _   | _   | CCTXI2 | CCTXI1 | CCTXI0 |

| bit 15 |     |     |     |     |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    | R-0    |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   | _   | _   | _   | MCTXI2 | MCTXI1 | MCTXI0 |

| bit 7 |     |     |     |     |        |        | bit 0  |

Legend:

bit 0

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 CCTXI<2:0>: Current (W Register) Context Identifier bits

111 = Reserved

•

•

011 = Reserved

010 = Alternate Working Register Set 2 is currently in use

001 = Alternate Working Register Set 1 is currently in use

000 = Default register set is currently in use

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 MCTXI<2:0>: Manual (W Register) Context Identifier bits

111 = Reserved

•

•

011 = Reserved

010 = Alternate Working Register Set 2 was most recently manually selected

001 = Alternate Working Register Set 1 was most recently manually selected

000 = Default register set was most recently manually selected

TABLE 4-2: CPU CORE REGISTER MAP (CONTINUED)

| SFR<br>Name | Addr. | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10      | Bit 9       | Bit 8        | Bit 7     | Bit 6   | Bit 5 | Bit 4      | Bit 3      | Bit 2        | Bit 1   | Bit 0  | All<br>Resets |

|-------------|-------|--------|-------------------|--------|--------|--------|-------------|-------------|--------------|-----------|---------|-------|------------|------------|--------------|---------|--------|---------------|

| DOENDL      | 003E  |        |                   |        |        | D      | o Loop End  | Address Re  | egister Low  | (DOENDL<  | :15:1>) |       |            |            |              |         | _      | 0000          |

| DOENDH      | 0040  | _      | _                 | _      | _      | _      | _           | _           | _            | _         | _       | DO Lo | oop End Ad | dress Regi | ster High (I | OOENDH< | 5:0>)  | 0000          |

| SR          | 0042  | OA     | ОВ                | SA     | SB     | OAB    | SAB         | DA          | DC           | IPL2      | IPL1    | IPL0  | RA         | N          | OV           | Z       | С      | 0000          |

| CORCON      | 0044  | VAR    | _                 | US1    | US0    | EDT    | DL2         | DL1         | DL0          | SATA      | SATB    | SATDW | ACCSAT     | IPL3       | SFA          | RND     | IF     | 0020          |

| MODCON      | 0046  | XMODEN | YMODEN            | _      | _      | BWM3   | BWM2        | BWM1        | BWM0         | YWM3      | YWM2    | YWM1  | YWM0       | XWM3       | XWM2         | XWM1    | XWM0   | 0000          |

| XMODSRT     | 0048  |        |                   |        |        |        | X Mode Star | t Address F | Register (XN | /ODSRT<1  | 5:1>)   |       |            |            |              |         | _      | 0000          |

| XMODEND     | 004A  |        |                   |        |        |        | X Mode End  | Address R   | egister (XIV | IODEND<1  | 5:1>)   |       |            |            |              |         | _      | 0001          |

| YMODSRT     | 004C  |        |                   |        |        |        | Y Mode Star | t Address F | Register (YN | //ODSRT<1 | 5:1>)   |       |            |            |              |         | _      | 0000          |

| YMODEND     | 004E  |        |                   |        |        |        | Y Mode End  | Address R   | egister (YM  | IODEND<1  | 5:1>)   |       |            |            |              |         | _      | 0001          |

| XBREV       | 0050  | BREN   |                   |        |        |        |             |             | XBRE         | V<14:0>   |         |       |            |            |              |         |        | 0000          |

| DISICNT     | 0052  | _      | — — DISICNT<13:0> |        |        |        |             |             |              |           |         |       | 0000       |            |              |         |        |               |

| TBLPAG      | 0054  | _      | _                 | _      | _      | _      | _           | _           | _            |           |         |       | TBLPAG     | G<7:0>     |              |         |        | 0000          |

| CTXTSTAT    | 005A  | _      | _                 | _      | _      | _      | CCTXI2      | CCTXI1      | CCTXI0       | _         | _       | _     | _          | _          | MCTXI2       | MCTXI1  | MCTXI0 | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The contents of this register should never be modified. The DSWPAG must always point to the first page.

dsPIC33EPXXGS50X FAMILY

**TABLE 4-3:** INTERRUPT CONTROLLER REGISTER MAP (CONTINUED)

| SFR<br>Name | Addr. | Bit 15 | Bit 14                    | Bit 13                    | Bit 12                    | Bit 11  | Bit 10                    | Bit 9                     | Bit 8                     | Bit 7    | Bit 6                     | Bit 5                     | Bit 4                     | Bit 3   | Bit 2                     | Bit 1                     | Bit 0                     | All<br>Resets |

|-------------|-------|--------|---------------------------|---------------------------|---------------------------|---------|---------------------------|---------------------------|---------------------------|----------|---------------------------|---------------------------|---------------------------|---------|---------------------------|---------------------------|---------------------------|---------------|

| IPC12       | 0858  | _      | _                         | _                         | _                         | _       | MI2C2IP2                  | MI2C2IP1                  | MI2C2IP0                  | _        | SI2C2IP2                  | SI2C2IP1                  | SI2C2IP0                  | _       | _                         | _                         | _                         | 0440          |

| IPC13       | 085A  | _      | _                         | _                         | _                         | _       | INT4IP2                   | INT4IP1                   | INT4IP0                   | I        | 1                         | 1                         | 1                         | _       | 1                         | _                         | 1                         | 0400          |

| IPC14       | 085C  | -      | _                         | _                         | _                         | -       | -                         | ı                         | -                         | ı        | PSEMIP2                   | PSEMIP1                   | PSEMIP0                   | _       | ı                         | _                         | 1                         | 0040          |

| IPC16       | 0860  | _      | _                         | _                         | _                         | _       | U2EIP2                    | U2EIP1                    | U2EIP0                    | -        | U1EIP2                    | U1EIP1                    | U1EIP0                    | _       | ı                         | _                         | -                         | 0440          |

| IPC18       | 0864  | _      | _                         | _                         | _                         | _       | _                         | _                         | _                         | _        | PSESIP2                   | PSESIP1                   | PSESIP0                   | _       | -                         | _                         | _                         | 0040          |

| IPC23       | 086E  |        | PWM2IP2                   | PWM2IP1                   | PWM2IP0                   |         | PWM1IP2                   | PWM1IP1                   | PWM1IP0                   | _        | _                         | _                         | _                         | _       | _                         | _                         | _                         | 4400          |

| IPC24       | 0870  |        | _                         | _                         | _                         |         | PWM5IP2                   | PWM5IP1                   | PWM5IP0                   | _        | PWM4IP2                   | PWM4IP1                   | PWM4IP0                   | _       | PWM3IP2                   | PWM3IP1                   | PWM3IP0                   | 0444          |

| IPC25       | 0872  | _      | AC2IP2                    | AC2IP1                    | AC2IP0                    | _       | _                         | _                         | _                         | -        | _                         | _                         | -                         | _       | -                         | _                         | _                         | 4000          |

| IPC26       | 0874  |        | _                         | _                         | _                         |         | _                         | _                         | _                         | _        | AC4IP2                    | AC4IP1                    | AC4IP0                    | _       | AC3IP2                    | AC3IP1                    | AC3IP0                    | 0044          |

| IPC27       | 0876  |        | ADCAN1IP2                 | ADCAN1IP1                 | ADCAN1IP0                 |         | ADCAN0IP2                 | ADCAN0IP1                 | ADCAN0IP0                 | _        | _                         | _                         | _                         | _       | _                         | _                         | _                         | 4400          |

| IPC28       | 0878  |        | ADCAN5IP2                 | ADCAN5IP1                 | ADCAN5IP0                 |         | ADCAN4IP2                 | ADCAN4IP1                 | ADCAN4IP0                 | _        | ADCAN3IP2                 | ADCAN3IP1                 | ADCAN3IP0                 | _       | ADCAN2IP2                 | ADCAN2IP1                 | ADCAN2IP0                 | 4444          |

| IPC29       | 087A  |        | _                         | _                         | _                         |         | _                         | _                         | _                         | _        | ADCAN7IP2                 | ADCAN7IP1                 | ADCAN7IP0                 | _       | ADCAN6IP2                 | ADCAN6IP1                 | ADCAN6IP0                 | 0044          |

| IPC35       | 0886  |        | JTAGIP2                   | JTAGIP1                   | JTAGIP0                   |         | ICDIP2                    | ICDIP1                    | ICDIP0                    | _        | _                         | _                         | _                         | _       | _                         | _                         | _                         | 4400          |

| IPC37       | 088A  | _      | ADCAN8IP2 <sup>(2)</sup>  | ADCAN8IP1 <sup>(2)</sup>  | ADCAN8IP0 <sup>(2)</sup>  | _       | _                         | _                         | _                         | -        | _                         | _                         | -                         | _       | -                         | _                         | _                         | 4000          |

| IPC38       | 088C  |        | ADCAN12IP2 <sup>(2)</sup> | ADCAN12IP1 <sup>(2)</sup> | ADCAN12IP0 <sup>(2)</sup> |         | ADCAN11IP2 <sup>(2)</sup> | ADCAN11IP1 <sup>(2)</sup> | ADCAN11IP0 <sup>(2)</sup> | _        | ADCAN10IP2 <sup>(2)</sup> | ADCAN10IP1 <sup>(2)</sup> | ADCAN10IP0 <sup>(2)</sup> | _       | ADCAN9IP2 <sup>(2)</sup>  | ADCAN9IP1 <sup>(2)</sup>  | ADCAN9IP0 <sup>(2)</sup>  | 4444          |

| IPC39       | 088E  |        | ADCAN16IP2 <sup>(1)</sup> | ADCAN16IP1(1)             | ADCAN16IP0 <sup>(1)</sup> |         | ADCAN15IP2 <sup>(1)</sup> | ADCAN15IP1 <sup>(1)</sup> | ADCAN15IP0 <sup>(1)</sup> | _        | ADCAN14IP2 <sup>(2)</sup> | ADCAN14IP1 <sup>(2)</sup> | ADCAN14IP0 <sup>(2)</sup> | _       | ADCAN13IP2 <sup>(1)</sup> | ADCAN13IP1                | ADCAN13IP0                | 4444          |

| IPC40       | 0890  |        | ADCAN20IP2                | ADCAN20IP1                | ADCAN20IP0                |         | ADCAN19IP2                | ADCAN19IP1                | ADCAN19IP0                | _        | ADCAN18IP2                | ADCAN18IP1                | ADCAN18IP0                | _       | ADCAN17IP2 <sup>(2)</sup> | ADCAN17IP1 <sup>(2)</sup> | ADCAN17IP0 <sup>(2)</sup> | 4444          |

| IPC41       | 0892  |        | _                         | _                         | _                         |         | _                         | _                         | _                         | _        | _                         | _                         | _                         | _       | ADCAN21IP2                | ADCAN21IP1                | ADCAN21IP0                | 0004          |

| IPC43       | 0896  |        | _                         | _                         | _                         |         | I2C2BCIP2                 | I2C2BCIP1                 | I2C2BCIP0                 | _        | I2C1BCIP2                 | I2C1BCIP1                 | I2C1BCIP0                 | _       | _                         | _                         | _                         | 0440          |

| IPC44       | 0898  |        | ADFLTR0IP2                | ADFLTR0IP1                | ADFLTR0IP0                |         | ADCMP1IP2                 | ADCMP1IP1                 | ADCMP1IP0                 | _        | ADCMP0IP2                 | ADCMP0IP1                 | ADCMP0IP0                 | _       | _                         | _                         | _                         | 4440          |

| IPC45       | 089A  |        | _                         | _                         | _                         | _       | _                         | _                         | _                         | _        | _                         | _                         | _                         | _       | ADFLTR1IP2                | ADFLTR1IP1                | ADFLTR1IP0                | 0004          |

| INTCON1     | 08C0  | NSTDIS | OVAERR                    | OVBERR                    | COVAERR                   | COVBERR | OVATE                     | OVBTE                     | COVTE                     | SFTACERR | DIV0ERR                   | _                         | MATHERR                   | ADDRERR | STKERR                    | OSCFAIL                   | _                         | 0000          |

| INTCON2     | 08C2  | GIE    | DISI                      | SWTRAP                    | _                         | _       | _                         | _                         | AIVTEN                    | _        | _                         | _                         | INT4EP                    | _       | INT2EP                    | INT1EP                    | INT0EP                    | 8000          |

| INTCON3     | 08C4  | _      | _                         | _                         | _                         | _       | -                         | -                         | NAE                       | -        | -                         | -                         | DOOVR                     | _       | 1                         | _                         | APLL                      | 0000          |

| INTCON4     | 08C6  |        | _                         | _                         | _                         | _       | _                         | _                         | _                         | _        | _                         | _                         | _                         | _       | _                         | _                         | SGHT                      | 0000          |

| INTTREG     | 08C8  | _      | _                         | _                         | _                         | ILR3    | ILR2                      | ILR1                      | ILR0                      | VECNUM7  | VECNUM6                   | VECNUM5                   | VECNUM4                   | VECNUM3 | VECNUM2                   | VECNUM1                   | VECNUM0                   | 0000          |

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Only available on dsPIC33EPXXGS506 devices.

Only available on dsPIC33EPXXGS504/505 and dsPIC33EPXXGS506 devices.

TABLE 4-20: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|--------|--------|--------|--------|---------|--------|--------|--------|---------------|

| RPINR0      | 06A0  |          |          |          | INT1R    | R<7:0>   |          |          |          | _      | _      | _      | _      | _       | _      | _      | _      | 0000          |

| RPINR1      | 06A2  | _        | _        | _        | _        | _        | _        | _        | _        |        |        |        | INT2I  | R<7:0>  |        |        |        | 0000          |

| RPINR2      | 06A4  |          |          |          | T1CKF    | R<7:0>   |          |          |          | _      | -      | _      | _      | _       | ı      | -      | _      | 0000          |

| RPINR3      | 06A6  | T3CKR7   | T3CKR6   | T3CKR5   | T3CKR4   | T3CKR3   | T3CKR2   | T3CKR1   | T3CKR0   | T2CKR7 | T2CKR6 | T2CKR5 | T2CKR4 | T2CKR3  | T2CKR2 | T2CKR1 | T2CKR0 | 0000          |

| RPINR7      | 06AE  | IC2R7    | IC2R6    | IC2R5    | IC2R4    | IC2R3    | IC2R2    | IC2R1    | IC2R0    | IC1R7  | IC1R6  | IC1R5  | IC1R4  | IC1R3   | IC1R2  | IC1R1  | IC1R0  | 0000          |

| RPINR8      | 06B0  | IC4R7    | IC4R6    | IC4R5    | IC4R4    | IC4R3    | IC4R2    | IC4R1    | IC4R0    | IC3R7  | IC3R6  | IC3R5  | IC3R4  | IC3R3   | IC3R2  | IC3R1  | IC3R0  | 0000          |

| RPINR11     | 06B6  |          | ı        | -        | -        | ı        | ı        | -        | _        |        |        |        | OCFA   | R<7:0>  |        |        |        | 0000          |

| RPINR12     | 06B8  | FLT2R7   | FLT2R6   | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | FLT1R7 | FLT1R6 | FLT1R5 | FLT1R4 | FLT1R3  | FLT1R2 | FLT1R1 | FLT1R0 | 0000          |

| RPINR13     | 06BA  | FLT4R7   | FLT4R6   | FLT4R5   | FLT4R4   | FLT4R3   | FLT4R2   | FLT4R1   | FLT4R0   | FLT3R7 | FLT3R6 | FLT3R5 | FLT3R4 | FLT3R3  | FLT3R2 | FLT3R1 | FLT3R0 | 0000          |

| RPINR18     | 06C4  | U1CTSR7  | U1CTSR6  | U1CTSR5  | U1CTSR4  | U1CTSR3  | U1CTSR2  | U1CTSR1  | U1CTS0   | U1RXR7 | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3  | U1RXR2 | U1RXR1 | U1RXR0 | 0000          |

| RPINR19     | 06C6  | U2CTSR7  | U2CTSR6  | U2CTSR5  | U2CTSR4  | U2CTSR3  | U2CTSR2  | U2CTSR1  | U2CTSR0  | U2RXR7 | U2RXR6 | U2RXR5 | U2RXR4 | U2RXR3  | U2RXR2 | U2RXR1 | U2RXR0 | 0000          |

| RPINR20     | 06C8  | SCK1INR7 | SCK1INR6 | SCK1INR5 | SCK1INR4 | SCK1INR3 | SCK1INR2 | SCK1INR1 | SCK1INR0 | SDI1R7 | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3  | SDI1R2 | SDI1R1 | SDI1R0 | 0000          |

| RPINR21     | 06CA  | -        | -        | _        | _        | -        | _        | _        | -        |        |        |        | SS1F   | R<7:0>  |        |        |        | 0000          |

| RPINR22     | 06CC  | SCK2INR7 | SCK2INR6 | SCK2INR5 | SCK2INR4 | SCK2INR3 | SCK2INR2 | SCK2INR1 | SCK2INR0 | SDI2R7 | SDI2R6 | SDI2R5 | SDI2R4 | SDI2R3  | SDI2R2 | SDI2R1 | SDI2R0 | 0000          |

| RPINR23     | 06CE  | -        | -        | _        | _        | -        | _        | _        | -        |        |        |        | SS2F   | R<7:0>  |        |        |        | 0000          |

| RPINR37     | 06EA  |          |          |          | SYNCI1   | R<7:0>   |          |          |          | 1      | -      | -      | _      | _       | _      | -      | _      | 0000          |

| RPINR38     | 06EC  | _        | -        | -        |          | _        | -        | _        | _        |        |        |        | SYNCI  | 2R<7:0> |        |        |        | 0000          |

| RPINR42     | 06F4  | FLT6R7   | FLT6R6   | FLT6R5   | FLT6R4   | FLT6R3   | FLT6R2   | FLT6R1   | FLT6R0   | FLT5R7 | FLT5R6 | FLT5R5 | FLT5R4 | FLT5R3  | FLT5R2 | FLT5R1 | FLT5R0 | 0000          |

| RPINR43     | 06F6  | FLT8R7   | FLT8R6   | FLT8R5   | FLT8R4   | FLT8R3   | FLT8R2   | FLT8R1   | FLT8R0   | FLT7R7 | FLT7R6 | FLT7R5 | FLT7R4 | FLT7R3  | FLT7R2 | FLT7R1 | FLT7R0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 10.0 I/O PORTS

**Note 1:** This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70000598) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

> 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

#### Parallel I/O (PIO) Ports 10.1

Generally, a Parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of

the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/Os. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means the corresponding LATx and TRISx registers, and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

**Peripheral Module Output Multiplexers** Peripheral Input Data Peripheral Module Enable I/O Peripheral Output Enable Output Enable Peripheral Output Data **PIO Module** Output Data Read TRISx Data Bus D Q I/O Pin WR TRISX CK L TRISx Latch D Q WR LATx + CK 🔻 WR PORTX Data Latch Read LATx Input Data Read PORTx

**FIGURE 10-1:** BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

| Input Name <sup>(1)</sup> | Function Name | Register | Configuration Bits |

|---------------------------|---------------|----------|--------------------|

| External Interrupt 1      | INT1          | RPINR0   | INT1R<7:0>         |

| External Interrupt 2      | INT2          | RPINR1   | INT2R<7:0>         |

| Timer1 External Clock     | T1CK          | RPINR2   | T1CKR<7:0>         |

| Timer2 External Clock     | T2CK          | RPINR3   | T2CKR<7:0>         |

| Timer3 External Clock     | T3CK          | RPINR3   | T3CKR<7:0>         |

| Input Capture 1           | IC1           | RPINR7   | IC1R<7:0>          |

| Input Capture 2           | IC2           | RPINR7   | IC2R<7:0>          |

| Input Capture 3           | IC3           | RPINR8   | IC3R<7:0>          |

| Input Capture 4           | IC4           | RPINR8   | IC4R<7:0>          |

| Output Compare Fault A    | OCFA          | RPINR11  | OCFAR<7:0>         |

| PWM Fault 1               | FLT1          | RPINR12  | FLT1R<7:0>         |

| PWM Fault 2               | FLT2          | RPINR12  | FLT2R<7:0>         |

| PWM Fault 3               | FLT3          | RPINR13  | FLT3R<7:0>         |

| PWM Fault 4               | FLT4          | RPINR13  | FLT4R<7:0>         |

| UART1 Receive             | U1RX          | RPINR18  | U1RXR<7:0>         |

| UART1 Clear-to-Send       | U1CTS         | RPINR18  | U1CTSR<7:0>        |

| UART2 Receive             | U2RX          | RPINR19  | U2RXR<7:0>         |

| UART2 Clear-to-Send       | U2CTS         | RPINR19  | U2CTSR<7:0>        |

| SPI1 Data Input           | SDI1          | RPINR20  | SDI1R<7:0>         |

| SPI1 Clock Input          | SCK1          | RPINR20  | SCK1R<7:0>         |

| SPI1 Slave Select         | SS1           | RPINR21  | SS1R<7:0>          |

| SPI2 Data Input           | SDI2          | RPINR22  | SDI2R<7:0>         |

| SPI2 Clock Input          | SCK2          | RPINR22  | SCK2R<7:0>         |

| SPI2 Slave Select         | SS2           | RPINR23  | SS2R<7:0>          |

| PWM Synch Input 1         | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |

| PWM Synch Input 2         | SYNCI2        | RPINR38  | SYNCI2R<7:0>       |

| PWM Fault 5               | FLT5          | RPINR42  | FLT5R<7:0>         |

| PWM Fault 6               | FLT6          | RPINR42  | FLT6R<7:0>         |

| PWM Fault 7               | FLT7          | RPINR43  | FLT7R<7:0>         |

| PWM Fault 8               | FLT8          | RPINR43  | FLT8R<7:0>         |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

#### 10.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 26-11 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

Note: Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 26.0 "Electrical Characteristics" of this data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 27.0 "DC and AC Device Characteristics Graphs"** for additional information.

#### REGISTER 10-12: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SCK1INR7 | SCK1INR6 | SCK1INR5 | SCK1INR4 | SCK1INR3 | SCK1INR2 | SCK1INR1 | SCK1INR0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SDI1R7 | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 SCK1INR<7:0>: Assign SPI1 Clock Input (SCK1) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181 10110100 = Input tied to RP180

•

•

00000001 = Input tied to RP1 00000000 = Input tied to Vss

bit 7-0 SDI1R<7:0>: Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181 10110100 = Input tied to RP180

•

.

00000001 = Input tied to RP1 00000000 = Input tied to Vss

#### REGISTER 10-16: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SYNCI1R7 | SYNCI1R6 | SYNCI1R5 | SYNCI1R4 | SYNCI1R3 | SYNCI1R2 | SYNCI1R1 | SYNCI1R0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 SYNCI1R<7:0>: Assign PWM Synchronization Input 1 to the Corresponding RPn Pin bits

> 10110101 = Input tied to RP181 10110100 = Input tied to RP180

00000001 = Input tied to RP1 00000000 = Input tied to Vss

bit 7-0 Unimplemented: Read as '0'

#### **REGISTER 10-36: RPOR16: PERIPHERAL PIN SELECT OUTPUT REGISTER 16**

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP177R<5:0>: Peripheral Output Function is Assigned to RP177 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP176R<5:0>: Peripheral Output Function is Assigned to RP176 Output Pin bits

(see Table 10-2 for peripheral function numbers)

#### REGISTER 10-37: RPOR17: PERIPHERAL PIN SELECT OUTPUT REGISTER 17

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP179R<5:0>: Peripheral Output Function is Assigned to RP179 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP178R<5:0>: Peripheral Output Function is Assigned to RP178 Output Pin bits

(see Table 10-2 for peripheral function numbers)

#### REGISTER 15-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER (1,2)

| R/W-1       | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTPER<15:8> |       |       |       |       |       |       |       |  |

| bit 15      |       |       |       |       |       |       | bit 8 |  |

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PTPE  | R<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PTPER<15:0>: Primary Master Time Base (PMTMR) Period Value bits

Note 1: The PWMx time base has a minimum value of 0x0010 and a maximum value of 0xFFF8.

2: Any period value that is less than 0x0028 must have the Least Significant 3 bits set to '0', thus yielding a period resolution at 8.32 ns (at fastest auxiliary clock rate).

#### REGISTER 15-4: SEVTCMP: PWMx SPECIAL EVENT COMPARE REGISTER<sup>(1)</sup>

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| SEVTCMP<12:5> |       |       |       |       |       |       |       |

| bit 15        |       |       |       |       |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0        | R/W-0 | R/W-0 | U-0   | U-0 | U-0 |

|-------|-------|--------------|-------|-------|-------|-----|-----|

|       | S     | SEVTCMP<4:0> | >     |       | _     | _   | _   |

| bit 7 |       |              |       |       | bit 0 |     |     |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **SEVTCMP<12:0>:** Special Event Compare Count Value bits

bit 2-0 **Unimplemented:** Read as '0'

Note 1: One LSB = 1.04 ns (at fastest auxiliary clock rate); therefore, the minimum SEVTCMP resolution is 8.32 ns.

#### REGISTER 19-2: ADCON1H: ADC CONTROL REGISTER 1 HIGH

| r-0    | r-0 | r-0 | r-0 | r-0 | r-0 | r-0 | r-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-1   | R/W-1   | r-0 | r-0 | r-0 | r-0 | r-0   |

|-------|---------|---------|-----|-----|-----|-----|-------|

| FORM  | SHRRES1 | SHRRES0 | _   | _   | _   | _   | _     |

| bit 7 |         |         |     |     |     |     | bit 0 |

Legend: r = Reserved bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Reserved:** Maintain as '0'

bit 7 FORM: Fractional Data Output Format bit

1 = Fractional0 = Integer

bit 6-5 SHRRES<1:0>: Shared ADC Core Resolution Selection bits

11 = 12-bit resolution 10 = 10-bit resolution 01 = 8-bit resolution 00 = 6-bit resolution

bit 4-0 Reserved: Maintain as '0'

#### REGISTER 20-1: CMPxCON: COMPARATOR x CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0 |

|--------|-----|---------|---------|---------|--------|---------|-------|

| CMPON  | _   | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN | FCLKSEL | DACOE |

| bit 15 |     |         |         |         |        |         | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | HC-0, HS | R/W-0  | R/W-0  | R/W-0 |

|--------|--------|--------|--------|----------|--------|--------|-------|

| INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT  | ALTINP | CMPPOL | RANGE |

| bit 7  |        |        |        |          |        |        | bit 0 |

| Legend:           | HC = Hardware Clearable bit | it HS = Hardware Settable bit      |                    |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 CMPON: Comparator Operating Mode bit

1 = Comparator module is enabled

0 = Comparator module is disabled (reduces power consumption)

bit 14 Unimplemented: Read as '0'

bit 13 CMPSIDL: Comparator Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode.

0 = Continues module operation in Idle mode

If a device has multiple comparators, any CMPSIDL bit set to '1' disables all comparators while in Idle mode.

bit 12-11 **HYSSEL<1:0>:** Comparator Hysteresis Select bits

11 = 20 mV hysteresis

10 = 10 mV hysteresis

01 = 5 mV hysteresis

00 = No hysteresis is selected

bit 10 FLTREN: Digital Filter Enable bit

1 = Digital filter is enabled

0 = Digital filter is disabled

bit 9 FCLKSEL: Digital Filter and Pulse Stretcher Clock Select bit

1 = Digital filter and pulse stretcher operate with the PWM clock

0 = Digital filter and pulse stretcher operate with the system clock

bit 8 DACOE: DACx Output Enable bit

1 = DACx analog voltage is connected to the DACOUTx pin<sup>(1)</sup>

0 = DACx analog voltage is not connected to the DACOUTx pin

bit 7-6 **INSEL<1:0>:** Input Source Select for Comparator bits

If ALTINP = 0, Select from Comparator Inputs:

11 = Selects CMPxD input pin

10 = Selects CMPxC input pin

01 = Selects CMPxB input pin

00 = Selects CMPxA input pin

If ALTINP = 1, Select from Alternate Inputs:

11 = Reserved

10 = Reserved

01 = Selects PGA2 output

00 = Selects PGA1 output

**Note 1:** DACOUTx can be associated only with a single comparator at any given time. The software must ensure that multiple comparators do not enable the DACx output by setting their respective DACOE bit.

#### REGISTER 21-1: PGAxCON: PGAx CONTROL REGISTER (CONTINUED)

bit 2-0 GAIN<2:0>: PGAx Gain Selection bits

111 = Reserved 110 = Gain of 64x 101 = Gain of 32x 100 = Gain of 16x

011 = Gain of 8x 010 = Gain of 4x 001 = Reserved 000 = Reserved

#### REGISTER 21-2: PGAxCAL: PGAx CALIBRATION REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|--|--|

| _     | _   |       | PGACAL<5:0> |       |       |       |       |  |  |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 **PGACAL<5:0>:** PGAx Offset Calibration bits

The calibration values for PGA1 and PGA2 must be copied from Flash addresses, 0x800E48 and 0x800E4C, respectively, into these bits before the module is enabled. Refer to the calibration data address table (Table 23-3) in **Section 23.0 "Special Features"** for more information.

## 23.2 Device Calibration and Identification

The PGAx and current source modules on the dsPIC33EPXXGS50X family devices require Calibration Data registers to improve performance of the module over a wide operating range. These Calibration registers are read-only and are stored in configuration memory space. Prior to enabling the module, the calibration data must be read (TBLPAG and Table Read instruction) and loaded into its respective SFR registers. The device calibration addresses are shown in Table 23-3.

The dsPIC33EPXXGS50X devices have two identification registers near the end of configuration memory space that store the Device ID (DEVID) and Device Revision (DEVREV). These registers are used to determine the mask, variant and manufacturing information about the device. These registers are read-only and are shown in Register 23-1 and Register 23-2.

#### TABLE 23-3: DEVICE CALIBRATION ADDRESSES<sup>(1)</sup>

| Calibration<br>Name | Address | Bits 23-16 | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5                           | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------------|---------|------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|---------------------------------|-------|-------|-------|-------|-------|

|                     |         |            |        |        |        |        |        |        |       |       |       |       |                                 |       |       |       |       |       |

| PGA1CAL             | 800E48  | _          | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | PGA1 Calibration Data           |       |       |       |       |       |

| PGA2CAL             | 800E4C  |            |        | _      | _      | _      | _      | _      |       | _     |       | _     | PGA2 Calibration Data           |       |       |       |       |       |

|                     |         |            |        |        |        |        |        |        |       |       |       |       | 1 0/12 Cambration Bata          |       |       |       |       |       |

| ISRCCAL             | 800E78  | _          | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | Current Source Calibration Data |       | ata   |       |       |       |

Note 1: The calibration data must be copied into its respective registers prior to enabling the module.

#### 23.7 JTAG Interface

The dsPIC33EPXXGS50X family devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

Note: Refer to "Programming and Diagnostics" (DS70608) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of the JTAG interface.

#### 23.8 In-Circuit Serial Programming™

The dsPIC33EPXXGS50X family devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming™ (ICSP™).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- · PGEC3 and PGED3

#### 23.9 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE™ emulator is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

## 23.10 Code Protection and CodeGuard™ Security

dsPIC33EPXXGS50X devices offer multiple levels of security for protecting individual intellectual property. The program Flash protection can be broken up into three segments: Boot Segment (BS), General Segment (GS) and Configuration Segment (CS). Boot Segment has the highest security privilege and can be thought to have limited restrictions when accessing other segments. General Segment has the least security and is intended for the end user system code. Configuration Segment contains only the device user configuration data which is located at the end of the program memory space.

The code protection features are controlled by the Configuration registers, FSEC and FBSLIM. The FSEC register controls the code-protect level for each segment and if that segment is write-protected. The size of BS and GS will depend on the BSLIM<12:0> setting and if the Alternate Interrupt Vector Table (AIVT) is enabled. The BSLIM<12:0> bits define the number of pages for BS with each page containing 512 IW. The smallest BS size is one page, which will consist of the Interrupt Vector Table (IVT) and 256 IW of code protection.

If the AIVT is enabled, the last page of BS will contain the AIVT and will not contain any BS code. With AIVT enabled, the smallest BS size is now two pages (1024 IW), with one page for the IVT and BS code, and the other page for the AIVT. Write protection of the BS does not cover the AIVT. The last page of BS can always be programmed or erased by BS code. The General Segment will start at the next page and will consume the rest of program Flash except for the Flash Configuration Words. The IVT will assume GS security only if BS is not enabled. The IVT is protected from being programmed or page erased when either security segment has enabled write protection.

Note: Refer to "CodeGuard™ Intermediate Security" (DS70005182) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

TABLE 26-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT                              | ERISTICS |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                  |      |  |  |  |  |

|-----------------------------------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|--|--|--|--|

| Parameter<br>No.                        | Тур.     | Max. | Units                                                                                                                                                                                                                                             | Units Conditions |      |  |  |  |  |

| Power-Down Current (IPD) <sup>(1)</sup> |          |      |                                                                                                                                                                                                                                                   |                  |      |  |  |  |  |

| DC60d                                   | 12       | 100  | μА                                                                                                                                                                                                                                                | -40°C            |      |  |  |  |  |

| DC60a                                   | 18       | 100  | μА                                                                                                                                                                                                                                                | +25°C            | 3.3V |  |  |  |  |

| DC60b                                   | 130      | 400  | μА                                                                                                                                                                                                                                                | +85°C            | 3.30 |  |  |  |  |

| DC60c 500 1100                          |          |      | μА                                                                                                                                                                                                                                                | +125°C           |      |  |  |  |  |

Note 1: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- · JTAG is disabled

#### TABLE 26-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT (△IWDT)<sup>(1)</sup>

| DC CHARACTER  | ISTICS |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |              |      |  |  |  |

|---------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|--|--|--|

| Parameter No. | Тур.   | Max. | Units                                                                                                                                                                                                                                            | s Conditions |      |  |  |  |

| DC61d         | 13     | 50   | μΑ                                                                                                                                                                                                                                               | -40°C        |      |  |  |  |

| DC61a         | 19     | 80   | μΑ                                                                                                                                                                                                                                               | +25°C        | 3.3V |  |  |  |

| DC61b         | 12     | _    | μΑ                                                                                                                                                                                                                                               | +85°C        | 3.3V |  |  |  |

| DC61c         | 13     | _    | μΑ                                                                                                                                                                                                                                               | +125°C       |      |  |  |  |

**Note 1:** The ΔIWDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

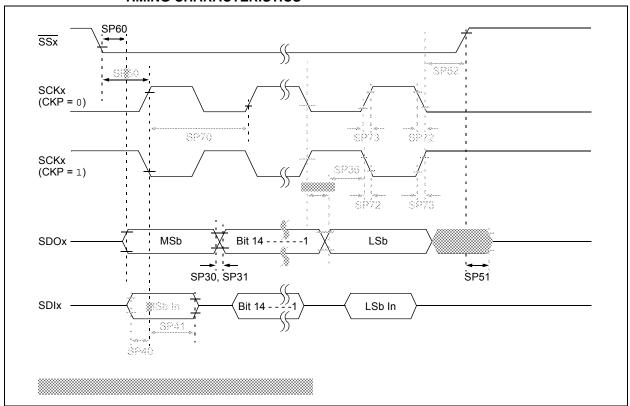

FIGURE 26-16: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

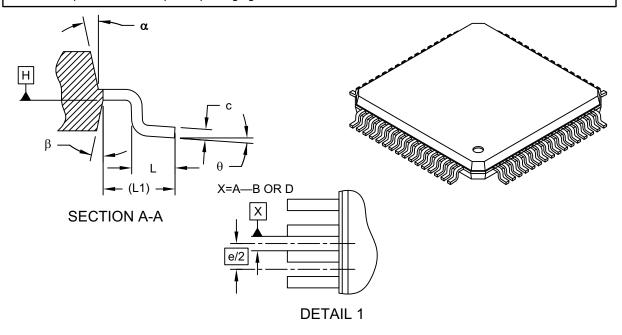

#### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |          |      |  |  |  |

|--------------------------|-------------|-----------|----------|------|--|--|--|

| Dimension                | MIN         | NOM       | MAX      |      |  |  |  |

| Number of Leads          | N           |           | 64       |      |  |  |  |

| Lead Pitch               | е           |           | 0.50 BSC |      |  |  |  |

| Overall Height           | Α           | -         | 1.20     |      |  |  |  |

| Molded Package Thickness | A2          | 0.95      | 1.00     | 1.05 |  |  |  |

| Standoff                 | A1          | 0.05      | 0.05 -   |      |  |  |  |

| Foot Length              | L           | 0.45      | 0.60     | 0.75 |  |  |  |

| Footprint                | L1          | 1.00 REF  |          |      |  |  |  |

| Foot Angle               | ф           | 0°        | 3.5°     | 7°   |  |  |  |

| Overall Width            | Е           | 12.00 BSC |          |      |  |  |  |

| Overall Length           | D           | 12.00 BSC |          |      |  |  |  |

| Molded Package Width     | E1          | 10.00 BSC |          |      |  |  |  |

| Molded Package Length    | D1          | 10.00 BSC |          |      |  |  |  |

| Lead Thickness           | С           | 0.09      | -        | 0.20 |  |  |  |

| Lead Width               | b           | 0.17      | 0.22     | 0.27 |  |  |  |

| Mold Draft Angle Top     | α           | 11°       | 12°      | 13°  |  |  |  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°      | 13°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support