Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs502t-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

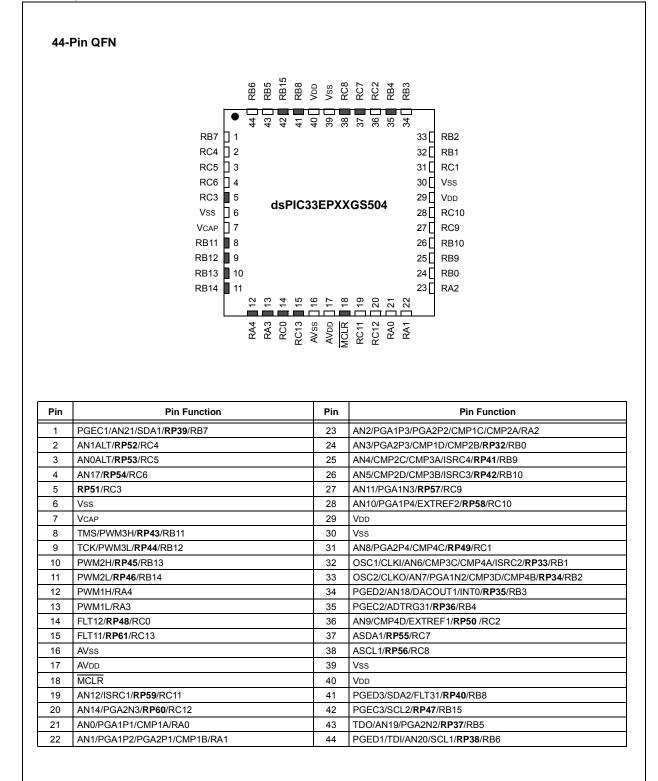

# **Pin Diagrams (Continued)**

Legend: Shaded pins are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXGS50X family requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins regardless if ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

# 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

# 3.6.1 KEY RESOURCES

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# TABLE 4-17: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXGS502 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| RPOR0       | 0670  | _      | _      | RP33R5  | RP33R4  | RP33R3  | RP33R2  | RP33R1  | RP33R0  |       | —     | RP32R5  | RP32R4  | RP32R3  | RP32R2  | RP32R1  | RP32R0  | 0000          |

| RPOR1       | 0672  | _      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | _     | _     | RP34R5  | RP34R4  | RP34R3  | RP34R2  | RP34R1  | RP34R0  | 0000          |

| RPOR2       | 0674  | _      |        | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  |       | -     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR3       | 0676  | _      |        | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  |       | -     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR4       | 0678  | —      |        | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | I     | —     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR5       | 067A  | —      |        | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | I     | —     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR6       | 067C  | —      |        | RP45R5  | RP45R4  | RP45R3  | RP45R2  | RP45R1  | RP45R0  | I     | —     | RP44R5  | RP44R4  | RP44R3  | RP44R2  | RP44R1  | RP44R0  | 0000          |

| RPOR7       | 067E  | —      |        | RP47R5  | RP47R4  | RP47R3  | RP47R2  | RP47R1  | RP47R0  | I     | —     | RP46R5  | RP46R4  | RP46R3  | RP46R2  | RP46R1  | RP46R0  | 0000          |

| RPOR16      | 0690  | —      |        | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |       | —     | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 | 0000          |

| RPOR17      | 0692  | _      |        | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | I     | —     | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | 0000          |

| RPOR18      | 0694  | —      | -      | RP181R5 | RP181R4 | RP181R3 | RP181R2 | RP181R1 | RP181R0 | _     | —     | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | 0000          |

dsPIC33EPXXGS50X FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXGS504/505 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------|

| RPOR0       | 0670  | _      |        | RP33R5  | RP33R4  | RP33R3  | RP33R2  | RP33R1  | RP33R0  | _     | _     | RP32R5  | RP32R4  | RP32R3  | RP32R2  | RP32R1  | RP32R0  | 0000          |

| RPOR1       | 0672  | -      |        | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  |       |       | RP34R5  | RP34R4  | RP34R3  | RP34R2  | RP34R1  | RP34R0  | 0000          |

| RPOR2       | 0674  | -      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | _     | —     | RP36R5  | RP36R4  | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR3       | 0676  | -      | —      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | _     | _     | RP38R5  | RP38R4  | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR4       | 0678  | _      | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | —     | _     | RP40R5  | RP40R4  | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR5       | 067A  | _      | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | —     | _     | RP42R5  | RP42R4  | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR6       | 067C  | _      | _      | RP45R5  | RP45R4  | RP45R3  | RP45R2  | RP45R1  | RP45R0  | —     | _     | RP44R5  | RP44R4  | RP44R3  | RP44R2  | RP44R1  | RP44R0  | 0000          |

| RPOR7       | 067E  | _      | _      | RP47R5  | RP47R4  | RP47R3  | RP47R2  | RP47R1  | RP47R0  | —     | _     | RP46R5  | RP46R4  | RP46R3  | RP46R2  | RP46R1  | RP46R0  | 0000          |

| RPOR8       | 0680  | _      | _      | RP49R5  | RP49R4  | RP49R3  | RP49R2  | RP49R1  | RP49R0  | —     | _     | RP48R5  | RP48R4  | RP48R3  | RP48R2  | RP48R1  | RP48R0  | 0000          |

| RPOR9       | 0682  | _      | _      | RP51R5  | RP51R4  | RP51R3  | RP51R2  | RP51R1  | RP51R0  | _     | —     | RP50R5  | RP50R4  | RP50R3  | RP50R2  | RP50R1  | RP50R0  | 0000          |

| RPOR10      | 0684  | _      | _      | RP53R5  | RP53R4  | RP53R3  | RP53R2  | RP53R1  | RP53R0  | —     | _     | RP52R5  | RP52R4  | RP52R3  | RP52R2  | RP52R1  | RP52R0  | 0000          |

| RPOR11      | 0686  | _      | _      | RP55R5  | RP55R4  | RP55R3  | RP55R2  | RP55R1  | RP55R0  | —     | _     | RP54R5  | RP54R4  | RP54R3  | RP54R2  | RP54R1  | RP54R0  | 0000          |

| RPOR12      | 0688  | _      | _      | RP57R5  | RP57R4  | RP57R3  | RP57R2  | RP57R1  | RP57R0  | —     | _     | RP56R5  | RP56R4  | RP56R3  | RP56R2  | RP56R1  | RP56R0  | 0000          |

| RPOR13      | 068A  | _      | -      | RP59R5  | RP59R4  | RP59R3  | RP59R2  | RP59R1  | RP59R0  | _     |       | RP58R5  | RP58R4  | RP58R3  | RP58R2  | RP58R1  | RP58R0  | 0000          |

| RPOR14      | 068C  | _      | -      | RP61R5  | RP61R4  | RP61R3  | RP61R2  | RP61R1  | RP61R0  | _     |       | RP60R5  | RP60R4  | RP60R3  | RP60R2  | RP60R1  | RP60R0  | 0000          |

| RPOR16      | 0690  | _      |        | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 | _     | _     | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 | 0000          |

| RPOR17      | 0692  | _      | -      | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 | _     | _     | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | 0000          |

| RPOR18      | 0694  | _      | -      | RP181R5 | RP181R4 | RP181R3 | RP181R2 | RP181R1 | RP181R0 | _     | _     | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 5.4 Dual Partition Flash Configuration

For dsPIC33EP64GS50X devices operating in Dual Partition Flash Program Memory modes, the Inactive Partition can be erased and programmed without stalling the processor. The same programming algorithms are used for programming and erasing the Flash in the Inactive Partition, as described in **Section 5.2 "RTSP Operation"**. On top of the page erase option, the entire Flash memory of the Inactive Partition can be erased by configuring the NVMOP<3:0> bits in the NVMCON register.

Note 1: The application software to be loaded into the Inactive Partition will have the address of the Active Partition. The bootloader firmware will need to offset the address by 0x400000 in order to write to the Inactive Partition.

# 5.4.1 FLASH PARTITION SWAPPING

The Boot Sequence Number is used for determining the Active Partition at start-up and is encoded within the FBTSEQ Configuration register bits. Unlike most Configuration registers, which only utilize the lower 16 bits of the program memory, FBTSEQ is a 24-bit Configuration Word. The Boot Sequence Number (BSEQ) is a 12-bit value and is stored in FBTSEQ twice. The true value is stored in bits, FBTSEQ<11:0>, and its complement is stored in bits, FBTSEQ<23:12>. At device Reset, the sequence numbers are read and the partition with the lowest sequence number becomes the Active Partition. If one of the Boot Sequence Numbers is invalid, the device will select the partition with the valid Boot Sequence Number, or default to Partition 1 if both sequence numbers are invalid. See Section 23.0 "Special Features" for more information.

The BOOTSWP instruction provides an alternative means of swapping the Active and Inactive Partitions (soft swap) without the need for a device Reset. The BOOTSWP must always be followed by a GOTO instruction. The BOOTSWP instruction swaps the Active and Inactive Partitions, and the PC vectors to the location specified by the GOTO instruction in the newly Active Partition.

It is important to note that interrupts should temporarily be disabled while performing the soft swap sequence and that after the partition swap, all peripherals and interrupts which were enabled remain enabled. Additionally, the RAM and stack will maintain state after the switch. As a result, it is recommended that applications using soft swaps jump to a routine that will reinitialize the device in order to ensure the firmware runs as expected. The Configuration registers will have no effect during a soft swap. For robustness of operation, in order to execute the BOOTSWP instruction, it is necessary to execute the NVM unlocking sequence as follows:

- 1. Write 0x55 to NVMKEY.

- 2. Write 0xAA to NVMKEY.

- 3. Execute the BOOTSWP instruction.

If the unlocking sequence is not performed, the BOOTSWP instruction will be executed as a forced NOP and a GOTO instruction, following the BOOTSWP instruction, will be executed, causing the PC to jump to that location in the current operating partition.

The SFTSWP and P2ACTIV bits in the NVMCON register are used to determine a successful swap of the Active and Inactive Partitions, as well as which partition is active. After the BOOTSWP and GOTO instructions, the SFTSWP bit should be polled to verify the partition swap has occurred and then cleared for the next panel swap event.

# 5.4.2 DUAL PARTITION MODES

While operating in Dual Partition mode, dsPIC33EP64GS50X family devices have the option for both partitions to have their own defined security segments, as shown in Figure 23-4. Alternatively, the device can operate in Protected Dual Partition mode, where Partition 1 becomes permanently erase/write-protected. Protected Dual Partition mode allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1.

dsPIC33EP64GS50X family devices can also operate in Privileged Dual Partition mode, where additional security protections are implemented to allow for protection of intellectual property when multiple parties have software within the device. In Privileged Dual Partition mode, both partitions place additional restrictions on the BSLIM register. These prevent changes to the size of the Boot Segment and General Segment, ensuring that neither segment will be altered.

# 5.5 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

# 5.5.1 KEY RESOURCES

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# dsPIC33EPXXGS50X FAMILY

| R/W-0           | R/W-0           | U-0                                  | U-0           | R/W-0                        | U-0               | R/W-0            | R/W-0         |

|-----------------|-----------------|--------------------------------------|---------------|------------------------------|-------------------|------------------|---------------|

| TRAPR           | IOPUWR          |                                      | —             | VREGSF                       |                   | CM               | VREGS         |

| bit 15          |                 |                                      | L             |                              |                   |                  | bit 8         |

|                 |                 |                                      |               |                              |                   |                  |               |

| R/W-0           | R/W-0           | R/W-0                                | R/W-0         | R/W-0                        | R/W-0             | R/W-1            | R/W-1         |

| EXTR            | SWR             | SWDTEN <sup>(2)</sup>                | WDTO          | SLEEP                        | IDLE              | BOR              | POR           |

| bit 7           |                 |                                      |               |                              |                   |                  | bit (         |

| Legend:         |                 |                                      |               |                              |                   |                  |               |

| R = Readable    | bit             | W = Writable                         | bit           | U = Unimple                  | mented bit, read  | l as '0'         |               |

| -n = Value at l |                 | '1' = Bit is set                     |               | '0' = Bit is cle             |                   | x = Bit is unki  | nown          |

|                 |                 |                                      |               |                              |                   |                  |               |

| bit 15          | TRAPR: Trap     | Reset Flag bit                       |               |                              |                   |                  |               |

|                 | -               | onflict Reset ha                     |               |                              |                   |                  |               |

|                 | 0 = A Trap Co   | onflict Reset ha                     | s not occurre | ed                           |                   |                  |               |

| bit 14          | IOPUWR: Ille    | gal Opcode or                        | Uninitialized | W Register Ac                | cess Reset Flag   | bit              |               |

|                 | •               | •                                    |               | gal address m                | ode or Uninitial  | ized W registe   | er used as ar |

|                 |                 | Pointer caused                       |               | ogistor Posot k              | nas not occurred  | 4                |               |

| bit 13-12       | -               | ited: Read as '                      |               | egister Reset i              | las not occurred  | 1                |               |

| bit 11          | •               |                                      |               |                              | n hit             |                  |               |

|                 |                 | ash Voltage Reg<br>Itage regulator i | -             |                              | p bit             |                  |               |

|                 |                 | Itage regulator                      |               | •                            | ing Sleep         |                  |               |

| bit 10          |                 | ted: Read as '                       | -             | 5                            | 0                 |                  |               |

| bit 9           | -               | ation Mismatch                       |               |                              |                   |                  |               |

|                 |                 | uration Mismato<br>uration Mismato   |               |                              |                   |                  |               |

| bit 8           | VREGS: Volta    | age Regulator S                      | Standby Durir | ng Sleep bit                 |                   |                  |               |

|                 | 1 = Voltage r   | egulator is activ                    | ve during Sle | ep                           |                   |                  |               |

|                 | 0 = Voltage r   | egulator goes i                      | nto Standby r | mode during SI               | еер               |                  |               |

| bit 7           |                 | nal Reset (MCL                       |               |                              |                   |                  |               |

|                 |                 | Clear (pin) Res                      |               |                              |                   |                  |               |

| bit 6           |                 | Clear (pin) Res                      |               |                              |                   |                  |               |

|                 |                 | instruction has                      | , .           |                              |                   |                  |               |

|                 |                 | instruction has                      |               |                              |                   |                  |               |

| bit 5           | SWDTEN: So      | oftware Enable/                      | Disable of W  | DT bit <b><sup>(2)</sup></b> |                   |                  |               |

|                 | 1 = WDT is e    |                                      |               |                              |                   |                  |               |

|                 | 0 = WDT is d    | isabled                              |               |                              |                   |                  |               |

| bit 4           |                 | hdog Timer Tim                       | -             | it                           |                   |                  |               |

|                 |                 | e-out has occur<br>e-out has not oc  |               |                              |                   |                  |               |

|                 |                 |                                      | set or cleare | d in software. S             | Setting one of th | ese bits in soft | ware does not |

|                 | use a device Re |                                      | hite are '11' | (upprogramm)                 |                   | alwaye anabla    | d rogardiaca  |

|                 | the SWDTEN<1:0  |                                      |               | unprogramme                  | ed), the WDT is   | aiways enable    | u, regardiess |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

© 2013-2017 Microchip Technology Inc.

of the SWDTEN bit setting.

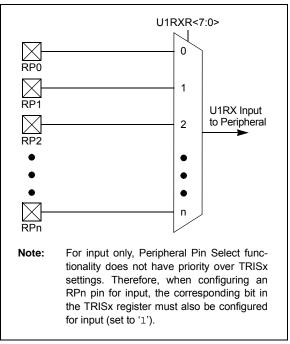

# 10.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-19). Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 10-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 10-2: REMAPPABLE INPUT FOR U1RX

# 10.4.4.1 Virtual Connections

The dsPIC33EPXXGS50X devices support six virtual RPn pins (RP176-RP181), which are identical in functionality to all other RPn pins, with the exception of pinouts. These six pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP176 and the PWM Fault input can be configured for RP176 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRISx setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRISx settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned.

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select x (ANSELx) registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select x registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

# 10.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

# 10.6.1 KEY RESOURCES

- "I/O Ports" (DS70000598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# dsPIC33EPXXGS50X FAMILY

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                                                                          | R/W-0                              |                  | <b>D</b> 444 A   |                 |        |

|---------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|------------------|-----------------|--------|

|               |                                                                                                           |                                                                                                                | 10,00-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT6R7        | FLT6R6                                                                                                    | FLT6R5                                                                                                         | FLT6R4                             | FLT6R3           | FLT6R2           | FLT6R1          | FLT6R0 |

| bit 15        |                                                                                                           | ·                                                                                                              |                                    | ·                |                  |                 | bit 8  |

|               |                                                                                                           |                                                                                                                |                                    |                  |                  |                 |        |

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                                                                          | R/W-0                              | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT5R7        | FLT5R6                                                                                                    | FLT5R5                                                                                                         | FLT5R4                             | FLT5R3           | FLT5R2           | FLT5R1          | FLT5R0 |

| bit 7         |                                                                                                           |                                                                                                                |                                    |                  |                  |                 | bit C  |

| Legend:       |                                                                                                           |                                                                                                                |                                    |                  |                  |                 |        |

| R = Readable  | e bit                                                                                                     | W = Writable                                                                                                   | bit                                | U = Unimpler     | nented bit, read | d as '0'        |        |

| -n = Value at | POR                                                                                                       | '1' = Bit is set                                                                                               |                                    | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 7-0       | 10110100 =<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to Vs<br>Assign PWM<br>Input tied to RI | ⊃180<br>⊃1<br>SS<br>Fault 5 (FLT5) | ) to the Corresp | oonding RPn Pi   | n bits          |        |

|               | •<br>•                                                                                                    | Input tied to RI                                                                                               |                                    |                  |                  |                 |        |

# REGISTER 10-18: RPINR42: PERIPHERAL PIN SELECT INPUT REGISTER 42

# dsPIC33EPXXGS50X FAMILY

## REGISTER 13-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0                 | R/W-0, HS               | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> |     | SYNCSEL4(4) | SYNCSEL3(4) | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0(4) |

| bit 7                 |                         |     |             |             |             |             | bit 0       |

| Legend:           | HS = Hardware Settable b | it                          |                    |

|-------------------|--------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared        | x = Bit is unknown |

bit 8 **IC32:** Input Capture x 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd ICx and even ICx form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

### bit 7 ICTRIG: Input Capture x Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source is used to trigger the input capture timer (Trigger mode)

- 0 = Input source is used to synchronize the input capture timer to a timer of another module (Synchronization mode)

#### bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

- bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

# REGISTER 15-12: PWMCONx: PWMx CONTROL REGISTER (x = 1 to 5) (CONTINUED)

- bit 7-6 DTC<1:0>: Dead-Time Control bits 11 = Reserved 10 = Dead-time function is disabled 01 = Negative dead time is actively applied for Complementary Output mode 00 = Positive dead time is actively applied for all Output modes bit 5-4 Unimplemented: Read as '0' bit 3 MTBS: Master Time Base Select bit 1 = PWMx generator uses the secondary master time base for synchronization and the clock source for the PWMx generation logic (if secondary time base is available) 0 = PWMx generator uses the primary master time base for synchronization and the clock source for the PWMx generation logic CAM: Center-Aligned Mode Enable bit<sup>(2,3,4)</sup> bit 2 1 = Center-Aligned mode is enabled 0 = Edge-Aligned mode is enabled XPRES: External PWMx Reset Control bit<sup>(5)</sup> bit 1 1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base mode 0 = External pins do not affect the PWMx time base bit 0 **IUE:** Immediate Update Enable bit 1 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are immediate 0 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are synchronized to the local PWMx time base Note 1: Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller. 2: The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored. 3: These bits should not be changed after the PWMx is enabled by setting PTEN = 1 (PTCON<15>). 4: Center-Aligned mode ignores the Least Significant 3 bits of the Duty Cycle, Phase and Dead-Time registers. The highest Center-Aligned mode resolution available is 8.32 ns with the clock prescaler set to

- 5: Configure CLMOD = 0 (FCLCONx<8>) and ITB = 1 (PWMCONx<9>) to operate in External Period Reset mode.

the fastest clock.

# REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 5)

|              | (X = 1         | 10 5)                            |                    |                                        |                   |                 |                  |

|--------------|----------------|----------------------------------|--------------------|----------------------------------------|-------------------|-----------------|------------------|

| R/W-0        | R/W-0          | R/W-0                            | R/W-0              | R/W-0                                  | R/W-0             | U-0             | U-0              |

| PHR          | PHF            | PLR                              | PLF                | FLTLEBEN                               | CLLEBEN           | —               |                  |

| bit 15       |                |                                  |                    |                                        |                   |                 | bit 8            |

|              |                |                                  |                    |                                        |                   |                 |                  |

| U-0          | U-0            | R/W-0                            | R/W-0              | R/W-0                                  | R/W-0             | R/W-0           | R/W-0            |

|              |                | BCH <sup>(1)</sup>               | BCL <sup>(1)</sup> | BPHH                                   | BPHL              | BPLH            | BPLL             |

| bit 7        |                |                                  |                    |                                        |                   |                 | bit 0            |

| Legend:      |                |                                  |                    |                                        |                   |                 |                  |

| R = Readat   | ole bit        | W = Writable b                   | oit                | U = Unimpler                           | nented bit, read  | as '0'          |                  |

| -n = Value a | at POR         | '1' = Bit is set                 |                    | '0' = Bit is clea                      |                   | x = Bit is unkr | nown             |

| bit 15       |                | H Rising Edge T                  | riggor Epoble      | - bit                                  |                   |                 |                  |

| bit 15       | 1 = Rising edg | ge of PWMxH v                    | vill trigger the   | Leading-Edge E<br>ling edge of PW      | •                 | PL              |                  |

| bit 14       | -              | I Falling Edge 1                 | -                  |                                        |                   |                 |                  |

|              |                |                                  |                    | e Leading-Edge                         | Blanking counte   | er              |                  |

|              | -              |                                  | -                  | lling edge of PW                       | /MxH              |                 |                  |

| bit 13       |                | Rising Edge T                    |                    |                                        |                   |                 |                  |

|              |                |                                  |                    | Leading-Edge E<br>sing edge of PW      |                   | r               |                  |

| bit 12       | -              | Falling Edge T                   | -                  |                                        |                   |                 |                  |

|              | 1 = Falling ed | ge of PWMxL v                    | vill trigger the   | Leading-Edge E<br>lling edge of PW     | •                 | er              |                  |

| bit 11       | -              |                                  | -                  | anking Enable bi                       |                   |                 |                  |

|              |                |                                  |                    | ne selected Faul<br>to the selected F  |                   |                 |                  |

| bit 10       | CLLEBEN: C     | urrent-Limit Lea                 | ading-Edge B       | lanking Enable I                       | bit               |                 |                  |

|              |                |                                  |                    | ne selected curre<br>to the selected o |                   | ut              |                  |

| bit 9-6      | Unimplemen     | ted: Read as '0                  | 2                  |                                        |                   |                 |                  |

| bit 5        | BCH: Blankin   | g in Selected B                  | lanking Signa      | al High Enable b                       | it <sup>(1)</sup> |                 |                  |

|              |                |                                  |                    | Fault input signa<br>ng signal is high |                   | lected blanking | g signal is high |

| bit 4        | BCL: Blankin   | g in Selected B                  | lanking Signa      | I Low Enable bit                       | t(1)              |                 |                  |

|              |                | nking (of currenting when the se |                    | Fault input signa<br>ng signal is low  | als) when the se  | elected blankin | g signal is low  |

| bit 3        | BPHH: Blank    | ing in PWMxH I                   | High Enable b      | oit                                    |                   |                 |                  |

|              |                | nking (of currenting when the PV |                    | Fault input signa<br>is high           | als) when the P   | WMxH output i   | s high           |

| bit 2        | BPHL: Blanki   | ing in PWMxH L                   | ow Enable b        | it                                     |                   |                 |                  |

|              |                | nking (of currenting when the PV |                    | Fault input signa<br>is low            | als) when the P\  | WMxH output i   | s low            |

|              |                |                                  |                    |                                        |                   |                 |                  |

**Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

# REGISTER 16-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 1 | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Transmit has not yet started, SPIxTXB is full                                                                                                                                                            |

|       | 0 = Transmit has started, SPIxTXB is empty                                                                                                                                                                   |

|       | Standard Buffer Mode:                                                                                                                                                                                        |

|       | Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB.<br>Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.                |

|       | Enhanced Buffer Mode:                                                                                                                                                                                        |

|       | Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write |

|       | operation.                                                                                                                                                                                                   |

| bit 0 | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                  |

|       | 1 = Receive is complete, SPIxRXB is full                                                                                                                                                                     |

|       | 0 = Receive is incomplete, SPIxRXB is empty                                                                                                                                                                  |

|       | Standard Buffer Mode:                                                                                                                                                                                        |

|       | Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically<br>cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.                               |

|       | Enhanced Buffer Mode:                                                                                                                                                                                        |

|       | Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread                                                                                                    |

|       | buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.                                                                                           |

# dsPIC33EPXXGS50X FAMILY

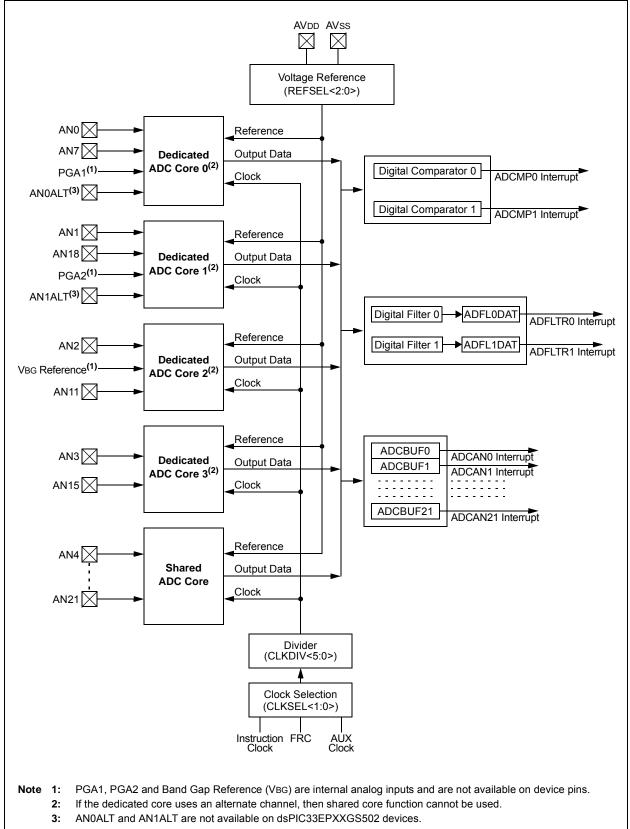

# REGISTER 19-21: ADMOD1L: ADC INPUT MODE CONTROL REGISTER 1 LOW

| U-0      | U-0    | U-0    | U-0    | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------|--------|--------|--------|--------|--------|--------|--------|

| —        | —      | —      | —      | DIFF21 | SIGN21 | DIFF20 | SIGN20 |

| bit 15   |        | •      | •      |        |        |        | bit 8  |

|          |        |        |        |        |        |        |        |

| R/W-0    | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| DIFF19   | SIGN19 | DIFF18 | SIGN18 | DIFF17 | SIGN17 | DIFF16 | SIGN16 |

| bit 7    |        |        | •      |        |        |        | bit 0  |

|          |        |        |        |        |        |        |        |

| Legend:  |        |        |        |        |        |        |        |

| <u> </u> | ,      |        |        |        |        |        |        |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-1(odd) DIFF<21:16>: Differential-Mode for Corresponding Analog Inputs bits

1 = Channel is differential

0 = Channel is single-ended

bit 10-0 (even) SIGN<21:16>: Output Data Sign for Corresponding Analog Inputs bits

1 = Channel output data is signed

0 = Channel output data is unsigned

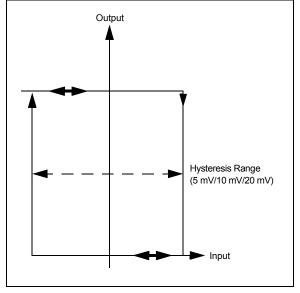

# 20.6 Hysteresis

An additional feature of the module is hysteresis control. Hysteresis can be enabled or disabled and its amplitude can be controlled by the HYSSEL<1:0> bits in the CMPxCON register. Three different values are available: 5 mV, 10 mV and 20 mV. It is also possible to select the edge (rising or falling) to which hysteresis is to be applied.

Hysteresis control prevents the comparator output from continuously changing state because of small perturbations (noise) at the input (see Figure 20-2).

# 20.7 Analog Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 20.7.1 KEY RESOURCES

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

| DC CHARACTERISTICS |        |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |     |   |                                                                                                                    |  |

|--------------------|--------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|--------------------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                              | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                         |   |     |   |                                                                                                                    |  |

| DO10 Vol           |        | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                                                                                                                                                                         |   | 0.4 | V |                                                                                                                    |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | —                                                                                                                                                                                                                                                                                       | _ | 0.4 | V | $V_{DD}$ = 3.3V,<br>IOL $\leq$ 12 mA, -40°C $\leq$ TA $\leq$ +85°C,<br>IOL $\leq$ 8 mA, +85°C $<$ TA $\leq$ +125°C |  |

| DO20               | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                                                                     | _ | _   | V | IOH ≥ -10 mA, VDD = 3.3V                                                                                           |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                                                                                                                                                                     |   |     | V | IOH $\ge$ -15 mA, VDD = 3.3V                                                                                       |  |

| DO20A              | Voh1   | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | _ | _   | V | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                              |  |

|                    |        |                                                             | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | - | _   |   | $IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                               |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                  | _ | -   |   | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                               |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5 <b>(1)</b>                                                                                                                                                                                                                                                                          | _ | —   | V | $IOH \ge -22 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                               |  |

|                    |        |                                                             | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                      |   | _   |   | IOH $\geq$ -18 mA, VDD = 3.3V                                                                                      |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                  | _ | _   |   | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                      |  |

## TABLE 26-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes RA0-RA2, RB0-RB1, RB9-RB10, RC1-RC2, RC9-RC10, RC12 and RD7 pins.

3: Includes all I/O pins that are not 4x driver pins (see Note 2).

#### TABLE 26-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |      |       |                        |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|-------|------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                          | Min. <sup>(2)</sup> | Тур. | Max. | Units | Conditions             |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low                                                                                                                                                                                                                                              | 2.65                | _    | 2.95 | V     | VDD<br>(Notes 2 and 3) |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, PGAs and comparators) may have degraded performance.

2: Parameters are for design guidance only and are not tested in manufacturing.

**3:** The VBOR specification is relative to VDD.

### TABLE 26-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$            |      |                                                |     |     |                    |

|--------------------|--------|------------------------------------------------------------------|------|------------------------------------------------|-----|-----|--------------------|

| Param<br>No.       | Symbol | Characteristic                                                   | Min. | Min. Typ. <sup>(1)</sup> Max. Units Conditions |     |     | Conditions         |

| OS50               | Fplli  | PLL Voltage Controlled Oscillator<br>(VCO) Input Frequency Range | 0.8  | _                                              | 8.0 | MHz | ECPLL, XTPLL modes |

| OS51               | Fvco   | On-Chip VCO System Frequency                                     | 120  | —                                              | 340 | MHz |                    |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                    | 0.9  | 1.5                                            | 3.1 | ms  |                    |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                           | -3   | 0.5                                            | 3   | %   |                    |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases, or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if Fosc = 120 MHz and the SPIx bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

#### TABLE 26-19: AUXILIARY PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |                    |     |       |            |  |

|--------------------|--------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                                    |                                                                                                                                                                                                                                                                                       | Min | Typ <sup>(1)</sup> | Max | Units | Conditions |  |

| OS56               | Fhpout | On-Chip 16x PLL CCO<br>Frequency                  |                                                                                                                                                                                                                                                                                       | 112 | 118                | 120 | MHz   |            |  |

| OS57               | Fhpin  | On-Chip 16x PLL Phase<br>Detector Input Frequency |                                                                                                                                                                                                                                                                                       | 7.0 | 7.37               | 7.5 | MHz   |            |  |

| OS58               | Tsu    | Frequency Generator Lock<br>Time                  |                                                                                                                                                                                                                                                                                       | _   | _                  | 10  | μs    |            |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested in manufacturing.

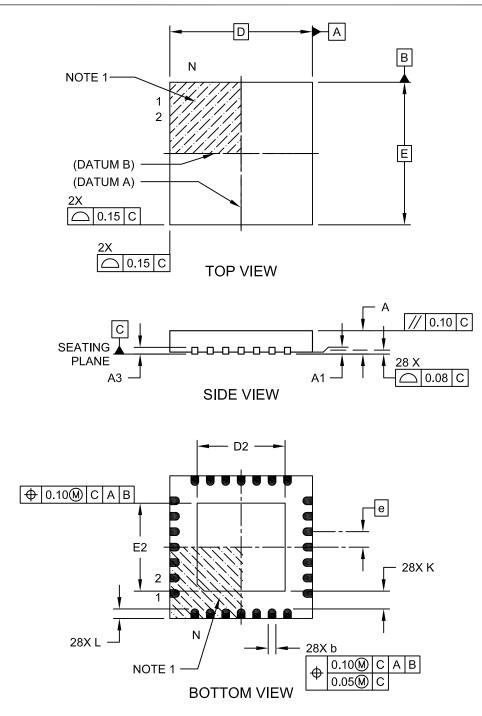

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2