Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C                                                                   |

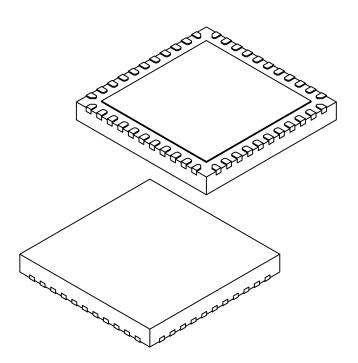

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs504-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin I   | Name <sup>(1)</sup>      | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                   |  |  |  |  |

|---------|--------------------------|-------------|----------------|-----|-------------------------------------------------------------------------------|--|--|--|--|

| MCLR    |                          | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |  |  |  |  |

| AVDD    |                          | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.  |  |  |  |  |

| AVss    |                          | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times. |  |  |  |  |

| Vdd     |                          | Р           | _              | No  | Positive supply for peripheral logic and I/O pins.                            |  |  |  |  |

| VCAP    |                          | Р           | _              | No  | CPU logic filter capacitor connection.                                        |  |  |  |  |

| Vss     |                          | Р           |                | No  | Ground reference for logic and I/O pins.                                      |  |  |  |  |

| Legend: | CMOS = CM<br>ST = Schmit |             |                |     |                                                                               |  |  |  |  |

PPS = Peripheral Pin Select

TTL = TTL input buffer

1: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**2:** These pins are dedicated on 64-pin devices.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXGS50X family requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins regardless if ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

**CORCON: CORE CONTROL REGISTER**

REGISTER 3-2:

| R/W-0           | U-0                                                                                                              | R/W-0                              | R/W-0                             | R/W-0                | R-0             | R-0             | R-0   |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------|----------------------|-----------------|-----------------|-------|--|--|--|

| VAR             |                                                                                                                  | US1                                | US0                               | EDT <sup>(1)</sup>   | DL2             | DL1             | DL0   |  |  |  |

| bit 15          |                                                                                                                  |                                    |                                   |                      |                 |                 | bit   |  |  |  |

| R/W-0           | R/W-0                                                                                                            | R/W-1                              | R/W-0                             | R/C-0                | R-0             | R/W-0           | R/W-0 |  |  |  |

| SATA            | SATB                                                                                                             | SATDW                              | ACCSAT                            | IPL3 <sup>(2)</sup>  | SFA             | RND             | IF    |  |  |  |

| bit 7           | OAID                                                                                                             | OAIDW                              | ACCOAL                            | 11 2011              |                 | THE             | bit   |  |  |  |

| Legend:         |                                                                                                                  | C = Clearable                      | - hit                             |                      |                 |                 |       |  |  |  |

| R = Readable    | bit                                                                                                              | W = Writable                       |                                   | U = Unimpler         | mented bit, rea | d as '0'        |       |  |  |  |

| -n = Value at F |                                                                                                                  | '1' = Bit is set                   |                                   | '0' = Bit is cle     |                 | x = Bit is unkn | iown  |  |  |  |

|                 |                                                                                                                  | 1 - Dit 13 301                     | •                                 |                      | arcu            |                 | lowin |  |  |  |

| bit 15          |                                                                                                                  | •                                  | ocessing Later                    |                      |                 |                 |       |  |  |  |

|                 |                                                                                                                  | • •                                | essing is enab<br>sing is enabled |                      |                 |                 |       |  |  |  |

| bit 14          | Unimplemen                                                                                                       | ted: Read as '                     | 0'                                |                      |                 |                 |       |  |  |  |

| bit 13-12       | -                                                                                                                |                                    | igned/Signed                      | Control bits         |                 |                 |       |  |  |  |

|                 | 11 = Reserve                                                                                                     |                                    | 0 0                               |                      |                 |                 |       |  |  |  |

|                 | 10 = DSP engine multiplies are mixed-sign                                                                        |                                    |                                   |                      |                 |                 |       |  |  |  |

|                 |                                                                                                                  | gine multiplies<br>gine multiplies |                                   |                      |                 |                 |       |  |  |  |

| bit 11          | EDT: Early DO                                                                                                    | Loop Termina                       | ation Control b                   | it(1)                |                 |                 |       |  |  |  |

|                 | <ul> <li>1 = Terminates executing DO loop at the end of current loop iteration</li> <li>0 = No effect</li> </ul> |                                    |                                   |                      |                 |                 |       |  |  |  |

| bit 10-8        | DL<2:0>: DO Loop Nesting Level Status bits                                                                       |                                    |                                   |                      |                 |                 |       |  |  |  |

|                 | 111 <b>= 7</b> do <b>lo</b>                                                                                      | ops are active                     |                                   |                      |                 |                 |       |  |  |  |

|                 | •                                                                                                                |                                    |                                   |                      |                 |                 |       |  |  |  |

|                 | •                                                                                                                |                                    |                                   |                      |                 |                 |       |  |  |  |

|                 | 001 = 1 DO lo                                                                                                    | op is active<br>ops are active     |                                   |                      |                 |                 |       |  |  |  |

| bit 7           |                                                                                                                  | •                                  |                                   |                      |                 |                 |       |  |  |  |

|                 | SATA: ACCA Saturation Enable bit<br>1 = Accumulator A saturation is enabled                                      |                                    |                                   |                      |                 |                 |       |  |  |  |

|                 |                                                                                                                  | itor A saturatio                   |                                   |                      |                 |                 |       |  |  |  |

| bit 6           | SATB: ACCB                                                                                                       | Saturation En                      | able bit                          |                      |                 |                 |       |  |  |  |

|                 |                                                                                                                  | itor B saturatio                   |                                   |                      |                 |                 |       |  |  |  |

| bit 5           | SATDW: Data                                                                                                      | a Space Write                      | from DSP Eng                      | ine Saturation       | Enable bit      |                 |       |  |  |  |

|                 | 1 = Data Spac                                                                                                    | ce write satura                    | tion is enabled                   | l                    |                 |                 |       |  |  |  |

| bit 4           | -                                                                                                                |                                    | ration Mode S                     |                      |                 |                 |       |  |  |  |

|                 |                                                                                                                  | ration (super s<br>ration (normal  |                                   |                      |                 |                 |       |  |  |  |

| L:1 0           |                                                                                                                  | •                                  | Level Status b                    | <sub>oit 3</sub> (2) |                 |                 |       |  |  |  |

| bit 3           |                                                                                                                  | contraped monity                   |                                   |                      |                 |                 |       |  |  |  |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### 4.3.5 X AND Y DATA SPACES

The dsPIC33EPXXGS50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY. N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.4 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 4.4.1 KEY RESOURCES

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 5.6 Control Registers

Five SFRs are used to write and erase the program Flash memory: NVMCON, NVMKEY, NVMADR, NVMADRU and NVMSRCADR/H.

The NVMCON register (Register 5-1) selects the operation to be performed (page erase, word/row program, Inactive Partition erase), initiates the program or erase cycle and is used to determine the Active Partition in Dual Partition modes.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. There are two NVM Address registers: NVMADRU and NVMADR. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word/row for programming operations, or the selected page for erase operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA.

For row programming operation, data to be written to program Flash memory is written into data memory space (RAM) at an address defined by the NVMSRCADR register (location of first element in row programming data).

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

NOTES:

#### 10.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-19). Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

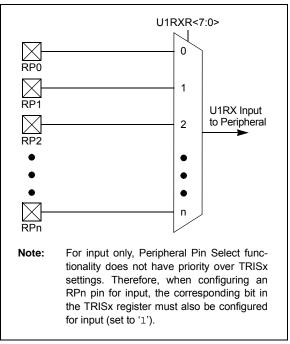

For example, Figure 10-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 10-2: REMAPPABLE INPUT FOR U1RX

### 10.4.4.1 Virtual Connections

The dsPIC33EPXXGS50X devices support six virtual RPn pins (RP176-RP181), which are identical in functionality to all other RPn pins, with the exception of pinouts. These six pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP176 and the PWM Fault input can be configured for RP176 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

### REGISTER 10-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| OCFAR7 | OCFAR6 | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 OCFAR<7:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180

00000001 = Input tied to RP1 00000000 = Input tied to Vss

| R/W-0         | R/W-0                                                                | R/W-0                                                                                        | R/W-0                    | R/W-0                                                                         | R/W-0          | R/W-0    | R/W-0  |  |

|---------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------|----------------|----------|--------|--|

| FLT4R7        | FLT4R6                                                               | FLT4R5                                                                                       | FLT4R4                   | FLT4R3                                                                        | FLT4R2         | FLT4R1   | FLT4R0 |  |

| bit 15        |                                                                      |                                                                                              |                          | ·                                                                             |                |          | bit 8  |  |

|               |                                                                      |                                                                                              |                          |                                                                               |                |          |        |  |

| R/W-0         | R/W-0                                                                | R/W-0                                                                                        | R/W-0                    | R/W-0                                                                         | R/W-0          | R/W-0    | R/W-0  |  |

| FLT3R7        | FLT3R6                                                               | FLT3R5                                                                                       | FLT3R4                   | FLT3R3                                                                        | FLT3R2         | FLT3R1   | FLT3R0 |  |

| bit 7         |                                                                      |                                                                                              |                          |                                                                               |                | ·        | bit (  |  |

| Legend:       |                                                                      |                                                                                              |                          |                                                                               |                |          |        |  |

| R = Readable  | > hit                                                                | W = Writable                                                                                 | hit                      | U = Unimpler                                                                  | mented hit rea | d as 'O' |        |  |

| -n = Value at |                                                                      | '1' = Bit is set                                                                             |                          | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unknown |                |          |        |  |

|               |                                                                      |                                                                                              |                          |                                                                               |                |          |        |  |

| bit 15-8      | 10110101 =<br>10110100 =<br>•<br>•<br>•<br>000000001 =<br>00000000 = | : Assign PWM<br>Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to VS | P181<br>P180<br>P1<br>SS |                                                                               | Ţ              |          |        |  |

| bit 7-0       | 10110101 =<br>10110100 =<br>00000001 =                               | : Assign PWM<br>Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to VS | P181<br>P180<br>P1       | ) to the Corresp                                                              | oonding KPn Pi | n dits   |        |  |

#### REGISTER 10-9: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13

## 14.2 Output Compare Control Registers

#### REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0        | U-0                                                        | R/W-0                                                                | R/W-0                         | R/W-0                              | R/W-0             | U-0              | U-0           |  |  |  |

|------------|------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------|------------------------------------|-------------------|------------------|---------------|--|--|--|

| _          | _                                                          | OCSIDL                                                               | OCTSEL2                       | OCTSEL1                            | OCTSEL0           |                  | _             |  |  |  |

| bit 15     |                                                            |                                                                      | •                             |                                    |                   |                  | bit           |  |  |  |

|            |                                                            |                                                                      |                               |                                    |                   |                  |               |  |  |  |

| R/W-0      | U-0                                                        | U-0                                                                  | R/W-0, HSC                    | R/W-0                              | R/W-0             | R/W-0            | R/W-0<br>OCM0 |  |  |  |

| ENFLTA     | —                                                          | _                                                                    | - OCFLTA TRIGMODE OCM2 OCM1 O |                                    |                   |                  |               |  |  |  |

| bit 7      |                                                            |                                                                      |                               |                                    |                   |                  | bit           |  |  |  |

| Legend:    |                                                            | HSC = Hardw                                                          | are Settable/Cl               | earable bit                        |                   |                  |               |  |  |  |

| R = Reada  | ble bit                                                    | W = Writable I                                                       | oit                           | U = Unimplem                       | ented bit, read a | as '0'           |               |  |  |  |

| -n = Value | at POR                                                     | '1' = Bit is set                                                     |                               | '0' = Bit is clea                  | red               | x = Bit is unkne | own           |  |  |  |

|            |                                                            |                                                                      |                               |                                    |                   |                  |               |  |  |  |

| bit 15-14  | -                                                          | nted: Read as '                                                      |                               |                                    |                   |                  |               |  |  |  |

| bit 13     |                                                            | tput Compare x                                                       | •                             |                                    |                   |                  |               |  |  |  |

|            | 1 = Output Compare x halts in CPU Idle mode                |                                                                      |                               |                                    |                   |                  |               |  |  |  |

|            | 0 = Output Compare x continues to operate in CPU Idle mode |                                                                      |                               |                                    |                   |                  |               |  |  |  |

| bit 12-10  |                                                            | 0>: Output Com                                                       | ipare x Clock S               | elect bits                         |                   |                  |               |  |  |  |

|            | 111 = Periph<br>110 = Reser                                | neral clock (FP)                                                     |                               |                                    |                   |                  |               |  |  |  |

|            | 101 = Reser                                                |                                                                      |                               |                                    |                   |                  |               |  |  |  |

|            | 100 = T1CL                                                 | K is the clock so                                                    | ource of the OC               | x (only the sync                   | hronous clock i   | s supported)     |               |  |  |  |

|            |                                                            | K is the clock source of the OCx                                     |                               |                                    |                   |                  |               |  |  |  |

|            |                                                            | K is the clock source of the OCx<br>K is the clock source of the OCx |                               |                                    |                   |                  |               |  |  |  |

|            |                                                            | K is the clock so                                                    |                               |                                    |                   |                  |               |  |  |  |

| bit 9-8    | Unimplemer                                                 | nted: Read as '                                                      | 0'                            |                                    |                   |                  |               |  |  |  |

| bit 7      | -                                                          | ult A Input Enat                                                     |                               |                                    |                   |                  |               |  |  |  |

|            |                                                            | Compare Fault A                                                      |                               | is enabled                         |                   |                  |               |  |  |  |

|            | 0 = Output C                                               | Compare Fault A                                                      | A input (OCFA)                | is disabled                        |                   |                  |               |  |  |  |

| bit 6-5    | Unimplemer                                                 | nted: Read as '                                                      | 0'                            |                                    |                   |                  |               |  |  |  |

| bit 4      | OCFLTA: PV                                                 | VM Fault A Con                                                       | dition Status bi              | t                                  |                   |                  |               |  |  |  |

|            |                                                            |                                                                      |                               | in has occurred<br>A pin has occur |                   |                  |               |  |  |  |

| bit 3      |                                                            | Trigger Status                                                       |                               | -                                  |                   |                  |               |  |  |  |

|            |                                                            |                                                                      |                               |                                    | OCxTMR or in      | software         |               |  |  |  |

|            |                                                            | AT is cleared or                                                     | ,                             |                                    |                   |                  |               |  |  |  |

| Note 1.    | OCxR and OC                                                | xRS are double                                                       | -buffered in P\               | MM mode only                       |                   |                  |               |  |  |  |

Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

#### **REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output is set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output is set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

#### **REGISTER 15-19: TRGCONX: PWMx TRIGGER CONTROL REGISTER (x = 1 to 5)**

| TRGDIV3<br>bit 15  | TRGDIV2                                                                                                                                                                     | TRGDIV1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TRGDIV0          | _                   |                  |                  | _         |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|------------------|------------------|-----------|--|--|--|--|

| bit 15             |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                     |                  |                  |           |  |  |  |  |

|                    |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L                |                     |                  | I                | bit 8     |  |  |  |  |

|                    |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                     |                  |                  |           |  |  |  |  |

| R/W-0              | U-0                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0            | R/W-0               | R/W-0            | R/W-0            | R/W-0     |  |  |  |  |

| DTM <sup>(1)</sup> | <u> </u>                                                                                                                                                                    | TRGSTRT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TRGSTRT4         | TRGSTRT3            | TRGSTRT2         | TRGSTRT1         | TRGSTRT0  |  |  |  |  |

| bit 7              |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                     |                  |                  | bit (     |  |  |  |  |

| Legend:            |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                     |                  |                  |           |  |  |  |  |

| R = Readable       | e bit                                                                                                                                                                       | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit              | U = Unimplem        | nented bit, read | l as '0'         |           |  |  |  |  |

| -n = Value at      | POR                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | '0' = Bit is clea   | ared             | x = Bit is unkn  | own       |  |  |  |  |

|                    |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                     |                  |                  |           |  |  |  |  |

| bit 15-12          | TRGDIV<3:0                                                                                                                                                                  | Trigger # Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | tput Divider bit | S                   |                  |                  |           |  |  |  |  |

|                    | 1111 <b>= Trigg</b> e                                                                                                                                                       | er output for eve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ery 16th trigge  | revent              |                  |                  |           |  |  |  |  |

|                    |                                                                                                                                                                             | er output for eve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                     |                  |                  |           |  |  |  |  |