Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C                                                                   |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs504-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

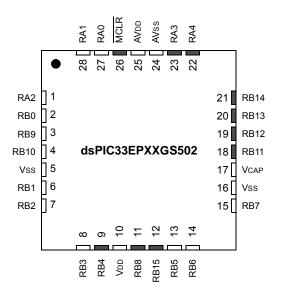

#### **Pin Diagrams (Continued)**

#### 28-Pin QFN-S, UQFN

| Pin | Pin Function                              | Pin | Pin Function                 |

|-----|-------------------------------------------|-----|------------------------------|

| 1   | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         | 15  | PGEC1/AN21/SDA1/RP39/RB7     |

| 2   | AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0           | 16  | Vss                          |

| 3   | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            | 17  | VCAP                         |

| 4   | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10           | 18  | TMS/PWM3H/ <b>RP43</b> /RB11 |

| 5   | Vss                                       | 19  | TCK/PWM3L/RP44/RB12          |

| 6   | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  | 20  | PWM2H/ <b>RP45</b> /RB13     |

| 7   | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/RP34/RB2 | 21  | PWM2L/ <b>RP46</b> /RB14     |

| 8   | PGED2/AN18/DACOUT1/INT0/ <b>RP35</b> /RB3 | 22  | PWM1H/RA4                    |

| 9   | PGEC2/ADTRG31/EXTREF1/RP36/RB4            | 23  | PWM1L/RA3                    |

| 10  | Vdd                                       | 24  | AVss                         |

| 11  | PGED3/SDA2/FLT31/RP40/RB8                 | 25  | AVdd                         |

| 12  | PGEC3/SCL2/ <b>RP47</b> /RB15             | 26  | MCLR                         |

| 13  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         | 27  | AN0/PGA1P1/CMP1A/RA0         |

| 14  | PGED1/TDI/AN20/SCL1/ <b>RP38</b> /RB6     | 28  | AN1/PGA1P2/PGA2P1/CMP1B/RA1  |

Legend: Shaded pins are up to 5 VDC tolerant. RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin I   | Name <sup>(1)</sup>      | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                   |                |  |  |  |

|---------|--------------------------|-------------|----------------|-----|-------------------------------------------------------------------------------|----------------|--|--|--|

| MCLR    |                          | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |                |  |  |  |

| AVDD    |                          | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.  |                |  |  |  |

| AVss    |                          | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times. |                |  |  |  |

| Vdd     |                          | Р           | _              | No  | Positive supply for peripheral logic and I/O pins.                            |                |  |  |  |

| VCAP    |                          | Р           | _              | No  | CPU logic filter capacitor connection.                                        |                |  |  |  |

| Vss     |                          | Р           |                | No  | Ground reference for logic and I/O pins.                                      |                |  |  |  |

| Legend: | CMOS = CM<br>ST = Schmit |             |                |     |                                                                               | Power<br>Input |  |  |  |

PPS = Peripheral Pin Select

TTL = TTL input buffer

1: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**2:** These pins are dedicated on 64-pin devices.

**CORCON: CORE CONTROL REGISTER**

REGISTER 3-2:

| R/W-0           | U-0                            | R/W-0                              | R/W-0                             | R/W-0                | R-0             | R-0             | R-0   |

|-----------------|--------------------------------|------------------------------------|-----------------------------------|----------------------|-----------------|-----------------|-------|

| VAR             |                                | US1                                | US0                               | EDT <sup>(1)</sup>   | DL2             | DL1             | DL0   |

| bit 15          |                                |                                    |                                   |                      |                 |                 | bit   |

| R/W-0           | R/W-0                          | R/W-1                              | R/W-0                             | R/C-0                | R-0             | R/W-0           | R/W-0 |

| SATA            | SATB                           | SATDW                              | ACCSAT                            | IPL3 <sup>(2)</sup>  | SFA             | RND             | IF    |

| bit 7           | OAID                           | OAIDW                              | ACCOAL                            | 11 2011              |                 | THE             | bit   |

| Legend:         |                                | C = Clearable                      | - hit                             |                      |                 |                 |       |

| R = Readable    | bit                            | W = Writable                       |                                   | U = Unimpler         | mented bit, rea | d as '0'        |       |

| -n = Value at F |                                | '1' = Bit is set                   |                                   | '0' = Bit is cle     |                 | x = Bit is unkn | iown  |

|                 |                                | 1 - Dit 13 301                     | •                                 |                      | arcu            |                 | lowin |

| bit 15          |                                | •                                  | ocessing Later                    |                      |                 |                 |       |

|                 |                                | · ·                                | essing is enab<br>sing is enabled |                      |                 |                 |       |

| bit 14          | Unimplemen                     | ted: Read as '                     | 0'                                |                      |                 |                 |       |

| bit 13-12       | -                              |                                    | igned/Signed                      | Control bits         |                 |                 |       |

|                 | 11 = Reserve                   |                                    | 0 0                               |                      |                 |                 |       |

|                 |                                |                                    | are mixed-sigi                    | า                    |                 |                 |       |

|                 |                                | gine multiplies<br>gine multiplies |                                   |                      |                 |                 |       |

| bit 11          | EDT: Early DO                  | Loop Termina                       | ation Control b                   | it(1)                |                 |                 |       |

|                 | 1 = Terminate<br>0 = No effect | es executing Do                    | o loop at the e                   | nd of current lo     | oop iteration   |                 |       |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                       | Level Status bi                   | ts                   |                 |                 |       |

|                 | 111 <b>= 7</b> do <b>lo</b>    | ops are active                     |                                   |                      |                 |                 |       |

|                 | •                              |                                    |                                   |                      |                 |                 |       |

|                 | •                              |                                    |                                   |                      |                 |                 |       |

|                 | 001 = 1 DO lo                  | op is active<br>ops are active     |                                   |                      |                 |                 |       |

| bit 7           |                                | Saturation En                      |                                   |                      |                 |                 |       |

|                 |                                | Itor A saturatio                   |                                   |                      |                 |                 |       |

|                 |                                | itor A saturatio                   |                                   |                      |                 |                 |       |

| bit 6           | SATB: ACCB                     | Saturation En                      | able bit                          |                      |                 |                 |       |

|                 |                                | itor B saturatio                   |                                   |                      |                 |                 |       |

| bit 5           | SATDW: Data                    | a Space Write                      | from DSP Eng                      | ine Saturation       | Enable bit      |                 |       |

|                 | 1 = Data Spac                  | ce write satura                    | tion is enabled                   | l                    |                 |                 |       |

| bit 4           | •                              |                                    | ration Mode S                     |                      |                 |                 |       |

|                 |                                | ration (super s<br>ration (normal  |                                   |                      |                 |                 |       |

| L:1 0           |                                | •                                  | Level Status b                    | <sub>oit 3</sub> (2) |                 |                 |       |

| bit 3           |                                | contraped monity                   |                                   |                      |                 |                 |       |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXGS50X family architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

### 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXGS50X family devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.9 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to permit access to calibration data and Device ID sections of the configuration memory space.

The program memory maps for the dsPIC33EP16/ 32GS50X and dsPIC33EP64GS50X devices not operating in Dual Partition mode, are shown in Figure 4-1 through Figure 4-3.

The dsPIC33EP64GS50X devices can operate in a Dual Partition Flash Program Memory mode, where the user program Flash memory is arranged as two separate address spaces, one for each of the Flash partitions. The Active Partition always starts at address, 0x000000, and contains half of the available Flash memory (32K). The Inactive Partition always starts at address, 0x400000, and implements the remaining half of Flash memory. As shown in Figure 4-4, the Active and Inactive Partitions are identical and both contain unique copies of the Reset vector, Interrupt Vector Tables (IVT and AIVT if enabled) and the Flash Configuration Words.

#### 4.2 Unique Device Identifier (UDID)

All (16-bit devices) family devices are individually encoded during final manufacturing with a Unique Device Identifier or UDID. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is a requirement. It may also be used by the application manufacturer for any number of things that may require unique identification, such as:

- Tracking the device

- Unique serial number

- Unique security key

The UDID comprises five 24-bit program words. When taken together, these fields form a unique 120-bit identifier.

The UDID is stored in five read-only locations, located between 800F00h and 800F08h in the device configuration space. Table 4-1 lists the addresses of the identifier words and shows their contents.

| Name  | Address | Bits 23:16  | Bits 15:8   | Bits 7:0 |  |  |  |

|-------|---------|-------------|-------------|----------|--|--|--|

| UDID1 | 800F00  | UDID Word 1 |             |          |  |  |  |

| UDID2 | 800F02  | UDID Word 2 |             |          |  |  |  |

| UDID3 | 800F04  | U           | UDID Word 3 |          |  |  |  |

| UDID4 | 800F06  | UDID Word 4 |             |          |  |  |  |

| UDID5 | 800F08  | U           | DID Word 5  |          |  |  |  |

TABLE 4-1: UDID ADDRESSES

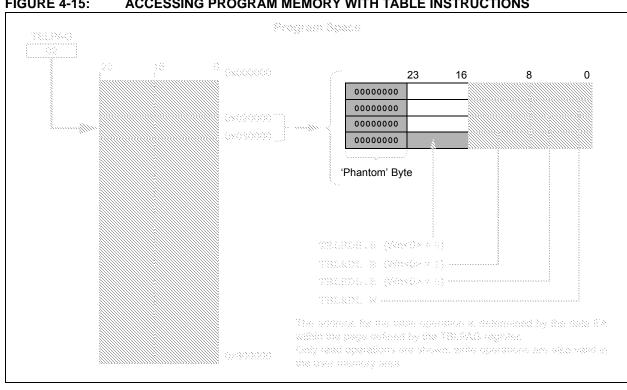

#### DATA ACCESS FROM PROGRAM 4.9.1 MEMORY USING TABLE **INSTRUCTIONS**

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### **FIGURE 4-15:** ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

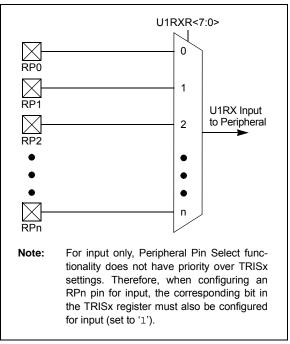

#### 10.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-19). Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 10-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 10-2: REMAPPABLE INPUT FOR U1RX

#### 10.4.4.1 Virtual Connections

The dsPIC33EPXXGS50X devices support six virtual RPn pins (RP176-RP181), which are identical in functionality to all other RPn pins, with the exception of pinouts. These six pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP176 and the PWM Fault input can be configured for RP176 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

#### 10.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 26-11 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 26.0 "Electrical Characteristics" of this data sheet. For example:

Vон = 2.4v @ Iон = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 27.0 "DC and AC Device Characteristics Graphs"** for additional information.

| R/W-0       | R/W-0           | R/W-0                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |

|-------------|-----------------|------------------------------------------|-------|-------------------|-----------------|--------------------|-------|

| IC2R7       | IC2R6           | IC2R5                                    | IC2R4 | IC2R3             | IC2R2           | IC2R1              | IC2R0 |

| bit 15      |                 |                                          |       |                   |                 |                    | bit 8 |

| R/W-0       | R/W-0           | R/W-0                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |

| IC1R7       | IC1R6           | IC1R5                                    | IC1R4 | IC1R3             | IC1R2           | IC1R1              | IC1R0 |

| pit 7       |                 |                                          |       |                   |                 |                    | bit ( |

| _egend:     |                 |                                          |       |                   |                 |                    |       |

| R = Readab  | ole bit         | W = Writable                             | bit   | U = Unimplem      | nented bit, rea | d as '0'           |       |

| n = Value a | t POR           | '1' = Bit is set                         |       | '0' = Bit is clea | ared            | x = Bit is unknown |       |

|             | 10110100 =<br>• | Input tied to RI                         | 2180  |                   |                 |                    |       |

|             |                 | = Input tied to RI<br>= Input tied to Vs |       |                   |                 |                    |       |

#### REGISTER 10-5: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

### 15.0 HIGH-SPEED PWM

Note: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM Module" (DS70000323) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The high-speed PWM module on dsPIC33EPXXGS50X devices supports a wide variety of PWM modes and output formats. This PWM module is ideal for power conversion applications, such as:

- AC/DC Converters

- DC/DC Converters

- Power Factor Correction

- Uninterruptible Power Supply (UPS)

- Inverters

- Battery Chargers

- Digital Lighting

#### 15.1 Features Overview

The high-speed PWM module incorporates the following features:

- Five PWMx Generators with Two Outputs per Generator

- · Two Master Time Base Modules

- Individual Time Base and Duty Cycle for Each PWM Output

- Duty Cycle, Dead Time, Phase Shift and a Frequency Resolution of 1.04 ns

- Independent Fault and Current-Limit Inputs

- Redundant Output

- True Independent Output

- Center-Aligned PWM mode

- Output Override Control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Dual Trigger from PWMx to Analog-to-Digital Converter (ADC)

- PWMxL and PWMxH Output Pin Swapping

- Independent PWMx Frequency, Duty Cycle and Phase-Shift Changes

- Enhanced Leading-Edge Blanking (LEB) Functionality

- PWM Capture Functionality

**Note:** Duty cycle, dead time, phase shift and frequency resolution is 8.32 ns in Center-Aligned PWM mode.

Figure 15-1 conceptualizes the PWM module in a simplified block diagram. Figure 15-2 illustrates how the module hardware is partitioned for each PWMx output pair for the Complementary PWM mode.

The PWM module contains five PWM generators. The module has up to 10 PWMx output pins: PWM1H/ PWM1L through PWM5H/PWM5L. For complementary outputs, these 10 I/O pins are grouped into high/low pairs.

#### 15.2 Feature Description

The PWM module is designed for applications that require:

- High resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode and Push-Pull mode outputs

- · The ability to create multiphase PWM outputs

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

Phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable.

Multiphase PWM is often used to improve DC/DC converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC converters are often operated in parallel, but phase shifted in time. A single PWM output, operating at 250 kHz, has a period of 4  $\mu$ s but an array of four PWM channels, staggered by 1  $\mu$ s each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

Variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50% and the power flow is controlled by varying the relative phase shift between the two PWM generators.

### 18.3 UART Control Registers

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                          | R/W-0                                                    | R/W-0                          | R/W-0                               | U-0                     | R/W-0                                                  | R/W-0         |

|-----------------------|------------------------------|----------------------------------------------------------|--------------------------------|-------------------------------------|-------------------------|--------------------------------------------------------|---------------|

| UARTEN <sup>(1)</sup> |                              | USIDL                                                    | IREN <sup>(2)</sup>            | RTSMD                               |                         | UEN1                                                   | UEN0          |

| bit 15                |                              |                                                          |                                | 1                                   |                         |                                                        | bit           |

|                       |                              |                                                          |                                |                                     |                         |                                                        |               |

| R/W-0, HC             | R/W-0                        | R/W-0, HC                                                | R/W-0                          | R/W-0                               | R/W-0                   | R/W-0                                                  | R/W-0         |

| WAKE                  | LPBACK                       | ABAUD                                                    | URXINV                         | BRGH                                | PDSEL1                  | PDSEL0                                                 | STSEL         |

| bit 7                 |                              |                                                          |                                |                                     |                         |                                                        | bit           |

| Legend:               |                              | HC = Hardwar                                             | e Clearable b                  | it                                  |                         |                                                        |               |

| R = Readabl           | e bit                        | W = Writable b                                           |                                | U = Unimplem                        | ented bit, read         | l as '0'                                               |               |

| -n = Value at         |                              | '1' = Bit is set                                         |                                | '0' = Bit is clea                   |                         | x = Bit is unkn                                        | own           |

| bit 15                | 1 = UARTx is                 |                                                          | ARTx pins are                  |                                     |                         | ed by UEN<1:0><br>UARTx power co                       |               |

| oit 14                |                              | ted: Read as '0                                          | ,                              |                                     |                         |                                                        |               |

| bit 13                | •                            | Tx Stop in Idle N                                        |                                |                                     |                         |                                                        |               |

|                       | 1 = Discontin                | •                                                        | eration when o                 | device enters Id                    | le mode                 |                                                        |               |

| pit 12                |                              | Encoder and De                                           |                                |                                     |                         |                                                        |               |

|                       |                              | oder and decod<br>oder and decod                         |                                |                                     |                         |                                                        |               |

| pit 11                | RTSMD: Mod                   | le Selection for                                         | UxRTS Pin bi                   | t                                   |                         |                                                        |               |

|                       |                              | in is in Simplex<br>in is in Flow Co                     |                                |                                     |                         |                                                        |               |

| oit 10                | Unimplemen                   | ted: Read as '0                                          | ,                              |                                     |                         |                                                        |               |

| oit 9-8               | UEN<1:0>: U                  | ARTx Pin Enab                                            | le bits                        |                                     |                         |                                                        |               |

|                       | 10 = UxTX, U<br>01 = UxTX, U | JxRX, <u>UxCTS</u> ai<br>JxRX and UxRT<br>nd UxRX pins a | nd UxRTS pin<br>S pins are ena | s are enabled a abled and used;     | nd used<br>UxCTS pin is | controlled by PC<br>controlled by PC<br>BCLKx pins are | ORT latches   |

| bit 7                 | WAKE: Wake                   | -up on Start Bit                                         | Detect During                  | g Sleep Mode E                      | nable bit               |                                                        |               |

|                       | in hardwa                    | ontinues to sam<br>are on the follow<br>-up is enabled   |                                |                                     | generated on            | the falling edge;                                      | bit is cleare |

| oit 6                 |                              | RTx Loopback                                             | Mode Select I                  | bit                                 |                         |                                                        |               |

|                       | 1 = Enables                  | Loopback mode<br>k mode is disab                         | :                              |                                     |                         |                                                        |               |

| "0                    |                              | Family Referen                                           |                                | r Transmitter (<br>r information on |                         | 0000582) in the<br>JARTx module fo                     | or receive or |

|                       |                              |                                                          | the 16y BPC                    | modo (BBCH -                        | 0)                      |                                                        |               |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 19-4: ADCON2H: ADC CONTROL REGISTER 2 HIGH

| R-0, HSC | R-0, HSC | r-0 | r-0 | r-0 | r-0 | R/W-0    | R/W-0    |

|----------|----------|-----|-----|-----|-----|----------|----------|

| REFRDY   | REFERR   | —   | —   | —   | —   | SHRSAMC9 | SHRSAMC8 |

| bit 15   |          |     |     |     |     |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SHRSAMC7 | SHRSAMC6 | SHRSAMC5 | SHRSAMC4 | SHRSAMC3 | SHRSAMC2 | SHRSAMC1 | SHRSAMC0 |

| bit 7    | ·        |          |          |          |          |          | bit 0    |

| Legend:           | r = Reserved bit | U = Unimplemented bit, read as '0'      |  |

|-------------------|------------------|-----------------------------------------|--|

| R = Readable bit  | W = Writable bit | HSC = Hardware Settable/Clearable bit   |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |

| bit 15    | <b>REFRDY:</b> Band Gap and Reference Voltage Ready Flag bit<br>1 = Band gap is ready<br>0 = Band gap is not ready                                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | <b>REFERR:</b> Band Gap or Reference Voltage Error Flag bit<br>1 = Band gap was removed after the ADC module was enabled (ADON = 1)<br>0 = No band gap error was detected                                         |

| bit 13-10 | Reserved: Maintain as '0'                                                                                                                                                                                         |

| bit 9-0   | <pre>SHRSAMC&lt;9:0&gt;: Shared ADC Core Sample Time Selection bits These bits specify the number of shared ADC Core Clock Periods (TADCORE) for the shared ADC core sample time. 1111111111 = 1025 TADCORE</pre> |

#### **REGISTER 19-11:** ADCOREXL: DEDICATED ADC CORE x CONTROL REGISTER LOW (x = 0 to 3)

| U-0               | U-0   | U-0              | U-0   | U-0                                | U-0   | R/W-0              | R/W-0  |

|-------------------|-------|------------------|-------|------------------------------------|-------|--------------------|--------|

| —                 | _     | —                | _     | —                                  |       | SAMO               | C<9:8> |

| bit 15            |       |                  |       |                                    |       |                    | bit 8  |

|                   |       |                  |       |                                    |       |                    |        |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0  |

|                   |       |                  | SAM   | C<7:0>                             |       |                    |        |

| bit 7             |       |                  |       |                                    |       |                    | bit (  |

| Legend:           |       |                  |       |                                    |       |                    |        |

| R = Readable      | bit   | W = Writable I   | oit   | U = Unimplemented bit, read as '0' |       |                    |        |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |        |

bit 15-10 Unimplemented: Read as '0'

### 22.3 Current Source Control Register

#### REGISTER 22-1: ISRCCON: CONSTANT-CURRENT SOURCE CONTROL REGISTER

| R/W-0                 | U-0                                                                                                                                                                                                                                                                                                | U-0                                                                | U-0                 | U-0              | R/W-0            | R/W-0              | R/W-0    |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|------------------|------------------|--------------------|----------|--|--|

| ISRCEN                | _                                                                                                                                                                                                                                                                                                  |                                                                    | —                   | _                | OUTSEL2          | OUTSEL1            | OUTSEL0  |  |  |

| bit 15                |                                                                                                                                                                                                                                                                                                    |                                                                    |                     | •                |                  |                    | bit 8    |  |  |

| U-0                   | U-0                                                                                                                                                                                                                                                                                                | R/W-0                                                              | R/W-0               | R/W-0            | R/W-0            | R/W-0              | R/W-0    |  |  |

| 0-0                   | 0-0                                                                                                                                                                                                                                                                                                | ISRCCAL5                                                           | ISRCCAL4            | ISRCCAL3         | ISRCCAL2         | ISRCCAL1           | ISRCCAL0 |  |  |

| <br>bit 7             |                                                                                                                                                                                                                                                                                                    | ISRUCALS                                                           | ISRUUAL4            | ISRUUALS         | ISRUCALZ         | ISRCCALT           | bit (    |  |  |

|                       |                                                                                                                                                                                                                                                                                                    |                                                                    |                     |                  |                  |                    | DILL     |  |  |

| Legend:               |                                                                                                                                                                                                                                                                                                    |                                                                    |                     |                  |                  |                    |          |  |  |

| R = Readabl           | e bit                                                                                                                                                                                                                                                                                              | W = Writable                                                       | bit                 | U = Unimpler     | nented bit, read | 1 as '0'           |          |  |  |

| -n = Value at         | POR                                                                                                                                                                                                                                                                                                | '1' = Bit is set                                                   |                     | '0' = Bit is cle | ared             | x = Bit is unknown |          |  |  |

|                       | Unimplemented: Read as '0'<br>OUTSEL<2:0>: Output Constant-Current Select bits                                                                                                                                                                                                                     |                                                                    |                     |                  |                  |                    |          |  |  |

| bit 14-11<br>bit 10-8 | 0 = Current s<br>Unimplemen<br>OUTSEL<2:0<br>111 = Reserv<br>110 = Reserv<br>101 = Reserv                                                                                                                                                                                                          | <b>)&gt;:</b> Output Con<br>ved<br>ved                             | o'<br>stant-Current | Select bits      |                  |                    |          |  |  |

|                       | 011 = Input p<br>010 = Input p<br>001 = Input p                                                                                                                                                                                                                                                    | in, ISRC3 (AN<br>in, ISRC2 (AN<br>in, ISRC1 (AN<br>put is selected | 5)<br>6)            |                  |                  |                    |          |  |  |

| bit 7-6               | Unimplemen                                                                                                                                                                                                                                                                                         | ted: Read as '                                                     | 0'                  |                  |                  |                    |          |  |  |

| bit 5-0               | ISRCCAL<5:0>: Constant-Current Source Calibration bits<br>The calibration value must be copied from Flash address, 0x800E78, into these bits before the<br>module is enabled. Refer to the calibration data address table (Table 23-3) in Section 23.0 "Special<br>Features" for more information. |                                                                    |                     |                  |                  |                    |          |  |  |

| TABLE 26-14: | DC CHARACTERISTICS: PROGRAM MEMORY |

|--------------|------------------------------------|

|--------------|------------------------------------|

| DC CHARACTERISTICS |        |                                                     | (unless |                     |      |       | s: <b>3.0V to 3.6V</b><br>≤ TA ≤ +85°C for Industrial<br>≤ TA ≤ +125°C for Extended |

|--------------------|--------|-----------------------------------------------------|---------|---------------------|------|-------|-------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | nbol Characteristic                                 |         | Typ. <sup>(1)</sup> | Max. | Units | Conditions                                                                          |

|                    |        | Program Flash Memory                                |         |                     |      |       |                                                                                     |

| D130               | Eр     | Cell Endurance                                      | 10,000  |                     | _    | E/W   | -40°C to +125°C                                                                     |

| D131               | Vpr    | VDD for Read                                        | 3.0     | _                   | 3.6  | V     |                                                                                     |

| D132b              | VPEW   | VDD for Self-Timed Write                            | 3.0     |                     | 3.6  | V     |                                                                                     |

| D134               | TRETD  | Characteristic Retention                            | 20      | —                   | —    | Year  | Provided no other specifications are violated, -40°C to +125°C                      |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | —       | 10                  | —    | mA    |                                                                                     |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up       | —       | —                   | 150  | mA    |                                                                                     |

| D137a              | Тре    | Page Erase Time                                     | 19.7    | —                   | 20.1 | ms    | TPE = 146893 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>                              |

| D137b              | TPE    | Page Erase Time                                     | 19.5    | —                   | 20.3 | ms    | TPE = 146893 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>                             |

| D138a              | Tww    | Word Write Cycle Time                               | 46.5    | —                   | 47.3 | μs    | Tww = 346 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>                                 |

| D138b              | Tww    | Word Write Cycle Time                               | 46.0    | —                   | 47.9 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C <b>(Note 3)</b>                                |

| D139a              | Trw    | Row Write Time                                      | 667     | _                   | 679  | μs    | Trw = 4965 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>                                |

| D139b              | Trw    | Row Write Time                                      | 660     | —                   | 687  | μs    | Trw = 4965 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>                               |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 26-20) and the value of the FRC Oscillator Tuning register (see Register 8-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

#### TABLE 26-31: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                              | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 26-31                              | _                                           | —                                                                                                                                                                                                                                                                                       | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | —                                        | Table 26-32                                 | —                                                                                                                                                                                                                                                                                       | 1   | 0,1 | 1   |  |  |

| 9 MHz                | —                                        | Table 26-33                                 | —                                                                                                                                                                                                                                                                                       | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 26-34                                                                                                                                                                                                                                                                             | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 26-35                                                                                                                                                                                                                                                                             | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | _                                           | Table 26-36                                                                                                                                                                                                                                                                             | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | _                                           | Table 26-37                                                                                                                                                                                                                                                                             | 0   | 0   | 0   |  |  |

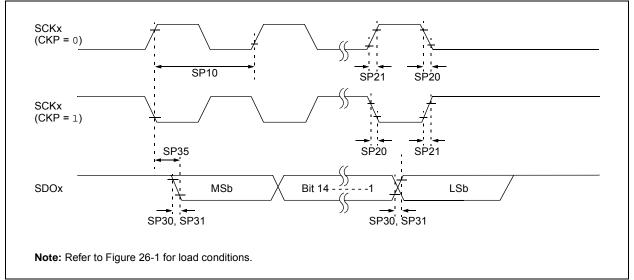

#### FIGURE 26-11: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

### TABLE 26-36:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |                        |       |                                |  |

|--------------------|-----------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|-------|--------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                | Min.                                                                                                                                                                                                                                                                                | Тур. <sup>(2)</sup> | Max.                   | Units | Conditions                     |  |

| SP70               | FscP                  | Maximum SCKx Input<br>Frequency                                              | _                                                                                                                                                                                                                                                                                   | —                   | Lesser of:<br>FP or 11 | MHz   | (Note 3)                       |  |

| SP72               | TscF                  | SCKx Input Fall Time                                                         | —                                                                                                                                                                                                                                                                                   | _                   | _                      | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73               | TscR                  | SCKx Input Rise Time                                                         | _                                                                                                                                                                                                                                                                                   | —                   |                        | ns    | See Parameter DO31<br>(Note 4) |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                                   | _                                                                                                                                                                                                                                                                                   | _                   |                        | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                                   | —                                                                                                                                                                                                                                                                                   | _                   |                        | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After<br>SCKx Edge                                    | —                                                                                                                                                                                                                                                                                   | 6                   | 20                     | ns    |                                |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                                 | 30                                                                                                                                                                                                                                                                                  | —                   | —                      | ns    |                                |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                   | 30                                                                                                                                                                                                                                                                                  | _                   | _                      | ns    |                                |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                    | 30                                                                                                                                                                                                                                                                                  | _                   | _                      | ns    |                                |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx $\downarrow$<br>Input | 120                                                                                                                                                                                                                                                                                 | —                   | —                      | ns    |                                |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                       | 10                                                                                                                                                                                                                                                                                  | —                   | 50                     | ns    | (Note 4)                       |  |

| SP52               | TscH2ssH,<br>TscL2ssH | SSx ↑ after SCKx Edge                                                        | 1.5 Tcy + 40                                                                                                                                                                                                                                                                        | _                   | _                      | ns    | (Note 4)                       |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                     | —                                                                                                                                                                                                                                                                                   | —                   | 50                     | ns    |                                |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

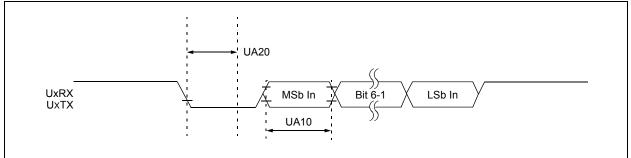

#### FIGURE 26-23: UARTX MODULE I/O TIMING CHARACTERISTICS

#### TABLE 26-41: UARTX MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                   | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                     |      |       |            |  |

|--------------------|---------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|--|

| Param<br>No.       | Symbol  | Characteristic <sup>(1)</sup>                     | Min.                                                                                                                                | Тур. <sup>(2)</sup> | Max. | Units | Conditions |  |

| UA10               | TUABAUD | UARTx Baud Time                                   | 66.67                                                                                                                               | _                   | _    | ns    |            |  |

| UA11               | FBAUD   | UARTx Baud Frequency                              | _                                                                                                                                   | —                   | 15   | Mbps  |            |  |

| UA20               | TCWF    | Start Bit Pulse Width to Trigger<br>UARTx Wake-up | 500                                                                                                                                 |                     |      | ns    |            |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 26-42: ANALOG CURRENT SPECIFICATIONS

| AC CHARACTERISTICS |        |                                       | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                |   |       |                                                                                                                    |

|--------------------|--------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---|-------|--------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>         | Min.                                                                                                                                  | Typ. <sup>(2)</sup> Max. Units |   | Units | Conditions                                                                                                         |

| AVD01              | IDD    | Analog Modules Current<br>Consumption | _                                                                                                                                     | 9                              | _ | mA    | Characterized data with the<br>following modules enabled:<br>APLL, 5 ADC Cores, 2 PGAs<br>and 4 Analog Comparators |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELoq, KEELoq logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2013-2017, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-1714-9