Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Betans                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs504t-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

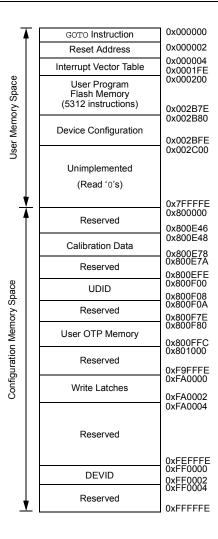

### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP16GS50X DEVICES

Note: Memory areas are not shown to scale.

### TABLE 4-30: PORTA REGISTER MAP FOR dsPIC33EPXXGS504/505 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|------------|-----------|-------|---------------|

| TRISA       | 0E00  | _      | _      | _      | _      |        |        | —     |       | _     |       | —     |       | -     | TRISA<4:0> |           |       | 001F          |

| PORTA       | 0E02  | _      | _      | —      | _      |        |        | —     |       | _     | _     | —     |       |       | RA<4:0>    |           |       | 0000          |

| LATA        | 0E04  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       |       | LATA<4:0>  |           |       | 0000          |

| ODCA        | 0E06  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       | (     | ODCA<4:0>  |           |       | 0000          |

| CNENA       | 0E08  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       | (     | CNIEA<4:0> |           |       | 0000          |

| CNPUA       | 0E0A  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       | C     | NPUA<4:0   | >         |       | 0000          |

| CNPDA       | 0E0C  | _      | _      | _      | _      | _      | _      | _     | _     | —     | _     | _     |       | C     | NPDA<4:0   | >         |       | 0000          |

| ANSELA      | 0E0E  | _      | —      | _      | —      | -      | -      | —     |       | —     |       | —     | —     | —     | /          | ANSA<2:0> |       | 0007          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-31: PORTB REGISTER MAP FOR dsPIC33EPXXGS504/505 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|-----------------|--------|--------|--------|--------|--------|---------|-------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB       | 0E10  |        | TRISB<15:0> FFF |        |        |        |        |        |         | FFFF  |           |       |       |       |       |       |       |               |

| PORTB       | 0E12  |        | RB<15:0> xxx    |        |        |        |        |        |         | xxxx  |           |       |       |       |       |       |       |               |

| LATB        | 0E14  |        | LATB<15:0> xxx  |        |        |        |        |        | xxxx    |       |           |       |       |       |       |       |       |               |

| ODCB        | 0E16  |        |                 |        |        |        |        |        | ODCB<1  | 5:0>  |           |       |       |       |       |       |       | 0000          |

| CNENB       | 0E18  |        |                 |        |        |        |        |        | CNIEB<1 | 5:0>  |           |       |       |       |       |       |       | 0000          |

| CNPUB       | 0E1A  |        | CNPUB<15:0> 00  |        |        |        |        |        | 0000    |       |           |       |       |       |       |       |       |               |

| CNPDB       | 0E1C  |        | CNPDB<15:0> 00  |        |        |        |        |        | 0000    |       |           |       |       |       |       |       |       |               |

| ANSELB      | 0E1E  | —      | _               | _      | _      | _      | ANSB<  | <10:9> | —       |       | ANSB<7:5> |       | -     |       | ANSE  | <3:0> |       | 06EF          |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-32: PORTC REGISTER MAP FOR dsPIC33EPXXGS504/505 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12                               | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------------------------------------|--------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC       | 0E20  | _      | _      |        | TRISC<13:0>                          |        |        |       |       |        |        | 3FFF  |       |       |       |       |       |               |

| PORTC       | 0E22  | _      | _      |        | RC<13:0>                             |        |        |       |       | xxxx   |        |       |       |       |       |       |       |               |

| LATC        | 0E24  | _      | _      |        | LATC<13:0>                           |        |        |       |       | xxxx   |        |       |       |       |       |       |       |               |

| ODCC        | 0E26  |        | _      |        |                                      |        |        |       |       | ODCC<  | 13:0>  |       |       |       |       |       |       | 0000          |

| CNENC       | 0E28  |        | _      |        |                                      |        |        |       |       | CNIEC< | 13:0>  |       |       |       |       |       |       | 0000          |

| CNPUC       | 0E2A  |        | _      |        |                                      |        |        |       |       | CNPUC< | :13:0> |       |       |       |       |       |       | 0000          |

| CNPDC       | 0E2C  |        | _      |        | CNPDC<13:0>                          |        |        |       |       | 0000   |        |       |       |       |       |       |       |               |

| ANSELC      | 0E2E  | _      | _      | -      | - ANSC<12:9> ANSC<6:4> - ANSC<2:0> 1 |        |        |       |       |        |        | 1E77  |       |       |       |       |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

When a PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the PSV pages can occur at the page boundaries when:

- The initial address, prior to modification, addresses the PSV page

- The EA calculation uses Pre- or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSRPAG register is incremented and the EA<15> bit is set to keep the base address within the PSV window. When an underflow is detected, the DSRPAG register is decremented and the EA<15> bit is set to keep the base

address within the PSV window. This creates a linear PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0 and PSV spaces. Table 4-37 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSRPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- Register Indirect with Register Offset Addressing

- Modulo Addressing

- Bit-Reversed Addressing

| TABLE 4-37: | OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0 AND |

|-------------|------------------------------------------------|

|             | PSV SPACE BOUNDARIES <sup>(2,3,4)</sup>        |

| O/U,        |                    |                | Before       |                        |                | After        |                        |

|-------------|--------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/0,<br>R/W | Operation          | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  | [++Wn]             | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | Or<br>[Wn++]       | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| U,<br>Read  |                    | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn] | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  |                    | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x7FFF).

2: An EDS access, with DSRPAG = 0x000, will generate an address error trap.

3: Only reads from PS are supported using DSRPAG.

4: Pseudolinear Addressing is not supported for large offsets.

## **REGISTER 6-1:** RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ul><li>1 = Device has been in Idle mode</li><li>0 = Device has not been in Idle mode</li></ul>                         |

| bit 1 | BOR: Brown-out Reset Flag bit                                                                                           |

|       | <ul><li>1 = A Brown-out Reset has occurred</li><li>0 = A Brown-out Reset has not occurred</li></ul>                     |

| bit 0 | POR: Power-on Reset Flag bit                                                                                            |

|       | <ul><li>1 = A Power-on Reset has occurred</li><li>0 = A Power-on Reset has not occurred</li></ul>                       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

### **REGISTER 7-1:** SR: CPU STATUS REGISTER<sup>(1)</sup>

| R/W-0                | R/W-0                | R/W-0                | R/W-0   | R/C-0 | R/C-0 | R-0   | R/W-0   |

|----------------------|----------------------|----------------------|---------|-------|-------|-------|---------|

| 10.00-0              | 10.00-0              | 10.00-0              | 10.00-0 | 100-0 | 100-0 | 11-0  | 10.00-0 |

| OA                   | OB                   | SA                   | SB      | OAB   | SAB   | DA    | DC      |

| bit 15               |                      |                      |         |       |       |       | bit 8   |

| (3)                  | (2)                  | (2)                  |         |       |       |       |         |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0   |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA      | N     | OV    | Z     | С       |

| bit 7                |                      |                      |         |       |       |       | bit 0   |

|                      |                      |                      |         |       |       |       |         |

| Logond:              |                      | C = Clearable        | hit     |       |       |       |         |

| Legend:           | C = Clearable bit |                        |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2

STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred

0 = Stack error trap has not occurred

bit 1

OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred

0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

### REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

bit 4-0

**PLLPRE<4:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler) 11111 = Input divided by 33

•

00001 = Input divided by 3

00000 = Input divided by 2 (default)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- **2:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0          | U-0           | U-0              | U-0              | U-0               | U-0              | U-0             | R/W-0   |

|--------------|---------------|------------------|------------------|-------------------|------------------|-----------------|---------|

| _            | —             | _                | —                | —                 | —                | _               | PLLDIV8 |

| bit 15       |               |                  |                  |                   |                  |                 | bit 8   |

|              |               |                  |                  |                   |                  |                 |         |

| R/W-0        | R/W-0         | R/W-1            | R/W-1            | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

|              |               |                  | PLLDI            | V<7:0>            |                  |                 |         |

| bit 7        |               |                  |                  |                   |                  |                 | bit 0   |

|              |               |                  |                  |                   |                  |                 |         |

| Legend:      |               |                  |                  |                   |                  |                 |         |

| R = Reada    | ble bit       | W = Writable     | bit              | U = Unimplen      | nented bit, read | d as '0'        |         |

| -n = Value a | at POR        | '1' = Bit is set |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|              |               |                  |                  |                   |                  |                 |         |

| bit 15-9     | Unimplemen    | ted: Read as '   | )'               |                   |                  |                 |         |

| bit 8-0      | PLLDIV<8:0>   | -: PLL Feedbac   | k Divisor bits ( | also denoted a    | is 'M', PLL mul  | tiplier)        |         |

|              | 111111111     | = 513            |                  |                   |                  |                 |         |

|              | •             |                  |                  |                   |                  |                 |         |

|              | •             |                  |                  |                   |                  |                 |         |

|              | •             |                  |                  |                   |                  |                 |         |

|              | 000110000=    | = 50 (default)   |                  |                   |                  |                 |         |

|              | •             |                  |                  |                   |                  |                 |         |

|              | •             |                  |                  |                   |                  |                 |         |

|              | • 000000010 = | = 4              |                  |                   |                  |                 |         |

|              | 00000010-     | <b>– –</b>       |                  |                   |                  |                 |         |

### REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

000000001 = 3 000000000 = 2

| U-0          | U-0          | U-0              | U-0            | U-0                                     | R/W-0            | U-0      | U-0   |  |  |

|--------------|--------------|------------------|----------------|-----------------------------------------|------------------|----------|-------|--|--|

| _            | —            | —                | —              | —                                       | CMPMD            | —        | _     |  |  |

| bit 15       |              |                  |                |                                         |                  |          | bit 8 |  |  |

|              |              |                  |                |                                         |                  |          |       |  |  |

| U-0          | U-0          | U-0              | U-0            | U-0                                     | U-0              | R/W-0    | U-0   |  |  |

| _            | _            | _                | —              | _                                       | —                | I2C2MD   | —     |  |  |

| bit 7        |              |                  |                |                                         |                  |          | bit 0 |  |  |

|              |              |                  |                |                                         |                  |          |       |  |  |

| Legend:      |              |                  |                |                                         |                  |          |       |  |  |

| R = Readab   | ole bit      | W = Writable     | bit            | U = Unimplem                            | nented bit, read | d as '0' |       |  |  |

| -n = Value a | at POR       | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |

|              |              |                  |                |                                         |                  |          |       |  |  |

| bit 15-11    | Unimplement  | ted: Read as '   | כ'             |                                         |                  |          |       |  |  |

| bit 10       | CMPMD: Con   | nparator Modul   | le Disable bit |                                         |                  |          |       |  |  |

|              | 1 = Comparat | or module is di  | sabled         |                                         |                  |          |       |  |  |

|              | 0 = Comparat | or module is ei  | nabled         |                                         |                  |          |       |  |  |

| bit 9-2      | Unimplement  | ted: Read as '   | כי             |                                         |                  |          |       |  |  |

| bit 1        | 12C2MD: 12C2 | 2 Module Disat   | ole bit        |                                         |                  |          |       |  |  |

|              |              | ule is disabled  |                |                                         |                  |          |       |  |  |

|              | 0 = I2C2 mod | ule is enabled   |                |                                         |                  |          |       |  |  |

### REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 0 | Unimplemented: Read as '0' |

|-------|----------------------------|

|       |                            |

### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0  | U-0  | U-0 | U-0  | U-0  | U-0   |

|--------|-----|------|------|-----|------|------|-------|

| —      | —   | —    | —    | —   | —    | —    | —     |

| bit 15 |     |      |      |     |      |      | bit 8 |

|        |     |      |      |     |      |      |       |

| 11.0   |     | 11.0 | 11.0 |     | 11.0 | 11.0 | 11.0  |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                        |                                    |  |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |  |

| bit 15-4 | Unimplemented: Read as '0'                        |

|----------|---------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit |

|          | 1 = Reference clock module is disabled            |

|          | 0 = Reference clock module is enabled             |

| bit 2-0  | Unimplemented: Read as '0'                        |

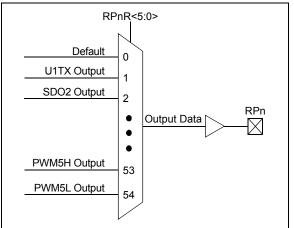

### 10.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 10-20 through Register 10-38). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 10-3: MULTIPLEXING REMAPPABLE OUTPUTS FOR RPn

## 10.4.5.1 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings, across any or all of the RPn pins, is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs, and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

### REGISTER 10-14: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0                              | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0                                   | R/W-0            | R/W-0    | R/W-0    |

|------------------------------------|------------------------------------|------------------------------------------------------------------------------|--------------|-----------------------------------------|------------------|----------|----------|

| SCK2INR7                           | SCK2INR6                           | SCK2INR5                                                                     | SCK2INR4     | SCK2INR3                                | SCK2INR2         | SCK2INR1 | SCK2INR0 |

| bit 15                             |                                    |                                                                              |              |                                         |                  |          | bit 8    |

| R/W-0                              | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0                                   | R/W-0            | R/W-0    | R/W-0    |

| SDI2R7                             | SDI2R6                             | SDI2R5                                                                       | SDI2R4       | SDI2R3                                  | SDI2R2           | SDI2R1   | SDI2R0   |

| bit 7                              |                                    |                                                                              |              |                                         |                  |          | bit (    |

| Legend:                            |                                    |                                                                              |              |                                         |                  |          |          |

| R = Readable                       | bit                                | W = Writable                                                                 | bit          | U = Unimpler                            | nented bit, read | l as '0' |          |

| -n = Value at POR '1' = Bit is set |                                    |                                                                              |              | '0' = Bit is cleared x = Bit is unknown |                  |          |          |

|                                    | 10110100 =<br>•<br>•<br>00000001 = | Input tied to Rf<br>Input tied to Rf<br>Input tied to Rf<br>Input tied to Vs | 2180<br>21   |                                         |                  |          |          |

| bit 7-0                            | 10110101 =                         | Input tied to RF<br>Input tied to RF                                         | 2181<br>2180 | 12) to the Corre                        | esponding RPn    | Pin bits |          |

### REGISTER 10-20: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0                                                                                                                                      | R/W-0                      | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|-----------------------------------------|--------|--------|--------|--|--|--|

| _             | —                                                                                                                                        | RP33R5                     | RP33R4 | RP33R3                                  | RP33R2 | RP33R1 | RP33R0 |  |  |  |

| bit 15        |                                                                                                                                          |                            |        |                                         |        |        | bit 8  |  |  |  |

|               |                                                                                                                                          |                            |        |                                         |        |        |        |  |  |  |

| U-0           | U-0                                                                                                                                      | R/W-0                      | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |  |  |  |

| _             | —                                                                                                                                        | RP32R5                     | RP32R4 | RP32R3                                  | RP32R2 | RP32R1 | RP32R0 |  |  |  |

| bit 7         |                                                                                                                                          |                            |        |                                         |        |        | bit 0  |  |  |  |

|               |                                                                                                                                          |                            |        |                                         |        |        |        |  |  |  |

| Legend:       |                                                                                                                                          |                            |        |                                         |        |        |        |  |  |  |

| R = Readabl   | e bit                                                                                                                                    | W = Writable               | bit    | U = Unimplemented bit, read as '0'      |        |        |        |  |  |  |

| -n = Value at | POR                                                                                                                                      | '1' = Bit is set           |        | '0' = Bit is cleared x = Bit is unknown |        |        |        |  |  |  |

|               |                                                                                                                                          |                            |        |                                         |        |        |        |  |  |  |

| bit 15-14     | Unimplemen                                                                                                                               | ted: Read as '             | 0'     |                                         |        |        |        |  |  |  |

| bit 13-8      | <b>RP33R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP33 Output Pin bits (see Table 10-2 for peripheral function numbers) |                            |        |                                         |        |        |        |  |  |  |

| bit 7-6       | Unimplemen                                                                                                                               | Unimplemented: Read as '0' |        |                                         |        |        |        |  |  |  |

bit 5-0 **RP32R<5:0>:** Peripheral Output Function is Assigned to RP32 Output Pin bits (see Table 10-2 for peripheral function numbers)

### REGISTER 10-21: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0             | U-0                                                                        | R/W-0          | R/W-0         | R/W-0          | R/W-0            | R/W-0    | R/W-0  |  |

|-----------------|----------------------------------------------------------------------------|----------------|---------------|----------------|------------------|----------|--------|--|

| _               | —                                                                          | RP35R5         | RP35R4        | RP35R3         | RP35R2           | RP35R1   | RP35R0 |  |

| bit 15          |                                                                            | •              |               |                |                  | •        | bit 8  |  |

|                 |                                                                            |                |               |                |                  |          |        |  |

| U-0             | U-0                                                                        | R/W-0          | R/W-0         | R/W-0          | R/W-0            | R/W-0    | R/W-0  |  |

| —               | —                                                                          | RP34R5         | RP34R4        | RP34R3         | RP34R2           | RP34R1   | RP34R0 |  |

| bit 7           |                                                                            | •              |               |                |                  | •        | bit 0  |  |

|                 |                                                                            |                |               |                |                  |          |        |  |

| Legend:         |                                                                            |                |               |                |                  |          |        |  |

| R = Readable    | bit                                                                        | W = Writable   | bit           | U = Unimpler   | mented bit, read | as '0'   |        |  |

| -n = Value at P | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |               |                |                  |          |        |  |

|                 |                                                                            |                |               |                |                  |          |        |  |

| bit 15-14       | Unimplemen                                                                 | ted: Read as ' | כ'            |                |                  |          |        |  |

| bit 13-8        | RP35R<5:0>:                                                                | Peripheral Ou  | tput Function | is Assigned to | RP35 Output F    | rin bits |        |  |

(see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP34R<5:0>:** Peripheral Output Function is Assigned to RP34 Output Pin bits (see Table 10-2 for peripheral function numbers)

NOTES:

### REGISTER 15-12: PWMCONx: PWMx CONTROL REGISTER (x = 1 to 5) (CONTINUED)

- bit 7-6 DTC<1:0>: Dead-Time Control bits 11 = Reserved 10 = Dead-time function is disabled 01 = Negative dead time is actively applied for Complementary Output mode 00 = Positive dead time is actively applied for all Output modes bit 5-4 Unimplemented: Read as '0' bit 3 MTBS: Master Time Base Select bit 1 = PWMx generator uses the secondary master time base for synchronization and the clock source for the PWMx generation logic (if secondary time base is available) 0 = PWMx generator uses the primary master time base for synchronization and the clock source for the PWMx generation logic CAM: Center-Aligned Mode Enable bit<sup>(2,3,4)</sup> bit 2 1 = Center-Aligned mode is enabled 0 = Edge-Aligned mode is enabled XPRES: External PWMx Reset Control bit<sup>(5)</sup> bit 1 1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base mode 0 = External pins do not affect the PWMx time base bit 0 **IUE:** Immediate Update Enable bit 1 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are immediate 0 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are synchronized to the local PWMx time base Note 1: Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller. 2: The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored. 3: These bits should not be changed after the PWMx is enabled by setting PTEN = 1 (PTCON<15>). 4: Center-Aligned mode ignores the Least Significant 3 bits of the Duty Cycle, Phase and Dead-Time registers. The highest Center-Aligned mode resolution available is 8.32 ns with the clock prescaler set to

- 5: Configure CLMOD = 0 (FCLCONx<8>) and ITB = 1 (PWMCONx<9>) to operate in External Period Reset mode.

the fastest clock.

### REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 5)

|              | (X = 1                                                                  | 10 5)                                                                                                                                                                                           |                    |                                        |                   |                 |                  |  |  |  |

|--------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------|-------------------|-----------------|------------------|--|--|--|

| R/W-0        | R/W-0                                                                   | R/W-0                                                                                                                                                                                           | R/W-0              | R/W-0                                  | R/W-0             | U-0             | U-0              |  |  |  |

| PHR          | PHF                                                                     | PLR                                                                                                                                                                                             | PLF                | FLTLEBEN                               | CLLEBEN           | —               |                  |  |  |  |

| bit 15       |                                                                         |                                                                                                                                                                                                 |                    |                                        |                   |                 | bit 8            |  |  |  |

|              |                                                                         |                                                                                                                                                                                                 |                    |                                        |                   |                 |                  |  |  |  |

| U-0          | U-0                                                                     | R/W-0                                                                                                                                                                                           | R/W-0              | R/W-0                                  | R/W-0             | R/W-0           | R/W-0            |  |  |  |

|              |                                                                         | BCH <sup>(1)</sup>                                                                                                                                                                              | BCL <sup>(1)</sup> | BPHH                                   | BPHL              | BPLH            | BPLL             |  |  |  |

| bit 7        |                                                                         |                                                                                                                                                                                                 |                    |                                        |                   |                 | bit 0            |  |  |  |

| Legend:      |                                                                         |                                                                                                                                                                                                 |                    |                                        |                   |                 |                  |  |  |  |

| R = Readat   | ole bit                                                                 | W = Writable b                                                                                                                                                                                  | oit                | U = Unimpler                           | nented bit, read  | as '0'          |                  |  |  |  |

| -n = Value a | at POR                                                                  | '1' = Bit is set                                                                                                                                                                                |                    | '0' = Bit is clea                      |                   | x = Bit is unkr | nown             |  |  |  |

| bit 15       |                                                                         | H Rising Edge T                                                                                                                                                                                 | riggor Enable      | - bit                                  |                   |                 |                  |  |  |  |

| bit 15       | 1 = Rising edg                                                          | ge of PWMxH v                                                                                                                                                                                   | vill trigger the   | Leading-Edge E<br>ling edge of PW      | •                 | PL              |                  |  |  |  |

| bit 14       | -                                                                       | I Falling Edge 1                                                                                                                                                                                | -                  |                                        |                   |                 |                  |  |  |  |

|              |                                                                         | 1 = Falling edge of PWMxH will trigger the Leading-Edge Blanking counter                                                                                                                        |                    |                                        |                   |                 |                  |  |  |  |

|              | -                                                                       | 0 = Leading-Edge Blanking ignores the falling edge of PWMxH                                                                                                                                     |                    |                                        |                   |                 |                  |  |  |  |

| bit 13       |                                                                         | PLR: PWMxL Rising Edge Trigger Enable bit                                                                                                                                                       |                    |                                        |                   |                 |                  |  |  |  |

|              | 1 = Rising edge of PWMxL will trigger the Leading-Edge Blanking counter |                                                                                                                                                                                                 |                    |                                        |                   |                 |                  |  |  |  |

| bit 12       | -                                                                       | <ul> <li>0 = Leading-Edge Blanking ignores the rising edge of PWMxL</li> <li>PLF: PWMxL Falling Edge Trigger Enable bit</li> </ul>                                                              |                    |                                        |                   |                 |                  |  |  |  |

|              | 1 = Falling ed                                                          | ge of PWMxL v                                                                                                                                                                                   | vill trigger the   | Leading-Edge E<br>lling edge of PW     | •                 | er              |                  |  |  |  |

| bit 11       | -                                                                       |                                                                                                                                                                                                 | -                  | anking Enable bi                       |                   |                 |                  |  |  |  |

|              |                                                                         |                                                                                                                                                                                                 |                    | ne selected Faul<br>to the selected F  |                   |                 |                  |  |  |  |

| bit 10       | CLLEBEN: C                                                              | urrent-Limit Lea                                                                                                                                                                                | ading-Edge B       | lanking Enable I                       | bit               |                 |                  |  |  |  |

|              |                                                                         |                                                                                                                                                                                                 |                    | ne selected curre<br>to the selected o |                   | ut              |                  |  |  |  |

| bit 9-6      | Unimplemen                                                              | ted: Read as '0                                                                                                                                                                                 | 2                  |                                        |                   |                 |                  |  |  |  |

| bit 5        | BCH: Blankin                                                            | g in Selected B                                                                                                                                                                                 | lanking Signa      | al High Enable b                       | it <sup>(1)</sup> |                 |                  |  |  |  |

|              |                                                                         |                                                                                                                                                                                                 |                    | Fault input signa<br>ng signal is high |                   | lected blanking | g signal is high |  |  |  |

| bit 4        | BCL: Blankin                                                            | g in Selected B                                                                                                                                                                                 | lanking Signa      | I Low Enable bit                       | t(1)              |                 |                  |  |  |  |

|              |                                                                         | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is low</li> <li>0 = No blanking when the selected blanking signal is low</li> </ul> |                    |                                        |                   |                 |                  |  |  |  |

| bit 3        | BPHH: Blank                                                             | ing in PWMxH I                                                                                                                                                                                  | High Enable b      | oit                                    |                   |                 |                  |  |  |  |

|              |                                                                         | nking (of currenting when the PV                                                                                                                                                                |                    | Fault input signa<br>is high           | als) when the P   | WMxH output i   | is high          |  |  |  |

| bit 2        | BPHL: Blanki                                                            | ing in PWMxH L                                                                                                                                                                                  | ow Enable b        | it                                     |                   |                 |                  |  |  |  |

|              |                                                                         | nking (of currenting when the PV                                                                                                                                                                |                    | Fault input signa<br>is low            | als) when the P\  | WMxH output i   | s low            |  |  |  |

|              |                                                                         |                                                                                                                                                                                                 |                    |                                        |                   |                 |                  |  |  |  |

**Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

## 22.3 Current Source Control Register

### REGISTER 22-1: ISRCCON: CONSTANT-CURRENT SOURCE CONTROL REGISTER

| R/W-0                 | U-0                                                                                       | U-0                                                                | U-0                           | U-0              | R/W-0            | R/W-0                                       | R/W-0    |

|-----------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------|------------------|------------------|---------------------------------------------|----------|

| ISRCEN                |                                                                                           |                                                                    | —                             | —                | OUTSEL2          | OUTSEL1                                     | OUTSEL0  |

| bit 15                |                                                                                           | •                                                                  | •                             | •                |                  |                                             | bit 8    |

| U-0                   | U-0                                                                                       | R/W-0                                                              | R/W-0                         | R/W-0            | R/W-0            | R/W-0                                       | R/W-0    |

| 0-0                   | 0-0                                                                                       | ISRCCAL5                                                           | ISRCCAL4                      | ISRCCAL3         | ISRCCAL2         | ISRCCAL1                                    | ISRCCAL0 |

| <br>bit 7             |                                                                                           | ISRCCALS                                                           | ISRUUAL4                      | ISRUUALS         | ISRCCALZ         | ISRCCALT                                    | bit (    |

|                       |                                                                                           |                                                                    |                               |                  |                  |                                             | DILC     |

| Legend:               |                                                                                           |                                                                    |                               |                  |                  |                                             |          |

| R = Readabl           | le bit                                                                                    | W = Writable                                                       | bit                           | U = Unimpler     | nented bit, read | d as '0'                                    |          |

| -n = Value at         | t POR                                                                                     | '1' = Bit is set                                                   |                               | '0' = Bit is cle | ared             | x = Bit is unkr                             | nown     |

|                       | •                                                                                         | >: Output Con                                                      |                               | Select bits      |                  |                                             |          |

| bit 14-11<br>bit 10-8 | 0 = Current s<br>Unimplemen<br>OUTSEL<2:0<br>111 = Reserv<br>110 = Reserv<br>101 = Reserv | ved<br>ved                                                         | o'<br>stant-Current           | Select bits      |                  |                                             |          |

|                       | 011 = Input p<br>010 = Input p<br>001 = Input p                                           | in, ISRC3 (AN<br>in, ISRC2 (AN<br>in, ISRC1 (AN<br>put is selected | 5)<br>6)                      |                  |                  |                                             |          |

| bit 7-6               | Unimplemen                                                                                | ted: Read as '                                                     | 0'                            |                  |                  |                                             |          |

| bit 5-0               | The calibratio module is ena                                                              |                                                                    | e copied from the calibration | Flash address    | s, 0x800E78, in  | to these bits be<br>-3) in <b>Section 2</b> |          |

# 25.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 25.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

### TABLE 26-44: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

| AC CH                                                           | ARACTE | RISTICS <sup>(2)</sup> | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |         |         |                                       |  |  |  |  |

|-----------------------------------------------------------------|--------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|---------|---------------------------------------|--|--|--|--|

| Param<br>No.SymbolCharacteristicsMin.Typ.(1)Max.UnitsConditions |        |                        |                                                                                                                                                                                                                                                                          |     |         |         |                                       |  |  |  |  |

|                                                                 |        |                        |                                                                                                                                                                                                                                                                          | Clo | ck Para | meters  |                                       |  |  |  |  |

| AD50                                                            | TAD    | ADC Clock Period       | 14.28                                                                                                                                                                                                                                                                    |     | —       | ns      |                                       |  |  |  |  |

|                                                                 |        |                        |                                                                                                                                                                                                                                                                          | Thr | oughpu  | ut Rate |                                       |  |  |  |  |

| AD51                                                            | Fтр    | SH0-SH3                | —                                                                                                                                                                                                                                                                        |     | 3.25    |         | 70 MHz ADC clock, 12 bits, no pending |  |  |  |  |

|                                                                 |        | SH4                    | _                                                                                                                                                                                                                                                                        |     | 3.25    | Msps    | conversion at time of trigger         |  |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is ensured, but not characterized.

### TABLE 26-45: HIGH-SPEED ANALOG COMPARATOR MODULE SPECIFICATIONS

| AC/DC (      | CHARACT | reristics <sup>(2)</sup>                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |    |      |    |                                                                                                                             |  |

|--------------|---------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|----|-----------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol  | Characteristic                                    | Min. Typ. Max. Units                                                                                                                                                                                                                                                                    |    |      |    | Comments                                                                                                                    |  |

| CM10         | VIOFF   | Input Offset Voltage                              | -35                                                                                                                                                                                                                                                                                     | ±5 | +35  | mV |                                                                                                                             |  |

| CM11         | VICM    | Input Common-Mode<br>Voltage Range <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                       | —  | AVdd | V  |                                                                                                                             |  |

| CM13         | CMRR    | Common-Mode<br>Rejection Ratio                    | 60                                                                                                                                                                                                                                                                                      | —  |      | dB |                                                                                                                             |  |

| CM14         | TRESP   | Large Signal Response                             | _                                                                                                                                                                                                                                                                                       | 15 | _    | ns | V+ input step of 100 mV while<br>V- input is held at AVDD/2. Delay<br>measured from analog input pin to<br>PWMx output pin. |  |

| CM15         | VHYST   | Input Hysteresis                                  | 5                                                                                                                                                                                                                                                                                       | 10 | 20   | mV | Depends on HYSSEL<1:0>                                                                                                      |  |

| CM16         | TON     | Comparator Enabled to Valid Output                | _                                                                                                                                                                                                                                                                                       | —  | 1    | μs |                                                                                                                             |  |

Note 1: These parameters are for design guidance only and are not tested in manufacturing.

2: The comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

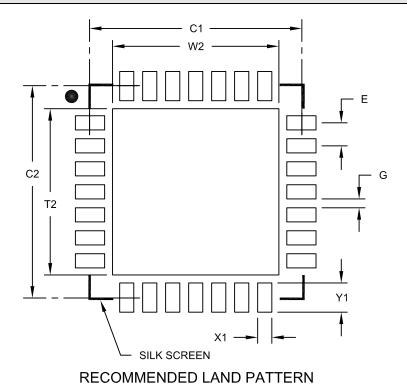

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |          | MILLIM | SC 4.70<br>4.70 |      |  |  |

|----------------------------|----------|--------|-----------------|------|--|--|

| Dimensio                   | n Limits | MIN    | NOM             | MAX  |  |  |

| Contact Pitch              | E        |        | 0.65 BSC        | 4.70 |  |  |

| Optional Center Pad Width  | W2       |        |                 | 4.70 |  |  |

| Optional Center Pad Length | T2       |        |                 | 4.70 |  |  |

| Contact Pad Spacing        | C1       |        | 6.00            |      |  |  |

| Contact Pad Spacing        | C2       |        | 6.00            |      |  |  |

| Contact Pad Width (X28)    | X1       |        |                 | 0.40 |  |  |

| Contact Pad Length (X28)   | Y1       |        |                 | 0.85 |  |  |

| Distance Between Pads      | G        | 0.25   |                 |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

| SPIx Slave Mode (Full-Duplex, CKE = 1,       |     |

|----------------------------------------------|-----|

| CKP = 1, SMP = 0)                            | 332 |

| Timer1-Timer5 External Clock Characteristics | 321 |

| UARTx I/O Characteristics                    | 342 |

|                                              |     |

### U

| Unique Device Identifier (UDID)<br>Universal Asynchronous Receiver | 31  |

|--------------------------------------------------------------------|-----|

| Transmitter (UART)                                                 |     |

| Control Registers                                                  |     |

| Helpful Tips                                                       |     |

| Resources                                                          | 224 |

| Universal Asynchronous Receiver Transmitter. See UART.             |     |

| User OTP Memory                                                    |     |

|                                                                    |     |

### ۷

| 285        |

|------------|

|            |

| . 277, 286 |

| 286        |

| 384        |

| 10         |

|            |

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830 Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781