Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C                                                                   |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs506-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

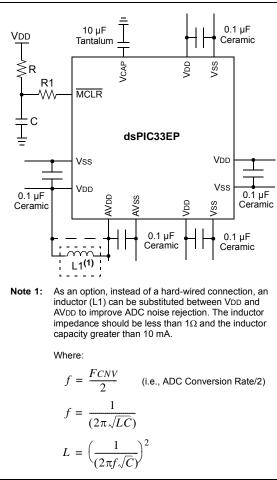

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

## 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (<0.5  $\Omega$ ) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu F$  (10  $\mu F$  is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 26.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 23.4 "On-Chip Voltage Regulator"** for details.

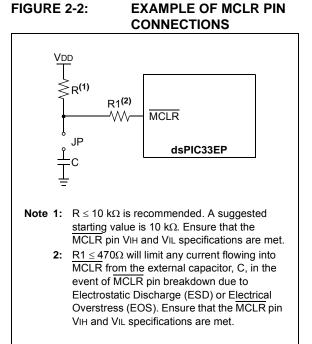

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

| 7                          | GOTO Instruction                                      | 0x000000                         |

|----------------------------|-------------------------------------------------------|----------------------------------|

|                            | Reset Address                                         | 0x000002                         |

| Ð                          | Interrupt Vector Table                                | 0x000004<br>0x0001FE             |

| User Memory Space          | User Program<br>Flash Memory<br>(22,207 instructions) | 0x000200<br>0x00AF7E             |

| er Mem                     | Device Configuration                                  | 0x00AF80<br>0x00AFFE             |

| Use                        |                                                       | 0x00B000                         |

|                            | Unimplemented                                         |                                  |

|                            | (Read '0's)                                           |                                  |

|                            | Reserved                                              | 0x7FFFFE<br>0x800000<br>0x800E46 |

|                            | Calibration Data                                      | 0x800E48                         |

|                            | Reserved                                              | 0x800E78<br>0x800E7A<br>0x800EFE |

| Configuration Memory Space | UDID                                                  | 0x800F00<br>0x800F08<br>0x800F0A |

| nory S                     | Reserved                                              | 0x800F7E                         |

| n Mer                      | User OTP Memory                                       | 0x800F80<br>0x800FFC             |

| Iratio                     | Reserved                                              | 0x801000                         |

| onfigu                     | Write Latches                                         | 0xF9FFFE<br>0xFA0000             |

| ŏ                          |                                                       | 0xFA0002<br>0xFA0004             |

|                            | Reserved                                              |                                  |

|                            | DEVID                                                 | 0xFEFFFE<br>0xFF0000             |

|                            | Reserved                                              | 0xFF0002<br>0xFF0004             |

| _                          |                                                       | 0xFFFFFE                         |

Note: Memory areas are not shown to scale.

### TABLE 4-7: PWM REGISTER MAP

| SFR<br>Name | Addr.                                                                          | Bit 15                                                                       | Bit 14                                                               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8         | Bit 7       | Bit 6          | Bit 5        | Bit 4    | Bit 3   | Bit 2   | Bit 1       | Bit 0   | All<br>Resets |

|-------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------|--------|--------|--------|--------|-----------|---------------|-------------|----------------|--------------|----------|---------|---------|-------------|---------|---------------|

| PTCON       | 0C00                                                                           | PTEN                                                                         | _                                                                    | PTSIDL | SESTAT | SEIEN  | EIPU   | SYNCPOL   | SYNCOEN       | SYNCEN      | SYNCSRC2       | SYNCSRC1     | SYNCSRC0 | SEVTPS3 | SEVTPS2 | SEVTPS1     | SEVTPS0 | 0000          |

| PTCON2      | 0C02                                                                           | —                                                                            |                                                                      | _      | _      | _      |        | _         | _             | —           |                | _            |          |         | F       | PCLKDIV<2:0 | >       | 0000          |

| PTPER       | 0C04                                                                           |                                                                              | PWMx Primary Master Time Base Period Register (PTPER<15:0>)          |        |        |        |        |           |               |             |                |              |          | FFF8    |         |             |         |               |

| SEVTCMP     | 0C06                                                                           |                                                                              | PWMx Special Event Compare Register (SEVTCMP12:0>)     –     –     – |        |        |        |        |           |               |             |                |              |          |         |         | 0000        |         |               |

| MDC         | 0C0A                                                                           |                                                                              | PWMx Master Duty Cycle Register (MDC<15:0>)                          |        |        |        |        |           |               |             |                |              |          |         | 0000    |             |         |               |

| STCON       | 0C0E                                                                           | —                                                                            | I                                                                    | _      | SESTAT | SEIEN  | EIPU   | SYNCPOL   | SYNCOEN       | SYNCEN      | SYNCSRC2       | SYNCSRC1     | SYNCSRC0 | SEVTPS3 | SEVTPS2 | SEVTPS1     | SEVTPS0 | 0000          |

| STCON2      | 0C10                                                                           | —                                                                            | I                                                                    | _      | _      |        |        |           | -             | —           |                | —            |          |         | F       | PCLKDIV<2:0 | >       | 0000          |

| STPER       | 0C12                                                                           |                                                                              |                                                                      |        |        |        |        | PWMx Seco | ondary Master | Time Base F | Period Registe | er (STPER<15 | :0>)     |         |         |             |         | FFF8          |

| SSEVTCMP    | 0C14                                                                           | PWMx Secondary Special Event Compare Register (SSEVTCMP<12:0>) — — — —       |                                                                      |        |        |        |        |           |               |             |                |              |          | 0000    |         |             |         |               |

| CHOP        | 0C1A                                                                           | 1A CHPCLKEN CHOPCLK6 CHOPCLK5 CHOPCLK4 CHOPCLK3 CHOPCLK2 CHOPCLK1 CHOPCLK0 0 |                                                                      |        |        |        |        |           |               |             |                |              |          |         | 0000    |             |         |               |

| PWMKEY      | V         0C1E         PWMx Protection Lock/Unlock Key Register (PWMKEY<15:0>) |                                                                              |                                                                      |        |        |        |        |           |               |             |                | 0000         |          |         |         |             |         |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-8: PWM GENERATOR 1 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13                                              | Bit 12  | Bit 11    | Bit 10          | Bit 9          | Bit 8          | Bit 7        | Bit 6        | Bit 5        | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|-----------------------------------------------------|---------|-----------|-----------------|----------------|----------------|--------------|--------------|--------------|----------|----------|----------|----------|----------|---------------|

| PWMCON1     | 0C20  | FLTSTAT | CLSTAT  | TRGSTAT                                             | FLTIEN  | CLIEN     | TRGIEN          | ITB            | MDCS           | DTC1         | DTC0         | _            | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON1      | 0C22  | PENH    | PENL    | POLH                                                | POLL    | PMOD1     | PMOD0           | OVRENH         | OVRENL         | OVRDAT1      | OVRDAT0      | FLTDAT1      | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON1     | 0C24  | IFLTMOD | CLSRC4  | CLSRC3                                              | CLSRC2  | CLSRC1    | CLSRC0          | CLPOL          | CLMOD          | FLTSRC4      | FLTSRC3      | FLTSRC2      | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC1        | 0C26  |         |         |                                                     |         |           |                 | PWM1 Gen       | erator Duty C  | ycle Registe | er (PDC1<15  | i:0>)        |          |          |          |          |          | 0000          |

| PHASE1      | 0C28  |         |         |                                                     |         | F         | WM1 Primary     | Phase-Shift o  | r Independent  | Time Base    | Period Reg   | ister (PHASE | 1<15:0>) |          |          |          |          | 0000          |

| DTR1        | 0C2A  | _       | _       |                                                     |         |           |                 |                | PWM1 D         | ead-Time R   | egister (DTI | R1<13:0>)    |          |          |          |          |          | 0000          |

| ALTDTR1     | 0C2C  | _       | _       | - PWM1 Alternate Dead-Time Register (ALTDTR1<13:0>) |         |           |                 |                |                |              |              |              |          | 0000     |          |          |          |               |

| SDC1        | 0C2E  |         |         |                                                     |         |           |                 | PWM1 Seco      | ondary Duty C  | ycle Registe | er (SDC1<1   | 5:0>)        |          |          |          |          |          | 0000          |

| SPHASE1     | 0C30  |         |         |                                                     |         |           |                 | PWM1 Second    | lary Phase-Sh  | ift Register | (SPHASE1     | <15:0>)      |          |          |          |          |          | 0000          |

| TRIG1       | 0C32  |         |         |                                                     |         | PWM1 Pr   | imary Trigger ( | Compare Value  | Register (TR   | GCMP<12:     | 0>)          |              |          |          | —        | —        | —        | 0000          |

| TRGCON1     | 0C34  | TRGDIV3 | TRGDIV2 | TRGDIV1                                             | TRGDIV0 |           | —               | _              | —              | DTM          | —            | TRGSTRT5     | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG1      | 0C36  |         |         |                                                     |         | PWM1 Seco | ondary Trigger  | Compare Valu   | e Register (S⁻ | FRGCMP<1     | 2:0>)        |              |          |          | —        | —        | _        | 0000          |

| PWMCAP1     | 0C38  |         |         |                                                     |         | PWM1 F    | Primary Time E  | Base Capture F | Register (PWN  | 1CAP<12:0>   | >)           |              |          |          | _        | _        | _        | 0000          |

| LEBCON1     | 0C3A  | PHR     | PHF     | PLR                                                 | PLF     | FLTLEBEN  | CLLEBEN         | _              | _              | _            | _            | BCH          | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY1     | 0C3C  | _       | _       | _                                                   | _       |           |                 | PWM1 Lead      | ling-Edge Bla  | nking Delay  | Register (L  | EB<8:0>)     |          |          | _        | _        | _        | 0000          |

| AUXCON1     | 0C3E  | HRPDIS  | HRDDIS  | _                                                   | _       | BLANKSEL3 | BLANKSEL2       | BLANKSEL1      | BLANKSEL0      | —            | _            | CHOPSEL3     | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-13: I2C1 AND I2C2 REGISTER MAP

| SFR<br>Name | Addr.                                                                                                          | Bit 15                       | Bit 14      | Bit 13    | Bit 12      | Bit 11     | Bit 10  | Bit 9  | Bit 8     | Bit 7       | Bit 6    | Bit 5      | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|----------------------------------------------------------------------------------------------------------------|------------------------------|-------------|-----------|-------------|------------|---------|--------|-----------|-------------|----------|------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1CONL    | 0200                                                                                                           | I2CEN                        | _           | I2CSIDL   | SCLREL      | STRICT     | A10M    | DISSLW | SMEN      | GCEN        | STREN    | ACKDT      | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1CONH    | 0202                                                                                                           | —                            | _           | —         | _           | _          | _       | —      | _         | _           | PCIE     | SCIE       | BOEN         | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C1STAT    | 0204                                                                                                           | ACKSTAT                      | TRSTAT      | ACKTIM    | _           | _          | BCL     | GCSTAT | ADD10     | IWCOL       | I2COV    | D_A        | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 0206                                                                                                           | _                            | —           | _         | _           | —          | _       |        |           |             |          | I2C1 Addr  | ess Register |              |       |       |       | 0000          |

| I2C1MSK     | 0208                                                                                                           | _                            | —           | _         | _           | —          | _       |        |           |             | I2C1 SI  | ave Mode A | ddress Mask  | Register     |       |       |       | 0000          |

| I2C1BRG     | 020A                                                                                                           |                              |             |           |             |            |         | E      | Baud Rate | Generator R | legister |            |              |              |       |       |       | 0000          |

| I2C1TRN     | 020C                                                                                                           | I2C1 Transmit Register 0 0 0 |             |           |             |            |         |        |           |             |          |            |              |              | OOFF  |       |       |               |

| I2C1RCV     | 020E                                                                                                           | _                            | —           | _         | _           | —          | _       | —      | _         |             |          |            | I2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2CON1    | 0210                                                                                                           | I2CEN                        | —           | I2CSIDL   | SCLREL      | STRICT     | A10M    | DISSLW | SMEN      | GCEN        | STREN    | ACKDT      | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2CON2    | 0212                                                                                                           | _                            | _           | _         | _           | _          | _       | _      | _         | _           | PCIE     | SCIE       | BOEN         | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C2STAT    | 0214                                                                                                           | ACKSTAT                      | TRSTAT      | ACKTIM    | _           | _          | BCL     | GCSTAT | ADD10     | IWCOL       | I2COV    | D_A        | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD     | 0216                                                                                                           | _                            | _           | _         | _           | _          | _       |        |           |             |          | I2C2 Addr  | ess Register |              |       |       |       | 0000          |

| I2C2MSK     | 0218                                                                                                           | _                            | —           | _         | _           | —          | _       |        |           |             | 12C2 SI  | ave Mode A | ddress Mask  | Register     |       |       |       | 0000          |

| I2C2BRG     | 021A                                                                                                           |                              |             |           |             |            |         | E      | Baud Rate | Generator R | legister |            |              |              |       |       |       | 0000          |

| I2C2TRN     | 021C                                                                                                           | _                            | —           | _         | _           | —          | _       | —      | _         |             |          |            | I2C2 Transr  | nit Register |       |       |       | OOFF          |

| I2C2RCV     | 2RCV         021E         —         —         —         —         —         I2C2 Receive Register         0000 |                              |             |           |             |            |         |        |           |             |          |            |              | 0000         |       |       |       |               |

| Legend:     | – unim                                                                                                         | plemented                    | road as '0' | Peact val | ues are sho | we in hove | dooimal | •      |           |             |          |            |              |              |       |       |       | •             |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8      | Bit 7        | Bit 6    | Bit 5 | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------------------------------------|--------|----------|--------|--------|--------|-----------|------------|--------------|----------|-------|-------------|--------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN                                 | _      | USIDL    | IREN   | RTSMD  | _      | UEN1      | UEN0       | WAKE         | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1                               | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF     | TRMT       | URXISEL1     | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _                                      | _      | _        | _      | _      | _      | _         |            |              |          | UART1 | Fransmit Re | gister |        |        |       | xxxx          |

| U1RXREG     | 0226  | _                                      | _      | _        | _      | _      | _      | _         |            |              |          | UART1 | Receive Re  | gister |        |        |       | 0000          |

| U1BRG       | 0228  |                                        |        |          |        |        |        | Baud Rate | e Generate | or Prescaler | Register |       |             |        |        |        |       | 0000          |

| U2MODE      | 0230  | UARTEN                                 | _      | USIDL    | IREN   | RTSMD  | _      | UEN1      | UEN0       | WAKE         | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1                               | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF     | TRMT       | URXISEL1     | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _                                      | _      | _        | _      | _      | —      | _         |            |              |          | UART2 | Fransmit Re | gister |        |        |       | xxxx          |

| U2RXREG     | 0236  | 6 — — — — — — — UART2 Receive Register |        |          |        |        |        |           |            |              |          |       |             |        | 0000   |        |       |               |

| U2BRG       | 0238  | Baud Rate Generator Prescaler Register |        |          |        |        |        |           |            |              |          |       |             | 0000   |        |        |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-21: NVM REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                                                              | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10  | Bit 9 | Bit 8 | it 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |   |   |      |          |        |        |        |      |

|-------------|-------|-------------------------------------------------------------------------------------|--------|--------|---------|--------|---------|-------|-------|------------------------------------------------------|---|---|------|----------|--------|--------|--------|------|

| NVMCON      | 0728  | WR                                                                                  | WREN   | WRERR  | NVMSIDL | SFTSWP | P2ACTIV | RPDF  | URERR | —                                                    | — | — | —    | NVMOP3   | NVMOP2 | NVMOP1 | NVMOP0 | 0000 |

| NVMADR      | 072A  | NVMADR<15:0>                                                                        |        |        |         |        |         |       |       |                                                      |   |   |      |          | 0000   |        |        |      |

| NVMADRU     | 072C  | -                                                                                   |        |        |         |        |         |       |       |                                                      |   |   |      |          |        |        |        | 0000 |

| NVMKEY      | 072E  | -                                                                                   | _      | _      | _       |        | _       | _     | _     |                                                      |   |   | NVMK | (EY<7:0> |        |        |        | 0000 |

| NVMSRCADR   | 0730  | NVM Source Data Address Register, Lower Word (NVMSRCADR<15:0>)                      |        |        |         |        |         |       |       |                                                      |   |   |      |          | 0000   |        |        |      |

| NVMSRCADRH  | 0732  | 32 — — — — — — — — NVM Source Data Address Register, Upper Byte (NVMSRCADR<23:16> 0 |        |        |         |        |         |       |       |                                                      |   |   |      |          |        | 0000   |        |      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-22: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|-----------|-----------|-----------|----------|----------|--------|----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR | _       | —      | VREGSF | _         | CM        | VREGS     | EXTR     | SWR      | SWDTEN | WDTO     | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | -      | COSC2  | COSC1   | COSC0  | _      | NOSC2     | NOSC1     | NOSC0     | CLKLOCK  | IOLOCK   | LOCK   | _        | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1   | DOZE0  | DOZEN  | FRCDIV2   | FRCDIV1   | FRCDIV0   | PLLPOST1 | PLLPOST0 | _      | PLLPRE4  | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 3040          |

| PLLFBD      | 0746  | -      |        | _       | _      | _      | _         | _         |           |          |          | PLL    | DIV<8:0> |         |         |         |         | 0030          |

| OSCTUN      | 0748  | -      |        | _       | _      | _      | _         | _         | _         | _        | _        |        |          | TUN     | <5:0>   |         |         | 0000          |

| LFSR        | 074C  | -      |        |         |        |        |           |           | LF        | SR<14:0> |          |        |          |         |         |         |         | 0000          |

| REFOCON     | 074E  | ROON   |        | ROSSLP  | ROSEL  | RODIV3 | RODIV2    | RODIV1    | RODIV0    | _        | _        | _      | _        | _       | _       | _       | _       | 0000          |

| ACLKCON     | 0750  | ENAPLL | APLLCK | SELACLK | _      | _      | APSTSCLR2 | APSTSCLR1 | APSTSCLR0 | ASRCSEL  | FRCSEL   | —      | _        | _       | _       | _       | _       | 2740          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

| R/W-1         | R/W-0       | R/W-0                                     | U-0            | U-0              | U-0              | U-0             | R/W-0  |

|---------------|-------------|-------------------------------------------|----------------|------------------|------------------|-----------------|--------|

| GIE           | DISI        | SWTRAP                                    | _              | _                | _                |                 | AIVTEN |

| bit 15        |             |                                           |                |                  |                  |                 | bit    |

|               |             |                                           |                |                  |                  |                 |        |

| U-0           | U-0         | U-0                                       | R/W-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |

|               |             | —                                         | INT4EP         |                  | INT2EP           | INT1EP          | INT0EP |

| bit 7         |             |                                           |                |                  |                  |                 | bit    |

| Legend:       |             |                                           |                |                  |                  |                 |        |

| R = Readable  | e bit       | W = Writable                              | bit            | U = Unimple      | mented bit, read | l as '0'        |        |

| -n = Value at | POR         | '1' = Bit is set                          |                | '0' = Bit is cle | eared            | x = Bit is unki | nown   |

|               |             |                                           |                |                  |                  |                 |        |

| bit 15        | GIE: Global | Interrupt Enable                          | e bit          |                  |                  |                 |        |

|               |             | ts and associate                          |                |                  |                  |                 |        |

|               |             | ts are disabled, I                        | •              | till enabled     |                  |                 |        |

| bit 14        |             | Instruction Statu                         |                |                  |                  |                 |        |

|               |             | struction is active<br>struction is not a |                |                  |                  |                 |        |

| bit 13        |             | Software Trap St                          |                |                  |                  |                 |        |

| DIL 15        |             | e trap is enabled                         |                |                  |                  |                 |        |

|               |             | e trap is disabled                        |                |                  |                  |                 |        |

| bit 12-9      | Unimpleme   | ented: Read as '                          | 0'             |                  |                  |                 |        |

| bit 8         | AIVTEN: Al  | ternate Interrupt                         | Vector Table E | Enable           |                  |                 |        |

|               |             | ternate Interrupt                         |                |                  |                  |                 |        |

|               |             | andard Interrupt                          |                |                  |                  |                 |        |

| bit 7-5       | -           | ented: Read as '                          |                |                  |                  |                 |        |

| bit 4         |             | ternal Interrupt 4                        | -              | Polarity Selec   | ct bit           |                 |        |

|               | •           | t on negative ed<br>t on positive edg     | •              |                  |                  |                 |        |

| bit 3         | -           | ented: Read as '                          |                |                  |                  |                 |        |

| bit 2         | -           | ternal Interrupt 2                        |                | Polarity Selec   | rt hit           |                 |        |

| SIL 2         |             | t on negative ed                          | 0              |                  |                  |                 |        |

|               |             | t on positive edg                         |                |                  |                  |                 |        |

| bit 1         | INT1EP: Ex  | ternal Interrupt 1                        | Edge Detect    | Polarity Selec   | ct bit           |                 |        |

|               |             | t on negative ed                          |                |                  |                  |                 |        |

|               | •           | t on positive edg                         |                |                  |                  |                 |        |

| bit 0         |             | ternal Interrupt (                        | -              | Polarity Selec   | ct bit           |                 |        |

|               |             | t on negative edg                         |                |                  |                  |                 |        |

|               | 0 = memup   | t on positive edg                         | e              |                  |                  |                 |        |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0         R/W-0         R/W-0         R/W-0         U-0         U-0         R/W-0           I2C1MD         U2MD         U1MD         SPI2MD         SPI1MD         —         —         ADCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0          | R/W-0          | R/W-0                          | R/W-0     | R/W-0             | U-0            | R/W-0           | U-0            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|--------------------------------|-----------|-------------------|----------------|-----------------|----------------|

| R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         I2C1MD       U2MD       U1MD       SP12MD       SP11MD       –       ADCM         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | T5MD           | T4MD           | T3MD                           | T2MD      | T1MD              | _              | PWMMD           | —              |

| I2C1MD     U2MD     U1MD     SPI2MD     SPI1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15         |                |                                |           |                   |                |                 | bit 8          |

| I2C1MD     U2MD     U1MD     SPI2MD     SPI1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>D</b> 444 0 | <b>D</b> #44.0 | <b>D</b> # <b>M</b> / <b>A</b> | DAMA      | <b>D</b> 444 0    |                |                 | <b>D</b> #44 0 |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 T5MD: Timer5 Module Disable bit 1 = Timer6 module is disabled 0 = Timer6 module is disabled 0 = Timer4 module is disabled 0 = Timer4 module is disabled 0 = Timer4 module is disabled 0 = Timer6 module Disable bit 1 = Timer3 module Disable bit 1 = Timer4 module is disabled 0 = Timer6 module Disable bit 1 = Timer3 module Disable bit 1 = Timer2 module is disabled 0 = Timer2 module Disable bit 1 = Timer1 module Disable bit 1 = PWMx module Disable bit 1 = UMX module Disable bit 1 = VMX module Disable bit 1 = VMX module Disable bit 1 = UMX module Disable bit 1 = PWMx module Disable bit 1 = UART2 module Disable bit 1 = UART1 module Disable bit 1 = SPI2 module Disable bit 1 = SPI2 module Disable bit 1 = SPI2 module Disable bit 1 = SPI1 module Disable bit 1 = ADC module Disable Dit 1 = AD                                                                                                                                     |                |                | 1                              |           |                   | U-0            | U-0             |                |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit<br>1 = Timer6 module is disabled<br>0 = Timer7 module is disabled<br>0 = UMX module is disabled<br>0 = UART2 Module Disable bit<br>1 = I2C1 module is disabled<br>0 = UART2 module is disabled<br>0 = UART2 module is disabled<br>0 = UART1 module is disabled<br>0 = UART1 module is disabled<br>0 = UART1 module is disabled<br>0 = SPI2 module is disabled<br>0 = SPI2 module is disabled<br>0 = SPI1 module is disabled<br>0 = SPI1 module is disabled<br>0 = SPI1 module is disabled<br>0 = SP11 module is disabled<br>1 = ADCC module is disabled                                                                                                                                                              |                | U2MD           | U1MD                           | SPI2MD    | SPI1MD            |                |                 |                |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit       1 = Timer5 module is disabled       0' = Bit is cleared       x = Bit is unknown         bit 14       T4MD: Timer4 Module Disable bit       1 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         0 = Timer4 module is disabled       0 = Timer3 module is disabled       0 = Timer3 module is disabled       0 = Timer4 module is disabled         0 = Timer3 module is disabled       0 = Timer2 module is disabled       0 = Timer3 module is disabled       0 = Timer4 module is disabled         0 = Timer4 module is disabled       0 = Timer4 module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = PWMX module Disable bit       1 = PVCT Module Disable bit         1 = PWMX module Disable bit       1 = PVMX module Disable bit       1 = PVCT module is disabled       0 = PVCT Module Disable bit         1 = PVLT module is disabled       0 = IZC1 module is disabled       0 = IZC1 module is disabled       0 = IZC1 module is disabled         0 = UART2 module is disabled       0 = UART2 module is disabled       0 = UART2 module is disabled       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DIL 7          |                |                                |           |                   |                |                 | bit (          |

| -n = Value at POR     '1' = Bit is set     '0' = Bit is cleared     x = Bit is unknown       bit 15     TSMD: Timer5 Module Disable bit     1 = Timer5 module is disabled     0 = Timer4 Module Disable bit       1 = Timer4 module is disabled     0 = Timer4 module is disabled     0 = Timer4 module is disabled       0 = Timer4 module is disabled     0 = Timer4 module is disabled     0 = Timer4 module is disabled       0 = Timer3 module is disabled     0 = Timer2 Module Disable bit     1 = Timer2 module is disabled       0 = Timer3 module is disabled     0 = Timer2 module is disabled     0 = Timer2 module is disabled       0 = Timer7 module is disabled     0 = Timer2 module is disabled     0 = Timer2 module is disabled       0 = Timer1 module is disabled     0 = Timer4 module is disabled     0 = Timer4 module is disabled       0 = Timer1 module is disabled     0 = Timer4 module is disabled     0 = Timer4 module is disabled       0 = Timer1 module is disabled     0 = Timer4 module is disabled     0 = Timer4 module is disabled       0 = Timer1 module is disabled     0 = Timer4 module is disabled     0 = Timer4 module is disabled       0 = Timer4 module is disabled     0 = Timer4 module is disabled     0 = Timer4 module is disabled       1 = PWMx module is disabled     0 = UART2 Module Disable bit     1 = UART2 module is disabled       0 = UART1 module is disabled     0 = UART1 module is disabled     0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Legend:        |                |                                |           |                   |                |                 |                |

| bit 15 TSMD: Timer5 Module Disable bit<br>1 = Timer5 module is disabled<br>0 = Timer5 module is enabled<br>bit 14 T4MD: Timer4 Module Disable bit<br>1 = Timer4 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer2 Module Disable bit<br>1 = Timer2 module is disabled<br>0 = Timer1 module Disable bit<br>1 = PWMx module Disable bit<br>1 = PWMx module Disable bit<br>1 = PWMx module Disable bit<br>1 = 12C1 module is enabled<br>0 = PVMXz module Disable bit<br>1 = 12C1 module is disabled<br>0 = UART2 module Disable bit<br>1 = 12C1 module is disabled<br>0 = UART2 module is disabled<br>0 = UART2 module is disabled<br>0 = UART2 module is disabled<br>0 = UART1 module is disabled<br>0 = SP12 module is enabled<br>bit 4 SP12MD: SP11 Module Disable bit<br>1 = SP11 module is enabled<br>bit 3 SP11MD: SP11 Module Disable bit<br>1 = SP11 module is disabled<br>0 = SP12 module is disabled<br>0 = SP11 module is disabled<br>0 = SP12 module is disabled<br>0 = SP12 module is disabled<br>1 = ADC Module Disable bit<br>1 = ADC module is disabled                                                                                                                                                                                                                                                                                                           | R = Readable   | e bit          | W = Writable                   | bit       | U = Unimplem      | ented bit, rea | ad as '0'       |                |

| 1 = Timer5 module is disabled         0 = Timer5 module is enabled         bit 14       T4MD: Timer4 Module Disable bit         1 = Timer4 module is disabled         0 = Timer3 module is disabled         0 = Timer2 module is disabled         0 = PWMM module Disable bit         1 = PWMx module is disabled         0 = PWMx module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = UART2 module is disabled         0 = UART1 module is disabled         0 = UART1 module is di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -n = Value at  | POR            | '1' = Bit is set               |           | '0' = Bit is clea | ared           | x = Bit is unkn | own            |

| 1 = Timer5 module is disabled         0 = Timer5 module is enabled         bit 14       T4MD: Timer4 Module Disable bit         1 = Timer4 module is disabled         0 = Timer3 module is disabled         0 = Timer2 module is disabled         0 = PWMx module is disabled         0 = PWMx module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = UART2 module is disabled         0 = UART1 module is disabled         0 = UART1 module is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | hit 15         | T5MD. Timor    | 5 Modulo Dical                 | alo hit   |                   |                |                 |                |

| 0 = Timer5 module is enabled         bit 14       TMMD: Timer4 Module Disable bit         1 = Timer4 module is enabled         bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer3 Module Disable bit         1 = Timer2 module is disabled         0 = Timer3 module is disabled         0 = Timer4 module is disabled         0 = PWMMx module Disable bit         1 = PWMx module is disabled         1 = PWMx module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = U2RT1 module is disabled         0 = UART2 module is disabled         0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 15         |                |                                |           |                   |                |                 |                |

| 1 = Timer4 module is disabled         0 = Timer4 module is enabled         bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled       0 = Timer3 module is disabled         0 = Timer2 module is disabled       0 = Timer2 module is disabled         0 = Timer2 module is disabled       0 = Timer2 module is disabled         0 = Timer2 module is disabled       0 = Timer2 module is disabled         0 = Timer2 module is disabled       0 = Timer2 module is disabled         0 = Timer1 module Disable bit       1 = Timer1 module is disabled         0 = Timer2 module is disabled       0 = Timer2 module is disabled         0 = Timer4 module Disable bit       1 = Timer1 module Disable bit         1 = Timer1 module is disabled       0 = Timer2 module is disabled         0 = PWMMD: PWMx Module Disable bit       1 = PWMx module Disable bit         1 = I2C1 module is disabled       0 = PWX module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = UART2 module Disable bit       1 = UART2 module Disable bit         1 = UART2 module is disabled       0 = UART2 module is disabled         0 = UART2 module is disabled       0 = UART1 module is disabled         0 = UART2 module is disabled       0 = UART1 module is disabled         0 = SPI2 module is disabled       0 = SPI2 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                |                                |           |                   |                |                 |                |

| bit 13 Timer3 Module Disabled<br>bit 13 TaMD: Timer3 Module Disable bit<br>1 = Timer3 module is enabled<br>bit 12 T2MD: Timer2 Module Disable bit<br>1 = Timer2 module is enabled<br>bit 12 T1MD: Timer1 Module Disable bit<br>1 = Timer1 module is disabled<br>0 = Timer1 module is disabled<br>0 = Timer1 module is disabled<br>0 = Timer1 module Disable bit<br>1 = PWMx module Disable bit<br>1 = DWMx module Disable bit<br>1 = DWMx module Disable bit<br>1 = L2C1 module is disabled<br>0 = IZC1 module is disabled<br>0 = IZC1 module is disabled<br>0 = UART2 module Disable bit<br>1 = UART2 module Disable bit<br>1 = UART2 module is disabled<br>0 = UART2 module is disabled<br>0 = UART2 module is disabled<br>0 = UART2 module Disable bit<br>1 = UART1 module is disabled<br>0 = SP12 module is disabled<br>0 = SP12 module is disabled<br>0 = SP11 module is disabled<br>1 = ADC module is disabled bit<br>1 = ADC module is dis | bit 14         | T4MD: Timer    | 4 Module Disal                 | ole bit   |                   |                |                 |                |

| bit 13 T3MD: Timer3 Module Disable bit<br>1 = Timer3 module is disabled<br>0 = Timer3 module is enabled<br>bit 12 T2MD: Timer2 Module Disable bit<br>1 = Timer2 module is enabled<br>0 = Timer2 module is enabled<br>bit 11 T1MD: Timer1 Module Disable bit<br>1 = Timer1 module is enabled<br>bit 10 Unimplemented: Read as '0'<br>bit 9 PWMMD: PWMx Module Disable bit<br>1 = PVMx module is enabled<br>bit 10 Unimplemented: Read as '0'<br>bit 9 PWMMD: PWMx Module Disable bit<br>1 = PVMx module is enabled<br>bit 8 Unimplemented: Read as '0'<br>bit 7 I2C1MD: I2C1 Module Disable bit<br>1 = I2C1 module is disabled<br>0 = I2C1 module is disabled<br>0 = I2C1 module is disabled<br>bit 6 U2MD: UART2 Module Disable bit<br>1 = UART2 module is disabled<br>0 = UART2 module is disabled<br>0 = UART1 module is disabled<br>0 = SPI2 module is disabled<br>bit 3 SPI2MD: SPI2 Module Disable bit<br>1 = SPI2 module is disabled<br>0 = SPI2 module is disabled<br>bit 3 SPI1 Module Disable bit<br>1 = SPI2 module is disabled<br>0 = SPI1 module is disabled<br>1 = SPI1 module is disabled<br>0 = SPI1 module is disabled<br>1 = ADC module is disable bit<br>1 = ADC module is disable    |                | 1 = Timer4 m   | odule is disable               | ed        |                   |                |                 |                |

| 1 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is enabled         bit 11       TIMD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = Timer1 module is disabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         bit 10       Unimplemented: Read as '0'         bit 9       PWMMD: PWMX Module Disable bit         1 = PWMx module is disabled       0 = PWMx module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1MD: I2C1 Module Disable bit         1 = 12C1 module is disabled       0 = I2C1 module is enabled         0 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = UART2 module is disabled       0 = UART2 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is enabled         bit 4       SPI2MD: SPI2 Module Disable bit         1 = SPI2 module is enabled       0 = SPI1 module is enabled         bit 3       SPI1MD: SPI1 Module Disable bit         1 = SPI2 module is enabled       0 = SPI1 module is enabled         bit 3       SPI1Module Disable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                | 0 = Timer4 m   | odule is enable                | ed        |                   |                |                 |                |

| 0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer1 module is enabled         bit 11       TIMD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWMX module Disable bit         1 = PWMX module Disable bit         1 = PUT Incolue is disabled         0 = PUT module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = UART2 module Disable bit         1 = UART2 module is disabled         0 = UART1 module Disable bit         1 = UART1 module Disable bit         1 = UART1 module is disabled         0 = UART2 module is disabled         0 = UART1 module is disabled         0 = SPI2 Module Disable bit         1 = SPI2 module is disabled         0 = SPI1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 13         |                |                                |           |                   |                |                 |                |

| bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       TIMD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWMX module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = UART2 module is disabled         0 = UART2 module is disabled         0 = UART1 module is disabled         0 = SPI2MD: SPI1 Module Disable bit         1 = SP12 module is disabled         0 = SPI1 module is disabled         0 = SPI1 module is disabled         0 = SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |                |                                |           |                   |                |                 |                |

| 1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWMx module Disable bit         1 = PWMx module is disabled         0 = PWMx module is disabled         0 = PWMx module is disabled         0 = PWMx module Disable bit         1 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = UART2 module is disabled         0 = UART2 module is disabled         0 = UART1 module is disabled         0 = SP12 module is disabled         0 = SP12 module is disabled         0 = SP11 module is disabled         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | hit 10         |                |                                |           |                   |                |                 |                |