Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

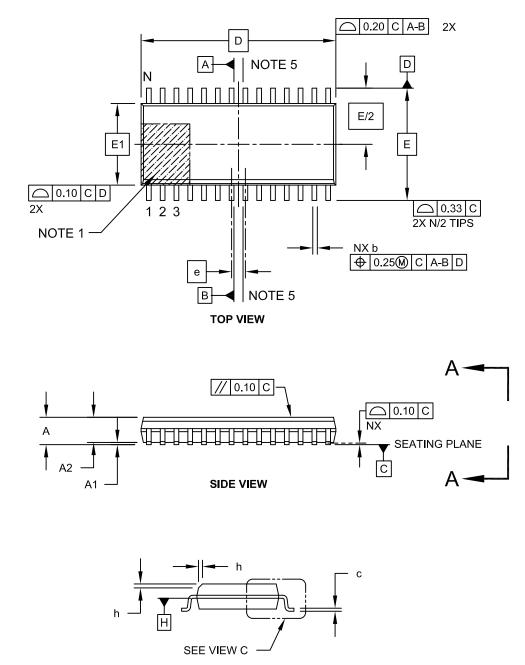

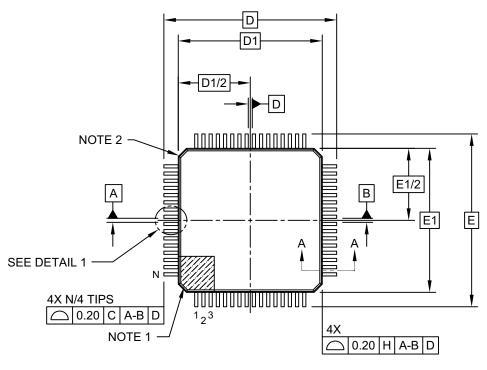

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep16gs506-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

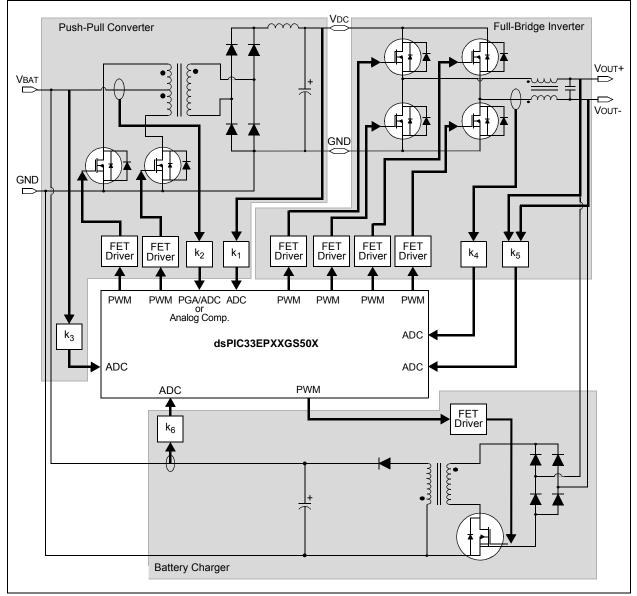

## FIGURE 2-6: OFF-LINE UPS

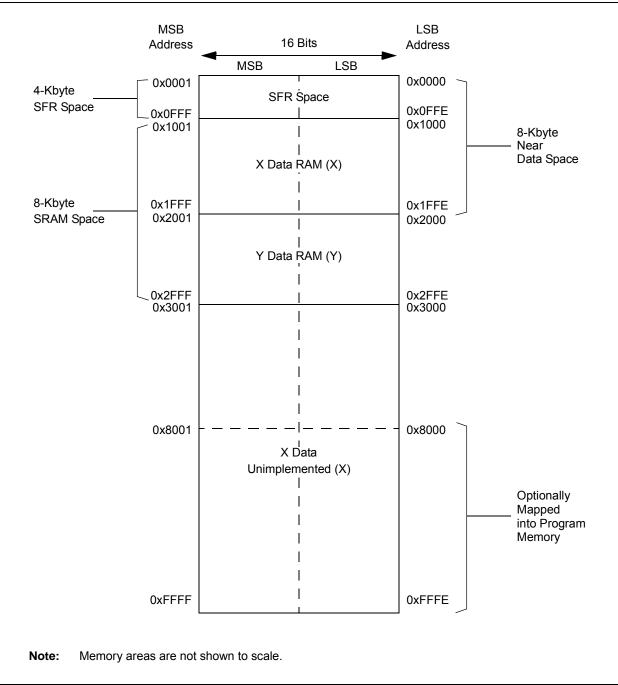

#### FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD |       | —      | ADCMD | 0000          |

| PMD2        | 0762  |        | —      | —      | -      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | -      |       | —     | -      | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3        | 0764  | Ι      | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | _     | _      | _      | _     | I2C2MD | _     | 0000          |

| PMD4        | 0766  | Ι      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | _     | _      | _     | 0000          |

| PMD6        | 076A  | Ι      | _      | _      | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _     | _      | _     | 0000          |

| PMD7        | 076C  | Ι      | _      | _      | _      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | _     | _     | _      | _      | _     | PGA1MD | _     | 0000          |

| PMD8        | 076E  | _      | —      | _      | —      | _      | PGA2MD | ABGMD  | _      | _      | _     | —     | _      | _      | _     | CCSMD  |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: CONSTANT-CURRENT SOURCE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|-------|-------|----------|----------|----------|----------|----------|----------|---------------|

| ISRCCON     | 0500  | ISRCEN | _      |        | _      |        | OUTSEL2 | OUTSEL1 | OUTSEL0 | _     | _     | ISRCCAL5 | ISRCCAL4 | ISRCCAL3 | ISRCCAL2 | ISRCCAL1 | ISRCCAL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-25: PROGRAMMABLE GAIN AMPLIFIER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| PGA1CON     | 0504  | PGAEN  | PGAOEN | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 | _     | _     |       |       |       | GAIN2  | GAIN1 | GAIN0 | 0000          |

| PGA1CAL     | 0506  | _      | —      | —      | —      | _      | —      | _      | _      | —     | —     |       |       | PGACA | L<5:0> |       |       | 0000          |

| PGA2CON     | 0508  | PGAEN  | PGAOEN | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 | —     | _     | _     | —     | _     | GAIN2  | GAIN1 | GAIN0 | 0000          |

| PGA2CAL     | 050A  | _      | —      | —      | —      | _      | —      | _      | _      | —     | —     |       |       | PGACA | L<5:0> |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

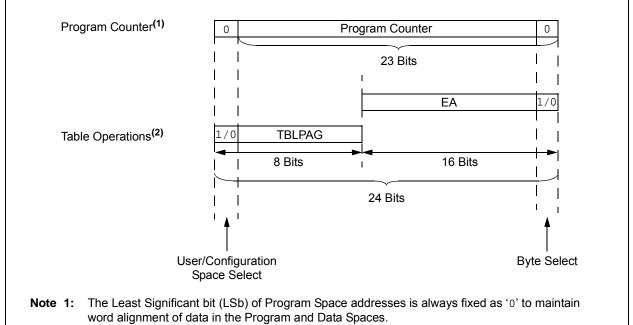

## 4.9 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXGS50X family architecture uses a 24-bit wide Program Space (PS) and a 16-bit wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXGS50X family devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## TABLE 4-40: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Type            | Access        |      | Progra      | m Space A | ddress        |     |

|------------------------|---------------|------|-------------|-----------|---------------|-----|

| Access Type            | Space         | <23> | <22:16>     | <15>      | <14:1>        | <0> |

| Instruction Access     | User          | 0    |             | PC<22:1>  |               | 0   |

| (Code Execution)       |               |      | 0xxx xxxx x | xxx xxx   | x xxxx xxx0   |     |

| TBLRD/TBLWT            | User          | TB   | LPAG<7:0>   |           | Data EA<15:0> |     |

| (Byte/Word Read/Write) |               | 0    | xxx xxxx    | XXXX      |               | xx  |

|                        | Configuration | TB   | LPAG<7:0>   |           | Data EA<15:0> |     |

|                        |               | 1    | xxx xxxx    | xxxx      | * ****        | xx  |

### FIGURE 4-14: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

**2:** Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-------|-------|-------|-----|-----|-------|

| VAR    | —   | US1   | US0   | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |       |       |       |     |     | bit 8 |

|        |     |       |       |       |     |     |       |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-----|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7 |       |       |        |                     |     |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

- 1 = Variable exception processing is enabled

- 0 = Fixed exception processing is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0          | U-0          | U-0                | U-0              | U-0              | U-0              | U-0             | R/W-0 |

|--------------|--------------|--------------------|------------------|------------------|------------------|-----------------|-------|

| _            | —            | —                  | —                | _                | —                | —               | NAE   |

| bit 15       |              |                    |                  |                  |                  |                 | bit 8 |

|              |              |                    |                  |                  |                  |                 |       |

| U-0          | U-0          | U-0                | R/W-0            | U-0              | U-0              | U-0             | R/W-0 |

| —            | —            |                    | DOOVR            | —                |                  |                 | APLL  |

| bit 7        |              |                    |                  |                  |                  |                 | bit 0 |

|              |              |                    |                  |                  |                  |                 |       |

| Legend:      |              |                    |                  |                  |                  |                 |       |

| R = Readal   | ole bit      | W = Writable       | bit              | U = Unimple      | mented bit, read | as '0'          |       |

| -n = Value a | at POR       | '1' = Bit is se    | t                | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|              |              |                    |                  |                  |                  |                 |       |

| bit 15-9     | Unimplemer   | nted: Read as      | '0'              |                  |                  |                 |       |

| bit 8        | NAE: NVM A   | ddress Error S     | Soft Trap Status | s bit            |                  |                 |       |

|              |              |                    | trap has occur   |                  |                  |                 |       |

|              |              |                    | trap has not o   | ccurred          |                  |                 |       |

| bit 7-5      | Unimplemer   | nted: Read as      | '0'              |                  |                  |                 |       |

| bit 4        | DOOVR: DO    | Stack Overflov     | v Soft Trap Sta  | tus bit          |                  |                 |       |

|              | 1 = DO stack | overflow soft t    | rap has occurre  | ed               |                  |                 |       |

|              | 0 = DO stack | overflow soft t    | rap has not oc   | curred           |                  |                 |       |

| bit 3-1      | Unimplemer   | nted: Read as      | '0'              |                  |                  |                 |       |

| bit 0        | APLL: Auxili | ary PLL Loss o     | of Lock Soft Tra | ap Status bit    |                  |                 |       |

|              | 1 = APLL loc | k soft trap has    | occurred         |                  |                  |                 |       |

|              |              | le a aft trans has | wet easy word    |                  |                  |                 |       |

0 = APLL lock soft trap has not occurred

### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0          | U-0          | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|--------------|------------------|----------------|------------------|------------------|-----------------|-------|

| _            | —            | —                | —              | —                | —                | —               | —     |

| bit 15       |              |                  |                |                  |                  |                 | bit 8 |

|              |              |                  |                |                  |                  |                 |       |

| U-0          | U-0          | U-0              | U-0            | U-0              | U-0              | U-0             | R/W-0 |

| _            | —            | —                | —              | —                | —                | —               | SGHT  |

| bit 7        |              | •                |                |                  |                  | •               | bit 0 |

|              |              |                  |                |                  |                  |                 |       |

| Legend:      |              |                  |                |                  |                  |                 |       |

| R = Readab   | le bit       | W = Writable     | bit            | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value a | t POR        | '1' = Bit is set | t              | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

|              |              |                  |                |                  |                  |                 |       |

| bit 15-1     | Unimplemen   | ted: Read as     | '0'            |                  |                  |                 |       |

| bit 0        | SGHT: Softwa | are Generated    | Hard Trap Sta  | tus bit          |                  |                 |       |

|              | 1 = Software | generated har    | d trap has occ | urred            |                  |                 |       |

|              | 0 = Software | generated har    | d trap has not | occurred         |                  |                 |       |

|              |              |                  |                |                  |                  |                 |       |

|              |              |                  |                |                  |                  |                 |       |

#### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| R/W-0           | U-0                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON            |                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                           | ROSEL                                                                                                                                                                                                | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15          |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       | bit 8                 |

| U-0             | U-0                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                  | U-0                   | U-0                   | U-0                   | U-0                   |

| _               | _                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                    |                       | —                     | —                     | _                     |

| bit 7           |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       | bit C                 |

| Legend:         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |

| R = Readable    | bit                                                                                                                                                                                                          | W = Writable b                                                                                                                                                                                                                                                                                                                                   | bit                                                                                                                                                                                                  | U = Unimplem          | nented bit, read      | l as '0'              |                       |

| -n = Value at F |                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                      | '0' = Bit is clea     |                       | x = Bit is unkr       | nown                  |

|                 |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |

| bit 15          | 1 = Reference                                                                                                                                                                                                | ence Oscillator<br>e oscillator outp<br>e oscillator outp                                                                                                                                                                                                                                                                                        | ut is enabled of                                                                                                                                                                                     |                       | 2)                    |                       |                       |

| bit 14          | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                    |                       |                       |                       |                       |

| bit 13          | ROSSLP: Re                                                                                                                                                                                                   | ference Oscillat                                                                                                                                                                                                                                                                                                                                 | or Run in Slee                                                                                                                                                                                       | ep bit                |                       |                       |                       |

|                 |                                                                                                                                                                                                              | e oscillator outp<br>e oscillator outp                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      |                       |                       |                       |                       |

| bit 12          | ROSEL: Refe                                                                                                                                                                                                  | erence Oscillato                                                                                                                                                                                                                                                                                                                                 | r Source Sele                                                                                                                                                                                        | ct bit                |                       |                       |                       |

|                 |                                                                                                                                                                                                              | crystal is used ock is used as                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                      |                       |                       |                       |                       |

| bit 11-8        | •                                                                                                                                                                                                            | Reference Osc                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                      |                       |                       |                       |                       |

|                 | 1110 = Refer<br>1101 = Refer<br>1100 = Refer<br>1011 = Refer<br>1010 = Refer<br>1000 = Refer<br>0111 = Refer<br>0110 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0101 = Refer<br>0011 = Refer | ence clock divic<br>ence clock divic | led by 16,384<br>led by 8,192<br>led by 4,096<br>led by 2,048<br>led by 1,024<br>led by 512<br>led by 512<br>led by 256<br>led by 128<br>led by 64<br>led by 32<br>led by 16<br>led by 8<br>led by 4 |                       |                       |                       |                       |

| bit 7-0         | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                    |                       |                       |                       |                       |

|                 | •                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

| R/W-0                                                                                                     | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC4R6                                                                                                     | IC4R5                                                                            | IC4R4                                                                                                                                                                                                                                                                                                                                                                                      | IC4R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IC4R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IC4R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IC4R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R/W-0                                                                                                     | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| IC3R6                                                                                                     | IC3R5                                                                            | IC3R4                                                                                                                                                                                                                                                                                                                                                                                      | IC3R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IC3R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IC3R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IC3R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                           |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                           |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |