Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

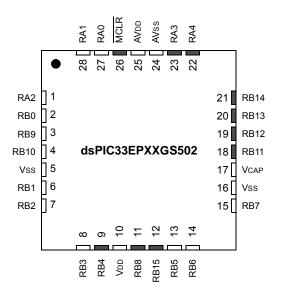

### **Pin Diagrams (Continued)**

#### 28-Pin QFN-S, UQFN

| Pin | Pin Function                              | Pin | Pin Function                 |

|-----|-------------------------------------------|-----|------------------------------|

| 1   | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         | 15  | PGEC1/AN21/SDA1/RP39/RB7     |

| 2   | AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0           | 16  | Vss                          |

| 3   | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            | 17  | VCAP                         |

| 4   | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10           | 18  | TMS/PWM3H/ <b>RP43</b> /RB11 |

| 5   | 5 Vss                                     |     | TCK/PWM3L/RP44/RB12          |

| 6   | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  | 20  | PWM2H/ <b>RP45</b> /RB13     |

| 7   | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/RP34/RB2 | 21  | PWM2L/ <b>RP46</b> /RB14     |

| 8   | PGED2/AN18/DACOUT1/INT0/ <b>RP35</b> /RB3 | 22  | PWM1H/RA4                    |

| 9   | PGEC2/ADTRG31/EXTREF1/RP36/RB4            | 23  | PWM1L/RA3                    |

| 10  | Vdd                                       | 24  | AVss                         |

| 11  | PGED3/SDA2/FLT31/RP40/RB8                 | 25  | AVdd                         |

| 12  | PGEC3/SCL2/ <b>RP47</b> /RB15             | 26  | MCLR                         |

| 13  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         | 27  | AN0/PGA1P1/CMP1A/RA0         |

| 14  | PGED1/TDI/AN20/SCL1/ <b>RP38</b> /RB6     | 28  | AN1/PGA1P2/PGA2P1/CMP1B/RA1  |

Legend: Shaded pins are up to 5 VDC tolerant. RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

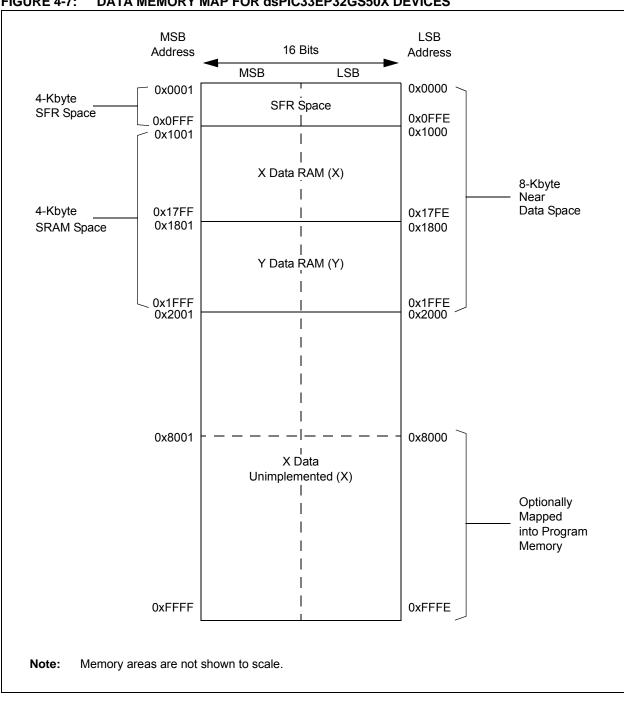

#### FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32GS50X DEVICES

#### TABLE 4-28: PORTA REGISTER MAP FOR dsPIC33EPXXGS502 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-----------|-------|------------|-----------|-------|---------------|

| TRISA       | 0E00  |        | _      | _      | _      |        |        | _     | _     |       |       |       |           |       | RISA<4:0>  | •         |       | 001F          |

| PORTA       | 0E02  | —      | —      | —      |        | _      |        | _     | —     |       |       | _     |           |       | RA<4:0>    |           |       | 0000          |

| LATA        | 0E04  | —      | —      | —      |        | _      |        | _     | —     |       |       | _     | LATA<4:0> |       |            | 0000      |       |               |

| ODCA        | 0E06  | —      | —      | —      |        | _      |        | _     | —     | -     |       | _     |           | (     | DDCA<4:0>  |           |       | 0000          |

| CNENA       | 0E08  | —      | —      | —      |        | _      |        | _     | —     | -     |       | _     |           | (     | CNIEA<4:0> | •         |       | 0000          |

| CNPUA       | 0E0A  | —      | —      | —      |        | _      |        | _     | —     | -     |       | _     |           | С     | NPUA<4:0   | >         |       | 0000          |

| CNPDA       | 0E0C  | —      | —      | —      |        | _      |        | _     | —     | -     |       | _     |           | С     | NPDA<4:0   | >         |       | 0000          |

| ANSELA      | 0E0E  | _      | _      | —      | -      | _      | _      | _     | -     | _     | _     |       | _         | _     | /          | ANSA<2:0> |       | 0007          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-29: PORTB REGISTER MAP FOR dsPIC33EPXXGS502 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|------------------------------------------------------|--------|--------|--------|--------|-------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB       | 0E10  |        | TRISB<15:0> FFFF                                     |        |        |        |        |       |          | FFFF  |       |       |       |       |       |       |       |               |

| PORTB       | 0E12  |        | RB<15:0> xxxx                                        |        |        |        |        |       |          | xxxx  |       |       |       |       |       |       |       |               |

| LATB        | 0E14  |        | LATB<15:0> xxx                                       |        |        |        |        |       |          | xxxx  |       |       |       |       |       |       |       |               |

| ODCB        | 0E16  |        |                                                      |        |        |        |        |       | ODCB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNENB       | 0E18  |        |                                                      |        |        |        |        |       | CNIEB<18 | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPUB       | 0E1A  |        | CNPUB<15:0> 00                                       |        |        |        |        |       | 0000     |       |       |       |       |       |       |       |       |               |

| CNPDB       | 0E1C  |        | CNPDB<15:0> 00                                       |        |        |        |        |       | 0000     |       |       |       |       |       |       |       |       |               |

| ANSELB      | 0E1E  | _      | <u>− − − − ANSB&lt;10:9&gt; − ANSB&lt;7:0&gt;</u> 00 |        |        |        |        | 06FF  |          |       |       |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 7-1: INTERRUPT VECTOR DETAILS

|                                      | Vector | IRQ       |                     | Inte     | errupt Bit Lo | cation      |

|--------------------------------------|--------|-----------|---------------------|----------|---------------|-------------|

| Interrupt Source                     | #      | #         | IVT Address         | Flag     | Enable        | Priority    |

|                                      | Hi     | ghest Nat | ural Order Priority | •        |               |             |

| INT0 – External Interrupt 0          | 8      | 0         | 0x000014            | IFS0<0>  | IEC0<0>       | IPC0<2:0>   |

| IC1 – Input Capture 1                | 9      | 1         | 0x000016            | IFS0<1>  | IEC0<1>       | IPC0<6:4>   |

| OC1 – Output Compare 1               | 10     | 2         | 0x000018            | IFS0<2>  | IEC0<2>       | IPC0<10:8>  |

| T1 – Timer1                          | 11     | 3         | 0x00001A            | IFS0<3>  | IEC0<3>       | IPC0<14:12> |

| Reserved                             | 12     | 4         | 0x00001C            | _        |               | _           |

| IC2 – Input Capture 2                | 13     | 5         | 0x00001E            | IFS0<5>  | IEC0<5>       | IPC1<6:4>   |

| OC2 – Output Compare 2               | 14     | 6         | 0x000020            | IFS0<6>  | IEC0<6>       | IPC1<10:8>  |

| T2 – Timer2                          | 15     | 7         | 0x000022            | IFS0<7>  | IEC0<7>       | IPC1<14:12> |

| T3 – Timer3                          | 16     | 8         | 0x000024            | IFS0<8>  | IEC0<8>       | IPC2<2:0>   |

| SPI1E – SPI1 Error                   | 17     | 9         | 0x000026            | IFS0<9>  | IEC0<9>       | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done            | 18     | 10        | 0x000028            | IFS0<10> | IEC0<10>      | IPC2<10:8>  |

| U1RX – UART1 Receiver                | 19     | 11        | 0x00002A            | IFS0<11> | IEC0<11>      | IPC2<14:12> |

| U1TX – UART1 Transmitter             | 20     | 12        | 0x00002C            | IFS0<12> | IEC0<12>      | IPC3<2:0>   |

| ADC – ADC Global Convert Done        | 21     | 13        | 0x00002E            | IFS0<13> | IEC0<13>      | IPC3<6:4>   |

| Reserved                             | 22     | 14        | 0x000030            | _        | _             | _           |

| NVM – NVM Write Complete             | 23     | 15        | 0x000032            | IFS0<15> | IEC0<15>      | IPC3<14:12> |

| SI2C1 – I2C1 Slave Event             | 24     | 16        | 0x000034            | IFS1<0>  | IEC1<0>       | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event            | 25     | 17        | 0x000036            | IFS1<1>  | IEC1<1>       | IPC4<6:4>   |

| CMP1 – Analog Comparator 1 Interrupt | 26     | 18        | 0x000038            | IFS1<2>  | IEC1<2>       | IPC4<10:8>  |

| CN – Input Change Interrupt          | 27     | 19        | 0x00003A            | IFS1<3>  | IEC1<3>       | IPC4<14:12> |

| INT1 – External Interrupt 1          | 28     | 20        | 0x00003C            | IFS1<4>  | IEC1<4>       | IPC5<2:0>   |

| Reserved                             | 29-32  | 21-24     | 0x00003E-0x000044   | _        | _             | _           |

| OC3 – Output Compare 3               | 33     | 25        | 0x000046            | IFS1<9>  | IEC1<9>       | IPC6<6:4>   |

| OC4 – Output Compare 4               | 34     | 26        | 0x000048            | IFS1<10> | IEC1<10>      | IPC6<10:8>  |

| T4 – Timer4                          | 35     | 27        | 0x00004A            | IFS1<11> | IEC1<11>      | IPC6<14:12> |

| T5 – Timer5                          | 36     | 28        | 0x00004C            | IFS1<12> | IEC1<12>      | IPC7<2:0>   |

| INT2 – External Interrupt 2          | 37     | 29        | 0x00004E            | IFS1<13> | IEC1<13>      | IPC7<6:4>   |

| U2RX – UART2 Receiver                | 38     | 30        | 0x000050            | IFS1<14> | IEC1<14>      | IPC7<10:8>  |

| U2TX – UART2 Transmitter             | 39     | 31        | 0x000052            | IFS1<15> | IEC1<15>      | IPC7<14:12> |

| SPI2E – SPI2 Error                   | 40     | 32        | 0x000054            | IFS2<0>  | IEC2<0>       | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done            | 41     | 33        | 0x000056            | IFS2<1>  | IEC2<1>       | IPC8<6:4>   |

| Reserved                             | 42-44  | 34-36     | 0x000058-0x00005C   | —        | _             | _           |

| IC3 – Input Capture 3                | 45     | 37        | 0x00005E            | IFS2<5>  | IEC2<5>       | IPC9<6:4>   |

| IC4 – Input Capture 4                | 46     | 38        | 0x000060            | IFS2<6>  | IEC2<6>       | IPC9<10:8>  |

| Reserved                             | 47-56  | 39-48     | 0x000062-0x000074   | _        | _             | _           |

| SI2C2 – I2C2 Slave Event             | 57     | 49        | 0x000076            | IFS3<1>  | IEC3<1>       | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event            | 58     | 50        | 0x000078            | IFS3<2>  | IEC3<2>       | IPC12<10:8> |

| Reserved                             | 59-61  | 51-53     | 0x00007A-0x00007E   | _        | _             | _           |

| INT4 – External Interrupt 4          | 62     | 54        | 0x000080            | IFS3<6>  | IEC3<6>       | IPC13<10:8> |

| Reserved                             | 63-64  | 55-54     | 0x000082-0x000084   | —        |               | _           |

| PSEM – PWM Special Event Match       | 65     | 57        | 0x000086            | IFS3<9>  | IEC3<9>       | IPC14<6:4>  |

| Reserved                             | 66-72  | 58-64     | 0x000088-0x000094   | —        |               | _           |

| U1E – UART1 Error Interrupt          | 73     | 65        | 0x000096            | IFS4<1>  | IEC4<1>       | IPC16<6:4>  |

| U2E – UART2 Error Interrupt          | 74     | 66        | 0x000098            | IFS4<2>  | IEC4<2>       | IPC16<10:8> |

| Reserved                             | 75-80  | 67-72     | 0x00009A-0x0000A4   | —        |               | _           |

### DS70005127D-page 104

| U-0          | U-0                        | U-0              | U-0            | U-0                                | R/W-0           | U-0    | U-0   |  |  |  |

|--------------|----------------------------|------------------|----------------|------------------------------------|-----------------|--------|-------|--|--|--|

| _            | —                          | —                | —              | —                                  | CMPMD           | —      | _     |  |  |  |

| bit 15       |                            |                  |                |                                    |                 |        | bit 8 |  |  |  |

|              |                            |                  |                |                                    |                 |        |       |  |  |  |

| U-0          | U-0                        | U-0              | U-0            | U-0                                | U-0             | R/W-0  | U-0   |  |  |  |

| _            | _                          | _                | —              | _                                  | —               | I2C2MD | —     |  |  |  |

| bit 7        |                            |                  |                |                                    |                 |        | bit 0 |  |  |  |

|              |                            |                  |                |                                    |                 |        |       |  |  |  |

| Legend:      |                            |                  |                |                                    |                 |        |       |  |  |  |

| R = Readab   | ole bit                    | W = Writable     | bit            | U = Unimplemented bit, read as '0' |                 |        |       |  |  |  |

| -n = Value a | at POR                     | '1' = Bit is set |                | '0' = Bit is clea                  | x = Bit is unkn | own    |       |  |  |  |

|              |                            |                  |                |                                    |                 |        |       |  |  |  |

| bit 15-11    | Unimplement                | ted: Read as '   | כ'             |                                    |                 |        |       |  |  |  |

| bit 10       | CMPMD: Con                 | nparator Modul   | le Disable bit |                                    |                 |        |       |  |  |  |

|              | 1 = Comparat               | or module is di  | sabled         |                                    |                 |        |       |  |  |  |

|              | 0 = Comparat               | or module is ei  | nabled         |                                    |                 |        |       |  |  |  |

| bit 9-2      | Unimplemented: Read as '0' |                  |                |                                    |                 |        |       |  |  |  |

| bit 1        | 12C2MD: 12C2               |                  |                |                                    |                 |        |       |  |  |  |

|              |                            | ule is disabled  |                |                                    |                 |        |       |  |  |  |

|              | 0 = I2C2 mod               | ule is enabled   |                |                                    |                 |        |       |  |  |  |

#### REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 0 | Unimplemented: Read as '0' |

|-------|----------------------------|

|       |                            |

#### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0  | U-0  | U-0 | U-0  | U-0  | U-0   |

|--------|-----|------|------|-----|------|------|-------|

| —      | —   | —    | —    | —   | —    | —    | —     |

| bit 15 |     |      |      |     |      |      | bit 8 |

|        |     |      |      |     |      |      |       |

| 11.0   |     | 11.0 | 11.0 |     | 11.0 | 11.0 | 11.0  |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                        |  |  |  |

|----------|---------------------------------------------------|--|--|--|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit |  |  |  |

|          | 1 = Reference clock module is disabled            |  |  |  |

|          | 0 = Reference clock module is enabled             |  |  |  |

| bit 2-0  | Unimplemented: Read as '0'                        |  |  |  |

### 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control x register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 26-11 for the maximum VIH specification for each pin.

#### 10.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

#### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP, as shown in Example 10-1.

### **10.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the ICN functionality of each I/O port. The CNENx registers contain the ICN interrupt enable control bits for each of the input pins. Setting any of these bits enables an ICN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source, or sink source, connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on Input Change Notification pins should always be disabled when the port pin is configured as a digital output.

#### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

### 10.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 10.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions.

#### 10.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. One example includes  $I^2C$  modules. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 10.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

### 10.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 26-11 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 26.0 "Electrical Characteristics" of this data sheet. For example:

Vон = 2.4v @ Iон = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 27.0 "DC and AC Device Characteristics Graphs"** for additional information.

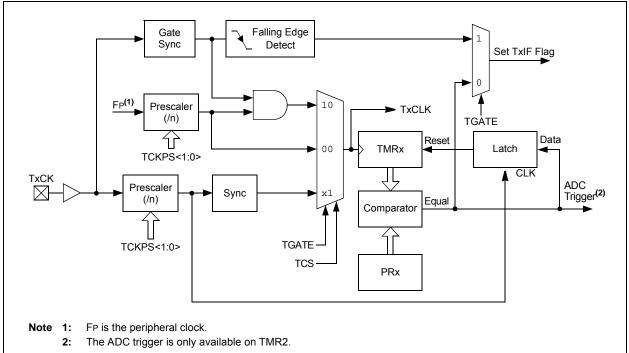

#### FIGURE 12-1: TIMERX BLOCK DIAGRAM (x = 2 THROUGH 5)

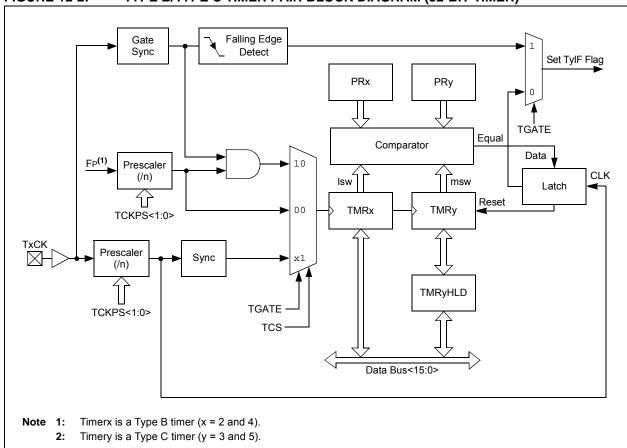

### FIGURE 12-2: TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

#### **REGISTER 15-20:** IOCONX: PWMx I/O CONTROL REGISTER (x = 1 to 5) (CONTINUED)

| bit 3-2 | CLDAT<1:0>: State for PWMxH and PWMxL Pins if CLMOD is Enabled bits <sup>(2)</sup>                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | IFLTMOD (FCLCONx<15>) = 0: Normal Fault Mode:                                                                                                                                                                    |

|         | If current limit is active, then CLDAT1 provides the state for the PWMxH pin.                                                                                                                                    |

|         | If current limit is active, then CLDAT0 provides the state for the PWMxL pin.                                                                                                                                    |

|         | IFLTMOD (FCLCONx<15>) = 1: Independent Fault Mode:                                                                                                                                                               |

|         | CLDAT<1:0> bits are ignored.                                                                                                                                                                                     |

| bit 1   | SWAP: SWAP PWMxH and PWMxL Pins bit                                                                                                                                                                              |

|         | <ul> <li>1 = PWMxH output signal is connected to the PWMxL pins; PWMxL output signal is connected to the<br/>PWMxH pins</li> </ul>                                                                               |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                                                                                                                     |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                                                                                                                       |

|         | <ul> <li>1 = Output overrides via the OVRDAT&lt;1:0&gt; bits are synchronized to the PWMx time base</li> <li>0 = Output overrides via the OVRDAT&lt;1:0&gt; bits occur on the next CPU clock boundary</li> </ul> |

|         |                                                                                                                                                                                                                  |

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: State represents the active/inactive state of the PWMx depending on the POLH and POLL bits settings.

#### **REGISTER 15-21:** TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 5)

| R/W-0                              | R/W-0 | R/W-0       | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------------|------------------------------------|-----------------------------------------|-------|-------|-------|

|                                    |       |             | TRGC                               | MP<12:5>                                |       |       |       |

| bit 15                             |       |             |                                    |                                         |       |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0       | R/W-0                              | R/W-0                                   | U-0   | U-0   | U-0   |

|                                    |       | TRGCMP<4:0> | >                                  |                                         |       | _     | —     |

| bit 7                              |       |             |                                    |                                         |       | bit C |       |

| Legend:                            |       |             |                                    |                                         |       |       |       |

| R = Readable bit W = Writable bit  |       |             | U = Unimplemented bit, read as '0' |                                         |       |       |       |

| -n = Value at POR (1' = Bit is set |       |             |                                    | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-3 **TRGCMP<12:0>:** Trigger Compare Value bits When the primary PWMx functions in the local time base, this register contains the compare values that can trigger the ADC module.

bit 2-0 Unimplemented: Read as '0'

#### REGISTER 19-27: ADTRIGXH: ADC CHANNEL TRIGGER x SELECTION REGISTER HIGH (x = 0 to 5) (CONTINUED)

- bit 4-0 TRGSRC(4x+2)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

- 11111 = ADTRG31

- 11110 = Reserved

- 11101 = Reserved

- 11100 = PWM Generator 5 current-limit trigger

- 11011 = PWM Generator 4 current-limit trigger

- 11010 = PWM Generator 3 current-limit trigger

- 11001 = PWM Generator 2 current-limit trigger

- 11000 = PWM Generator 1 current-limit trigger

- 10111 = Output Compare 2 trigger

- 10110 = Output Compare 1 trigger

- 10101 = Reserved 10100 = Reserved

- 10011 = PWM Generator 5 secondary trigger

- 10010 = PWM Generator 4 secondary trigger

- 10001 = PWM Generator 3 secondary trigger

- 10000 = PWM Generator 2 secondary trigger

- 01111 = PWM Generator 1 secondary trigger

- 01110 = PWM secondary Special Event Trigger

- 01101 = Timer2 period match

- 01100 = Timer1 period match

- 01011 = Reserved

- 01010 = Reserved

- 01001 = PWM Generator 5 primary trigger

- 01000 = PWM Generator 4 primary trigger

- 00111 = PWM Generator 3 primary trigger

- 00110 = PWM Generator 2 primary trigger

- 00101 = PWM Generator 1 primary trigger

- 00100 = PWM Special Event Trigger

- 00011 = Reserved

- 00010 = Level software trigger

- 00001 = Common software trigger

- 00000 = No trigger is enabled

#### REGISTER 19-34: ADFLxCON: ADC DIGITAL FILTER x CONTROL REGISTER (x = 0 or 1) (CONTINUED)

#### TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |                           |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |      |                     |  |  |

|--------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------------------|--|--|

| Parameter<br>No.   | Тур.                      | Max. | Units                                                                                                                                                                                                                                                                                   | Conditions |      |                     |  |  |

| Operating Curr     | rent (IDD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |            |      |                     |  |  |

| DC20d              | 7                         | 12   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      |                     |  |  |

| DC20a              | 7                         | 12   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V | 10 MIPS             |  |  |

| DC20b              | 7                         | 12   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V |                     |  |  |

| DC20c              | 7                         | 12   | mA                                                                                                                                                                                                                                                                                      | +125°C     | -    |                     |  |  |

| DC22d              | 11                        | 19   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      | 20 MIPS             |  |  |

| DC22a              | 11                        | 19   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V |                     |  |  |

| DC22b              | 11                        | 19   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V |                     |  |  |

| DC22c              | 11                        | 19   | mA                                                                                                                                                                                                                                                                                      | +125°C     |      |                     |  |  |

| DC24d              | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      | 40 MIPS             |  |  |

| DC24a              | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3∨ |                     |  |  |

| DC24b              | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V |                     |  |  |

| DC24c              | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +125°C     | -    |                     |  |  |

| DC25d              | 26                        | 41   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      | 60 MIPS             |  |  |

| DC25a              | 26                        | 41   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3∨ |                     |  |  |

| DC25b              | 26                        | 41   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V |                     |  |  |

| DC25c              | 26                        | 41   | mA                                                                                                                                                                                                                                                                                      | +125°C     |      |                     |  |  |

| DC26d              | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      |                     |  |  |

| DC26a              | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V | 70 MIPS             |  |  |

| DC26b              | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | +85°C      |      |                     |  |  |

| DC27d              | 51                        | 81   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      | 70 14/00            |  |  |

| DC27a              | 51                        | 81   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V | 70 MIPS<br>(Note 2) |  |  |

| DC27b              | 52                        | 82   | mA                                                                                                                                                                                                                                                                                      | +85°C      |      | (NOLE Z)            |  |  |

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (all defined PMDx bits are set)

- CPU is executing while(1) statement

- JTAG is disabled

- **2:** For this specification, the following test conditions apply:

- · APLL clock is enabled

- All 5 PWMs enabled and operating at maximum speed (PTCON2<2:0> = 000), PTPER = 1000h, 50% duty cycle

- All other peripherals are disabled (corresponding PMDx bits are set)

| TABLE 26-14: | DC CHARACTERISTICS: PROGRAM MEMORY |

|--------------|------------------------------------|

|--------------|------------------------------------|

| DC CHARACTERISTICS |        |                                                     | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |       |            |      |                                                                |  |

|--------------------|--------|-----------------------------------------------------|---------------------------------------------------------------------------|-------|------------|------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | I Characteristic Min. Typ. <sup>(1)</sup> Max. Un   |                                                                           | Units | Conditions |      |                                                                |  |

|                    |        | Program Flash Memory                                |                                                                           |       |            |      |                                                                |  |

| D130               | Eр     | Cell Endurance                                      | 10,000                                                                    |       | _          | E/W  | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                                        | 3.0                                                                       | _     | 3.6        | V    |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write                            | 3.0                                                                       |       | 3.6        | V    |                                                                |  |

| D134               | TRETD  | Characteristic Retention                            | 20                                                                        | —     | —          | Year | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | —                                                                         | 10    | —          | mA   |                                                                |  |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up       | —                                                                         | —     | 150        | mA   |                                                                |  |

| D137a              | Тре    | Page Erase Time                                     | 19.7                                                                      | —     | 20.1       | ms   | TPE = 146893 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>         |  |

| D137b              | TPE    | Page Erase Time                                     | 19.5                                                                      | —     | 20.3       | ms   | TPE = 146893 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>        |  |

| D138a              | Tww    | Word Write Cycle Time                               | 46.5                                                                      | —     | 47.3       | μs   | Tww = 346 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>            |  |

| D138b              | Tww    | Word Write Cycle Time                               | 46.0                                                                      | —     | 47.9       | μs   | Tww = 346 FRC cycles,<br>TA = +125°C <b>(Note 3)</b>           |  |

| D139a              | Trw    | Row Write Time                                      | 667                                                                       | _     | 679        | μs   | Trw = 4965 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>           |  |

| D139b              | Trw    | Row Write Time                                      | 660                                                                       | —     | 687        | μs   | Trw = 4965 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>          |  |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 26-20) and the value of the FRC Oscillator Tuning register (see Register 8-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

### TABLE 26-38:SPix SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                                |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCKx Input Frequency                 | _                                                     | _                   | 11   | MHz   | (Note 3)                       |

| SP72               | TscF                  | SCKx Input Fall Time                         | —                                                     | _                   | _    | ns    | See Parameter DO32 (Note 4)    |

| SP73               | TscR                  | SCKx Input Rise Time                         | —                                                     | _                   | -    | ns    | See Parameter DO31<br>(Note 4) |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —                                                     | _                   | _    | ns    | See Parameter DO32 (Note 4)    |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After<br>SCKx Edge    | —                                                     | 6                   | 20   | ns    |                                |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                    | _                   |      | ns    |                                |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 30                                                    | —                   |      | ns    |                                |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 30                                                    | —                   |      | ns    |                                |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx ↓<br>Input           | 120                                                   | —                   | —    | ns    |                                |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance       | 10                                                    | _                   | 50   | ns    | (Note 4)                       |

| SP52               | TscH2ssH,<br>TscL2ssH | SSx ↑ After SCKx Edge                        | 1.5 Tcy + 40                                          | —                   | _    | ns    | (Note 4)                       |

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| Instruction Addressing Modes70                        |

|-------------------------------------------------------|

| File Register Instructions70                          |

| Fundamental Modes Supported70                         |

| MAC Instructions71                                    |

| MCU Instructions70                                    |

| Move and Accumulator Instructions                     |

| Other Instructions71                                  |

| Instruction Set Summary                               |

| Overview                                              |

| Symbols Used in Opcode Descriptions                   |

| Instruction-Based Power-Saving Modes                  |

| Idle                                                  |

| Sleep116                                              |

| Inter-Integrated Circuit (I <sup>2</sup> C)           |

| Control Registers                                     |

| Resources                                             |

| Inter-Integrated Circuit. See I <sup>2</sup> C.       |

| Internet Address                                      |

| Interrupt Controller                                  |

| Alternate Interrupt Vector Table (AIVT)               |

| Control and Status Registers                          |

| INTCON1                                               |

| INTCON2                                               |

| INTCON3                                               |

| INTCON494                                             |

| INTTREG94                                             |

| Interrupt Vector Details92                            |

| Interrupt Vector Table (IVT)                          |

| Reset Sequence                                        |

| Resources                                             |

| Interrupts Coincident with Power Save Instructions116 |

| J                                                     |

| JTAG Boundary Scan Interface                          |

| JTAG Interface                                        |

| L                                                     |

| Leading-Edge Blanking (LEB)181                        |

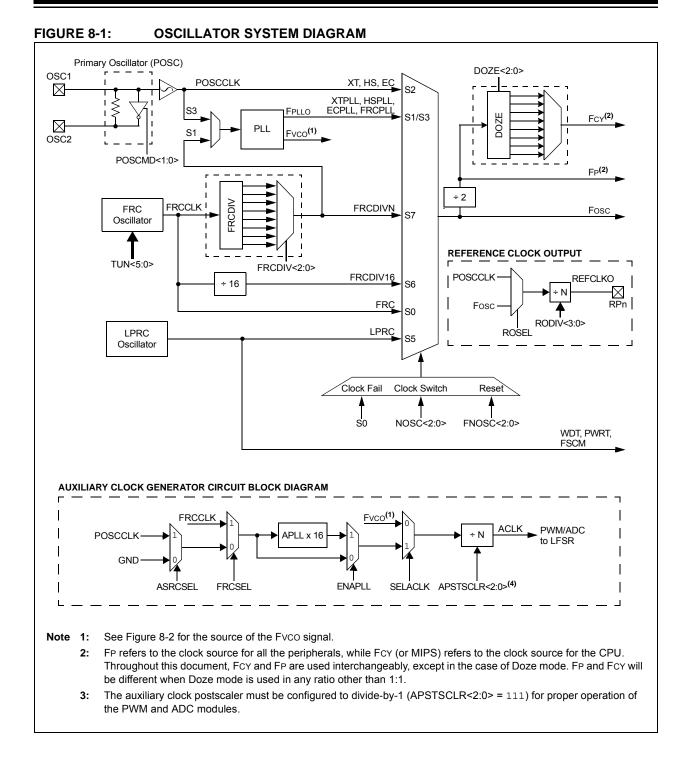

| LPRC Oscillator                                       |

| Use with WDT                                          |

| 200 With WD1                                          |

#### Μ

| Memory Organization                         | 31  |

|---------------------------------------------|-----|

| Resources                                   | 41  |

| Microchip Internet Web Site                 |     |

| Modulo Addressing                           | 72  |

| Applicability                               | 73  |

| Operation Example                           | 72  |

| Start and End Address                       | 72  |

| W Address Register Selection                | 72  |

| MPLAB REAL ICE In-Circuit Emulator System   |     |

| MPLAB X Integrated Development              |     |

| Environment Software                        |     |

| MPLINK Object Linker/MPLIB Object Librarian | 300 |

| 0                                           |     |

| Oppillator                                  |     |

| Oscillator        |     |

|-------------------|-----|

| Control Registers |     |

| Resources         | 106 |

| Output Compare    |     |

| Control Registers |     |

| Resources         | 175 |

#### Ρ

| 1                                     |

|---------------------------------------|

| Packaging                             |

| Details                               |

| Marking 353                           |

| Peripheral Module Disable (PMD) 117   |

| Peripheral Pin Select (PPS) 127       |

| Available Peripherals                 |

| Available Pins 127                    |

| Control 127                           |

| Control Registers 134                 |

| Input Mapping 128                     |

| Output Mapping 130                    |

| Output Selection for Remappable Pins  |

| Selectable Input Sources 129          |

| PGA                                   |

| Pinout I/O Descriptions (table)       |

| Power-Saving Features 115             |

| Clock Frequency and Switching 115     |

| Resources 117                         |

| Program Address Space                 |

| Construction75                        |

| Data Access from Program Memory Using |

| Table Instructions76                  |

| Memory Map (dsPIC33EP16GS50X Devices) |

| Memory Map (dsPIC33EP32GS50X Devices) |

| Memory Map (dsPIC33EP64GS50X Devices, |

| Dual Partition)35                     |

| Memory Map (dsPIC33EP64GS50X Devices) |

| Table Read High Instructions (TBLRDH) |

| Table Read Low Instructions (TBLRDL)  |

| Program Memory                        |

| Interfacing with Data Memory Spaces   |

| Organization 36                       |

| Reset Vector 36                       |

| Programmable Gain Amplifier (PGA) 271 |

| Description                           |

| Resources 273                         |

| Programmable Gain Amplifier. See PGA. |

| Programmer's Model                    |

| Register Descriptions23               |

| R                                     |

### к

| Register Maps                              |     |

|--------------------------------------------|-----|

| ADC                                        | 54  |

| Analog Comparator                          | 61  |

| Configuration Registers                    | 278 |

| Constant-Current Source                    | 60  |

| CPU Core                                   | 42  |

| I2C1 and I2C2                              | 52  |

| Input Capture 1 through Input Capture 4    | 47  |

| Interrupt Controller                       | 44  |

| JTAG Interface                             | 61  |

| NVM                                        | 59  |

| Output Compare 1 through Output Compare 4. | 48  |

| Peripheral Pin Select Input                | 58  |

| Peripheral Pin Select Output               |     |

| (dsPIC33EPXXGS502 Devices)                 | 56  |

| Peripheral Pin Select Output               |     |

| (dsPIC33EPXXGS504/505 Devices)             | 56  |

| Peripheral Pin Select Output               |     |

| (dsPIC33EPXXGS506 Devices)                 | 57  |

|                                            |     |

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELoq, KEELoq logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2013-2017, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-1714-9