Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                       |     |

|-------|-----------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers |     |

| 3.0   | CPU                                                                   |     |

| 4.0   | Memory Organization                                                   |     |

| 5.0   | Flash Program Memory                                                  | 77  |

| 6.0   | Resets                                                                |     |

| 7.0   | Interrupt Controller                                                  |     |

| 8.0   | Oscillator Configuration                                              | 103 |

| 9.0   | Power-Saving Features                                                 | 115 |

| 10.0  | I/O Ports                                                             | 125 |

| 11.0  | Timer1                                                                | 163 |

| 12.0  | Timer2/3 and Timer4/5                                                 |     |

| 13.0  | Input Capture                                                         | 171 |

| 14.0  | Output Compare                                                        | 175 |

| 15.0  | High-Speed PWM                                                        |     |

| 16.0  | Serial Peripheral Interface (SPI)                                     |     |

| 17.0  | Inter-Integrated Circuit (I <sup>2</sup> C)                           |     |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)                    |     |

| 19.0  | High-Speed, 12-Bit Analog-to-Digital Converter (ADC)                  |     |

| 20.0  | High-Speed Analog Comparator                                          |     |

| 21.0  | Programmable Gain Amplifier (PGA)                                     |     |

| 22.0  | Constant-Current Source                                               |     |

| 23.0  | Special Features                                                      |     |

| 24.0  | Instruction Set Summary                                               |     |

| 25.0  | Development Support                                                   |     |

| 26.0  | Electrical Characteristics                                            |     |

| 27.0  |                                                                       |     |

|       | Packaging Information                                                 |     |

| Appe  | endix A: Revision History                                             |     |

| Index | (                                                                     |     |

|       | Microchip Web Site                                                    |     |

| Custo | omer Change Notification Service                                      |     |

| Custo | omer Support                                                          |     |

| Prod  | uct Identification System                                             |     |

#### TABLE 4-20: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|--------------|--------|--------|--------|--------|--------|--------|--------|---------------|

| RPINR0      | 06A0  |          |          |          | INT1F    | <7:0>    |          |          |          | _            | _      | _      | _      | —      | _      |        |        | 0000          |

| RPINR1      | 06A2  | _        | _        | _        | _        | _        | _        | _        | _        |              |        |        | INT2   | R<7:0> |        |        |        | 0000          |

| RPINR2      | 06A4  |          |          |          | T1CKF    | R<7:0>   |          |          |          | _            | _      | —      | _      | _      | _      | —      | _      | 0000          |

| RPINR3      | 06A6  | T3CKR7   | T3CKR6   | T3CKR5   | T3CKR4   | T3CKR3   | T3CKR2   | T3CKR1   | T3CKR0   | T2CKR7       | T2CKR6 | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 | 0000          |

| RPINR7      | 06AE  | IC2R7    | IC2R6    | IC2R5    | IC2R4    | IC2R3    | IC2R2    | IC2R1    | IC2R0    | IC1R7        | IC1R6  | IC1R5  | IC1R4  | IC1R3  | IC1R2  | IC1R1  | IC1R0  | 0000          |

| RPINR8      | 06B0  | IC4R7    | IC4R6    | IC4R5    | IC4R4    | IC4R3    | IC4R2    | IC4R1    | IC4R0    | IC3R7        | IC3R6  | IC3R5  | IC3R4  | IC3R3  | IC3R2  | IC3R1  | IC3R0  | 0000          |

| RPINR11     | 06B6  | _        | _        | _        | _        | _        | _        | _        | _        |              |        |        | OCFA   | R<7:0> |        |        |        | 0000          |

| RPINR12     | 06B8  | FLT2R7   | FLT2R6   | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | FLT1R7       | FLT1R6 | FLT1R5 | FLT1R4 | FLT1R3 | FLT1R2 | FLT1R1 | FLT1R0 | 0000          |

| RPINR13     | 06BA  | FLT4R7   | FLT4R6   | FLT4R5   | FLT4R4   | FLT4R3   | FLT4R2   | FLT4R1   | FLT4R0   | FLT3R7       | FLT3R6 | FLT3R5 | FLT3R4 | FLT3R3 | FLT3R2 | FLT3R1 | FLT3R0 | 0000          |

| RPINR18     | 06C4  | U1CTSR7  | U1CTSR6  | U1CTSR5  | U1CTSR4  | U1CTSR3  | U1CTSR2  | U1CTSR1  | U1CTS0   | U1RXR7       | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 | 0000          |

| RPINR19     | 06C6  | U2CTSR7  | U2CTSR6  | U2CTSR5  | U2CTSR4  | U2CTSR3  | U2CTSR2  | U2CTSR1  | U2CTSR0  | U2RXR7       | U2RXR6 | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 | 0000          |

| RPINR20     | 06C8  | SCK1INR7 | SCK1INR6 | SCK1INR5 | SCK1INR4 | SCK1INR3 | SCK1INR2 | SCK1INR1 | SCK1INR0 | SDI1R7       | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 | 0000          |

| RPINR21     | 06CA  | _        | _        | _        | _        | _        | _        | _        | _        |              |        |        | SS1F   | R<7:0> |        |        |        | 0000          |

| RPINR22     | 06CC  | SCK2INR7 | SCK2INR6 | SCK2INR5 | SCK2INR4 | SCK2INR3 | SCK2INR2 | SCK2INR1 | SCK2INR0 | SDI2R7       | SDI2R6 | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 | 0000          |

| RPINR23     | 06CE  | _        | _        | _        | _        | _        | _        | _        | _        |              |        |        | SS2F   | R<7:0> |        |        |        | 0000          |

| RPINR37     | 06EA  |          |          |          | SYNCI    | R<7:0>   |          |          |          |              |        |        |        |        | 0000   |        |        |               |

| RPINR38     | 06EC  | _        | —        | —        | _        | —        | —        | _        | —        | SYNCI2R<7:0> |        |        |        |        | 0000   |        |        |               |

| RPINR42     | 06F4  | FLT6R7   | FLT6R6   | FLT6R5   | FLT6R4   | FLT6R3   | FLT6R2   | FLT6R1   | FLT6R0   | FLT5R7       | FLT5R6 | FLT5R5 | FLT5R4 | FLT5R3 | FLT5R2 | FLT5R1 | FLT5R0 | 0000          |

| RPINR43     | 06F6  | FLT8R7   | FLT8R6   | FLT8R5   | FLT8R4   | FLT8R3   | FLT8R2   | FLT8R1   | FLT8R0   | FLT7R7       | FLT7R6 | FLT7R5 | FLT7R4 | FLT7R3 | FLT7R2 | FLT7R1 | FLT7R0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-26: ANALOG COMPARATOR REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10      | Bit 9   | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3         | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |  |  |

|-------------|-------|--------|--------|---------|---------|---------|-------------|---------|-------|--------|--------|--------|--------|---------------|--------|--------|-------|---------------|--|--|

| CMP1CON     | 0540  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT       | ALTINP | CMPPOL | RANGE | 0000          |  |  |

| CMP1DAC     | 0542  | _      | —      | —       |         |         | CMREF<11:0> |         |       |        |        |        |        | 0000          |        |        |       |               |  |  |

| CMP2CON     | 0544  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT       | ALTINP | CMPPOL | RANGE | 0000          |  |  |

| CMP2DAC     | 0546  | -      | —      | _       | -       |         |             |         |       |        | CMREF  | <11:0> |        |               |        |        |       | 0000          |  |  |

| CMP3CON     | 0548  | CMPON  | _      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT       | ALTINP | CMPPOL | RANGE | 0000          |  |  |

| CMP3DAC     | 054A  | -      | _      | _       | _       |         |             |         |       |        | CMREF  | <11:0> |        |               |        |        |       | 0000          |  |  |

| CMP4CON     | 054C  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT       | ALTINP | CMPPOL | RANGE | 0000          |  |  |

| CMP4DAC     | 054E  | —      | —      | _       | _       |         |             |         |       |        | CMREF  | <11:0> |        | CMREF<11:0> 0 |        |        |       |               |  |  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-27: JTAG INTERFACE REGISTER MAP

| SFR<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|------|--------|--------|--------|--------|--------|--------|-------|-------|---------|-------|---------|-------|-------|-------|-------|-------|---------------|

| JDATAH      | 0FF0 | _      | _      | _      | —      |        |        |       |       |         | JDATA | H<11:0> |       |       |       |       |       | xxxx          |

| JDATAL      | 0FF2 |        |        |        |        |        |        |       | JDATA | L<15:0> |       |         |       |       |       |       |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.7.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

#### 4.8 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

### 4.8.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these situations are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume<br>word-sized data (LSb of every EA is<br>always clear). The XB value is scaled<br>accordingly to generate compatible (byte) |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | addresses.                                                                                                                                                           |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed        |

|-------|-------------------------------------------|

|       | Addressing can be enabled simultaneously  |

|       | using the same W register, but Bit-       |

|       | Reversed Addressing operation will always |

|       | take precedence for data writes when      |

|       | enabled.                                  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### **REGISTER 6-1:** RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ul><li>1 = Device has been in Idle mode</li><li>0 = Device has not been in Idle mode</li></ul>                         |

| bit 1 | BOR: Brown-out Reset Flag bit                                                                                           |

|       | <ul><li>1 = A Brown-out Reset has occurred</li><li>0 = A Brown-out Reset has not occurred</li></ul>                     |

| bit 0 | POR: Power-on Reset Flag bit                                                                                            |

|       | <ul><li>1 = A Power-on Reset has occurred</li><li>0 = A Power-on Reset has not occurred</li></ul>                       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70000600) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXGS50X family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior, contains the Global Interrupt Enable bit (GIE) and the Alternate Interrupt Vector Table Enable bit (AIVTEN).

INTCON3 contains the status flags for the Auxiliary PLL and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap Status bit (SGHT).

#### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt sources can be assigned to one of seven priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<7:0>) and Interrupt Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP<2:0> bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

#### **REGISTER 7-1:** SR: CPU STATUS REGISTER<sup>(1)</sup>

| R/W-0                | R/W-0                | R/W-0                | R/W-0   | R/C-0 | R/C-0 | R-0   | R/W-0   |

|----------------------|----------------------|----------------------|---------|-------|-------|-------|---------|

| 10.00-0              | 10.00-0              | 10.00-0              | 10.00-0 | 100-0 | 100-0 | 11-0  | 10.00-0 |

| OA                   | OB                   | SA                   | SB      | OAB   | SAB   | DA    | DC      |

| bit 15               |                      |                      |         |       |       |       | bit 8   |

| (3)                  | (2)                  | (2)                  |         |       |       |       |         |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0   |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA      | N     | OV    | Z     | С       |

| bit 7                |                      |                      |         |       |       |       | bit 0   |

|                      |                      |                      |         |       |       |       |         |

| Logond:              |                      | C = Clearable        | hit     |       |       |       |         |

| Legend:           | C = Clearable bit |                        |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

| R/W-1         | R/W-0       | R/W-0                                     | U-0            | U-0              | U-0              | U-0             | R/W-0  |

|---------------|-------------|-------------------------------------------|----------------|------------------|------------------|-----------------|--------|

| GIE           | DISI        | SWTRAP                                    | _              | _                | _                |                 | AIVTEN |

| bit 15        |             |                                           |                |                  |                  |                 | bit    |

|               |             |                                           |                |                  |                  |                 |        |

| U-0           | U-0         | U-0                                       | R/W-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |

|               |             | —                                         | INT4EP         |                  | INT2EP           | INT1EP          | INT0EP |

| bit 7         |             |                                           |                |                  |                  |                 | bit    |

| Legend:       |             |                                           |                |                  |                  |                 |        |

| R = Readable  | e bit       | W = Writable                              | bit            | U = Unimple      | mented bit, read | l as '0'        |        |

| -n = Value at | POR         | '1' = Bit is set                          |                | '0' = Bit is cle | eared            | x = Bit is unki | nown   |

|               |             |                                           |                |                  |                  |                 |        |

| bit 15        | GIE: Global | Interrupt Enable                          | e bit          |                  |                  |                 |        |

|               |             | ts and associate                          |                |                  |                  |                 |        |

|               |             | ts are disabled, I                        | •              | till enabled     |                  |                 |        |

| bit 14        |             | Instruction Statu                         |                |                  |                  |                 |        |

|               |             | struction is active<br>struction is not a |                |                  |                  |                 |        |

| bit 13        |             | Software Trap St                          |                |                  |                  |                 |        |

| DIL 15        |             | e trap is enabled                         |                |                  |                  |                 |        |

|               |             | e trap is disabled                        |                |                  |                  |                 |        |

| bit 12-9      | Unimpleme   | ented: Read as '                          | 0'             |                  |                  |                 |        |

| bit 8         | AIVTEN: Al  | ternate Interrupt                         | Vector Table E | Enable           |                  |                 |        |

|               |             | ternate Interrupt                         |                |                  |                  |                 |        |

|               |             | andard Interrupt                          |                |                  |                  |                 |        |

| bit 7-5       | -           | ented: Read as '                          |                |                  |                  |                 |        |

| bit 4         |             | ternal Interrupt 4                        | -              | Polarity Selec   | ct bit           |                 |        |

|               | •           | t on negative ed<br>t on positive edg     | •              |                  |                  |                 |        |

| bit 3         | -           | ented: Read as '                          |                |                  |                  |                 |        |

| bit 2         | -           | ternal Interrupt 2                        |                | Polarity Selec   | rt hit           |                 |        |

| SIL 2         |             | t on negative ed                          | 0              |                  |                  |                 |        |

|               |             | t on positive edg                         |                |                  |                  |                 |        |

| bit 1         | INT1EP: Ex  | ternal Interrupt 1                        | Edge Detect    | Polarity Selec   | ct bit           |                 |        |

|               |             | t on negative ed                          |                |                  |                  |                 |        |

|               | •           | t on positive edg                         |                |                  |                  |                 |        |

| bit 0         |             | ternal Interrupt (                        | -              | Polarity Selec   | ct bit           |                 |        |

|               |             | t on negative edg                         |                |                  |                  |                 |        |

|               | 0 = memup   | t on positive edg                         | e              |                  |                  |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

#### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0   |

|--------|-----|-----|-----|------|------|------|-------|

| —      | —   | —   | —   | ILR3 | ILR2 | ILR1 | ILR0  |

| bit 15 |     |     |     |      |      |      | bit 8 |

| R-0     |

|---------|---------|---------|---------|---------|---------|---------|---------|

| VECNUM7 | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7   | •       |         |         |         |         | ·       | bit 0   |

| Legend:                    |                                                                             |                                           |                       |                    |  |  |  |  |

|----------------------------|-----------------------------------------------------------------------------|-------------------------------------------|-----------------------|--------------------|--|--|--|--|

| R = Readabl                | e bit                                                                       | W = Writable bit                          | U = Unimplemented bit | read as '0'        |  |  |  |  |

| -n = Value at              | POR                                                                         | '1' = Bit is set                          | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |

| bit 15-12                  | Unimple                                                                     | mented: Read as '0'                       |                       |                    |  |  |  |  |

| bit 11-8                   | ILR<3:0>                                                                    | New CPU Interrupt Priority                | Level bits            |                    |  |  |  |  |

|                            |                                                                             | 1111 = CPU Interrupt Priority Level is 15 |                       |                    |  |  |  |  |

|                            | •                                                                           |                                           |                       |                    |  |  |  |  |

|                            | •                                                                           |                                           |                       |                    |  |  |  |  |

|                            | •                                                                           |                                           |                       |                    |  |  |  |  |

|                            | 0001 = CPU Interrupt Priority Level is 1                                    |                                           |                       |                    |  |  |  |  |

| 0000 = CPU Interrupt Prior |                                                                             | PU Interrupt Priority Level is            | 0                     |                    |  |  |  |  |

| bit 7-0                    | VECNUM<7:0>: Vector Number of Pending Interrupt bits                        |                                           |                       |                    |  |  |  |  |

|                            | 11111111 = 255, Reserved; do not use                                        |                                           |                       |                    |  |  |  |  |

|                            | •                                                                           |                                           |                       |                    |  |  |  |  |

|                            | •                                                                           |                                           |                       |                    |  |  |  |  |

|                            | •                                                                           |                                           |                       |                    |  |  |  |  |

|                            |                                                                             | 00001001 = 9, IC1 – Input Capture 1       |                       |                    |  |  |  |  |

|                            | 00001000 = 8, INTO – External Interrupt 0                                   |                                           |                       |                    |  |  |  |  |

|                            | 00000111 = 7, Reserved; do not use<br>00000110 = 6, Generic soft error trap |                                           |                       |                    |  |  |  |  |

|                            | 00000101 = 5, Reserved; do not use                                          |                                           |                       |                    |  |  |  |  |

|                            | 00000101 = 3, Nescrived, do not use $00000100 = 4$ , Math error trap        |                                           |                       |                    |  |  |  |  |

|                            | 00000011 = 3, Stack error trap                                              |                                           |                       |                    |  |  |  |  |

|                            | 0000010 = 2, Generic hard trap                                              |                                           |                       |                    |  |  |  |  |

|                            |                                                                             | 1 = 1, Address error trap                 |                       |                    |  |  |  |  |

|                            | 0000000                                                                     | 0 = 0, Oscillator fail trap               |                       |                    |  |  |  |  |

#### REGISTER 10-13: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

|         | U-0   |

|---------|-------|

| L 1 A F | —     |

| bit 15  | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SS1R7 | SS1R6 | SS1R5 | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 SS1R<7:0>: Assign SPI1 Slave Select (SS1) to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180 •

00000001 = Input tied to RP1 00000000 = Input tied to Vss

| U-0        | U-0                                                                                                                                                       | U-0                                                     | U-0                           | U-0                          | U-0              | U-0               | U-0             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------|------------------------------|------------------|-------------------|-----------------|

| _          | —                                                                                                                                                         | —                                                       | —                             | —                            | —                | —                 | —               |

| bit 15     |                                                                                                                                                           |                                                         |                               |                              |                  |                   | bit 8           |

| U-0        | R/W-0                                                                                                                                                     | R/W-0                                                   | R/W-0                         | R/W-0                        | R/W-0            | R/W-0             | R/W-0           |

| _          | PCIE                                                                                                                                                      | SCIE                                                    | BOEN                          | SDAHT                        | SBCDE            | AHEN              | DHEN            |

| bit 7      |                                                                                                                                                           |                                                         |                               |                              |                  |                   | bit             |

| Legend:    |                                                                                                                                                           |                                                         |                               |                              |                  |                   |                 |

| R = Reada  | ble bit                                                                                                                                                   | W = Writable                                            | bit                           | U = Unimplem                 | nented bit, read | as '0'            |                 |

| -n = Value | at POR                                                                                                                                                    | '1' = Bit is set                                        | t                             | '0' = Bit is clea            | ared             | x = Bit is unkr   | nown            |

| bit 15-7   | Unimpleme                                                                                                                                                 | nted: Read as '                                         | ·0'                           |                              |                  |                   |                 |

| bit 6      | -                                                                                                                                                         |                                                         |                               | I <sup>2</sup> C Slave mode  | only)            |                   |                 |

|            | •                                                                                                                                                         | interrupt on det                                        | •                             |                              | ony)             |                   |                 |

|            |                                                                                                                                                           | ection interrupts                                       |                               | condition                    |                  |                   |                 |

| bit 5      | •                                                                                                                                                         | •                                                       |                               | <sup>12</sup> C Slave mode   | only)            |                   |                 |

|            | <b>SCIE:</b> Start Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)<br>1 = Enables interrupt on detection of Start or Restart conditions |                                                         |                               |                              |                  |                   |                 |

|            |                                                                                                                                                           | ection interrupts                                       |                               |                              |                  |                   |                 |

| bit 4      | BOEN: Buffe                                                                                                                                               | er Overwrite En                                         | able bit (I <sup>2</sup> C SI | ave mode only)               |                  |                   |                 |

|            | 1 = I2CxRC                                                                                                                                                | V is updated an                                         | d ACK is gene                 | rated for a recei            | ved address/da   | ata byte, ignorir | ng the state of |

|            |                                                                                                                                                           | OV only if the R                                        |                               |                              |                  | <i>y v c</i>      | •               |

|            | 0 = I2CxRC                                                                                                                                                | V is only update                                        | ed when I2CO                  | / is clear                   |                  |                   |                 |

| bit 3      | SDAHT: SD                                                                                                                                                 | Ax Hold Time S                                          | election bit                  |                              |                  |                   |                 |

|            |                                                                                                                                                           |                                                         |                               | after the falling            |                  |                   |                 |

|            |                                                                                                                                                           |                                                         |                               | after the falling            | -                |                   |                 |

| bit 2      |                                                                                                                                                           |                                                         |                               | Enable bit (I <sup>2</sup> C | Slave mode on    | ly)               |                 |

|            |                                                                                                                                                           | slave bus collis                                        |                               |                              |                  |                   |                 |

|            |                                                                                                                                                           | is collision inter                                      |                               | npled low when               | the module is i  | n a high state    | the BCL bit i   |

|            |                                                                                                                                                           |                                                         |                               | node is only vali            |                  |                   |                 |

| bit 1      |                                                                                                                                                           | ress Hold Enabl                                         |                               | -                            | a aannig aata a  |                   |                 |

|            |                                                                                                                                                           |                                                         | •                             | CLx for a match              | ning received    | address byte.     | the SCI RF      |

|            |                                                                                                                                                           |                                                         |                               | and SCLx will be             |                  |                   |                 |

|            |                                                                                                                                                           | s holding is disa                                       |                               |                              |                  |                   |                 |

| bit 0      | DHEN: Data                                                                                                                                                | Hold Enable bi                                          | t (I <sup>2</sup> C Slave me  | ode only)                    |                  |                   |                 |

|            |                                                                                                                                                           |                                                         |                               |                              | بطغم أستعمله أ   | a alawa harduu    |                 |

| DILU       | 1 = Followir                                                                                                                                              | ng the 8th falling                                      | g edge of SCL                 | x for a received             | u data byte, the | e slave narowa    | are clears th   |

| bit U      | SCLRE                                                                                                                                                     | ng the 8th falling<br>L (I2CxCONL<<br>Iding is disabled | 12>) bit and S                |                              | u dala dyle, ine | e slave narowa    | are clears th   |

REGISTER 17-2: I2CxCONH: I2Cx CONTROL REGISTER HIGH

#### 18.3 UART Control Registers

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                          | R/W-0                                                    | R/W-0                          | R/W-0                               | U-0                     | R/W-0                                                  | R/W-0         |

|-----------------------|------------------------------|----------------------------------------------------------|--------------------------------|-------------------------------------|-------------------------|--------------------------------------------------------|---------------|

| UARTEN <sup>(1)</sup> |                              | USIDL                                                    | IREN <sup>(2)</sup>            | RTSMD                               |                         | UEN1                                                   | UEN0          |

| bit 15                |                              |                                                          |                                | 1                                   |                         |                                                        | bit           |

|                       |                              |                                                          |                                |                                     |                         |                                                        |               |

| R/W-0, HC             | R/W-0                        | R/W-0, HC                                                | R/W-0                          | R/W-0                               | R/W-0                   | R/W-0                                                  | R/W-0         |

| WAKE                  | LPBACK                       | ABAUD                                                    | URXINV                         | BRGH                                | PDSEL1                  | PDSEL0                                                 | STSEL         |

| bit 7                 |                              |                                                          |                                |                                     |                         |                                                        | bit           |

| Legend:               |                              | HC = Hardwar                                             | e Clearable b                  | it                                  |                         |                                                        |               |

| R = Readabl           | e bit                        | W = Writable b                                           |                                | U = Unimplem                        | ented bit, read         | l as '0'                                               |               |

| -n = Value at         |                              | '1' = Bit is set                                         |                                | '0' = Bit is clea                   |                         | x = Bit is unkn                                        | own           |

| bit 15                | 1 = UARTx is                 |                                                          | ARTx pins are                  |                                     |                         | ed by UEN<1:0><br>UARTx power co                       |               |

| oit 14                |                              | ted: Read as '0                                          | ,                              |                                     |                         |                                                        |               |

| bit 13                | •                            | Tx Stop in Idle N                                        |                                |                                     |                         |                                                        |               |

|                       | 1 = Discontin                | •                                                        | eration when o                 | device enters Id                    | le mode                 |                                                        |               |

| pit 12                |                              | Encoder and De                                           |                                |                                     |                         |                                                        |               |

|                       |                              | oder and decod<br>oder and decod                         |                                |                                     |                         |                                                        |               |

| pit 11                | RTSMD: Mod                   | le Selection for                                         | UxRTS Pin bi                   | t                                   |                         |                                                        |               |

|                       |                              | in is in Simplex<br>in is in Flow Co                     |                                |                                     |                         |                                                        |               |

| oit 10                | Unimplemen                   | ted: Read as '0                                          | ,                              |                                     |                         |                                                        |               |

| oit 9-8               | UEN<1:0>: U                  | ARTx Pin Enab                                            | le bits                        |                                     |                         |                                                        |               |

|                       | 10 = UxTX, U<br>01 = UxTX, U | JxRX, <u>UxCTS</u> ai<br>JxRX and UxRT<br>nd UxRX pins a | nd UxRTS pin<br>S pins are ena | s are enabled a abled and used;     | nd used<br>UxCTS pin is | controlled by PC<br>controlled by PC<br>BCLKx pins are | ORT latches   |

| bit 7                 | WAKE: Wake                   | -up on Start Bit                                         | Detect During                  | g Sleep Mode E                      | nable bit               |                                                        |               |

|                       | in hardwa                    | ontinues to sam<br>are on the follow<br>-up is enabled   |                                |                                     | generated on            | the falling edge;                                      | bit is cleare |

| oit 6                 |                              | RTx Loopback                                             | Mode Select I                  | bit                                 |                         |                                                        |               |

|                       | 1 = Enables                  | Loopback mode<br>k mode is disab                         | :                              |                                     |                         |                                                        |               |

| "0                    |                              | Family Referen                                           |                                | r Transmitter (<br>r information on |                         | 0000582) in the<br>JARTx module fo                     | or receive or |

|                       |                              |                                                          | the 16y BPC                    | modo (BBCH -                        | 0)                      |                                                        |               |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 19-29: ADCAL0H: ADC CALIBRATION REGISTER 0 HIGH

| R-0, HSC            | U-0                                                                                                                                               | U-0                                    | U-0              | r-0              | R/W-0            | R/W-0            | R/W-0            |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|------------------|------------------|------------------|------------------|

| CAL3RDY             | —                                                                                                                                                 | —                                      | —                | _                | CAL3DIFF         | CAL3EN           | CAL3RUN          |

| bit 15              |                                                                                                                                                   |                                        |                  |                  |                  |                  | bit 8            |

|                     |                                                                                                                                                   |                                        |                  |                  |                  |                  |                  |

| R-0, HSC            | U-0                                                                                                                                               | U-0                                    | U-0              | r-0              | R/W-0            | R/W-0            | R/W-0            |

| CAL2RDY             |                                                                                                                                                   | —                                      |                  | _                | CAL2DIFF         | CAL2EN           | CAL2RUN          |

| bit 7               | ·                                                                                                                                                 | ·                                      | •                |                  |                  |                  | bit 0            |

|                     |                                                                                                                                                   |                                        |                  |                  |                  |                  |                  |

| Legend:             |                                                                                                                                                   | r = Reserved                           | bit              | U = Unimpler     | nented bit, read | as '0'           |                  |

| R = Readabl         | e bit                                                                                                                                             | W = Writable                           | bit              | HSC = Hardw      | vare Settable/C  | earable bit      |                  |

| -n = Value at       | POR                                                                                                                                               | '1' = Bit is set                       |                  | '0' = Bit is cle | ared             | x = Bit is unkr  | nown             |

|                     |                                                                                                                                                   |                                        |                  |                  |                  |                  |                  |

| bit 15              |                                                                                                                                                   | Dedicated ADC                          |                  |                  | g bit            |                  |                  |

|                     |                                                                                                                                                   | ed ADC Core 3 c                        |                  |                  |                  |                  |                  |

| hit 11 10           |                                                                                                                                                   | ed ADC Core 3 c                        |                  | progress         |                  |                  |                  |

| bit 14-12<br>bit 11 | -                                                                                                                                                 | nted: Read as '<br>/lust be written a  |                  |                  |                  |                  |                  |

| bit 10              |                                                                                                                                                   |                                        |                  | ntial Mada Cali  | ibration bit     |                  |                  |

|                     | <b>CAL3DIFF:</b> Dedicated ADC Core 3 Differential-Mode Calibration bit<br>1 = Dedicated ADC Core 3 will be calibrated in Differential Input mode |                                        |                  |                  |                  |                  |                  |

|                     | 0 = Dedicated ADC Core 3 will be calibrated in Single-Ended Input mode                                                                            |                                        |                  |                  |                  |                  |                  |

| bit 9               | CAL3EN: De                                                                                                                                        | edicated ADC C                         | ore 3 Calibratio | on Enable bit    | ·                |                  |                  |

|                     | 1 = Dedicate                                                                                                                                      | ed ADC Core 3 o                        | calibration bits | (CALxRDY, CA     | LxDIFF and CA    | LxRUN) can b     | e accessed by    |

|                     | software                                                                                                                                          | e                                      |                  |                  |                  |                  |                  |

| 1.1.0               |                                                                                                                                                   | ed ADC Core 3                          |                  |                  |                  |                  |                  |

| bit 8               |                                                                                                                                                   | Dedicated ADC<br>it is set by soft     |                  |                  | ara 2 adibratia  | n avala ia atar  | tad: this hit is |

|                     |                                                                                                                                                   | ically cleared by                      |                  |                  |                  | IT CYCLE IS SLAI | teu, this bit is |

|                     |                                                                                                                                                   | e can start the n                      |                  | cycle            |                  |                  |                  |

| bit 7               | CAL2RDY:                                                                                                                                          | Dedicated ADC                          | Core 2 Calibra   | tion Status Flag | g bit            |                  |                  |

|                     |                                                                                                                                                   | ed ADC Core 2 c                        |                  |                  |                  |                  |                  |

|                     |                                                                                                                                                   | ed ADC Core 2 c                        |                  | progress         |                  |                  |                  |

| bit 6-4             | -                                                                                                                                                 | nted: Read as '                        |                  |                  |                  |                  |                  |

| bit 3               |                                                                                                                                                   | /lust be written a                     |                  |                  |                  |                  |                  |

| bit 2               |                                                                                                                                                   | Dedicated ADC                          |                  |                  |                  |                  |                  |

|                     |                                                                                                                                                   | ed ADC Core 2 v<br>ed ADC Core 2 v     |                  |                  |                  |                  |                  |

| bit 1               |                                                                                                                                                   | edicated ADC C                         |                  | -                |                  |                  |                  |

| bit i               |                                                                                                                                                   | ed ADC Core 2 (                        |                  |                  | LxDIFF and CA    | LxRUN) can b     | e accessed by    |

|                     | software                                                                                                                                          |                                        |                  | (,,              |                  | ,,               |                  |

|                     | 0 = Dedicate                                                                                                                                      | ed ADC Core 2                          | calibration bits | are disabled     |                  |                  |                  |

| bit 0               |                                                                                                                                                   | Dedicated ADC                          |                  |                  |                  |                  |                  |

|                     |                                                                                                                                                   | it is set by soft                      |                  | icated ADC Co    | ore 2 calibratio | n cycle is star  | ted; this bit is |

|                     |                                                                                                                                                   | ically cleared by<br>e can start the n |                  | cycle            |                  |                  |                  |

|                     |                                                                                                                                                   |                                        |                  | 0,000            |                  |                  |                  |

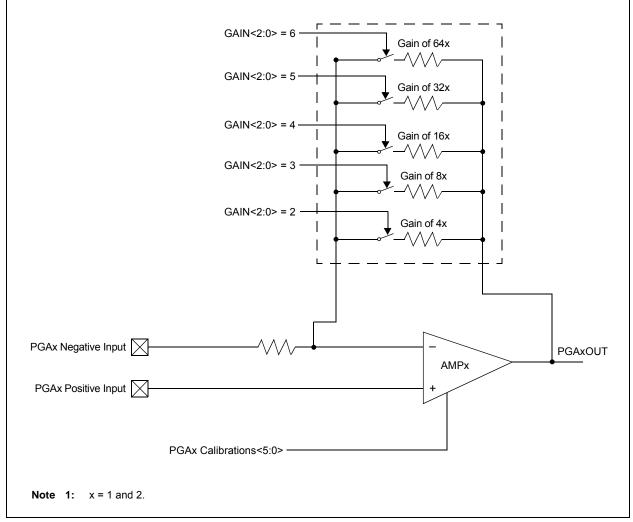

#### 21.0 PROGRAMMABLE GAIN AMPLIFIER (PGA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Gain Amplifier (PGA)" (DS70005146) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family devices have two Programmable Gain Amplifiers (PGA1, PGA2). The PGA is an op amp-based, non-inverting amplifier with user-programmable gains. The output of the PGA can be connected to a number of dedicated Sample-and-Hold inputs of the Analog-to-Digital Converter and/or to the high-speed analog comparator module. The PGA has five selectable gains and may be used as a ground referenced amplifier (single-ended) or used with an independent ground reference point.

Key features of the PGA module include:

- Single-Ended or Independent Ground Reference

- Selectable Gains: 4x, 8x, 16x, 32x and 64x

- High Gain Bandwidth

- Rail-to-Rail Output Voltage

- Wide Input Voltage Range

| DC CH        | ARACTE | RISTICS                                 | (unless | otherwise           | <b>stated)</b><br>ture -40 | °C ≤ Ta s | <b>0V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +125°C for Extended                                                                          |

|--------------|--------|-----------------------------------------|---------|---------------------|----------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                          | Min.    | Тур. <sup>(1)</sup> | Max.                       | Units     | Conditions                                                                                                                                    |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>  |         |                     |                            |           |                                                                                                                                               |

| DI50         |        | I/O Pins 5V Tolerant <sup>(4)</sup>     | -1      | —                   | +1                         | μA        | $Vss \le VPIN \le VDD,$ pin at high-impedance                                                                                                 |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1      | —                   | +1                         | μA        | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1      | —                   | +1                         | μA        | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1      | —                   | +1                         | μA        | $Vss \le VPIN \le VDD,$<br>pin at high-impedance,<br>-40°C \le TA ≤ +125°C                                                                    |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1      | —                   | +1                         | μA        | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |

| DI55         |        | MCLR                                    | -5      | —                   | +5                         | μA        | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |

| DI56         |        | OSC1                                    | -5      | —                   | +5                         | μA        | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                     |

#### TABLE 26-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

5: VIL Source < (Vss – 0.3). Characterized but not tested.

6: VIH Source > (VDD + 0.3) for pins that are not 5V tolerant only.

7: Digital 5V tolerant pins do not have internal high-side diodes to VDD and cannot tolerate any "positive" input injection current.

8: Injection Currents > | 0 | can affect the ADC results by approximately 4-6 counts.

**9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

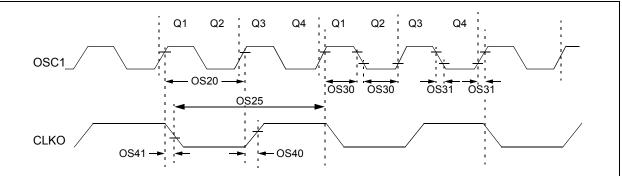

#### FIGURE 26-2: EXTERNAL CLOCK TIMING