Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

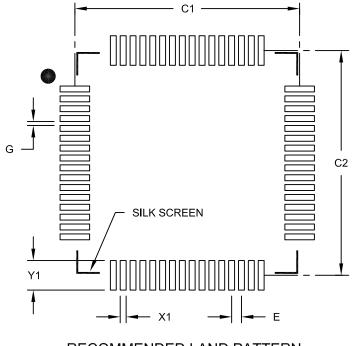

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

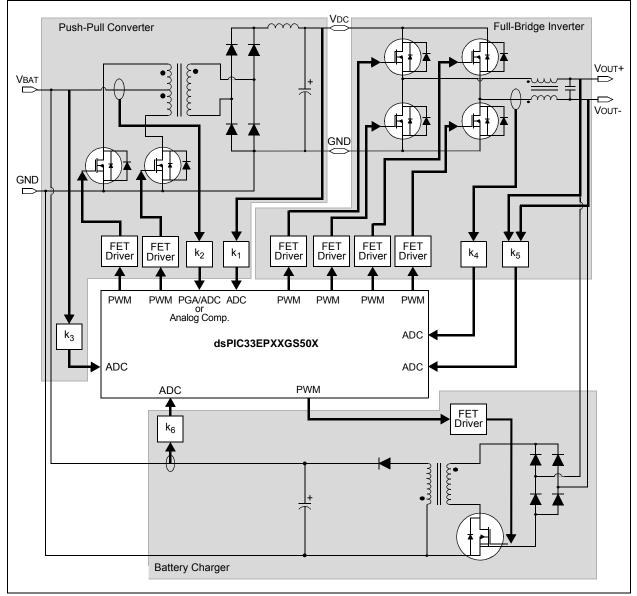

## FIGURE 2-6: OFF-LINE UPS

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for Digital Signal Processing (DSP). The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1 Registers

The dsPIC33EPXXGS50X devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EPXXGS50X devices include two Alternate Working register sets which consist of W0 through W14. The Alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The Alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register. The Alternate Working registers can also be accessed manually by using the CTXTSWP instruction. The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current and most recent, manually selected Working register sets.

## 3.2 Instruction Set

The instruction set for dsPIC33EPXXGS50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The base Data Space can be addressed as up to 4K words or 8 Kbytes, and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Refer to "**Data Memory**" (DS70595) in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on PSV and table accesses.

On dsPIC33EPXXGS50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- · Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction. **CORCON: CORE CONTROL REGISTER**

REGISTER 3-2:

| R/W-0           | U-0                                                                                                                                       | R/W-0                             | R/W-0           | R/W-0                | R-0             | R-0             | R-0   |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|----------------------|-----------------|-----------------|-------|--|--|--|--|--|

| VAR             |                                                                                                                                           | US1                               | US0             | EDT <sup>(1)</sup>   | DL2             | DL1             | DL0   |  |  |  |  |  |

| bit 15          |                                                                                                                                           |                                   |                 |                      |                 |                 | bit   |  |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                     | R/W-1                             | R/W-0           | R/C-0                | R-0             | R/W-0           | R/W-0 |  |  |  |  |  |

| SATA            | SATB                                                                                                                                      | SATDW                             | ACCSAT          | IPL3 <sup>(2)</sup>  | SFA             | RND             | IF    |  |  |  |  |  |

| bit 7           | OAID                                                                                                                                      | OAIDW                             | ACCOAL          | 11 2011              | UIA             | THE             | bit   |  |  |  |  |  |

| Legend:         |                                                                                                                                           | C = Clearable                     | - hit           |                      |                 |                 |       |  |  |  |  |  |

| R = Readable    | bit                                                                                                                                       | W = Writable                      |                 | U = Unimpler         | mented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value at F |                                                                                                                                           | '1' = Bit is set                  |                 | '0' = Bit is cle     |                 | x = Bit is unkn | iown  |  |  |  |  |  |

|                 |                                                                                                                                           | 1 - Dit 13 301                    | •               |                      | arcu            |                 | lowin |  |  |  |  |  |

| bit 15          |                                                                                                                                           | •                                 | ocessing Later  |                      |                 |                 |       |  |  |  |  |  |

|                 | <ul> <li>1 = Variable exception processing is enabled</li> <li>0 = Fixed exception processing is enabled</li> </ul>                       |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

| bit 14          | Unimplemen                                                                                                                                | ted: Read as '                    | 0'              |                      |                 |                 |       |  |  |  |  |  |

| bit 13-12       | Unimplemented: Read as '0'<br>US<1:0>: DSP Multiply Unsigned/Signed Control bits                                                          |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | 11 = Reserved                                                                                                                             |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | 10 = DSP engine multiplies are mixed-sign                                                                                                 |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | 01 = DSP engine multiplies are unsigned<br>00 = DSP engine multiplies are signed                                                          |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

| bit 11          | <b>EDT:</b> Early DO Loop Termination Control bit <sup>(1)</sup><br>1 = Terminates executing DO loop at the end of current loop iteration |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | 1 = Terminate<br>0 = No effect                                                                                                            | es executing Do                   | o loop at the e | nd of current lo     | oop iteration   |                 |       |  |  |  |  |  |

| bit 10-8        | DL<2:0>: DO Loop Nesting Level Status bits                                                                                                |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | 111 = 7 DO loops are active                                                                                                               |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | •                                                                                                                                         |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | •                                                                                                                                         |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | 001 = 1 DO loop is active<br>000 = 0 DO loops are active                                                                                  |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

| bit 7           |                                                                                                                                           | •                                 |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | SATA: ACCA Saturation Enable bit<br>1 = Accumulator A saturation is enabled                                                               |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 |                                                                                                                                           | itor A saturatio                  |                 |                      |                 |                 |       |  |  |  |  |  |

| bit 6           | SATB: ACCB                                                                                                                                | Saturation En                     | able bit        |                      |                 |                 |       |  |  |  |  |  |

|                 |                                                                                                                                           | itor B saturatio                  |                 |                      |                 |                 |       |  |  |  |  |  |

| bit 5           | SATDW: Data Space Write from DSP Engine Saturation Enable bit                                                                             |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 | 1 = Data Space write saturation is enabled<br>0 = Data Space write saturation is disabled                                                 |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

| bit 4           | ACCSAT: Accumulator Saturation Mode Select bit                                                                                            |                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|                 |                                                                                                                                           | ration (super s<br>ration (normal |                 |                      |                 |                 |       |  |  |  |  |  |

| L:1 0           |                                                                                                                                           | •                                 | Level Status b  | <sub>oit 3</sub> (2) |                 |                 |       |  |  |  |  |  |

| bit 3           |                                                                                                                                           | contraped monity                  |                 |                      |                 |                 |       |  |  |  |  |  |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2   | SFA: Stack Frame Active Status bit                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG</li> <li>0 = Stack frame is not active; W14 and W15 address the base Data Space</li> </ul> |

| bit 1   | RND: Rounding Mode Select bit                                                                                                                                                             |

|         | <ul><li>1 = Biased (conventional) rounding is enabled</li><li>0 = Unbiased (convergent) rounding is enabled</li></ul>                                                                     |

| bit 0   | IF: Integer or Fractional Multiplier Mode Select bit                                                                                                                                      |

|         | <ul> <li>1 = Integer mode is enabled for DSP multiply</li> <li>0 = Fractional mode is enabled for DSP multiply</li> </ul>                                                                 |

| Note 1: | This bit is always read as '0'.                                                                                                                                                           |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## REGISTER 3-3: CTXTSTAT: CPU W REGISTER CONTEXT STATUS REGISTER

| U-0                                                                      | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    | R-0    |  |  |

|--------------------------------------------------------------------------|-----|-----|-----|-----|--------|--------|--------|--|--|

| —                                                                        | —   | —   | —   | —   | CCTXI2 | CCTXI1 | CCTXI0 |  |  |

| bit 15 bit 8                                                             |     |     |     |     |        |        |        |  |  |

|                                                                          |     |     |     |     |        |        |        |  |  |

| U-0                                                                      | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    | R-0    |  |  |

|                                                                          | —   | —   | _   | —   | MCTXI2 | MCTXI1 | MCTXI0 |  |  |

| bit 7                                                                    |     |     |     |     |        |        | bit 0  |  |  |

|                                                                          |     |     |     |     |        |        |        |  |  |

| Legend:                                                                  |     |     |     |     |        |        |        |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'     |     |     |     |     |        | as '0' |        |  |  |

| -n = Value at POR (1' = Bit is set 0' = Bit is cleared x = Bit is unknow |     |     |     |     |        | nown   |        |  |  |

| bit 15-11 | Unimplemented: Read as '0'                                                 |  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 10-8  | CCTXI<2:0>: Current (W Register) Context Identifier bits                   |  |  |  |  |  |  |

|           | 111 = Reserved                                                             |  |  |  |  |  |  |

|           | •                                                                          |  |  |  |  |  |  |

|           | •                                                                          |  |  |  |  |  |  |

|           | •                                                                          |  |  |  |  |  |  |

|           | 011 = Reserved                                                             |  |  |  |  |  |  |

|           | 010 = Alternate Working Register Set 2 is currently in use                 |  |  |  |  |  |  |

|           | 001 = Alternate Working Register Set 1 is currently in use                 |  |  |  |  |  |  |

|           | 000 = Default register set is currently in use                             |  |  |  |  |  |  |

| bit 7-3   | Unimplemented: Read as '0'                                                 |  |  |  |  |  |  |

| bit 2-0   | MCTXI<2:0>: Manual (W Register) Context Identifier bits                    |  |  |  |  |  |  |

|           | 111 = Reserved                                                             |  |  |  |  |  |  |

|           | •                                                                          |  |  |  |  |  |  |

|           | •                                                                          |  |  |  |  |  |  |

|           | •                                                                          |  |  |  |  |  |  |

|           | 011 = Reserved                                                             |  |  |  |  |  |  |

|           | 010 = Alternate Working Register Set 2 was most recently manually selected |  |  |  |  |  |  |

|           | 001 = Alternate Working Register Set 1 was most recently manually selected |  |  |  |  |  |  |

|           | 000 = Default register set was most recently manually selected             |  |  |  |  |  |  |

## TABLE 4-2: CPU CORE REGISTER MAP (CONTINUED)

|             |       |                                                    |        |        |        |        | ,           |             |              |          |       |       |            |             |              |         |        |               |

|-------------|-------|----------------------------------------------------|--------|--------|--------|--------|-------------|-------------|--------------|----------|-------|-------|------------|-------------|--------------|---------|--------|---------------|

| SFR<br>Name | Addr. | Bit 15                                             | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10      | Bit 9       | Bit 8        | Bit 7    | Bit 6 | Bit 5 | Bit 4      | Bit 3       | Bit 2        | Bit 1   | Bit 0  | All<br>Resets |

| DOENDL      | 003E  | 3E DO Loop End Address Register Low (DOENDL<15:1>) |        |        |        |        |             |             |              |          |       | —     | 0000       |             |              |         |        |               |

| DOENDH      | 0040  | _                                                  | _      | _      | _      | _      | _           | _           | _            | _        | _     | DO LO | oop End Ad | dress Regis | ster High ([ | DOENDH< | 5:0>)  | 0000          |

| SR          | 0042  | OA                                                 | OB     | SA     | SB     | OAB    | SAB         | DA          | DC           | IPL2     | IPL1  | IPL0  | RA         | Ν           | OV           | Z       | С      | 0000          |

| CORCON      | 0044  | VAR                                                | _      | US1    | US0    | EDT    | DL2         | DL1         | DL0          | SATA     | SATB  | SATDW | ACCSAT     | IPL3        | SFA          | RND     | IF     | 0020          |

| MODCON      | 0046  | XMODEN                                             | YMODEN | _      | _      | BWM3   | BWM2        | BWM1        | BWM0         | YWM3     | YWM2  | YWM1  | YWM0       | XWM3        | XWM2         | XWM1    | XWM0   | 0000          |

| XMODSRT     | 0048  |                                                    |        |        |        |        | X Mode Star | t Address F | Register (XN | 10DSRT<1 | 5:1>) |       |            |             |              |         | _      | 0000          |

| XMODEND     | 004A  |                                                    |        |        |        |        | X Mode End  | I Address R | egister (XN  | ODEND<1  | 5:1>) |       |            |             |              |         | _      | 0001          |

| YMODSRT     | 004C  |                                                    |        |        |        |        | Y Mode Star | t Address F | Register (YN | 10DSRT<1 | 5:1>) |       |            |             |              |         | _      | 0000          |

| YMODEND     | 004E  |                                                    |        |        |        |        | Y Mode End  | I Address R | egister (YN  | ODEND<1  | 5:1>) |       |            |             |              |         | _      | 0001          |

| XBREV       | 0050  | BREN                                               |        |        |        |        |             |             | XBRE         | V<14:0>  |       |       |            |             |              |         |        | 0000          |

| DISICNT     | 0052  | — — DISICNT<13:0>                                  |        |        |        |        |             |             |              | 0000     |       |       |            |             |              |         |        |               |

| TBLPAG      | 0054  | TBLPAG<7:0>                                        |        |        |        |        |             |             | 0000         |          |       |       |            |             |              |         |        |               |

| CTXTSTAT    | 005A  | _                                                  | _      | _      | _      | _      | CCTXI2      | CCTXI1      | CCTXI0       | _        | _     | _     | _          | —           | MCTXI2       | MCTXI1  | MCTXI0 | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The contents of this register should never be modified. The DSWPAG must always point to the first page.

# 5.2 RTSP Operation

The dsPIC33EPXXGS50X family Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a single page (8 rows or 512 instructions) of memory at a time and to program one row at a time. It is possible to program two instructions at a time as well.

The page erase and single row write blocks are edgealigned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively. Figure 26-14 in **Section 26.0 "Electrical Characteristics"** lists the typical erase and programming times.

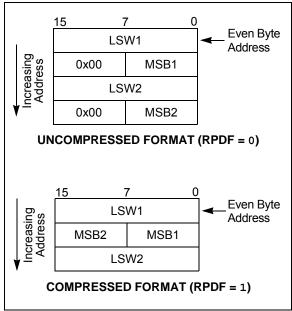

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

The basic sequence for RTSP word programming is to use the TBLWTL and TBLWTH instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. Refer to Figure 4-1 through Figure 4-4 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

All erase and program operations may optionally use the NVM interrupt to signal the successful completion of the operation. For example, when performing Flash write operations on the Inactive Partition in Dual Partition mode, where the CPU remains running, it is necessary to wait for the NVM interrupt before programming the next block of Flash program memory.

### FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

# 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000000, 0x000004, 0x000008, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

| R/W-0           | R/W-0                                  | R/W-0                                                                                           | R/W-0              | R/W-0                              | R/W-0          | R/W-0              | R/W-0  |  |

|-----------------|----------------------------------------|-------------------------------------------------------------------------------------------------|--------------------|------------------------------------|----------------|--------------------|--------|--|

| T1CKR7          | T1CKR6                                 | T1CKR5                                                                                          | T1CKR4             | T1CKR3                             | T1CKR2         | T1CKR1             | T1CKR0 |  |

| bit 15          |                                        |                                                                                                 |                    |                                    |                |                    | bit 8  |  |

|                 |                                        |                                                                                                 |                    |                                    |                |                    |        |  |

| U-0             | U-0                                    | U-0                                                                                             | U-0                | U-0                                | U-0            | U-0                | U-0    |  |

| —               | —                                      | —                                                                                               | —                  | _                                  | -              | —                  | —      |  |

| bit 7           |                                        |                                                                                                 |                    |                                    |                | •                  | bit 0  |  |

|                 |                                        |                                                                                                 |                    |                                    |                |                    |        |  |

| Legend:         |                                        |                                                                                                 |                    |                                    |                |                    |        |  |

| R = Readable    | bit                                    | W = Writable                                                                                    | bit                | U = Unimplemented bit, read as '0' |                |                    |        |  |

| -n = Value at P | OR                                     | '1' = Bit is set                                                                                |                    | '0' = Bit is cle                   | ared           | x = Bit is unknown |        |  |

| bit 15-8        | 10110101 =<br>10110100 =<br>00000001 = | : Assign Timer'<br>Input tied to RF<br>Input tied to RF<br>Input tied to RF<br>Input tied to Vs | 2181<br>2180<br>21 | ck (T1CK) to t                     | he Correspondi | ng RPn Pin bits    | 5      |  |

#### REGISTER 10-3: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2

bit 7-0 Unimplemented: Read as '0'

# **REGISTER 15-13:** PDCx: PWMx GENERATOR DUTY CYCLE REGISTER (x = 1 to 5)<sup>(1,2,3)</sup>

| R/W-0           | R/W-0                             | R/W-0 | R/W-0             | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|-----------------|-----------------------------------|-------|-------------------|--------------|-----------------|----------|-------|

|                 |                                   |       | PDC               | x<15:8>      |                 |          |       |

| bit 15          |                                   |       |                   |              |                 |          | bit 8 |

|                 |                                   |       |                   |              |                 |          |       |

| R/W-0           | R/W-0                             | R/W-0 | R/W-0             | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                 |                                   |       | PDO               | Cx<7:0>      |                 |          |       |

| bit 7           |                                   |       |                   |              |                 |          | bit 0 |

|                 |                                   |       |                   |              |                 |          |       |

| Legend:         |                                   |       |                   |              |                 |          |       |

| R = Readable    | R = Readable bit W = Writable bit |       |                   | U = Unimplen | nented bit, rea | d as '0' |       |

| -n = Value at I | '1' = Bit is set                  |       | '0' = Bit is clea | ared         | x = Bit is unkr | nown     |       |

bit 15-0 **PDCx<15:0>:** PWMx Generator Duty Cycle Value bits

**Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In the Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL.

**2:** The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

**3:** As the duty cycle gets closer to 0% or 100% of the PWMx period (0 to 40 ns, depending on the mode of operation), PWMx duty cycle resolution will increase from 1 to 3 LSBs.

# **REGISTER 15-14:** SDCx: PWMx SECONDARY DUTY CYCLE REGISTER (x = 1 to 5)<sup>(1,2,3)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | SDCx  | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|        | -     | -     | SDCx  | (<7:0> | -     | -     |       |

| bit 7  |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 SDCx<15:0>: PWMx Secondary Duty Cycle for PWMxL Output Pin bits

**Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle.

- **2:** The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period 0x0008.

- **3:** As the duty cycle gets closer to 0% or 100% of the PWMx period (0 to 40 ns, depending on the mode of operation), PWMx duty cycle resolution will increase from 1 to 3 LSBs.

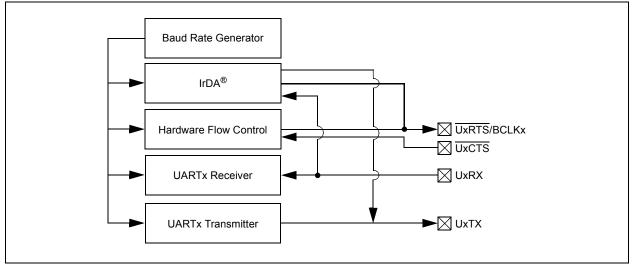

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXGS50X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps in 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps in 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit Mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 18-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 18-1: UARTx SIMPLIFIED BLOCK DIAGRAM

| R-0, HSC        | U-0                                                                                                                  | U-0                 | U-0             | R-0, HSC          | R-0, HSC       | R-0, HSC        | R-0, HSC |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|-------------------|----------------|-----------------|----------|--|--|--|--|--|

| SHRRDY          | —                                                                                                                    | _                   | —               | C3RDY             | C2RDY          | C1RDY           | CORDY    |  |  |  |  |  |

| bit 15          |                                                                                                                      |                     |                 |                   |                |                 | bit 8    |  |  |  |  |  |

|                 |                                                                                                                      |                     |                 |                   |                |                 |          |  |  |  |  |  |

| R/W-0           | U-0                                                                                                                  | U-0                 | U-0             | R/W-0             | R/W-0          | R/W-0           | R/W-0    |  |  |  |  |  |

| SHRPWR<br>bit 7 |                                                                                                                      | —                   | —               | C3PWR             | C2PWR          | C1PWR           | C0PWR    |  |  |  |  |  |

|                 |                                                                                                                      |                     |                 |                   |                |                 | bit (    |  |  |  |  |  |

| Legend:         |                                                                                                                      | U = Unimplem        | nented bit, rea | id as '0'         |                |                 |          |  |  |  |  |  |

| R = Readabl     | e bit                                                                                                                | W = Writable        | oit             | HSC = Hardw       | are Settable/C | learable bit    |          |  |  |  |  |  |

| -n = Value at   | POR                                                                                                                  | '1' = Bit is set    |                 | '0' = Bit is clea | ared           | x = Bit is unkr | iown     |  |  |  |  |  |

| bit 15          | SHRRDY: Sh                                                                                                           | ared ADC Core       | Ready Flag      | bit               |                |                 |          |  |  |  |  |  |

|                 | SHRRDY: Shared ADC Core Ready Flag bit<br>1 = ADC core is powered and ready for operation                            |                     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 14-12       |                                                                                                                      | is not ready fo     | -               |                   |                |                 |          |  |  |  |  |  |

| bit 14-12       |                                                                                                                      | ted: Read as '      |                 | ag hit            |                |                 |          |  |  |  |  |  |

|                 | <b>C3RDY:</b> Dedicated ADC Core 3 Ready Flag bit<br>1 = ADC core is powered and ready for operation                 |                     |                 |                   |                |                 |          |  |  |  |  |  |

|                 |                                                                                                                      | is not ready fo     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 10          |                                                                                                                      | cated ADC Cor       | •               | •                 |                |                 |          |  |  |  |  |  |

|                 | <ul> <li>1 = ADC core is powered and ready for operation</li> <li>0 = ADC core is not ready for operation</li> </ul> |                     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 9           |                                                                                                                      | •                   | •               | ag hit            |                |                 |          |  |  |  |  |  |

|                 | C1RDY: Dedicated ADC Core 1 Ready Flag bit<br>1 = ADC core is powered and ready for operation                        |                     |                 |                   |                |                 |          |  |  |  |  |  |

|                 |                                                                                                                      | is not ready fo     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 8           | CORDY: Dedicated ADC Core 0 Ready Flag bit                                                                           |                     |                 |                   |                |                 |          |  |  |  |  |  |

|                 | <ul> <li>1 = ADC core is powered and ready for operation</li> <li>0 = ADC core is not ready for operation</li> </ul> |                     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 7           |                                                                                                                      | -                   | •               | able hit          |                |                 |          |  |  |  |  |  |

|                 | SHRPWR: Shared ADC Core x Power Enable bit<br>1 = ADC Core x is powered                                              |                     |                 |                   |                |                 |          |  |  |  |  |  |

|                 | 0 = ADC  Core  x  is off                                                                                             |                     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 6-4         | -                                                                                                                    | ted: Read as 'o     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 3           |                                                                                                                      | licated ADC Co      | re 3 Power E    | nable bit         |                |                 |          |  |  |  |  |  |

|                 | 1 = ADC core is powered                                                                                              |                     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 2           | <ul> <li>0 = ADC core is off</li> <li>C2PWR: Dedicated ADC Core 2 Power Enable bit</li> </ul>                        |                     |                 |                   |                |                 |          |  |  |  |  |  |

|                 | 1 = ADC core                                                                                                         |                     |                 |                   |                |                 |          |  |  |  |  |  |

|                 | 0 = ADC core                                                                                                         | 0 = ADC core is off |                 |                   |                |                 |          |  |  |  |  |  |

| bit 1           | C1PWR: Dedicated ADC Core 1 Power Enable bit                                                                         |                     |                 |                   |                |                 |          |  |  |  |  |  |

|                 | 1 = ADC core<br>0 = ADC core                                                                                         |                     |                 |                   |                |                 |          |  |  |  |  |  |

| bit 0           |                                                                                                                      | licated ADC Co      | re 0 Power E    | nable bit         |                |                 |          |  |  |  |  |  |

|                 | 1 = ADC core                                                                                                         | •                   |                 |                   |                |                 |          |  |  |  |  |  |

|                 | 0 = ADC core                                                                                                         | us off              |                 |                   |                |                 |          |  |  |  |  |  |

## REGISTER 19-9: ADCON5L: ADC CONTROL REGISTER 5 LOW

## REGISTER 21-1: PGAxCON: PGAx CONTROL REGISTER (CONTINUED)

- bit 2-0 GAIN<2:0>: PGAx Gain Selection bits

- 111 = Reserved

- 110 = Gain of 64x

- 101 = Gain of 32x

- 100 = Gain of 16x

- 011 = Gain of 8x

- 010 = Gain of 4x

- 001 = Reserved

- 000 = Reserved

## REGISTER 21-2: PGAxCAL: PGAx CALIBRATION REGISTER

| U-0             | U-0 | U-0              | U-0   | U-0                                     | U-0      | U-0   | U-0   |  |

|-----------------|-----|------------------|-------|-----------------------------------------|----------|-------|-------|--|

| —               | —   | —                |       |                                         |          |       | —     |  |

| bit 15          |     |                  |       |                                         |          |       | bit 8 |  |

|                 |     |                  |       |                                         |          |       |       |  |

| U-0             | U-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 |  |

| —               | —   |                  |       | PGAC                                    | CAL<5:0> |       |       |  |

| bit 7           |     |                  |       |                                         |          |       | bit 0 |  |

|                 |     |                  |       |                                         |          |       |       |  |

| Legend:         |     |                  |       |                                         |          |       |       |  |

| R = Readable    | bit | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |          |       |       |  |

| -n = Value at P | OR  | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |          |       |       |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 PGACAL<5:0>: PGAx Offset Calibration bits

The calibration values for PGA1 and PGA2 must be copied from Flash addresses, 0x800E48 and 0x800E4C, respectively, into these bits before the module is enabled. Refer to the calibration data address table (Table 23-3) in **Section 23.0 "Special Features"** for more information.

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax       | Description                                                | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------|------------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 9                  | BSW                  | BSW.C   | Ws,Wb                 | Write C bit to Ws <wb></wb>                                | 1             | 1                             | None                     |

|                    |                      | BSW.Z   | Ws,Wb                 | Write Z bit to Ws <wb></wb>                                | 1             | 1                             | None                     |

| 10                 | BTG                  | BTG     | f,#bit4               | Bit Toggle f                                               | 1             | 1                             | None                     |

|                    |                      | BTG     | Ws,#bit4              | Bit Toggle Ws                                              | 1             | 1                             | None                     |

| 11                 | BTSC                 | BTSC    | f,#bit4               | Bit Test f, Skip if Clear                                  | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSC    | Ws,#bit4              | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)                 | None                     |

| 12                 | BTSS                 | BTSS    | f,#bit4               | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSS    | Ws,#bit4              | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)                 | None                     |

| 13                 | BTST                 | BTST    | f,#bit4               | Bit Test f                                                 | 1             | 1                             | Z                        |

|                    |                      | BTST.C  | Ws,#bit4              | Bit Test Ws to C                                           | 1             | 1                             | С                        |

|                    |                      | BTST.Z  | Ws,#bit4              | Bit Test Ws to Z                                           | 1             | 1                             | Z                        |

|                    |                      | BTST.C  | Ws,Wb                 | Bit Test Ws <wb> to C</wb>                                 | 1             | 1                             | С                        |

|                    |                      | BTST.Z  | Ws,Wb                 | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1                             | Z                        |

| 14                 | BTSTS                | BTSTS   | f,#bit4               | Bit Test then Set f                                        | 1             | 1                             | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4              | Bit Test Ws to C, then Set                                 | 1             | 1                             | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4              | Bit Test Ws to Z, then Set                                 | 1             | 1                             | Z                        |

| 15                 | CALL                 | CALL    | lit23                 | Call subroutine                                            | 2             | 4                             | SFA                      |

|                    |                      | CALL    | Wn                    | Call indirect subroutine                                   | 1             | 4                             | SFA                      |

|                    |                      | CALL.L  | Wn                    | Call indirect subroutine (long address)                    | 1             | 4                             | SFA                      |

| 16                 | CLR                  | CLR     | f                     | f = 0x0000                                                 | 1             | 1                             | None                     |

|                    |                      | CLR     | WREG                  | WREG = 0x0000                                              | 1             | 1                             | None                     |

|                    |                      | CLR     | Ws                    | Ws = 0x0000                                                | 1             | 1                             | None                     |

|                    |                      | CLR     | Acc,Wx,Wxd,Wy,Wyd,AWB | Clear Accumulator                                          | 1             | 1                             | OA,OB,SA,SB              |

| 17                 | CLRWDT               | CLRWDT  |                       | Clear Watchdog Timer                                       | 1             | 1                             | WDTO,Sleep               |

| 18                 | COM                  | COM     | f                     | $f = \overline{f}$                                         | 1             | 1                             | N,Z                      |

|                    |                      | COM     | f,WREG                | WREG = f                                                   | 1             | 1                             | N,Z                      |

|                    |                      | COM     | Ws,Wd                 | $Wd = \overline{Ws}$                                       | 1             | 1                             | N,Z                      |

| 19                 | CP                   | CP      | f                     | Compare f with WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,#lit8              | Compare Wb with lit8                                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                 | Compare Wb with Ws (Wb – Ws)                               | 1             | 1                             | C,DC,N,OV,Z              |

| 20                 | CP0                  | CP0     | f                     | Compare f with 0x0000                                      | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CP0     | Ws                    | Compare Ws with 0x0000                                     | 1             | 1                             | C,DC,N,OV,Z              |

| 21                 | CPB                  | CPB     | f                     | Compare f with WREG, with Borrow                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit8              | Compare Wb with lit8, with Borrow                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                 | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

| 22                 | CPSEQ                | CPSEQ   | Wb,Wn                 | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBEQ                | CPBEQ   | Wb,Wn,Expr            | Compare Wb with Wn, branch if =                            | 1             | 1 (5)                         | None                     |

| 23                 | CPSGT                | CPSGT   | Wb,Wn                 | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBGT                | CPBGT   | Wb,Wn,Expr            | Compare Wb with Wn, branch if >                            | 1             | 1 (5)                         | None                     |

| 24                 | CPSLT                | CPSLT   | Wb,Wn                 | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBLT                | CPBLT   | Wb,Wn,Expr            | Compare Wb with Wn, branch if <                            | 1             | 1 (5)                         | None                     |

| 25                 | CPSNE                | CPSNE   | Wb,Wn                 | Compare Wb with Wn, skip if ≠                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBNE                | CPBNE   | Wb,Wn,Expr            | Compare Wb with Wn, branch if ≠                            | 1             | 1 (5)                         | None                     |

### TABLE 24-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTERISTICS |                                      |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |     |                                                       | $\leq$ TA $\leq$ +85°C for Industrial                                                                                                                                                                                                    |

|--------------------|--------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.             | Symbol                               | Characteristic                                              | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                         |   |     | Conditions                                            |                                                                                                                                                                                                                                          |

| DO10               | Vol                                  | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    | _                                                                                                                                                                                                                                                                                       |   | 0.4 | V                                                     | $ \begin{array}{l} V{\rm DD} = 3.3{\rm V}, \\ {\rm IOL} \le 6 \mbox{ mA}, \ -40^{\circ}{\rm C} \le {\rm Ta} \le +85^{\circ}{\rm C}, \\ {\rm IOL} \le 5 \mbox{ mA}, \ +85^{\circ}{\rm C} < {\rm Ta} \le +125^{\circ}{\rm C} \end{array} $ |

|                    |                                      | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                       | — | 0.4 | V                                                     | $V_{DD}$ = 3.3V,<br>IOL $\leq$ 12 mA, -40°C $\leq$ TA $\leq$ +85°C,<br>IOL $\leq$ 8 mA, +85°C $<$ TA $\leq$ +125°C                                                                                                                       |

| DO20               | Vон                                  | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                                                                     | _ | _   | V                                                     | IOH ≥ -10 mA, VDD = 3.3V                                                                                                                                                                                                                 |

|                    |                                      | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                                                                                                                                                                     | _ | _   | V                                                     | IOH ≥ -15 mA, VDD = 3.3V                                                                                                                                                                                                                 |

| DO20A              | Von1                                 | Output High Voltage                                         | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | _ | _   |                                                       | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                                                                    |

|                    | 4x Source Driver Pins <sup>(2)</sup> | 2.0 <sup>(1)</sup>                                          |                                                                                                                                                                                                                                                                                         |   | V   | $IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$ |                                                                                                                                                                                                                                          |

|                    |                                      |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                  | _ | -   |                                                       | IOH $\ge$ -7 mA, VDD = 3.3V                                                                                                                                                                                                              |

| l                  |                                      |                                                             | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | _ | _   |                                                       | $IOH \ge -22 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                                                                    |

|                    | 8x Source Driver Pins <sup>(3)</sup> | 2.0 <sup>(1)</sup>                                          | _                                                                                                                                                                                                                                                                                       | _ | V   | $IOH \ge -18 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$ |                                                                                                                                                                                                                                          |

|                    |                                      |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                  | — | —   |                                                       | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                                                                                                                                            |

### TABLE 26-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes RA0-RA2, RB0-RB1, RB9-RB10, RC1-RC2, RC9-RC10, RC12 and RD7 pins.

3: Includes all I/O pins that are not 4x driver pins (see **Note 2**).

#### TABLE 26-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                            | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |      |       |                        |

|--------------------|--------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------|

| Param<br>No.       | Symbol | Characteristic                             | Min. <sup>(2)</sup>                                                                                                                                                                                                         | Тур. | Max. | Units | Conditions             |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low | 2.65                                                                                                                                                                                                                        | _    | 2.95 | V     | VDD<br>(Notes 2 and 3) |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, PGAs and comparators) may have degraded performance.

2: Parameters are for design guidance only and are not tested in manufacturing.

**3:** The VBOR specification is relative to VDD.

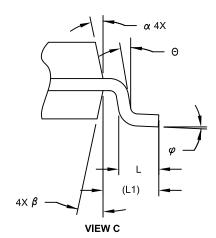

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N         | <b>ILLIMETER</b> | S        |      |

|--------------------------|-----------|------------------|----------|------|

| Dimension                | Limits    | MIN              | NOM      | MAX  |

| Number of Pins           | N         |                  | 28       |      |

| Pitch                    | е         |                  | 1.27 BSC |      |

| Overall Height           | A         | -                | -        | 2.65 |

| Molded Package Thickness | A2        | 2.05             | -        | -    |

| Standoff §               | A1        | 0.10             | -        | 0.30 |

| Overall Width            | E         | 10.30 BSC        |          |      |

| Molded Package Width     | E1        | 7.50 BSC         |          |      |

| Overall Length           | D         | 17.90 BSC        |          |      |

| Chamfer (Optional)       | h         | 0.25             | -        | 0.75 |

| Foot Length              | L         | 0.40             | -        | 1.27 |

| Footprint                | L1        |                  | 1.40 REF |      |

| Lead Angle               | Θ         | 0°               | -        | -    |

| Foot Angle               | $\varphi$ | 0°               | -        | 8°   |

| Lead Thickness           | С         | 0.18             | -        | 0.33 |

| Lead Width               | b         | 0.31             | -        | 0.51 |

| Mold Draft Angle Top     | α         | 5°               | -        | 15°  |

| Mold Draft Angle Bottom  | β         | 5°               | -        | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

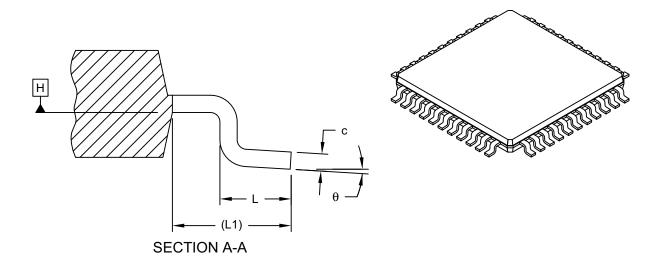

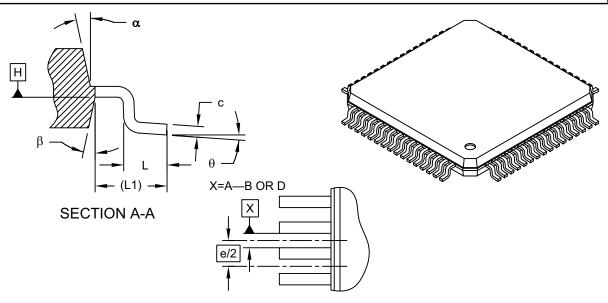

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           |           | S    |