Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

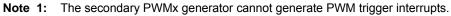

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

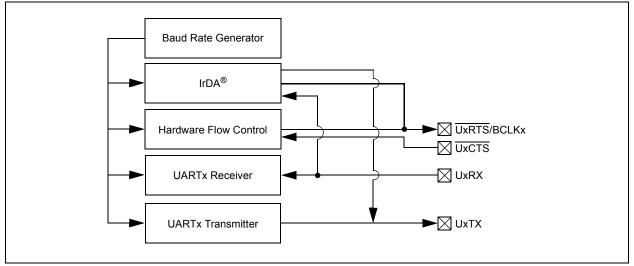

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502t-e-2n |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD |       | —      | ADCMD | 0000          |

| PMD2        | 0762  |        | —      | —      | -      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | -      |       | —     | -      | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3        | 0764  | Ι      | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | _     | _      | _      | _     | I2C2MD | _     | 0000          |

| PMD4        | 0766  | Ι      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | _     | _      | _     | 0000          |

| PMD6        | 076A  | Ι      | _      | _      | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _     | _      | _     | 0000          |

| PMD7        | 076C  | Ι      | _      | _      | _      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | _     | _     | _      | _      | _     | PGA1MD | _     | 0000          |

| PMD8        | 076E  | _      | —      | _      | —      | _      | PGA2MD | ABGMD  | _      | _      | _     | —     | _      | _      | _     | CCSMD  |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-24: CONSTANT-CURRENT SOURCE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|-------|-------|----------|----------|----------|----------|----------|----------|---------------|

| ISRCCON     | 0500  | ISRCEN | _      |        | _      |        | OUTSEL2 | OUTSEL1 | OUTSEL0 | _     | _     | ISRCCAL5 | ISRCCAL4 | ISRCCAL3 | ISRCCAL2 | ISRCCAL1 | ISRCCAL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-25: PROGRAMMABLE GAIN AMPLIFIER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| PGA1CON     | 0504  | PGAEN  | PGAOEN | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 | _     | _     |       |       |       | GAIN2  | GAIN1 | GAIN0 | 0000          |

| PGA1CAL     | 0506  | _      | —      | —      | —      | _      | —      | _      | _      | —     | —     |       |       | PGACA | L<5:0> |       |       | 0000          |

| PGA2CON     | 0508  | PGAEN  | PGAOEN | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 | —     | —     | _     | —     | _     | GAIN2  | GAIN1 | GAIN0 | 0000          |

| PGA2CAL     | 050A  | _      | —      | —      | —      | _      | —      | _      | _      | —     | —     |       |       | PGACA | L<5:0> |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-30: PORTA REGISTER MAP FOR dsPIC33EPXXGS504/505 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|------------|-------|------------|-----------|-------|---------------|

| TRISA       | 0E00  | _      | _      | _      | _      |        |        | —     |       | _     |       | —     |            | -     | TRISA<4:0> |           |       | 001F          |

| PORTA       | 0E02  | _      | _      | —      | _      |        |        | —     |       | _     | _     | —     | RA<4:0>    |       |            |           |       | 0000          |

| LATA        | 0E04  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | LATA<4:0>  |       |            |           | 0000  |               |

| ODCA        | 0E06  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            | (     | ODCA<4:0>  |           |       | 0000          |

| CNENA       | 0E08  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            | (     | CNIEA<4:0> |           |       | 0000          |

| CNPUA       | 0E0A  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            | C     | NPUA<4:0   | >         |       | 0000          |

| CNPDA       | 0E0C  | _      | _      | _      | _      | _      | _      | _     | _     | —     | _     | _     | CNPDA<4:0> |       |            | 0000      |       |               |

| ANSELA      | 0E0E  | _      | —      | _      | —      | -      | -      | —     |       | —     |       | —     | —          | —     | /          | ANSA<2:0> |       | 0007          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-31: PORTB REGISTER MAP FOR dsPIC33EPXXGS504/505 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|-----------------------------------------|--------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB       | 0E10  |        |                                         |        |        |        |        |       | TRISB<1 | 5:0>  |       |       |       |       |       |       |       | FFFF          |

| PORTB       | 0E12  |        | RB<15:0>                                |        |        |        |        |       |         |       | xxxx  |       |       |       |       |       |       |               |

| LATB        | 0E14  |        |                                         |        |        |        |        |       |         |       | xxxx  |       |       |       |       |       |       |               |

| ODCB        | 0E16  |        | ODCB<15:0> 0                            |        |        |        |        |       |         |       | 0000  |       |       |       |       |       |       |               |

| CNENB       | 0E18  |        |                                         |        |        |        |        |       | CNIEB<1 | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPUB       | 0E1A  |        |                                         |        |        |        |        |       | CNPUB<1 | 15:0> |       |       |       |       |       |       |       | 0000          |

| CNPDB       | 0E1C  |        | CNPDB<15:0> 0                           |        |        |        |        |       |         |       | 0000  |       |       |       |       |       |       |               |

| ANSELB      | 0E1E  | —      | ANSB<10:9> - ANSB<7:5> - ANSB<3:0> 06EH |        |        |        |        |       |         |       | 06EF  |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-32: PORTC REGISTER MAP FOR dsPIC33EPXXGS504/505 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13                                | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|---------------------------------------|-------------|--------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC       | 0E20  | _      | _      |                                       | TRISC<13:0> |        |        |       |       |        |        | 3FFF  |       |       |       |       |       |               |

| PORTC       | 0E22  | _      | _      |                                       | RC<13:0>    |        |        |       |       |        |        |       | xxxx  |       |       |       |       |               |

| LATC        | 0E24  | _      | _      |                                       | LATC<13:0>  |        |        |       |       |        |        | xxxx  |       |       |       |       |       |               |

| ODCC        | 0E26  |        | _      |                                       | ODCC<13:0>  |        |        |       |       |        | 0000   |       |       |       |       |       |       |               |

| CNENC       | 0E28  |        | _      |                                       |             |        |        |       |       | CNIEC< | 13:0>  |       |       |       |       |       |       | 0000          |

| CNPUC       | 0E2A  |        | _      |                                       |             |        |        |       |       | CNPUC< | :13:0> |       |       |       |       |       |       | 0000          |

| CNPDC       | 0E2C  |        | _      |                                       | CNPDC<13:0> |        |        |       |       |        |        | 0000  |       |       |       |       |       |               |

| ANSELC      | 0E2E  | _      | _      | - ANSC<12:9> ANSC<6:4> - ANSC<2:0> 1E |             |        |        |       |       |        |        | 1E77  |       |       |       |       |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 4.7.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

### 4.8 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

## 4.8.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these situations are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume<br>word-sized data (LSb of every EA is<br>always clear). The XB value is scaled<br>accordingly to generate compatible (byte) |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | addresses.                                                                                                                                                           |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed        |

|-------|-------------------------------------------|

|       | Addressing can be enabled simultaneously  |

|       | using the same W register, but Bit-       |

|       | Reversed Addressing operation will always |

|       | take precedence for data writes when      |

|       | enabled.                                  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### 8.1 **CPU Clocking System**

The dsPIC33EPXXGS50X family of devices provides six system clock options:

- · Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (FRCPLL)

- · FRC Oscillator with Postscaler

- · Primary (XT, HS or EC) Oscillator

- · Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

0.8 MHz < FPLLI<sup>(1)</sup> < 8.0 MHz FPLLO<sup>(1)</sup> ≤ 120 MHz @ +125℃ 120 MHz < Fvco<sup>(1)</sup> < 340 MHz FPLLO<sup>(1)</sup> ≤ 140 MHz @ +85°C FPLL ÷N1 Fvco Fosc PFD VCO ÷ N2 PLLPRE<4:0> PLLPOST<1:0> ÷Μ PLLDIV<8:0> Note 1: This frequency range must be met at all times.

#### **FIGURE 8-2:** PLL BLOCK DIAGRAM

Instruction execution speed or device operating frequency, FCY, is given by Equation 8-1.

#### **EQUATION 8-1: DEVICE OPERATING** FREQUENCY

### FCY = FOSC/2

Figure 8-2 is a block diagram of the PLL module. Equation 8-2 provides the relationship between Input Frequency (FIN) and Output Frequency (FPLLO). Equation 8-3 provides the relationship between Input Frequency (FIN) and VCO Frequency (FVCO).

#### **EQUATION 8-2: FPLLO CALCULATION**

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{PLLDIV < 8:0 > + 2}{(PLLPRE < 4:0 > + 2) \times 2(PLLPOST < 1:0 > + 1)}\right)$$

Where: N1 = PLLPRE < 4:0 > +2

$N2 = 2 \times (PLLPOST < 1:0 > +1)$ M = PLLDIV < 8:0 > +2

#### **EQUATION 8-3: Fvco CALCULATION**

$$F_{VCO} = F_{IN} \times \left(\frac{M}{N1}\right) = F_{IN} \times \left(\frac{PLLDIV < 8:0 > +2}{(PLLPRE < 4:0 > +2)}\right)$$

### 8.5 Oscillator Control Registers

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | R/W-0  | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|--------|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | IOLOCK | LOCK | —   | CF <sup>(3)</sup> | —   | —   | OSWEN |

| bit 7   |        |      |     |                   |     |     | bit 0 |

| Legend:           | y = Value set from Cor | nfiguration bits on POR |                    |

|-------------------|------------------------|-------------------------|--------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit   | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared    | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | <b>COSC&lt;2:0&gt;:</b> Current Oscillator Selection bits (read-only)<br>111 = Fast RC Oscillator (FRC) with Divide-by-n<br>110 = Fast RC Oscillator (FRC) with Divide-by-16                  |

|           | 101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved                                                                                                                                        |

|           | 011 = Primary Oscillator (XT, HS, EC) with PLL<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                    |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                                                                                                                       |

|           | 111 = Fast RC Oscillator (FRC) with Divide-by-n                                                                                                                                               |

|           | 110 = Fast RC Oscillator (FRC) with Divide-by-16<br>101 = Low-Power RC Oscillator (LPRC)                                                                                                      |

|           | 100 = Reserved                                                                                                                                                                                |

|           | 011 = Primary Oscillator (XT, HS, EC) with PLL                                                                                                                                                |

|           | 010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)                                                                                     |

|           | 000 = Fast RC Oscillator (FRC)                                                                                                                                                                |

| bit 7     | CLKLOCK: Clock Lock Enable bit                                                                                                                                                                |

|           | 1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and<br>PLL configurations may be modified                                                      |

|           | <ul> <li>0 = Clock and PLL selections are not locked, configurations may be modified</li> </ul>                                                                                               |

| bit 6     | IOLOCK: I/O Lock Enable bit                                                                                                                                                                   |

|           | 1 = I/O lock is active                                                                                                                                                                        |

| hit E     | 0 = I/O lock is not active                                                                                                                                                                    |

| bit 5     | <b>LOCK:</b> PLL Lock Status bit (read-only)<br>1 = Indicates that PLL is in lock or PLL start-up timer is satisfied                                                                          |

|           | 0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled                                                                                                       |

| Note 1:   | Writes to this register require an unlock sequence.                                                                                                                                           |

| 2:        | Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.                                                                                         |

|           | This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.                     |

| 3:        | This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an                                                                                |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| R/W-0           | U-0                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| ROON            |                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                           | ROSEL                                                                                                                                                                                                | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15          |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       | bit 8                 |  |  |  |

| U-0             | U-0                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                  | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

| _               | _                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                    |                       | —                     | —                     | _                     |  |  |  |

| bit 7           |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       | bit C                 |  |  |  |

| Legend:         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

| R = Readable    | bit                                                                                                                                                                                                          | W = Writable b                                                                                                                                                                                                                                                                                                                                   | bit                                                                                                                                                                                                  | U = Unimplem          | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at F |                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                      | '0' = Bit is clea     |                       | x = Bit is unkr       | nown                  |  |  |  |

|                 |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

| bit 15          | 1 = Reference                                                                                                                                                                                                | ence Oscillator<br>e oscillator outp<br>e oscillator outp                                                                                                                                                                                                                                                                                        | ut is enabled of                                                                                                                                                                                     |                       | 2)                    |                       |                       |  |  |  |

| bit 14          | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                    |                       |                       |                       |                       |  |  |  |

| bit 13          | ROSSLP: Reference Oscillator Run in Sleep bit                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                              | e oscillator outp<br>e oscillator outp                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

| bit 12          | ROSEL: Reference Oscillator Source Select bit                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                              | crystal is used                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

| bit 11-8        | <ul> <li>0 = System clock is used as the reference clock</li> <li>RODIV&lt;3:0&gt;: Reference Oscillator Divider bits<sup>(1)</sup></li> </ul>                                                               |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                 | 1110 = Refer<br>1101 = Refer<br>1100 = Refer<br>1011 = Refer<br>1010 = Refer<br>1000 = Refer<br>0111 = Refer<br>0110 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer | ence clock divic<br>ence clock divic | led by 16,384<br>led by 8,192<br>led by 4,096<br>led by 2,048<br>led by 1,024<br>led by 512<br>led by 512<br>led by 256<br>led by 128<br>led by 64<br>led by 32<br>led by 16<br>led by 8<br>led by 4 |                       |                       |                       |                       |  |  |  |

| bit 7-0         | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                    |                       |                       |                       |                       |  |  |  |

|                 | •                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

|  | REGISTER 9-2: | PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 |

|--|---------------|----------------------------------------------------|

|--|---------------|----------------------------------------------------|

| U-0          | U-0                                                                                                       | U-0                                       | U-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|-------------------|-----------------|-----------------|-------|--|--|--|

| —            |                                                                                                           |                                           | —   | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |

| pit 15       |                                                                                                           |                                           |     |                   | I               |                 | bit 8 |  |  |  |

| U-0          | U-0                                                                                                       | U-0                                       | U-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| _            | _                                                                                                         | _                                         | —   | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |

| bit 7        |                                                                                                           | ·                                         |     |                   |                 |                 | bit ( |  |  |  |

| Legend:      |                                                                                                           |                                           |     |                   |                 |                 |       |  |  |  |

| R = Readab   | le bit                                                                                                    | W = Writable I                            | oit | U = Unimplen      | nented bit, rea | ıd as '0'       |       |  |  |  |

| -n = Value a | t POR                                                                                                     | '1' = Bit is set                          |     | '0' = Bit is clea |                 | x = Bit is unkr | nown  |  |  |  |

| bit 15-12    | Unimplom                                                                                                  | nted. Dood oo '                           | .,  |                   |                 |                 |       |  |  |  |

| bit 11       | -                                                                                                         | ented: Read as '0<br>out Capture 4 Moo    |     | i+                |                 |                 |       |  |  |  |

|              | •                                                                                                         | apture 4 module i                         |     | iit.              |                 |                 |       |  |  |  |

|              |                                                                                                           | apture 4 module i                         |     |                   |                 |                 |       |  |  |  |

| oit 10       | IC3MD: Input Capture 3 Module Disable bit                                                                 |                                           |     |                   |                 |                 |       |  |  |  |

|              | 1 = Input Capture 3 module is disabled                                                                    |                                           |     |                   |                 |                 |       |  |  |  |

|              | 0 = Input Capture 3 module is enabled                                                                     |                                           |     |                   |                 |                 |       |  |  |  |

| bit 9        | IC2MD: Inp                                                                                                | IC2MD: Input Capture 2 Module Disable bit |     |                   |                 |                 |       |  |  |  |

|              | 1 = Input Capture 2 module is disabled                                                                    |                                           |     |                   |                 |                 |       |  |  |  |

|              |                                                                                                           | apture 2 module i                         |     |                   |                 |                 |       |  |  |  |

| bit 8        | IC1MD: Input Capture 1 Module Disable bit                                                                 |                                           |     |                   |                 |                 |       |  |  |  |

|              | <ul> <li>1 = Input Capture 1 module is disabled</li> <li>0 = Input Capture 1 module is enabled</li> </ul> |                                           |     |                   |                 |                 |       |  |  |  |

| bit 7-4      |                                                                                                           | ented: Read as '(                         |     |                   |                 |                 |       |  |  |  |

| bit 3        | •                                                                                                         | utput Compare 4                           |     | ole hit           |                 |                 |       |  |  |  |

|              |                                                                                                           | Compare 4 modu                            |     |                   |                 |                 |       |  |  |  |

|              | 0 = Output Compare 4 module is enabled                                                                    |                                           |     |                   |                 |                 |       |  |  |  |

| bit 2        | OC3MD: Output Compare 3 Module Disable bit                                                                |                                           |     |                   |                 |                 |       |  |  |  |

|              |                                                                                                           | Compare 3 modu<br>Compare 3 modu          |     |                   |                 |                 |       |  |  |  |

| bit 1        | •                                                                                                         | utput Compare 2                           |     | ole bit           |                 |                 |       |  |  |  |

|              |                                                                                                           | Compare 2 modu<br>Compare 2 modu          |     |                   |                 |                 |       |  |  |  |

| bit 0        |                                                                                                           | utput Compare 1                           |     | ole bit           |                 |                 |       |  |  |  |

|              | 1 = Output                                                                                                |                                           |     |                   |                 |                 |       |  |  |  |

### **REGISTER 15-10: MDC: PWMx MASTER DUTY CYCLE REGISTER**<sup>(1,2)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                                   |       |                  | MDC   | C<15:8>                            |       |                 |       |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |

|                                   |       |                  |       |                                    |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | MD    | C<7:0>                             |       |                 |       |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |

|                                   |       |                  |       |                                    |       |                 |       |

| Legend:                           |       |                  |       |                                    |       |                 |       |

| R = Readable bit W = Writable bit |       |                  | oit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is clea                  | red   | x = Bit is unkr | nown  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

**Note 1:** The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

2: As the duty cycle gets closer to 0% or 100% of the PWMx period (0 to 40 ns, depending on the mode of operation), PWMx duty cycle resolution will increase from 1 to 3 LSBs.

### REGISTER 15-11: PWMKEY: PWMx PROTECTION LOCK/UNLOCK KEY REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | PWMKE | Y<15:8> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PWMK  | EY<7:0> |       |       |       |

| bit 7  |       |       |       |         |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PWMKEY<15:0>:** PWMx Protection Lock/Unlock Key Value bits

### **REGISTER 15-19: TRGCONX: PWMx TRIGGER CONTROL REGISTER (x = 1 to 5)**

| TRGDIV3<br>bit 15  | TRGDIV2                                                                                                                                                        | TRGDIV1           | TRGDIV0          | _                   |                  |                  | _         |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|---------------------|------------------|------------------|-----------|--|--|--|--|

| bit 15             |                                                                                                                                                                |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    |                                                                                                                                                                |                   | L                |                     |                  | I                | bit 8     |  |  |  |  |

|                    |                                                                                                                                                                |                   |                  |                     |                  |                  |           |  |  |  |  |

| R/W-0              | U-0                                                                                                                                                            | R/W-0             | R/W-0            | R/W-0               | R/W-0            | R/W-0            | R/W-0     |  |  |  |  |

| DTM <sup>(1)</sup> | <u> </u>                                                                                                                                                       | TRGSTRT5          | TRGSTRT4         | TRGSTRT3            | TRGSTRT2         | TRGSTRT1         | TRGSTRT0  |  |  |  |  |

| bit 7              |                                                                                                                                                                |                   |                  |                     |                  |                  | bit (     |  |  |  |  |

| Legend:            |                                                                                                                                                                |                   |                  |                     |                  |                  |           |  |  |  |  |

| R = Readable       | e bit                                                                                                                                                          | W = Writable      | bit              | U = Unimplem        | nented bit, read | l as '0'         |           |  |  |  |  |

| -n = Value at      | POR                                                                                                                                                            | '1' = Bit is set  |                  | '0' = Bit is clea   | ared             | x = Bit is unkn  | own       |  |  |  |  |

|                    |                                                                                                                                                                |                   |                  |                     |                  |                  |           |  |  |  |  |

| bit 15-12          | TRGDIV<3:0                                                                                                                                                     | Trigger # Out     | tput Divider bit | S                   |                  |                  |           |  |  |  |  |

|                    | 1111 <b>= Trigg</b> e                                                                                                                                          | er output for eve | ery 16th trigge  | revent              |                  |                  |           |  |  |  |  |

|                    | 1110 = Trigger output for every 15th trigger event                                                                                                             |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 1101 = Trigger output for every 14th trigger event                                                                                                             |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 1100 = Trigger output for every 13th trigger event<br>1011 = Trigger output for every 12th trigger event                                                       |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    |                                                                                                                                                                |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 1010 = Trigger output for every 11th trigger event<br>1001 = Trigger output for every 10th trigger event                                                       |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 1000 = Trigger output for every 9th trigger event                                                                                                              |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 0111 = Trigger output for every 8th trigger event                                                                                                              |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 0110 = Trigger output for every 7th trigger event                                                                                                              |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 0101 = Trigger output for every 6th trigger event<br>0100 = Trigger output for every 5th trigger event                                                         |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    |                                                                                                                                                                |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 0011 = Trigger output for every 4th trigger event<br>0010 = Trigger output for every 3rd trigger event                                                         |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 0001 = Trigger output for every 2nd trigger event                                                                                                              |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    |                                                                                                                                                                | er output for eve |                  |                     |                  |                  |           |  |  |  |  |

| bit 11-8           | Unimplemen                                                                                                                                                     | ted: Read as '0   | )'               |                     |                  |                  |           |  |  |  |  |

| bit 7              | Dual Trigger Mode bit <sup>(1)</sup>                                                                                                                           |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 1 = Secondary trigger event is combined with the primary trigger event to create a PWM trigger                                                                 |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | <ul> <li>Secondary trigger event is not combined with the primary trigger event to create a PWM trigger<br/>two separate PWM triggers are generated</li> </ul> |                   |                  |                     |                  |                  |           |  |  |  |  |

| bit 6              |                                                                                                                                                                | ted: Read as '(   | •                |                     |                  |                  |           |  |  |  |  |

| bit 5-0            | TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits                                                                                                      |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 111111 = Wait 63 PWM cycles before generating the first trigger event after the module is enabled                                                              |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | •                                                                                                                                                              |                   | 5                | <b>J</b>            | 00111            |                  |           |  |  |  |  |

|                    | •                                                                                                                                                              |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | •                                                                                                                                                              |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 000010 <b>= W</b> a                                                                                                                                            | ait 2 PWM cycle   | s before dene    | rating the first t  | rigger event aft | er the module i  | s enabled |  |  |  |  |

|                    | 000010 = Wait 2 PWM cycles before generating the first trigger event after the module is enabled                                                               |                   |                  |                     |                  |                  |           |  |  |  |  |

|                    | 000001 = Wa                                                                                                                                                    | it 1 PWM cvcle    | e before genera  | ating the first tri | gger event afte  | er the module is | enabled   |  |  |  |  |

### REGISTER 16-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 1 | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                                |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Transmit has not yet started, SPIxTXB is full                                                                                                                                                                                                           |

|       | 0 = Transmit has started, SPIxTXB is empty                                                                                                                                                                                                                  |

|       | Standard Buffer Mode:                                                                                                                                                                                                                                       |

|       | Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB.<br>Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.                                                               |

|       | Enhanced Buffer Mode:                                                                                                                                                                                                                                       |

|       | Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available<br>buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write<br>operation.                               |

| bit 0 | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                 |

|       | 1 = Receive is complete, SPIxRXB is full<br>0 = Receive is incomplete, SPIxRXB is empty                                                                                                                                                                     |

|       | Standard Buffer Mode:<br>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.                                                        |

|       | Enhanced Buffer Mode:<br>Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread<br>buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from<br>SPIxSR. |

NOTES:

| U-0          | U-0                                                                                                                                                          | U-0                                                              | U-0                          | U-0                         | U-0                                                                                                                                                                        | U-0             | U-0           |  |  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--|--|--|--|--|--|--|

|              | —                                                                                                                                                            | —                                                                | —                            | —                           |                                                                                                                                                                            | _               | —             |  |  |  |  |  |  |  |

| bit 15       |                                                                                                                                                              |                                                                  |                              |                             |                                                                                                                                                                            |                 | bit 8         |  |  |  |  |  |  |  |

| U-0          | R/W-0                                                                                                                                                        | R/W-0                                                            | R/W-0                        | R/W-0                       | R/W-0                                                                                                                                                                      | R/W-0           | R/W-0         |  |  |  |  |  |  |  |

|              | PCIE                                                                                                                                                         | SCIE                                                             | BOEN                         | SDAHT                       | SBCDE                                                                                                                                                                      | AHEN            | DHEN          |  |  |  |  |  |  |  |

| bit 7        |                                                                                                                                                              |                                                                  |                              |                             | 1                                                                                                                                                                          |                 | bit           |  |  |  |  |  |  |  |

| Legend:      |                                                                                                                                                              |                                                                  |                              |                             |                                                                                                                                                                            |                 |               |  |  |  |  |  |  |  |

| R = Readal   | ble bit                                                                                                                                                      | W = Writable                                                     | bit                          | U = Unimplem                | nented bit, read                                                                                                                                                           | as '0'          |               |  |  |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                       | '1' = Bit is set                                                 |                              | '0' = Bit is clea           | ared                                                                                                                                                                       | x = Bit is unkr | nown          |  |  |  |  |  |  |  |

|              |                                                                                                                                                              |                                                                  |                              |                             |                                                                                                                                                                            |                 |               |  |  |  |  |  |  |  |

| bit 15-7     | -                                                                                                                                                            | nted: Read as '                                                  |                              | 2                           |                                                                                                                                                                            |                 |               |  |  |  |  |  |  |  |

| bit 6        | •                                                                                                                                                            |                                                                  | •                            | I <sup>2</sup> C Slave mode | only)                                                                                                                                                                      |                 |               |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Enables interrupt on detection of Stop condition</li> <li>0 = Stop detection interrupts are disabled</li> </ul>                                 |                                                                  |                              |                             |                                                                                                                                                                            |                 |               |  |  |  |  |  |  |  |