Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502t-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

| 7                          | GOTO Instruction                                      | 0x000000                         |

|----------------------------|-------------------------------------------------------|----------------------------------|

|                            | Reset Address                                         | 0x000002                         |

| Ð                          | Interrupt Vector Table                                | 0x000004<br>0x0001FE             |

| User Memory Space          | User Program<br>Flash Memory<br>(22,207 instructions) | 0x000200<br>0x00AF7E             |

| er Mem                     | Device Configuration                                  | 0x00AF80<br>0x00AFFE             |

| Use                        |                                                       | 0x00B000                         |

|                            | Unimplemented                                         |                                  |

|                            | (Read '0's)                                           |                                  |

|                            | Reserved                                              | 0x7FFFFE<br>0x800000<br>0x800E46 |

|                            | Calibration Data                                      | 0x800E48                         |

|                            | Reserved                                              | 0x800E78<br>0x800E7A<br>0x800EFE |

| Configuration Memory Space | UDID                                                  | 0x800F00<br>0x800F08<br>0x800F0A |

| nory S                     | Reserved                                              | 0x800F7E                         |

| n Mer                      | User OTP Memory                                       | 0x800F80<br>0x800FFC             |

| Iratio                     | Reserved                                              | 0x801000                         |

| onfigu                     | Write Latches                                         | 0xF9FFFE<br>0xFA0000             |

| ŏ                          |                                                       | 0xFA0002<br>0xFA0004             |

|                            | Reserved                                              |                                  |

|                            | DEVID                                                 | 0xFEFFFE<br>0xFF0000             |

|                            | Reserved                                              | 0xFF0002<br>0xFF0004             |

| _                          |                                                       | 0xFFFFFE                         |

Note: Memory areas are not shown to scale.

| TABLE 4     | 4-6:  | OU                        | TPUT (                              | COMPAR   | RE 1 TH | ROUGH   | Ουτρι   |       | <b>IPARE</b> | 4 REGI       | Ster M       | AP     |          |          |          |          |          |               |

|-------------|-------|---------------------------|-------------------------------------|----------|---------|---------|---------|-------|--------------|--------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15                    | Bit 14                              | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8        | Bit 7        | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| OC1CON1     | 0900  | _                         | _                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | —            | ENFLTA       | —            | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD                     | FLTOUT                              | FLTTRIEN | OCINV   |         | —       | _     | OC32         | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |                           |                                     |          |         |         |         | 0     | utput Comp   | are 1 Seco   | ndary Regist | er     |          |          |          |          |          | xxxx          |

| OC1R        | 0906  |                           |                                     |          |         |         |         |       | Output       | Compare 1    | Register     |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |                           |                                     |          |         |         |         |       | Time         | r Value 1 Re | egister      |        |          |          |          |          |          | xxxx          |

| OC2CON1     | 090A  |                           | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 |       | —            | ENFLTA       |              | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2     | 090C  | FLTMD                     | FLTOUT                              | FLTTRIEN | OCINV   |         | —       |       | OC32         | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |                           | Output Compare 2 Secondary Register |          |         |         |         |       | xxxx         |              |              |        |          |          |          |          |          |               |

| OC2R        | 0910  | Output Compare 2 Register |                                     |          |         |         | xxxx    |       |              |              |              |        |          |          |          |          |          |               |

| OC2TMR      | 0912  |                           | Timer Value 2 Register              |          |         |         |         |       | xxxx         |              |              |        |          |          |          |          |          |               |

| OC3CON1     | 0914  |                           | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 |       | —            | ENFLTA       |              | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                     | FLTOUT                              | FLTTRIEN | OCINV   |         | —       |       | OC32         | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |                           |                                     |          |         |         |         | 0     | utput Comp   | are 3 Seco   | ndary Regist | er     |          |          |          |          |          | xxxx          |

| OC3R        | 091A  |                           |                                     |          |         |         |         |       | Output       | Compare 3    | Register     |        |          |          |          |          |          | xxxx          |

| OC3TMR      | 091C  |                           |                                     |          |         |         |         |       | Time         | r Value 3 Re | egister      |        |          |          |          |          |          | xxxx          |

| OC4CON1     | 091E  |                           | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 |       | —            | ENFLTA       |              | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                     | FLTOUT                              | FLTTRIEN | OCINV   |         | -       |       | OC32         | OCTRIG       | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |                           |                                     |          |         |         |         | 0     | utput Comp   | are 4 Seco   | ndary Regist | er     |          |          |          |          |          | xxxx          |

| OC4R        | 0924  |                           |                                     |          |         |         |         |       | Output       | Compare 4    | Register     |        |          |          |          |          |          | xxxx          |

| OC4TMR      | 0926  |                           |                                     |          |         |         |         |       | Time         | r Value 4 Re | egister      |        |          |          |          |          |          | xxxx          |

-

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-26: ANALOG COMPARATOR REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10      | Bit 9   | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|---------|---------|---------|-------------|---------|-------|--------|--------|--------|--------|---------|--------|--------|-------|---------------|

| CMP1CON     | 0540  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP1DAC     | 0542  | _      | —      | —       |         |         | CMREF<11:0> |         |       |        |        | 0000   |        |         |        |        |       |               |

| CMP2CON     | 0544  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP2DAC     | 0546  | -      | —      | _       | -       |         | CMREF<11:0> |         |       |        |        | 0000   |        |         |        |        |       |               |

| CMP3CON     | 0548  | CMPON  | _      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP3DAC     | 054A  | -      | _      | _       | _       |         |             |         |       |        | CMREF  | <11:0> |        |         |        |        |       | 0000          |

| CMP4CON     | 054C  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP4DAC     | 054E  | —      | —      | _       | _       |         | CMREF<11:0> |         |       |        |        | 0000   |        |         |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-27: JTAG INTERFACE REGISTER MAP

| SFR<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11       | Bit 10       | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|------|--------|--------|--------|--------|--------------|--------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| JDATAH      | 0FF0 | _      | _      | _      | —      |              | JDATAH<11:0> |       |       |       |       |       | xxxx  |       |       |       |       |               |

| JDATAL      | 0FF2 |        |        |        |        | JDATAL<15:0> |              |       |       |       |       | 0000  |       |       |       |       |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## **REGISTER 6-1:** RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ul><li>1 = Device has been in Idle mode</li><li>0 = Device has not been in Idle mode</li></ul>                         |

| bit 1 | BOR: Brown-out Reset Flag bit                                                                                           |

|       | <ul><li>1 = A Brown-out Reset has occurred</li><li>0 = A Brown-out Reset has not occurred</li></ul>                     |

| bit 0 | POR: Power-on Reset Flag bit                                                                                            |

|       | <ul><li>1 = A Power-on Reset has occurred</li><li>0 = A Power-on Reset has not occurred</li></ul>                       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

NOTES:

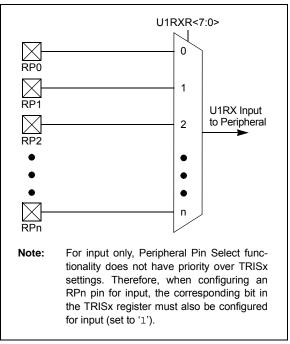

### 10.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-19). Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 10-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 10-2: REMAPPABLE INPUT FOR U1RX

### 10.4.4.1 Virtual Connections

The dsPIC33EPXXGS50X devices support six virtual RPn pins (RP176-RP181), which are identical in functionality to all other RPn pins, with the exception of pinouts. These six pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP176 and the PWM Fault input can be configured for RP176 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

| Function     | RPnR<5:0> | Output Name                                                 |

|--------------|-----------|-------------------------------------------------------------|

| Default PORT | 000000    | RPn tied to Default Pin                                     |

| U1TX         | 000001    | RPn tied to UART1 Transmit                                  |

| U1RTS        | 000010    | RPn tied to UART1 Request-to-Send                           |

| U2TX         | 000011    | RPn tied to UART2 Transmit                                  |

| U2RTS        | 000100    | RPn tied to UART2 Request-to-Send                           |

| SDO1         | 000101    | RPn tied to SPI1 Data Output                                |

| SCK1         | 000110    | RPn tied to SPI1 Clock Output                               |

| SS1          | 000111    | RPn tied to SPI1 Slave Select                               |

| SDO2         | 001000    | RPn tied to SPI2 Data Output                                |

| SCK2         | 001001    | RPn tied to SPI2 Clock Output                               |

| SS2          | 001010    | RPn tied to SPI2 Slave Select                               |

| OC1          | 010000    | RPn tied to Output Compare 1 Output                         |

| OC2          | 010001    | RPn tied to Output Compare 2 Output                         |

| OC3          | 010010    | RPn tied to Output Compare 3 Output                         |

| OC4          | 010011    | RPn tied to Output Compare 4 Output                         |

| ACMP1        | 011000    | RPn tied to Analog Comparator 1 Output                      |

| ACMP2        | 011001    | RPn tied to Analog Comparator 2 Output                      |

| ACMP3        | 011010    | RPn tied to Analog Comparator 3 Output                      |

| SYNCO1       | 101101    | RPn tied to PWM Primary Master Time Base Sync Output        |

| SYNCO2       | 101110    | RPn tied to PWM Secondary Master Time Base Sync Output      |

| REFCLKO      | 110001    | RPn tied to Reference Clock Output                          |

| ACMP4        | 110010    | RPn tied to Analog Comparator 4 Output                      |

| PWM4H        | 110011    | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM4L        | 110100    | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM5H        | 110101    | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

| PWM5L        | 110110    | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

### TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| R/W-0             | R/W-0                                                               | R/W-0                                                                                                             | R/W-0                                      | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

|-------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|------------------|-----------------|----------|

| SCK1INR7          | SCK1INR6                                                            | SCK1INR5                                                                                                          | SCK1INR4                                   | SCK1INR3         | SCK1INR2         | SCK1INR1        | SCK1INR0 |

| bit 15            |                                                                     |                                                                                                                   |                                            |                  |                  |                 | bit 8    |

|                   |                                                                     |                                                                                                                   |                                            |                  |                  |                 |          |

| R/W-0             | R/W-0                                                               | R/W-0                                                                                                             | R/W-0                                      | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

| SDI1R7            | SDI1R6                                                              | SDI1R5                                                                                                            | SDI1R4                                     | SDI1R3           | SDI1R2           | SDI1R1          | SDI1R0   |

| bit 7             |                                                                     |                                                                                                                   |                                            |                  |                  |                 | bit 0    |

| Legend:           |                                                                     |                                                                                                                   |                                            |                  |                  |                 |          |

| R = Readable      | bit                                                                 | W = Writable                                                                                                      | bit                                        | U = Unimpler     | nented bit, read | as '0'          |          |

| -n = Value at POR |                                                                     | '1' = Bit is set                                                                                                  |                                            | '0' = Bit is cle |                  | x = Bit is unkr | nown     |

| bit 7-0           | 10110100 =<br>00000001 =<br>00000000 =<br>SDI1R<7:0>:<br>10110101 = | Input tied to RF<br>Input tied to RF<br>Input tied to Vs<br>Assign SPI1 D<br>Input tied to RF<br>Input tied to RF | 2180<br>21<br>35<br>2ata Input (SD<br>2181 | 11) to the Corre | esponding RPn    | Pin bits        |          |

|                   |                                                                     | Input tied to RF<br>Input tied to Vs                                                                              |                                            |                  |                  |                 |          |

### REGISTER 10-12: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

### REGISTER 10-13: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

|         | U-0   |

|---------|-------|

| L 1 A F | —     |

| bit 15  | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SS1R7 | SS1R6 | SS1R5 | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 SS1R<7:0>: Assign SPI1 Slave Select (SS1) to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180 •

00000001 = Input tied to RP1 00000000 = Input tied to Vss

### REGISTER 15-22: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (x = 1 to 5) (CONTINUED)

| bit 7-3 | FLTSRC<4:0>: Fault Control Signal Source Select for PWMx Generator bits         1111 = Fault 31 (Default)         10001 = Reserved         10000 = Analog Comparator 4         01111 = Analog Comparator 3         01100 = Analog Comparator 2         01101 = Analog Comparator 1         01100 = Fault 12         01011 = Fault 11         01000 = Fault 12         01011 = Fault 10         01000 = Fault 8         00111 = Fault 7         00110 = Fault 6         00101 = Fault 3         00010 = Fault 4         00011 = Fault 11 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWMx Generator bit <sup>(1)</sup><br>1 = The selected Fault source is active-low<br>0 = The selected Fault source is active-high                                                                                                                                                                                                                                                                                                                                                                      |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWMx Generator bits<br>11 = Fault input is disabled<br>10 = Reserved<br>01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (cycle)<br>00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (latched condition)                                                                                                                                                                                                                                          |

Note 1: These bits should be changed only when PTEN = 0 (PTCON<15>).

### REGISTER 15-23: STRIGX: PWMx SECONDARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 5)<sup>(1)</sup>

| R/W-0                                                                                                                                                                                                             | R/W-0        | R/W-0            | R/W-0           | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|-----------------|-----------------------------------------|-----------------|----------|-------|--|--|

|                                                                                                                                                                                                                   |              |                  | STRGC           | MP<12:5>                                |                 |          |       |  |  |

| bit 15                                                                                                                                                                                                            |              |                  |                 |                                         |                 |          | bit 8 |  |  |

|                                                                                                                                                                                                                   |              |                  |                 |                                         |                 |          |       |  |  |

| R/W-0                                                                                                                                                                                                             | R/W-0        | R/W-0            | R/W-0           | R/W-0                                   | U-0             | U-0      | U-0   |  |  |

|                                                                                                                                                                                                                   |              | STRGCMP<4:0      | >               |                                         | —               | —        | —     |  |  |

| bit 7                                                                                                                                                                                                             |              |                  |                 |                                         |                 |          | bit 0 |  |  |

|                                                                                                                                                                                                                   |              |                  |                 |                                         |                 |          |       |  |  |

| Legend:                                                                                                                                                                                                           |              |                  |                 |                                         |                 |          |       |  |  |

| R = Readable                                                                                                                                                                                                      | e bit        | W = Writable     | bit             | U = Unimplem                            | ented bit, read | 1 as '0' |       |  |  |

| -n = Value at                                                                                                                                                                                                     | POR          | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |  |

| bit 15-3 <b>STRGCMP&lt;12:0&gt;:</b> Secondary Trigger Compare Value bits<br>When the secondary PWMx functions in the local time base, this register contains the compare values that can trigger the ADC module. |              |                  |                 |                                         |                 |          |       |  |  |

| bit 2-0                                                                                                                                                                                                           | Unimpleme    | nted: Read as '  | כ'              |                                         |                 |          |       |  |  |

| Note 1: S                                                                                                                                                                                                         | TRIGx cannot | generate the PV  | VM trigger inte | errupts.                                |                 |          |       |  |  |

### 20.3 Module Applications

This module provides a means for the SMPS dsPIC<sup>®</sup> DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator and an associated 12-bit DAC that provides a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- Generate an Interrupt

- Trigger an ADC Sample and Convert Process

- Truncate the PWMx Signal (current limit)

- Truncate the PWMx Period (current minimum)

- Disable the PWMx Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWMx output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

### 20.4 Digital-to-Analog Comparator (DAC)

Each analog comparator has a dedicated 12-bit DAC that is used to program the comparator threshold voltage via the CMPxDAC register. The DAC voltage reference source is selected using the EXTREF and RANGE bits in the CMPxCON register.

The EXTREF bit selects either the external voltage reference, EXTREFx, or an internal source as the voltage reference source. The EXTREFx input enables users to connect to a voltage reference that better suits their application. The RANGE bit enables AVDD as the voltage reference source for the DAC when an internal voltage reference is selected.

**Note:** EXTREF2 is not available on all devices.

Each DACx has an output enable bit, DACOE, in the CMPxCON register that enables the DACx reference voltage to be routed to an external output pin (DACOUTx). Refer to Figure 20-1 for connecting the DACx output voltage to the DACOUTx pins.

| Note 1: | Ensure that multiple DACOE bits are not |

|---------|-----------------------------------------|

|         | set in software. The output on the      |

|         | DACOUTx pin will be indeterminate if    |

|         | multiple comparators enable the DACx    |

|         | output.                                 |

2: DACOUT2 is not available on all devices.

### 20.5 Pulse Stretcher and Digital Logic

The analog comparator can respond to very fast transient signals. After the comparator output is given the desired polarity, the signal is passed to a pulse stretching circuit. The pulse stretching circuit has an asynchronous set function and a delay circuit that ensures the minimum pulse width is three system clock cycles wide to allow the attached circuitry to properly respond to a narrow pulse event.

The pulse stretcher circuit is followed by a digital filter. The digital filter is enabled via the FLTREN bit in the CMPxCON register. The digital filter operates with the clock specified via the FCLKSEL bit in the CMPxCON register. The comparator signal must be stable in a high or low state, for at least three of the selected clock cycles, for it to pass through the digital filter.

### TABLE 23-1: CONFIGURATION REGISTER MAP<sup>(3)</sup> (CONTINUED)

|                      | -•      |                                      |            | ••••=• |          |        | (          |        | ,      |       |       |       |       |          |         |         |                         |          |         |

|----------------------|---------|--------------------------------------|------------|--------|----------|--------|------------|--------|--------|-------|-------|-------|-------|----------|---------|---------|-------------------------|----------|---------|

| Name                 | Address | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-16 | Bit 15 | Bit 14   | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5    | Bit 4   | Bit 3   | Bit 2                   | Bit 1    | Bit 0   |

| FDEVOPT              | 002BAC  | 16                                   |            |        |          |        |            |        |        |       |       |       |       |          |         |         |                         |          |         |

|                      | 0057AC  | 32                                   | —          | _      | _        | _      | _          | _      | _      | —     | _     | _     | DBCC  | —        | ALTI2C2 | ALTI2C1 | Reserved <sup>(1)</sup> | _        | PWMLOCK |

|                      | 00AFAC  | 64                                   |            |        |          |        |            |        |        |       |       |       |       |          |         |         |                         |          |         |

| FALTREG              | 002BB0  | 16                                   |            |        |          |        |            |        |        |       |       |       |       |          |         |         |                         |          |         |

|                      | 0057B0  | 32                                   | _          | _      | _        | _      | _          | —      | _      | _     | —     | _     |       | CTXT2<2: | 0>      | _       | с                       | TXT1<2:0 | >       |

|                      | 00AFB0  | 64                                   |            |        |          |        |            |        |        |       |       |       |       |          |         |         |                         |          |         |

| FBTSEQ               | 002BFC  | 16                                   |            |        | •        | •      | •          |        | •      |       |       |       |       |          |         |         |                         |          |         |

|                      | 0057FC  | 32                                   |            | IBSE   | EQ<11:0> |        | BSEQ<11:0> |        |        |       |       |       |       |          |         |         |                         |          |         |

|                      | 00AFFC  | 64                                   | 1          |        |          |        |            |        |        |       |       |       |       |          |         |         |                         |          |         |

| FBOOT <sup>(4)</sup> | 801000  | _                                    | —          | _      | _        | _      |            | _      |        | —     | _     | _     | _     |          |         | _       | _                       | BTMC     | DE<1:0> |

Note 1: These bits are reserved and must be programmed as '1'.

2: This bit is reserved and must be programmed as '0'.

3: When operating in Dual Partition mode, each partition will have dedicated Configuration registers. On a device Reset, the configuration values of the Active Partition are read at start-up, but during a soft swap condition, the configuration settings of the newly Active Partition are ignored.

4: FBOOT resides in configuration memory space.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter is changed as a result of the instruction, or a PSV or table read is performed. In these cases, the execution takes multiple instruction cycles,

Slit6

Wb

Wd

Wdo

Wm,Wn

with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the "16-bit MCU and DSC Programmer's Reference Manual' (DS70157).

| Description                                                                   |

|-------------------------------------------------------------------------------|

| Means literal defined by "text"                                               |

| Means "content of text"                                                       |

| Means "the location addressed by text"                                        |

| Optional field or operation                                                   |

| a is selected from the set of values b, c, d                                  |

| Register bit field                                                            |

| Byte mode selection                                                           |

| Double-Word mode selection                                                    |

| Shadow register select                                                        |

| Word mode selection (default)                                                 |

| One of two accumulators {A, B}                                                |

| Accumulator write-back destination address register $\in$ {W13, [W13]+ = 2}   |

| 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$ |

| MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero          |

| Absolute address, label or expression (resolved by the linker)                |

| File register address ∈ {0x00000x1FFF}                                        |

| 1-bit unsigned literal $\in \{0,1\}$                                          |

| 4-bit unsigned literal $\in \{015\}$                                          |

| 5-bit unsigned literal $\in \{031\}$                                          |

| 8-bit unsigned literal $\in \{0255\}$                                         |

| 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode    |

| 14-bit unsigned literal $\in \{016384\}$                                      |

| 16-bit unsigned literal $\in$ {065535}                                        |

| 23-bit unsigned literal $\in$ {08388608}; LSb must be '0'                     |

| Field does not require an entry, can be blank                                 |

| DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate   |

| Program Counter                                                               |

| 10-bit signed literal $\in$ {-512511}                                         |

| 16-bit signed literal ∈ {-3276832767}                                         |

|                                                                               |

Destination W register ∈ { Wd, [Wd], [Wd++], [Wd--], [++Wd], [--Wd] }

{ Wnd, [Wnd], [Wnd++], [Wnd--], [++Wnd], [--Wnd], [Wnd+Wb] }

Dividend, Divisor Working register pair (direct addressing)

6-bit signed literal  $\in$  {-16...16}

Base W register  $\in$  {W0...W15}

Destination W register  $\in$

#### **TABLE 24-1:** SYMBOLS USED IN OPCODE DESCRIPTIONS

### 25.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 25.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 25.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 25.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

### TABLE 26-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT       | ERISTICS                     |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                  |      |  |  |  |  |

|------------------|------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|--|--|--|--|

| Parameter<br>No. | Тур.                         | Max. | Units                                                                                                                                                                                                                                                                                   | Units Conditions |      |  |  |  |  |

| Power-Down       | Current (IPD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |                  |      |  |  |  |  |

| DC60d            | 12                           | 100  | μA                                                                                                                                                                                                                                                                                      | -40°C            |      |  |  |  |  |

| DC60a            | 18                           | 100  | μA                                                                                                                                                                                                                                                                                      | +25°C            | 3.3V |  |  |  |  |

| DC60b            | 130                          | 400  | μΑ                                                                                                                                                                                                                                                                                      | +85°C            | 3.3V |  |  |  |  |

| DC60c            | 500                          | 1100 | μΑ                                                                                                                                                                                                                                                                                      | +125°C           |      |  |  |  |  |

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

### TABLE 26-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT (△IwDT)<sup>(1)</sup>

| DC CHARACTER            | RISTICS |    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |       |  |  |  |

|-------------------------|---------|----|-------------------------------------------------------|------------|-------|--|--|--|

| Parameter No. Typ. Max. |         |    | Units                                                 | Conditions |       |  |  |  |

| DC61d                   | 13      | 50 | μΑ                                                    | -40°C      |       |  |  |  |

| DC61a                   | 19      | 80 | μA                                                    | +25°C      | 2.21/ |  |  |  |

| DC61b                   | 12      | —  | μA                                                    | +85°C      | 3.3V  |  |  |  |

| DC61c                   | 13      | —  | μA                                                    | +125°C     |       |  |  |  |

**Note 1:** The  $\triangle$ IWDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

| TABLE 26-14: | DC CHARACTERISTICS: PROGRAM MEMORY |

|--------------|------------------------------------|

|--------------|------------------------------------|

| DC CHARACTERISTICS |        |                                                     | (unless |                     | vise state | pnditions: 3.0V to 3.6V<br>ed)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                                |  |

|--------------------|--------|-----------------------------------------------------|---------|---------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                      | Min.    | Тур. <sup>(1)</sup> | Max.       | Units                                                                                                                                           | Conditions                                                     |  |

|                    |        | Program Flash Memory                                |         |                     |            |                                                                                                                                                 |                                                                |  |

| D130               | Eр     | Cell Endurance                                      | 10,000  | _                   | _          | E/W                                                                                                                                             | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                                        | 3.0     | —                   | 3.6        | V                                                                                                                                               |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write                            | 3.0     | —                   | 3.6        | V                                                                                                                                               |                                                                |  |

| D134               | TRETD  | Characteristic Retention                            | 20      | —                   | —          | Year                                                                                                                                            | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | —       | 10                  | —          | mA                                                                                                                                              |                                                                |  |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up       | —       | —                   | 150        | mA                                                                                                                                              |                                                                |  |

| D137a              | TPE    | Page Erase Time                                     | 19.7    | —                   | 20.1       | ms                                                                                                                                              | TPE = 146893 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>         |  |

| D137b              | TPE    | Page Erase Time                                     | 19.5    | —                   | 20.3       | ms                                                                                                                                              | TPE = 146893 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>        |  |

| D138a              | Tww    | Word Write Cycle Time                               | 46.5    | —                   | 47.3       | μs                                                                                                                                              | Tww = 346 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>            |  |

| D138b              | Tww    | Word Write Cycle Time                               | 46.0    | -                   | 47.9       | μs                                                                                                                                              | Tww = 346 FRC cycles,<br>TA = +125°C <b>(Note 3)</b>           |  |

| D139a              | Trw    | Row Write Time                                      | 667     | -                   | 679        | μs                                                                                                                                              | Trw = 4965 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>           |  |

| D139b              | Trw    | Row Write Time                                      | 660     | _                   | 687        | μs                                                                                                                                              | Trw = 4965 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>          |  |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 26-20) and the value of the FRC Oscillator Tuning register (see Register 8-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

### 26.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EPXXGS50X family AC characteristics and timing parameters.

### TABLE 26-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)               |

|--------------------|----------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial            |

|                    | $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended                                   |

|                    | Operating voltage VDD range as described in <b>Section 26.1 "DC Characteristics</b> ". |

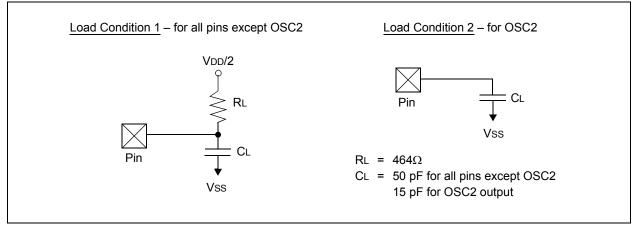

### FIGURE 26-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 26-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   | pF    | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Cio    | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            |      | _    | 400  | pF    | In I <sup>2</sup> C mode                                            |

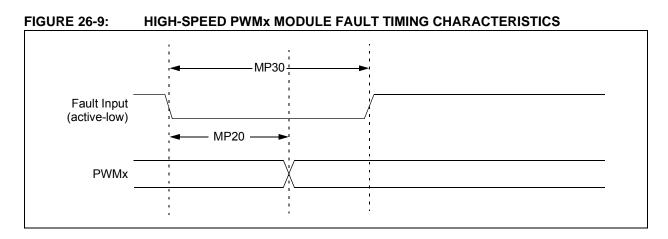

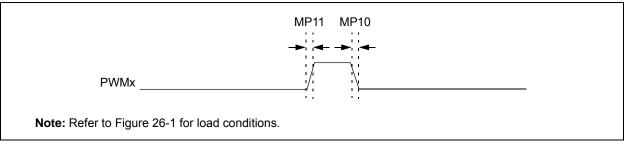

### FIGURE 26-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

### TABLE 26-30: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

|              |        |                                     | (unless | rd Opera<br>otherwi<br>ng tempe | se stateo<br>rature - | <b>i)</b><br>-40°C ≤ T | <b>3.0V to 3.6V</b><br>$A \le +85^{\circ}C$ for Industrial<br>$A \le +125^{\circ}C$ for Extended |

|--------------|--------|-------------------------------------|---------|---------------------------------|-----------------------|------------------------|--------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>       | Min.    | Тур.                            | Max.                  | Units                  | Conditions                                                                                       |

| MP10         | TFPWM  | PWMx Output Fall Time               | —       | _                               | —                     | ns                     | See Parameter DO32                                                                               |

| MP11         | TRPWM  | PWMx Output Rise Time               | _       | _                               | _                     | ns                     | See Parameter DO31                                                                               |

| MP20         | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _       | _                               | 15                    | ns                     |                                                                                                  |

| MP30         | Tfh    | Fault Input Pulse Width             | 15      | —                               | —                     | ns                     |                                                                                                  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

### TABLE 26-44: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

| AC CH        | ARACTE |                  | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |         |         |                                       |  |

|--------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|---------|---------------------------------------|--|

| Param<br>No. | Symbol | Characteristics  | Min.                                                                                                                                                                                                                                                                         | Тур. <sup>(1)</sup> | Max.    | Units   | Conditions                            |  |

|              |        |                  |                                                                                                                                                                                                                                                                              | Clo                 | ck Para | meters  |                                       |  |

| AD50         | TAD    | ADC Clock Period | 14.28                                                                                                                                                                                                                                                                        |                     | —       | ns      |                                       |  |

|              |        |                  |                                                                                                                                                                                                                                                                              | Thr                 | oughpu  | ut Rate |                                       |  |

| AD51         | Fтр    | SH0-SH3          | —                                                                                                                                                                                                                                                                            |                     | 3.25    |         | 70 MHz ADC clock, 12 bits, no pending |  |

|              |        | SH4              | _                                                                                                                                                                                                                                                                            |                     | 3.25    | Msps    | conversion at time of trigger         |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is ensured, but not characterized.

#### TABLE 26-45: HIGH-SPEED ANALOG COMPARATOR MODULE SPECIFICATIONS

| AC/DC CHARACTERISTICS <sup>(2)</sup> |        |                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                             |  |

|--------------------------------------|--------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.                         | Symbol | Characteristic                                    | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Comments                                                                                                                    |  |

| CM10                                 | VIOFF  | Input Offset Voltage                              | -35                                                                                                                                                                                                                                                                                     | ±5   | +35  | mV    |                                                                                                                             |  |

| CM11                                 | VICM   | Input Common-Mode<br>Voltage Range <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                       | —    | AVDD | V     |                                                                                                                             |  |

| CM13                                 | CMRR   | Common-Mode<br>Rejection Ratio                    | 60                                                                                                                                                                                                                                                                                      | —    | _    | dB    |                                                                                                                             |  |

| CM14                                 | TRESP  | Large Signal Response                             | _                                                                                                                                                                                                                                                                                       | 15   | _    | ns    | V+ input step of 100 mV while<br>V- input is held at AVDD/2. Delay<br>measured from analog input pin to<br>PWMx output pin. |  |

| CM15                                 | VHYST  | Input Hysteresis                                  | 5                                                                                                                                                                                                                                                                                       | 10   | 20   | mV    | Depends on HYSSEL<1:0>                                                                                                      |  |

| CM16                                 | TON    | Comparator Enabled to Valid Output                | _                                                                                                                                                                                                                                                                                       | —    | 1    | μs    |                                                                                                                             |  |

Note 1: These parameters are for design guidance only and are not tested in manufacturing.

2: The comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

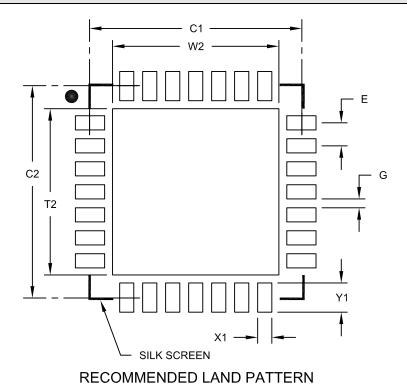

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |  |  |

|----------------------------|-------------|------|----------|------|--|--|

| Dimensio                   | MIN         | NOM  | MAX      |      |  |  |

| Contact Pitch              | E           |      | 0.65 BSC |      |  |  |

| Optional Center Pad Width  | W2          |      |          | 4.70 |  |  |

| Optional Center Pad Length | T2          |      |          | 4.70 |  |  |

| Contact Pad Spacing        | C1          |      | 6.00     |      |  |  |

| Contact Pad Spacing        | C2          |      | 6.00     |      |  |  |

| Contact Pad Width (X28)    | X1          |      |          | 0.40 |  |  |

| Contact Pad Length (X28)   | Y1          |      |          | 0.85 |  |  |

| Distance Between Pads      | G           | 0.25 |          |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A