#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

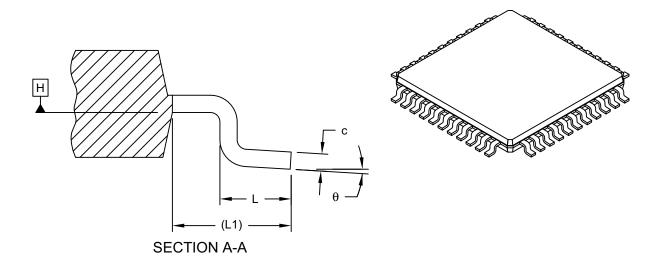

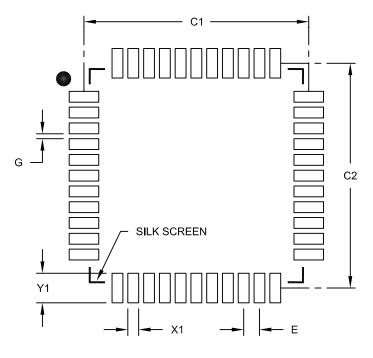

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXGS50X Digital Signal Controller (DSC) devices.

dsPIC33EPXXGS50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

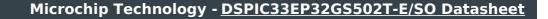

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXGS50X FAMILY BLOCK DIAGRAM

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2   | SFA: Stack Frame Active Status bit                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG</li> <li>0 = Stack frame is not active; W14 and W15 address the base Data Space</li> </ul> |

| bit 1   | RND: Rounding Mode Select bit                                                                                                                                                             |

|         | <ul><li>1 = Biased (conventional) rounding is enabled</li><li>0 = Unbiased (convergent) rounding is enabled</li></ul>                                                                     |

| bit 0   | IF: Integer or Fractional Multiplier Mode Select bit                                                                                                                                      |

|         | <ul> <li>1 = Integer mode is enabled for DSP multiply</li> <li>0 = Fractional mode is enabled for DSP multiply</li> </ul>                                                                 |

| Note 1: | This bit is always read as '0'.                                                                                                                                                           |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 3-3: CTXTSTAT: CPU W REGISTER CONTEXT STATUS REGISTER

| U-0             | U-0                                                                       | U-0          | U-0 | U-0          | R-0              | R-0    | R-0    |

|-----------------|---------------------------------------------------------------------------|--------------|-----|--------------|------------------|--------|--------|

| —               | —                                                                         | —            | —   | —            | CCTXI2           | CCTXI1 | CCTXI0 |

| bit 15          |                                                                           | •            |     |              |                  |        | bit 8  |

|                 |                                                                           |              |     |              |                  |        |        |

| U-0             | U-0                                                                       | U-0          | U-0 | U-0          | R-0              | R-0    | R-0    |

|                 | —                                                                         | —            | _   | —            | MCTXI2           | MCTXI1 | MCTXI0 |

| bit 7           |                                                                           |              |     |              |                  |        | bit 0  |

|                 |                                                                           |              |     |              |                  |        |        |

| Legend:         |                                                                           |              |     |              |                  |        |        |

| R = Readable I  | bit                                                                       | W = Writable | bit | U = Unimpler | nented bit, read | as '0' |        |

| -n = Value at P | -n = Value at POR (1' = Bit is set 0' = Bit is cleared x = Bit is unknown |              |     |              |                  |        |        |

| bit 15-11 | Unimplemented: Read as '0'                                                 |

|-----------|----------------------------------------------------------------------------|

| bit 10-8  | CCTXI<2:0>: Current (W Register) Context Identifier bits                   |

|           | 111 = Reserved                                                             |

|           | •                                                                          |

|           | •                                                                          |

|           | •                                                                          |

|           | 011 = Reserved                                                             |

|           | 010 = Alternate Working Register Set 2 is currently in use                 |

|           | 001 = Alternate Working Register Set 1 is currently in use                 |

|           | 000 = Default register set is currently in use                             |

| bit 7-3   | Unimplemented: Read as '0'                                                 |

| bit 2-0   | MCTXI<2:0>: Manual (W Register) Context Identifier bits                    |

|           | 111 = Reserved                                                             |

|           | •                                                                          |

|           | •                                                                          |

|           | •                                                                          |

|           | 011 = Reserved                                                             |

|           | 010 = Alternate Working Register Set 2 was most recently manually selected |

|           | 001 = Alternate Working Register Set 1 was most recently manually selected |

|           | 000 = Default register set was most recently manually selected             |

#### TABLE 4-26: ANALOG COMPARATOR REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10      | Bit 9   | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|---------|---------|---------|-------------|---------|-------|--------|--------|--------|--------|---------|--------|--------|-------|---------------|

| CMP1CON     | 0540  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP1DAC     | 0542  | _      | —      | —       |         |         | CMREF<11:0> |         |       |        |        |        | 0000   |         |        |        |       |               |

| CMP2CON     | 0544  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP2DAC     | 0546  | -      | —      | _       | -       |         |             |         |       |        | CMREF  | <11:0> |        |         |        |        |       | 0000          |

| CMP3CON     | 0548  | CMPON  | _      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP3DAC     | 054A  | -      | _      | _       | _       |         |             |         |       |        | CMREF  | <11:0> |        |         |        |        |       | 0000          |

| CMP4CON     | 054C  | CMPON  | —      | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN      | FCLKSEL | DACOE | INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT | ALTINP | CMPPOL | RANGE | 0000          |

| CMP4DAC     | 054E  | —      | —      | _       | _       |         | CMREF<11:0> |         |       |        |        |        | 0000   |         |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-27: JTAG INTERFACE REGISTER MAP

| SFR<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10       | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|------|--------|--------|--------|--------|--------|--------------|-------|-------|-------|-------|---------|-------|-------|-------|-------|-------|---------------|

| JDATAH      | 0FF0 | _      | _      | _      | —      |        |              |       |       |       | JDATA | H<11:0> |       |       |       |       |       | xxxx          |

| JDATAL      | 0FF2 |        |        |        |        |        | JDATAL<15:0> |       |       |       |       |         |       | 0000  |       |       |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-------|-------|-------|-----|-----|-------|

| VAR    | —   | US1   | US0   | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |       |       |       |     |     | bit 8 |

|        |     |       |       |       |     |     |       |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-----|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7 |       |       |        |                     |     |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

- 1 = Variable exception processing is enabled

- 0 = Fixed exception processing is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0          | U-0          | U-0                | U-0              | U-0              | U-0              | U-0    | R/W-0 |

|--------------|--------------|--------------------|------------------|------------------|------------------|--------|-------|

| _            | —            | —                  | —                | _                | —                | —      | NAE   |

| bit 15       |              |                    |                  |                  |                  |        | bit 8 |

|              |              |                    |                  |                  |                  |        |       |

| U-0          | U-0          | U-0                | R/W-0            | U-0              | U-0              | U-0    | R/W-0 |

| —            | —            |                    | DOOVR            | —                |                  |        | APLL  |

| bit 7        |              |                    |                  |                  |                  |        | bit 0 |

|              |              |                    |                  |                  |                  |        |       |

| Legend:      |              |                    |                  |                  |                  |        |       |

| R = Readal   | ole bit      | W = Writable       | bit              | U = Unimple      | mented bit, read | as '0' |       |

| -n = Value a | at POR       | '1' = Bit is se    | t                | '0' = Bit is cle | x = Bit is unkr  | nown   |       |

|              |              |                    |                  |                  |                  |        |       |

| bit 15-9     | Unimplemer   | nted: Read as      | '0'              |                  |                  |        |       |

| bit 8        | NAE: NVM A   | ddress Error S     | Soft Trap Status | s bit            |                  |        |       |

|              |              |                    | trap has occur   |                  |                  |        |       |

|              |              |                    | trap has not o   | ccurred          |                  |        |       |

| bit 7-5      | Unimplemer   | nted: Read as      | '0'              |                  |                  |        |       |

| bit 4        | DOOVR: DO    | Stack Overflov     | v Soft Trap Sta  | tus bit          |                  |        |       |

|              | 1 = DO stack | overflow soft t    | rap has occurre  | ed               |                  |        |       |

|              | 0 = DO stack | overflow soft t    | rap has not oc   | curred           |                  |        |       |

| bit 3-1      | Unimplemer   | nted: Read as      | '0'              |                  |                  |        |       |

| bit 0        | APLL: Auxili | ary PLL Loss o     | of Lock Soft Tra | ap Status bit    |                  |        |       |

|              | 1 = APLL loc | k soft trap has    | occurred         |                  |                  |        |       |

|              |              | le a aft trans has | wet easy word    |                  |                  |        |       |

0 = APLL lock soft trap has not occurred

#### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0          | U-0          | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|--------------|------------------|----------------|------------------|------------------|-----------------|-------|

| _            | —            | —                | —              | —                | —                | —               | —     |

| bit 15       |              |                  |                |                  |                  |                 | bit 8 |

|              |              |                  |                |                  |                  |                 |       |

| U-0          | U-0          | U-0              | U-0            | U-0              | U-0              | U-0             | R/W-0 |

| _            | —            | —                | —              | —                | —                | —               | SGHT  |

| bit 7        |              | •                |                |                  |                  | •               | bit 0 |

|              |              |                  |                |                  |                  |                 |       |

| Legend:      |              |                  |                |                  |                  |                 |       |

| R = Readab   | le bit       | W = Writable     | bit            | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value a | t POR        | '1' = Bit is set | t              | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

|              |              |                  |                |                  |                  |                 |       |

| bit 15-1     | Unimplemen   | ted: Read as     | '0'            |                  |                  |                 |       |

| bit 0        | SGHT: Softwa | are Generated    | Hard Trap Sta  | tus bit          |                  |                 |       |

|              | 1 = Software | generated har    | d trap has occ | urred            |                  |                 |       |

|              | 0 = Software | generated har    | d trap has not | occurred         |                  |                 |       |

|              |              |                  |                |                  |                  |                 |       |

|              |              |                  |                |                  |                  |                 |       |

#### REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

bit 4-0

**PLLPRE<4:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler) 11111 = Input divided by 33

•

00001 = Input divided by 3

00000 = Input divided by 2 (default)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- **2:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0          | U-0           | U-0              | U-0              | U-0              | U-0              | U-0             | R/W-0   |

|--------------|---------------|------------------|------------------|------------------|------------------|-----------------|---------|

| _            | —             | _                | —                | —                | —                | _               | PLLDIV8 |

| bit 15       |               |                  |                  |                  |                  |                 | bit 8   |

|              |               |                  |                  |                  |                  |                 |         |

| R/W-0        | R/W-0         | R/W-1            | R/W-1            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|              |               |                  | PLLDI            | V<7:0>           |                  |                 |         |

| bit 7        |               |                  |                  |                  |                  |                 | bit 0   |

|              |               |                  |                  |                  |                  |                 |         |

| Legend:      |               |                  |                  |                  |                  |                 |         |

| R = Reada    | ble bit       | W = Writable     | bit              | U = Unimplen     | nented bit, read | d as '0'        |         |

| -n = Value a | at POR        | '1' = Bit is set |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|              |               |                  |                  |                  |                  |                 |         |

| bit 15-9     | Unimplemen    | ted: Read as '   | )'               |                  |                  |                 |         |

| bit 8-0      | PLLDIV<8:0>   | -: PLL Feedbac   | k Divisor bits ( | also denoted a   | is 'M', PLL mul  | tiplier)        |         |

|              | 111111111     | = 513            |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | 000110000=    | = 50 (default)   |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | •             |                  |                  |                  |                  |                 |         |

|              | • 000000010 = | = 4              |                  |                  |                  |                 |         |

|              | 00000010-     | <b>– –</b>       |                  |                  |                  |                 |         |

#### REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

000000001 = 3 000000000 = 2

#### REGISTER 8-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

|                                                                                                |                          |                 |                        |                | -               |                    |       |

|------------------------------------------------------------------------------------------------|--------------------------|-----------------|------------------------|----------------|-----------------|--------------------|-------|

| U-0                                                                                            | U-0                      | U-0             | U-0                    | U-0            | U-0             | U-0                | U-0   |

| —                                                                                              | —                        | —               | _                      | —              | —               | —                  | _     |

| bit 15                                                                                         |                          |                 |                        |                |                 |                    | bit 8 |

|                                                                                                |                          |                 |                        |                |                 |                    |       |

| U-0                                                                                            | U-0                      | R/W-0           | R/W-0                  | R/W-0          | R/W-0           | R/W-0              | R/W-0 |

|                                                                                                |                          |                 |                        | TUN            | <5:0>           |                    |       |

| bit 7                                                                                          |                          |                 |                        |                |                 |                    | bit 0 |

|                                                                                                |                          |                 |                        |                |                 |                    |       |

| Legend:                                                                                        |                          |                 |                        |                |                 |                    |       |

| R = Readable bit W = Writable bit                                                              |                          |                 |                        | U = Unimplem   | nented bit, rea | d as '0'           |       |

| -n = Value at POR '1' = Bit is set                                                             |                          |                 | '0' = Bit is cleared x |                | x = Bit is unkr | x = Bit is unknown |       |

|                                                                                                |                          |                 |                        |                |                 |                    |       |

| bit 15-6                                                                                       | Unimplemen               | ted: Read as 'd | )'                     |                |                 |                    |       |

| bit 5-0                                                                                        | <b>TUN&lt;5:0&gt;:</b> F | RC Oscillator T | uning bits             |                |                 |                    |       |

|                                                                                                |                          | aximum frequen  |                        |                | 7 MHz)          |                    |       |

|                                                                                                | 011110 = Ce              | enter frequency | + 1.41% (7.47          | '4 MHz)        |                 |                    |       |

|                                                                                                | •                        |                 |                        |                |                 |                    |       |

|                                                                                                | •                        |                 |                        |                |                 |                    |       |

|                                                                                                |                          | enter frequency | •                      | ,              |                 |                    |       |

| 000000 = Center frequency (7.37 MHz nominal)<br>111111 = Center frequency – 0.047% (7.367 MHz) |                          |                 |                        |                |                 |                    |       |

|                                                                                                | •                        | enter frequency | - 0.047% (7.3          | o7 MHZ)        |                 |                    |       |

|                                                                                                | •                        |                 |                        |                |                 |                    |       |

|                                                                                                | •                        |                 |                        |                |                 |                    |       |

|                                                                                                |                          | enter frequency | •                      | ,              | <b>A</b> 11 \   |                    |       |

|                                                                                                | 100000 = MII             | nimum frequend  | cy deviation of        | -1.5% (7.259 N | /IHZ)           |                    |       |

|                                                                                                |                          |                 |                        |                |                 |                    |       |

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

| Function     | RPnR<5:0> | Output Name                                                 |

|--------------|-----------|-------------------------------------------------------------|

| Default PORT | 000000    | RPn tied to Default Pin                                     |

| U1TX         | 000001    | RPn tied to UART1 Transmit                                  |

| U1RTS        | 000010    | RPn tied to UART1 Request-to-Send                           |

| U2TX         | 000011    | RPn tied to UART2 Transmit                                  |

| U2RTS        | 000100    | RPn tied to UART2 Request-to-Send                           |

| SDO1         | 000101    | RPn tied to SPI1 Data Output                                |

| SCK1         | 000110    | RPn tied to SPI1 Clock Output                               |

| SS1          | 000111    | RPn tied to SPI1 Slave Select                               |

| SDO2         | 001000    | RPn tied to SPI2 Data Output                                |

| SCK2         | 001001    | RPn tied to SPI2 Clock Output                               |

| SS2          | 001010    | RPn tied to SPI2 Slave Select                               |

| OC1          | 010000    | RPn tied to Output Compare 1 Output                         |

| OC2          | 010001    | RPn tied to Output Compare 2 Output                         |

| OC3          | 010010    | RPn tied to Output Compare 3 Output                         |

| OC4          | 010011    | RPn tied to Output Compare 4 Output                         |

| ACMP1        | 011000    | RPn tied to Analog Comparator 1 Output                      |

| ACMP2        | 011001    | RPn tied to Analog Comparator 2 Output                      |

| ACMP3        | 011010    | RPn tied to Analog Comparator 3 Output                      |

| SYNCO1       | 101101    | RPn tied to PWM Primary Master Time Base Sync Output        |

| SYNCO2       | 101110    | RPn tied to PWM Secondary Master Time Base Sync Output      |

| REFCLKO      | 110001    | RPn tied to Reference Clock Output                          |

| ACMP4        | 110010    | RPn tied to Analog Comparator 4 Output                      |

| PWM4H        | 110011    | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM4L        | 110100    | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM5H        | 110101    | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

| PWM5L        | 110110    | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

#### TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

#### REGISTER 10-14: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0                             | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0                    | R/W-0            | R/W-0           | R/W-0              |  |

|-----------------------------------|------------------------------------|------------------------------------------------------------------------------|--------------|--------------------------|------------------|-----------------|--------------------|--|

| SCK2INR7                          | SCK2INR6                           | SCK2INR5                                                                     | SCK2INR4     | SCK2INR3                 | SCK2INR2         | SCK2INR1        | SCK2INR0           |  |

| bit 15                            |                                    |                                                                              |              |                          |                  |                 | bit 8              |  |

| R/W-0                             | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0                    | R/W-0            | R/W-0           | R/W-0              |  |

| SDI2R7                            | SDI2R6                             | SDI2R5                                                                       | SDI2R4       | SDI2R3                   | SDI2R2           | SDI2R1          | SDI2R0             |  |

| bit 7                             |                                    |                                                                              |              |                          |                  |                 | bit (              |  |

| Legend:                           |                                    |                                                                              |              |                          |                  |                 |                    |  |

| R = Readable                      | bit                                | W = Writable                                                                 | bit          | U = Unimpler             | nented bit, read | l as '0'        |                    |  |

| -n = Value at POR '1' = Bit is se |                                    | '1' = Bit is set                                                             |              | '0' = Bit is cleared x = |                  | x = Bit is unkr | x = Bit is unknown |  |

|                                   | 10110100 =<br>•<br>•<br>00000001 = | Input tied to Rf<br>Input tied to Rf<br>Input tied to Rf<br>Input tied to Vs | 2180<br>21   |                          |                  |                 |                    |  |

| bit 7-0                           | 10110101 =                         | Input tied to RF<br>Input tied to RF                                         | 2181<br>2180 | 12) to the Corre         | esponding RPn    | Pin bits        |                    |  |

#### REGISTER 10-20: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0                               | R/W-0                              | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0  |

|---------------|-----------------------------------|------------------------------------|--------|-----------------------------------------|------------------|----------|--------|

| _             | —                                 | RP33R5                             | RP33R4 | RP33R3                                  | RP33R2           | RP33R1   | RP33R0 |

| bit 15        |                                   |                                    |        |                                         |                  |          | bit 8  |

|               |                                   |                                    |        |                                         |                  |          |        |

| U-0           | U-0                               | R/W-0                              | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0  |

| _             | —                                 | RP32R5                             | RP32R4 | RP32R3                                  | RP32R2           | RP32R1   | RP32R0 |

| bit 7         |                                   |                                    |        |                                         |                  |          | bit 0  |

|               |                                   |                                    |        |                                         |                  |          |        |

| Legend:       |                                   |                                    |        |                                         |                  |          |        |

| R = Readabl   | R = Readable bit W = Writable bit |                                    | bit    | U = Unimpler                            | mented bit, read | 1 as '0' |        |

| -n = Value at | POR                               | '1' = Bit is set                   |        | '0' = Bit is cleared x = Bit is unknown |                  |          |        |

|               |                                   |                                    |        |                                         |                  |          |        |

| bit 15-14     | Unimplemen                        | ted: Read as '                     | 0'     |                                         |                  |          |        |

| bit 13-8      |                                   | : Peripheral Ou<br>-2 for peripher | •      | •                                       | RP33 Output F    | Pin bits |        |

| bit 7-6       | Unimplemen                        | ted: Read as '                     | 0'     |                                         |                  |          |        |

bit 5-0 **RP32R<5:0>:** Peripheral Output Function is Assigned to RP32 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-21: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0                                | U-0                               | R/W-0                | R/W-0         | R/W-0                              | R/W-0              | R/W-0    | R/W-0  |  |

|------------------------------------|-----------------------------------|----------------------|---------------|------------------------------------|--------------------|----------|--------|--|

| _                                  | —                                 | RP35R5               | RP35R4        | RP35R3                             | RP35R2             | RP35R1   | RP35R0 |  |

| bit 15                             |                                   | •                    |               |                                    |                    | •        | bit 8  |  |

|                                    |                                   |                      |               |                                    |                    |          |        |  |

| U-0                                | U-0                               | R/W-0                | R/W-0         | R/W-0                              | R/W-0              | R/W-0    | R/W-0  |  |

| —                                  | —                                 | RP34R5               | RP34R4        | RP34R3                             | RP34R2             | RP34R1   | RP34R0 |  |

| bit 7                              |                                   | •                    |               |                                    |                    | •        | bit 0  |  |

|                                    |                                   |                      |               |                                    |                    |          |        |  |

| Legend:                            |                                   |                      |               |                                    |                    |          |        |  |

| R = Readable                       | R = Readable bit W = Writable bit |                      | bit           | U = Unimplemented bit, read as '0' |                    |          |        |  |

| -n = Value at POR '1' = Bit is set |                                   | '0' = Bit is cleared |               | ared                               | x = Bit is unknown |          |        |  |

|                                    |                                   |                      |               |                                    |                    |          |        |  |

| bit 15-14                          | Unimplemen                        | ted: Read as '       | כ'            |                                    |                    |          |        |  |

| bit 13-8                           | RP35R<5:0>:                       | Peripheral Ou        | tput Function | is Assigned to                     | RP35 Output F      | rin bits |        |  |

(see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP34R<5:0>:** Peripheral Output Function is Assigned to RP34 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 5)

|              | (X = 1                                                                                                                                                                                                                | 10 5)                                                                                                                                                                                           |                    |                                        |                   |                 |        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------|-------------------|-----------------|--------|

| R/W-0        | R/W-0                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                           | R/W-0              | R/W-0                                  | R/W-0             | U-0             | U-0    |

| PHR          | PHF                                                                                                                                                                                                                   | PLR                                                                                                                                                                                             | PLF                | FLTLEBEN                               | CLLEBEN           | —               |        |

| bit 15       |                                                                                                                                                                                                                       |                                                                                                                                                                                                 |                    |                                        |                   |                 | bit 8  |

|              |                                                                                                                                                                                                                       |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

| U-0          | U-0                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                           | R/W-0              | R/W-0                                  | R/W-0             | R/W-0           | R/W-0  |

|              |                                                                                                                                                                                                                       | BCH <sup>(1)</sup>                                                                                                                                                                              | BCL <sup>(1)</sup> | BPHH                                   | BPHL              | BPLH            | BPLL   |

| bit 7        |                                                                                                                                                                                                                       |                                                                                                                                                                                                 |                    |                                        |                   |                 | bit 0  |

| Legend:      |                                                                                                                                                                                                                       |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

| R = Readat   | ole bit                                                                                                                                                                                                               | W = Writable b                                                                                                                                                                                  | oit                | U = Unimpler                           | nented bit, read  | as '0'          |        |

| -n = Value a | at POR                                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                                                                |                    | '0' = Bit is clea                      |                   | x = Bit is unkr | nown   |

| bit 15       |                                                                                                                                                                                                                       | H Rising Edge T                                                                                                                                                                                 | riggor Epoble      | 2 bit                                  |                   |                 |        |

| bit 15       | 1 = Rising edg                                                                                                                                                                                                        | ge of PWMxH v                                                                                                                                                                                   | vill trigger the   | Leading-Edge E                         | •                 | PL              |        |

| bit 14       | -                                                                                                                                                                                                                     |                                                                                                                                                                                                 | -                  |                                        |                   |                 |        |

|              | PHF: PWMxH Falling Edge Trigger Enable bit<br>1 = Falling edge of PWMxH will trigger the Leading-Edge Blanking counter                                                                                                |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

|              | 0 = Leading-Edge Blanking ignores the falling edge of PWMxH                                                                                                                                                           |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

| bit 13       | PLR: PWMxL Rising Edge Trigger Enable bit                                                                                                                                                                             |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

|              | 1 = Rising edge of PWMxL will trigger the Leading-Edge Blanking counter                                                                                                                                               |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

| bit 12       | 0 = Leading-Edge Blanking ignores the rising edge of PWMxL                                                                                                                                                            |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

|              | <ul> <li>PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger the Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores the falling edge of PWMxL</li> </ul> |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

| bit 11       | FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit                                                                                                                                                                |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

|              | <ul> <li>1 = Leading-Edge Blanking is applied to the selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to the selected Fault input</li> </ul>                                                    |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

| bit 10       | CLLEBEN: C                                                                                                                                                                                                            | urrent-Limit Lea                                                                                                                                                                                | ading-Edge B       | lanking Enable I                       | bit               |                 |        |

|              |                                                                                                                                                                                                                       |                                                                                                                                                                                                 |                    | ne selected curre<br>to the selected o |                   | ut              |        |

| bit 9-6      | Unimplemen                                                                                                                                                                                                            | ted: Read as '0                                                                                                                                                                                 | 2                  |                                        |                   |                 |        |

| bit 5        | BCH: Blankin                                                                                                                                                                                                          | g in Selected B                                                                                                                                                                                 | lanking Signa      | al High Enable b                       | it <sup>(1)</sup> |                 |        |

|              | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is high</li> <li>0 = No blanking when the selected blanking signal is high</li> </ul>                     |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

| bit 4        | BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup>                                                                                                                                               |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

|              |                                                                                                                                                                                                                       | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is low</li> <li>0 = No blanking when the selected blanking signal is low</li> </ul> |                    |                                        |                   |                 |        |

| bit 3        | BPHH: Blank                                                                                                                                                                                                           | ing in PWMxH I                                                                                                                                                                                  | High Enable b      | oit                                    |                   |                 |        |

|              |                                                                                                                                                                                                                       | nking (of currenting when the PV                                                                                                                                                                |                    | Fault input signa<br>is high           | als) when the P   | WMxH output i   | s high |

| bit 2        | BPHL: Blanki                                                                                                                                                                                                          | ing in PWMxH L                                                                                                                                                                                  | ow Enable b        | it                                     |                   |                 |        |

|              |                                                                                                                                                                                                                       | nking (of currenting when the PV                                                                                                                                                                |                    | Fault input signa<br>is low            | als) when the P\  | WMxH output i   | s low  |

|              |                                                                                                                                                                                                                       |                                                                                                                                                                                                 |                    |                                        |                   |                 |        |

**Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

### 16.3 SPI Control Registers

#### REGISTER 16-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0           | U-0                                                                         | R/W-0                                  | U-0                                    | U-0                                                    | R/W-0                             | R/W-0             | R/W-0           |

|-----------------|-----------------------------------------------------------------------------|----------------------------------------|----------------------------------------|--------------------------------------------------------|-----------------------------------|-------------------|-----------------|

| SPIEN           |                                                                             | SPISIDL                                | _                                      | _                                                      | SPIBEC2                           | SPIBEC1           | SPIBEC0         |

| bit 15          |                                                                             |                                        |                                        | ·                                                      |                                   |                   | bit 8           |

|                 |                                                                             |                                        |                                        |                                                        |                                   |                   |                 |

| R/W-0           | R/C-0, HS                                                                   | R/W-0                                  | R/W-0                                  | R/W-0                                                  | R/W-0                             | R-0, HS, HC       | R-0, HS, HC     |

| SRMPT           | SPIROV                                                                      | SRXMPT                                 | SISEL2                                 | SISEL1                                                 | SISEL0                            | SPITBF            | SPIRBF          |

| bit 7           |                                                                             |                                        |                                        |                                                        |                                   |                   | bit (           |

| Legend:         |                                                                             | C = Clearabl                           | e bit                                  | U = Unimpleme                                          | ented bit read                    | as '0'            |                 |

| R = Readable    | bit                                                                         | W = Writable                           |                                        | HS = Hardware                                          |                                   | HC = Hardwar      | e Clearable bi  |

| -n = Value at I |                                                                             | '1' = Bit is se                        |                                        | '0' = Bit is clear                                     |                                   | x = Bit is unkr   |                 |

|                 |                                                                             |                                        |                                        |                                                        |                                   |                   |                 |

| bit 15          | SPIEN: SPIX                                                                 | Enable bit                             |                                        |                                                        |                                   |                   |                 |

|                 | 1 = Enables<br>0 = Disables                                                 |                                        | d configures S                         | SCKx, SDOx, SD                                         | Ix and $\overline{SSx}$ as        | serial port pins  |                 |

| bit 14          | Unimplemer                                                                  | nted: Read as                          | '0'                                    |                                                        |                                   |                   |                 |

| bit 13          | SPISIDL: SP                                                                 | Plx Stop in Idle                       | Mode bit                               |                                                        |                                   |                   |                 |

|                 |                                                                             | nues the modu<br>s the module          |                                        | hen device enter<br>le mode                            | rs Idle mode                      |                   |                 |

| bit 12-11       | Unimplemer                                                                  | nted: Read as                          | '0'                                    |                                                        |                                   |                   |                 |

| bit 10-8        | SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) |                                        |                                        |                                                        |                                   |                   |                 |

|                 | Master Mode<br>Number of S                                                  | <u>e:</u><br>PIx transfers t           | hat are pendir                         | ıg.                                                    |                                   |                   |                 |

|                 | Slave Mode:<br>Number of S                                                  | PIx transfers t                        | hat are unread                         | 1.                                                     |                                   |                   |                 |

| bit 7           | SRMPT: SPI                                                                  | x Shift Registe                        | er (SPIxSR) Er                         | mpty bit (valid in                                     | Enhanced Buff                     | er mode)          |                 |

|                 |                                                                             | ft register is er<br>ft register is no |                                        | y to send or rece                                      | ive the data                      |                   |                 |

| bit 6           | SPIROV: SP                                                                  | Ix Receive Ov                          | erflow Flag bit                        | :                                                      |                                   |                   |                 |

|                 | data in th                                                                  | ne SPIxBUF re                          | gister                                 | ed and discarded;                                      | the user applic                   | ation has not rea | ad the previous |

|                 |                                                                             | low has occurr                         |                                        |                                                        |                                   |                   |                 |

| bit 5           |                                                                             |                                        | FO Empty bit                           | (valid in Enhance                                      | ed Buffer mode                    | e)                |                 |

|                 | 1 = RX FIFO<br>0 = RX FIFO                                                  |                                        |                                        |                                                        |                                   |                   |                 |

| bit 4-2         |                                                                             |                                        | ntorrunt Modo                          | hite (valid in Enh                                     | ancod Ruffor r                    | modo)             |                 |

| DIL 4-2         |                                                                             |                                        | -                                      | bits (valid in Enh<br>ouffer is full (SPIT             |                                   | noue)             |                 |

|                 | 110 = Interru<br>101 = Interru<br>100 = Interru                             | upt when the la<br>upt when the la     | ast bit is shifte<br>ast bit is shifte | d into SPIxSR, a<br>d out of SPIxSR<br>into the SPIxSR | nd as a result,<br>and the transn | nit is complete   |                 |

|                 | 011 = Interru                                                               | upt when the Supt when the S           | Plx receive b                          | uffer is full (SPIR<br>uffer is 3/4 or mo              | re full                           | is set)           |                 |

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

| Note 1: | Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the                                                                                                                                                         |

"dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.

2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### 19.2 Analog-to-Digital Converter Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 19.2.1 KEY RESOURCES

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 19-1: ADCON1L: ADC CONTROL REGISTER 1 LOW

| ADON <sup>(1)</sup> — |        |   |   |   |       |

|-----------------------|--------|---|---|---|-------|

| ADON" —               | ADSIDL | — | — | — | —     |

| bit 15                |        |   |   |   | bit 8 |

| U-0   | r-0 | r-0 | r-0 | r-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | —   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           | r = Reserved bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | ADON: ADC Enable bit <sup>(1)</sup> |

|--------|-------------------------------------|

|        | 1 = ADC module is enabled           |

0 = ADC module is off

bit 14 Unimplemented: Read as '0'

- bit 13 **ADSIDL:** ADC Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12-7 Unimplemented: Read as '0'

bit 6-3 Reserved: Maintain as '0'

bit 2-0 Unimplemented: Read as '0'

**Note 1:** Set the ADON bit only after the ADC module has been configured. Changing ADC Configuration bits when ADON = 1 will result in unpredictable behavior.