Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502t-i-2n |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 3.6.1 KEY RESOURCES

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| TABLE 4     | 4-4:  | TIME   | R1 THR                | OUGH . | TIMER5 | REGIST | FER MA | Р           |               |               |              |        |        |       |       |       |       |               |

|-------------|-------|--------|-----------------------|--------|--------|--------|--------|-------------|---------------|---------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14                | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8         | Bit 7         | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |        |                       |        |        |        |        |             | Timer1        | Register      |              |        |        |       |       |       |       | xxxx          |

| PR1         | 0102  |        |                       |        |        |        |        |             | Period R      | Register 1    |              |        |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON    | _                     | TSIDL  | _      | _      | _      | _           | _             |               | TGATE        | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2        | 0106  |        |                       |        |        |        |        |             | Timer2        | Register      |              |        |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108  |        |                       |        |        |        | Timer  | 3 Holding F | Register (for | 32-bit time   | r operations | only)  |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |        |                       |        |        |        |        |             | Timer3        | Register      |              |        |        |       |       |       |       | xxxx          |

| PR2         | 010C  |        | Period Register 2 FFF |        |        |        |        |             | FFFF          |               |              |        |        |       |       |       |       |               |

| PR3         | 010E  |        |                       |        |        |        |        |             | Period R      | Register 3    |              |        |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | _                     | TSIDL  | _      | _      | _      | _           | _             | _             | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON       | 0112  | TON    | _                     | TSIDL  | _      | _      | _      | _           | _             | _             | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | —     | 0000          |

| TMR4        | 0114  |        |                       |        |        |        |        |             | Timer4        | Register      |              |        |        |       |       |       |       | xxxx          |

| TMR5HLD     | 0116  |        |                       |        |        |        | Tir    | ner5 Holdin | g Register (  | (for 32-bit o | perations or | ıly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |                       |        |        |        |        |             | Timer5        | Register      |              |        |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        |                       |        |        |        |        |             | Period R      | Register 4    |              |        |        |       |       |       |       | FFFF          |

| PR5         | 011C  |        |                       |        |        |        |        |             | Period R      | Register 5    |              |        |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON    | _                     | TSIDL  | —      | _      | —      | _           | _             | —             | TGATE        | TCKPS1 | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON    | _                     | TSIDL  | _      | _      | _      | _           | _             |               | TGATE        | TCKPS1 | TCKPS0 |       | _     | TCS   | _     | 0000          |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXGS50X FAMILY

### TABLE 4-11: PWM GENERATOR 4 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14                                                                                | Bit 13  | Bit 12  | Bit 11    | Bit 10         | Bit 9          | Bit 8          | Bit 7        | Bit 6         | Bit 5       | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------------------------------------------------------------------------------------|---------|---------|-----------|----------------|----------------|----------------|--------------|---------------|-------------|----------|----------|----------|----------|----------|---------------|

| PWMCON4     | 0C80  | FLTSTAT | CLSTAT                                                                                | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN         | ITB            | MDCS           | DTC1         | DTC0          | _           |          | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON4      | 0C82  | PENH    | PENL                                                                                  | POLH    | POLL    | PMOD1     | PMOD0          | OVRENH         | OVRENL         | OVRDAT1      | OVRDAT0       | FLTDAT1     | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON4     | 0C84  | IFLTMOD | CLSRC4                                                                                | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0         | CLPOL          | CLMOD          | FLTSRC4      | FLTSRC3       | FLTSRC2     | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC4        | 0C86  |         | PWM4 Generator Duty Cycle Register (PDC4<15:0>) 0000                                  |         |         |           |                |                | 0000           |              |               |             |          |          |          |          |          |               |

| PHASE4      | 0C88  |         | PWM4 Primary Phase-Shift or Independent Time Base Period Register (PHASE4<15:0>) 0000 |         |         |           |                |                | 0000           |              |               |             |          |          |          |          |          |               |

| DTR4        | 0C8A  | -       | _                                                                                     |         |         |           |                |                | PWM4 D         | ead-Time R   | legister (DTI | R4<13:0>)   |          |          |          |          |          | 0000          |

| ALTDTR4     | 0C8C  | -       | _                                                                                     |         |         |           |                | Р              | WM4 Alternate  | e Dead-Time  | e Register (/ | ALTDTR4<13: | 0>)      |          |          |          |          | 0000          |

| SDC4        | 0C8E  |         |                                                                                       |         |         |           |                | PWM4 Sec       | ondary Duty C  | ycle Registe | er (SDC4<18   | 5:0>)       |          |          |          |          |          | 0000          |

| SPHASE4     | 0C90  |         |                                                                                       |         |         |           |                | PWM4 Second    | dary Phase-Sh  | ift Register | (SPHASE4      | <15:0>)     |          |          |          |          |          | 0000          |

| TRIG4       | 0C92  |         |                                                                                       |         |         | PWM4 Pri  | mary Trigger ( | Compare Value  | e Register (TR | GCMP<12:0    | D>)           |             |          |          | _        | _        | _        | 0000          |

| TRGCON4     | 0C94  | TRGDIV3 | TRGDIV2                                                                               | TRGDIV1 | TRGDIV0 | _         | -              | _              | _              | DTM          | _             | TRGSTRT5    | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG4      | 0C96  |         |                                                                                       |         |         | PWM4 Seco | ndary Trigger  | Compare Valu   | e Register (S1 | rrgcmp<1     | 2:0>)         |             |          |          | _        | _        | _        | 0000          |

| PWMCAP4     | 0C98  |         |                                                                                       |         |         | PWM4 P    | rimary Time E  | Base Capture F | Register (PWN  | 1CAP<12:0>   | ·)            |             |          |          | _        | _        | _        | 0000          |

| LEBCON4     | 0C9A  | PHR     | PHF                                                                                   | PLR     | PLF     | FLTLEBEN  | CLLEBEN        | —              | —              | _            | _             | BCH         | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY4     | 0C9C  | _       | _                                                                                     | _       | _       |           |                | PWM4 Lea       | ding-Edge Bla  | nking Delay  | Register (L   | EB<8:0>)    |          |          | _        | —        | _        | 0000          |

| AUXCON4     | 0C9E  | HRPDIS  | HRDDIS                                                                                | _       | _       | BLANKSEL3 | BLANKSEL2      | BLANKSEL1      | BLANKSEL0      | _            | _             | CHOPSEL3    | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-12: PWM GENERATOR 5 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10         | Bit 9          | Bit 8            | Bit 7         | Bit 6        | Bit 5        | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|---------|---------|-----------|----------------|----------------|------------------|---------------|--------------|--------------|----------|----------|----------|----------|----------|---------------|

| PWMCON5     | 0CA0  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN         | ITB            | MDCS             | DTC1          | DTC0         | _            | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON5      | 0CA2  | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0          | OVRENH         | OVRENL           | OVRDAT1       | OVRDAT0      | FLTDAT1      | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON5     | 0CA4  | IFLTMOD | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0         | CLPOL          | CLMOD            | FLTSRC4       | FLTSRC3      | FLTSRC2      | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC5        | 0CA6  |         |         |         |         |           |                | PWM5 Ger       | nerator Duty C   | ycle Registe  | er (PDC5<1   | 5:0>)        |          |          |          |          |          | 0000          |

| PHASE5      | 0CA8  |         |         |         |         | F         | WM5 Primary    | Phase-Shift o  | or Independent   | t Time Base   | Period Reg   | ister (PHASE | 5<15:0>) |          |          |          |          | 0000          |

| DTR5        | 0CAA  | _       | —       |         |         |           |                |                | PWM5 D           | ead-Time F    | Register (DT | R5<13:0>)    |          |          |          |          |          | 0000          |

| ALTDTR5     | 0CAC  |         | —       |         |         |           |                | Р              | WM5 Alternate    | e Dead-Tim    | e Register ( | ALTDTR5<13   | :0>)     |          |          |          |          | 0000          |

| SDC5        | 0CAE  |         |         |         |         |           |                | PWM5 Sec       | ondary Duty C    | ycle Registe  | er (SDC5<1   | 5:0>)        |          |          |          |          |          | 0000          |

| SPHASE5     | 0CB0  |         |         |         |         |           |                | PWM5 Secon     | dary Phase-Sł    | nift Register | (SPHASE5     | <15:0>)      |          |          |          |          |          | 0000          |

| TRIG5       | 0CB2  |         |         |         |         | PWM5 Pri  | mary Trigger ( | Compare Value  | e Register (TR   | GCMP<12:      | 0>)          |              |          |          | —        | _        | _        | 0000          |

| TRGCON5     | 0CB4  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | _         | -              | _              | _                | DTM           | _            | TRGSTRT5     | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG5      | 0CB6  |         |         |         |         | PWM5 Seco | ndary Trigger  | Compare Valu   | ue Register (S   | rrgcmp<1      | 2:0>)        |              |          |          | _        | _        | _        | 0000          |

| PWMCAP5     | 0CB8  |         |         |         |         | PWM5 F    | rimary Time B  | Base Capture I | Register (PWN    | 1CAP<12:0>    | >)           |              |          |          | _        | —        | _        | 0000          |

| LEBCON5     | 0CBA  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN        | —              | —                | _             | —            | BCH          | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY5     | 0CBC  | —       | —       | _       | _       |           |                | PWM5 Lea       | ding-Edge Bla    | nking Delay   | Register (L  | .EB<8:0>)    |          |          | —        | —        | _        | 0000          |

| AUXCON5     | 0CBE  | HRPDIS  | HRDDIS  | _       | —       | BLANKSEL3 | BLANKSEL2      | BLANKSEL1      | <b>BLANKSEL0</b> |               | _            | CHOPSEL3     | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0             | R/W-0                                            | R/W-0                                                                                         | R/W-0            | R/W-0            | R/W-0          | R/W-0           | R/W-0   |

|-------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------|------------------|----------------|-----------------|---------|

| U1CTSR7           | U1CTSR6                                          | U1CTSR5                                                                                       | U1CTSR4          | U1CTSR3          | U1CTSR2        | U1CTSR1         | U1CTSR0 |

| bit 15            |                                                  |                                                                                               | ·                |                  |                |                 | bit 8   |

|                   |                                                  |                                                                                               |                  |                  |                |                 |         |

| R/W-0             | R/W-0                                            | R/W-0                                                                                         | R/W-0            | R/W-0            | R/W-0          | R/W-0           | R/W-0   |

| U1RXR7            | U1RXR6                                           | U1RXR5                                                                                        | U1RXR4           | U1RXR3           | U1RXR2         | U1RXR1          | U1RXR0  |

| bit 7             |                                                  |                                                                                               |                  |                  |                |                 | bit 0   |

| <u> </u>          |                                                  |                                                                                               |                  |                  |                |                 |         |

| Legend:           |                                                  |                                                                                               |                  |                  |                |                 |         |

| R = Readable bit  |                                                  | W = Writable                                                                                  |                  | U = Unimplen     |                |                 |         |

| -n = Value at POR |                                                  | '1' = Bit is set                                                                              |                  | '0' = Bit is cle | ared           | x = Bit is unkr | iown    |

| bit 7-0           | 10110100 =<br>•<br>•<br>00000001 =<br>00000000 = | Input tied to RF<br>Input tied to RF<br>Input tied to RF<br>Input tied to Vs<br>: Assign UART | 2180<br>21<br>35 | 1RX) to the Co   | rresponding RF | n Pin bits      |         |

### REGISTER 10-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| R/W-0            |        |                  |        |                  |                  |                 |        |

|------------------|--------|------------------|--------|------------------|------------------|-----------------|--------|

|                  | R/W-0  | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT8R7           | FLT8R6 | FLT8R5           | FLT8R4 | FLT8R3           | FLT8R2           | FLT8R1          | FLT8R0 |

| bit 15           |        |                  |        |                  |                  |                 | bit 8  |

|                  |        |                  |        |                  |                  |                 |        |

| R/W-0            | R/W-0  | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT7R7           | FLT7R6 | FLT7R5           | FLT7R4 | FLT7R3           | FLT7R2           | FLT7R1          | FLT7R0 |

| bit 7            |        |                  |        |                  |                  |                 | bit C  |

|                  |        |                  |        |                  |                  |                 |        |

| Legend:          |        |                  |        |                  |                  |                 |        |

| R = Readable bit |        | W = Writable     | bit    | U = Unimpler     | nented bit, read | d as '0'        |        |

| -n = Value at    | POR    | '1' = Bit is set | :      | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15-8         |        | Assign PWM       | · · ·  | to the Corresp   | onding RPn Pi    | n bits          |        |

### REGISTER 10-19: RPINR43: PERIPHERAL PIN SELECT INPUT REGISTER 43

#### **REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output is set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output is set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

| -                           | R/W-0                                                                                                                                                                    | R/W-0                                                                                                                                                                                           | U-0                                                                                                                                         | U-0                     | U-0             | U-0               | U-0    |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------|--------|

| FRMEN                       | SPIFSD                                                                                                                                                                   | FRMPOL                                                                                                                                                                                          | _                                                                                                                                           | —                       | _               | —                 | _      |

| bit 15                      | ÷                                                                                                                                                                        |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   | bit 8  |

|                             |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |        |

| U-0                         | U-0                                                                                                                                                                      | U-0                                                                                                                                                                                             | U-0                                                                                                                                         | U-0                     | U-0             | R/W-0             | R/W-0  |

| —                           | _                                                                                                                                                                        | _                                                                                                                                                                                               | —                                                                                                                                           |                         | —               | FRMDLY            | SPIBEN |

| bit 7                       |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   | bit 0  |

|                             |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |        |

| Legend:                     |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |        |

| R = Readab                  | ole bit                                                                                                                                                                  | W = Writable b                                                                                                                                                                                  | oit                                                                                                                                         | U = Unimplen            | nented bit, rea | id as '0'         |        |

| -n = Value a                | at POR                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                                                |                                                                                                                                             | '0' = Bit is cle        | ared            | x = Bit is unkn   | nown   |

|                             |                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                             |                         |                 |                   |        |

| bit 15                      | FRMEN: Fran                                                                                                                                                              | med SPIx Suppo                                                                                                                                                                                  | ort bit                                                                                                                                     |                         |                 |                   |        |

|                             |                                                                                                                                                                          |                                                                                                                                                                                                 | •                                                                                                                                           | pin is used as          | the frame syn   | c pulse input/out | tput)  |

|                             | 0 = Framed S                                                                                                                                                             | SPIx support is d                                                                                                                                                                               | licablod                                                                                                                                    |                         |                 |                   |        |

|                             |                                                                                                                                                                          | ••                                                                                                                                                                                              |                                                                                                                                             |                         |                 |                   |        |

| bit 14                      | SPIFSD: Fran                                                                                                                                                             | me Sync Pulse [                                                                                                                                                                                 | Direction Co                                                                                                                                | ntrol bit               |                 |                   |        |

| bit 14                      | <b>SPIFSD:</b> Fran<br>1 = Frame sy                                                                                                                                      | ••                                                                                                                                                                                              | Direction Co<br>slave)                                                                                                                      | ntrol bit               |                 |                   |        |

| bit 14<br>bit 13            | <b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy                                                                                                                      | me Sync Pulse I<br>nc pulse input (s                                                                                                                                                            | Direction Co<br>slave)<br>(master)                                                                                                          | ntrol bit               |                 |                   |        |

|                             | <b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy<br><b>FRMPOL:</b> Fra<br>1 = Frame sy                                                                                | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output                                                                                                                                         | Direction Co<br>slave)<br>(master)<br>Polarity bit<br>e-high                                                                                | ntrol bit               |                 |                   |        |

|                             | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fra<br>1 = Frame sy<br>0 = Frame sy                                                                              | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ                                                                                                  | Direction Col<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low                                                                      | ntrol bit               |                 |                   |        |

| bit 13                      | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fran<br>1 = Frame sy<br>0 = Frame sy<br>Unimplemen                                                               | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ                                                                             | Direction Col<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low                                                                      |                         |                 |                   |        |

| bit 13<br>bit 12-2          | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fra<br>1 = Frame sy<br>0 = Frame sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame sy                                 | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ<br>ted: Read as '0                                                          | Direction Col<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low<br>,<br>Edge Select<br>les with the f                                | t bit<br>îrst bit clock |                 |                   |        |

| bit 13<br>bit 12-2<br>bit 1 | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fra<br>1 = Frame sy<br>0 = Frame sy<br>Unimplement<br>FRMDLY: Fra<br>1 = Frame sy<br>0 = Frame sy                | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ<br>ted: Read as '0<br>ame Sync Pulse<br>nc pulse coincid                    | Direction Col<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low<br>,<br>Edge Select<br>les with the f<br>es the first b              | t bit<br>îrst bit clock |                 |                   |        |

| bit 13<br>bit 12-2          | SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fra<br>1 = Frame sy<br>0 = Frame sy<br>Unimplement<br>FRMDLY: Fra<br>1 = Frame sy<br>0 = Frame sy<br>SPIBEN: Ent | me Sync Pulse I<br>nc pulse input (s<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ<br>ted: Read as '0<br>ame Sync Pulse<br>nc pulse coincid<br>nc pulse preced | Direction Con<br>slave)<br>(master)<br>Polarity bit<br>e-high<br>e-low<br>,<br>Edge Select<br>les with the f<br>es the first b<br>nable bit | t bit<br>îrst bit clock |                 |                   |        |

### REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

NOTES:

### REGISTER 17-1: I2CxCONL: I2Cx CONTROL REGISTER LOW (CONTINUED)

| bit 6 | STREN: SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Used in conjunction with the SCLREL bit.                                                                                                               |

|       | <ul> <li>1 = Enables software or receives clock stretching</li> <li>0 = Disables software or receives clock stretching</li> </ul>                      |

| 54 C  | C C                                                                                                                                                    |

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                       |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge                                    |

|       | 0 = Sends ACK during Acknowledge                                                                                                                       |

| bit 4 | ACKEN: Acknowledge Sequence Enable bit                                                                                                                 |

|       | (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                          |

|       | 1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit; hardware is clear at the end of the master Acknowledge sequence |

|       | 0 = Acknowledge sequence is not in progress                                                                                                            |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                            |

|       | 1 = Enables Receive mode for I <sup>2</sup> C; hardware is clear at the end of the eighth bit of the master receive data byte                          |

|       | 0 = Receive sequence is not in progress                                                                                                                |

| bit 2 | PEN: Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                             |

|       | 1 = Initiates Stop condition on SDAx and SCLx pins; hardware is clear at the end of the master Stop sequence                                           |

|       | 0 = Stop condition is not in progress                                                                                                                  |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                           |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins; hardware is clear at the end of the master Repeated Start sequence                       |

|       | 0 = Repeated Start condition is not in progress                                                                                                        |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                            |

|       | 1 = Initiates Start condition on SDAx and SCLx pins; hardware is clear at the end of the master Start sequence                                         |

0 = Start condition is not in progress

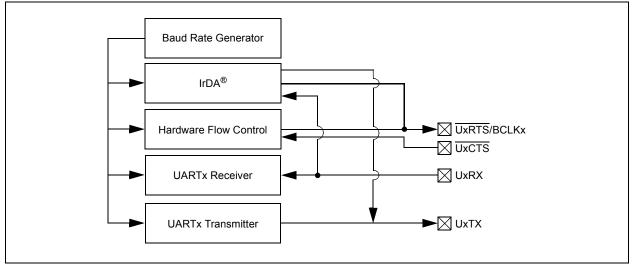

## 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXGS50X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps in 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps in 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit Mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 18-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 18-1: UARTX SIMPLIFIED BLOCK DIAGRAM

| R/W-0         | R/W-0                                                          | R/W-0                                                                                                                                                                           | R/W-0                                                                                          | R/W-0             | R/W-0                        | R/W-0            | R/W-0           |

|---------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------|------------------------------|------------------|-----------------|

| CLKSEL1       | CLKSEL0                                                        | CLKDIV5                                                                                                                                                                         | CLKDIV4                                                                                        | CLKDIV3           | CLKDIV2                      | CLKDIV1          | CLKDIV0         |

| bit 15        |                                                                |                                                                                                                                                                                 |                                                                                                |                   |                              |                  | bit             |

| R/W-0         | U-0                                                            | U-0                                                                                                                                                                             | U-0                                                                                            | R/W-0             | R/W-0                        | R/W-0            | R/W-0           |

| SHREN         |                                                                |                                                                                                                                                                                 | _                                                                                              | C3EN              | C2EN                         | C1EN             | COEN            |

| bit 7         |                                                                |                                                                                                                                                                                 |                                                                                                |                   |                              |                  | bit             |

| Legend:       |                                                                |                                                                                                                                                                                 |                                                                                                |                   |                              |                  |                 |

| R = Readabl   | e bit                                                          | W = Writable                                                                                                                                                                    | bit                                                                                            | U = Unimplem      | nented bit, read             | d as '0'         |                 |

| -n = Value at | POR                                                            | '1' = Bit is set                                                                                                                                                                |                                                                                                | '0' = Bit is clea | ared                         | x = Bit is unkr  | nown            |

| bit 15-14     | 11 = APLL<br>10 = FRC                                          | D>: ADC Module<br>system Clock x 3<br>ystem Clock)                                                                                                                              |                                                                                                | Selection bits    |                              |                  |                 |

|               | module clock<br>TCORESRC cld<br>register or the<br>111111 = 64 | orms a TCORESR<br>source selecte<br>ock to get a col<br>e SHRADCS<6<br>Source Clock P<br>Source Clock P<br>Source Clock P<br>Source Clock P<br>Source Clock P<br>Source Clock P | d by the CLKS<br>re-specific TAD<br>:0> bits in the /<br>Periods<br>eriods<br>eriods<br>eriods | EL<2:0> bits. T   | hen, each AD<br>ng the ADCS< | C core individua | ally divides th |

| bit 7         | 1 = Shared A                                                   | red ADC Core I<br>DC core is ena<br>DC core is disa                                                                                                                             | bled                                                                                           |                   |                              |                  |                 |

| bit 6-4       | Unimplemen                                                     | ted: Read as '                                                                                                                                                                  | )'                                                                                             |                   |                              |                  |                 |

| bit 3         | 1 = Dedicated                                                  | ated ADC Core<br>d ADC Core 3 is<br>d ADC Core 3 is                                                                                                                             | s enabled                                                                                      |                   |                              |                  |                 |

| bit 2         | 1 = Dedicated                                                  | ated ADC Core<br>d ADC Core 2 is<br>d ADC Core 2 is                                                                                                                             | s enabled                                                                                      |                   |                              |                  |                 |

| bit 1         | 1 = Dedicated                                                  | ated ADC Core<br>d ADC Core 1 is<br>d ADC Core 1 is                                                                                                                             | s enabled                                                                                      |                   |                              |                  |                 |

| bit 0         | COEN: Dedic                                                    | ated ADC Core                                                                                                                                                                   | 0 Enable bits                                                                                  |                   |                              |                  |                 |

#### REGISTER 19-27: ADTRIGXH: ADC CHANNEL TRIGGER x SELECTION REGISTER HIGH (x = 0 to 5)

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0          | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|----------------|-------|-------|

|        | _   | _   |       | TF    | RGSRC(4x+3)<4: | 0>    |       |

| bit 15 |     |     |       |       |                |       | bit 8 |

|        |     |     |       |       |                |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0          | R/W-0 | R/W-0 |

|        | _   | _   |       | TR    | GSRC(4x+2)<4   | :0>   |       |

| bit 7  |     |     |       |       |                |       | bit 0 |

## Legend:

| •                 |                  |                               |                    |  |

|-------------------|------------------|-------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as '0'             |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |  |

#### bit 15-13 Unimplemented: Read as '0'

bit 12-8 TRGSRC(4x+3)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

| TRGSRC(4x+3)<4:0>: Ingger Source Selection T  |

|-----------------------------------------------|

| 11111 = ADTRG31                               |

| 11110 = Reserved                              |

| 11101 = Reserved                              |

| 11100 = PWM Generator 5 current-limit trigger |

| 11011 = PWM Generator 4 current-limit trigger |

| 11010 = PWM Generator 3 current-limit trigger |

| 11001 = PWM Generator 2 current-limit trigger |

| 11000 = PWM Generator 1 current-limit trigger |

| 10111 = Output Compare 2 trigger              |

| 10110 = Output Compare 1 trigger              |

| 10101 = Reserved                              |

| 10100 = Reserved                              |

| 10011 = PWM Generator 5 secondary trigger     |

| 10010 = PWM Generator 4 secondary trigger     |

| 10001 = PWM Generator 3 secondary trigger     |

| 10000 = PWM Generator 2 secondary trigger     |

| 01111 = PWM Generator 1 secondary trigger     |

| 01110 = PWM secondary Special Event Trigger   |

| 01101 = Timer2 period match                   |

| 01100 = Timer1 period match                   |

| 01011 = Reserved                              |

| 01010 = Reserved                              |

| 01001 = PWM Generator 5 primary trigger       |

| 01000 = PWM Generator 4 primary trigger       |

| 00111 = PWM Generator 3 primary trigger       |

| 00110 = PWM Generator 2 primary trigger       |

| 00101 = PWM Generator 1 primary trigger       |

| 00100 = PWM Special Event Trigger             |

| 00011 = Reserved                              |

| 00010 = Level software trigger                |

| 00001 = Common software trigger               |

| 00000 = No trigger is enabled                 |

| Unimplemented: Read as '0'                    |

|                                               |

bit 7-5

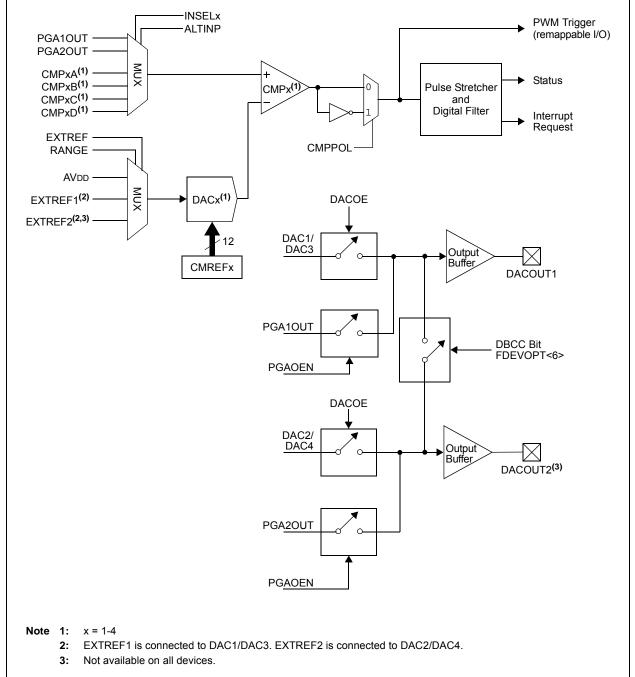

## 20.2 Module Description

Figure 20-1 shows a functional block diagram of one analog comparator from the high-speed analog comparator module. The analog comparator provides high-speed operation with a typical delay of 15 ns. The negative input of the comparator is always connected to the DACx circuit. The positive input of the comparator is connected to an analog multiplexer that selects the desired source pin. The analog comparator input pins are typically shared with pins used by the Analog-to-Digital Converter (ADC) module. Both the comparator and the ADC can use the same pins at the same time. This capability enables a user to measure an input voltage with the ADC and detect voltage transients with the comparator.

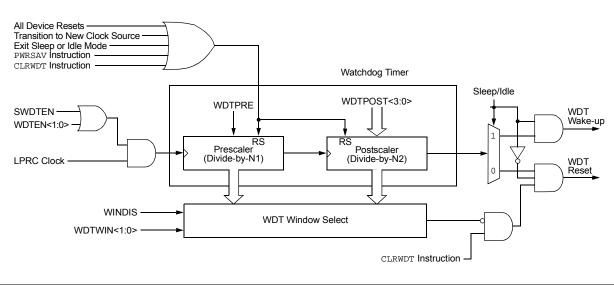

## 23.6 Watchdog Timer (WDT)

For dsPIC33EPXXGS50X family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 23.6.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Time-out Period (TWDT), as shown in Parameter SY12 in Table 26-23.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods, ranges from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

### FIGURE 23-2: WDT BLOCK DIAGRAM

## 23.6.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) needs to be cleared in software after the device wakes up.

## 23.6.3 ENABLING WDT

The WDT is enabled or disabled by the WDTEN<1:0> Configuration bits in the FWDT Configuration register. When the WDTEN<1:0> Configuration bits have been programmed to '0b11', the WDT is always enabled.

The WDT can be optionally controlled in software when the WDTEN<1:0> Configuration bits have been programmed to '0b10'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disables the WDT during non-critical segments for maximum power savings.

The WDT Time-out flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 23.6.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<7>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

| Base<br>Instr<br># Assembly<br>Mnemonic |        | Assembly Syntax |                             | Description                                       | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|-----------------------------------------|--------|-----------------|-----------------------------|---------------------------------------------------|---------------|-------------------------------|--------------------------|

| 48                                      | MOV    | MOV             | f,Wn                        | Move f to Wn                                      | 1 1           | 1                             | None                     |

|                                         |        | MOV             | f                           | Move f to f                                       | 1             | 1                             | None                     |

|                                         |        | MOV             | f,WREG                      | Move f to WREG                                    | 1             | 1                             | None                     |

|                                         |        | MOV             | #lit16,Wn                   | Move 16-bit literal to Wn                         | 1             | 1                             | None                     |

|                                         |        | MOV.b           | #lit8,Wn                    | Move 8-bit literal to Wn                          | 1             | 1                             | None                     |

|                                         |        | MOV             | Wn,f                        | Move Wn to f                                      | 1             | 1                             | None                     |

|                                         |        | MOV             | Wso,Wdo                     | Move Ws to Wd                                     | 1             | 1                             | None                     |

|                                         |        | MOV             | WREG, f                     | Move WREG to f                                    | 1             | 1                             | None                     |

|                                         |        | MOV.D           | Wns,Wd                      | Move Double from W(ns):W(ns + 1) to Wd            | 1             | 2                             | None                     |

|                                         |        | MOV.D           | Ws,Wnd                      | Move Double from Ws to W(nd + 1):W(nd)            | 1             | 2                             | None                     |

| 19                                      | MOVPAG | MOVPAG          | #lit10,DSRPAG               | Move 10-bit literal to DSRPAG                     | 1             | 1                             | None                     |

|                                         |        | MOVPAG          | #lit8,TBLPAG                | Move 8-bit literal to TBLPAG                      | 1             | 1                             | None                     |

|                                         |        | MOVPAGW         | Ws, DSRPAG                  | Move Ws<9:0> to DSRPAG                            | 1             | 1                             | None                     |

|                                         |        | MOVPAGW         | Ws, TBLPAG                  | Move Ws<7:0> to TBLPAG                            | 1             | 1                             | None                     |

| 50                                      | MOVSAC | MOVSAC          | Acc,Wx,Wxd,Wy,Wyd,AWB       | Prefetch and store accumulator                    | 1             | 1                             | None                     |

| 51                                      | MPY    | MPY             | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | Multiply Wm by Wn to Accumulator                  | 1             | 1                             | OA,OB,OAB<br>SA,SB,SAB   |

|                                         |        | MPY             | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd     | Square Wm to Accumulator                          | 1             | 1                             | OA,OB,OAE<br>SA,SB,SAE   |

| 52                                      | MPY.N  | MPY.N           | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | -(Multiply Wm by Wn) to Accumulator               | 1             | 1                             | None                     |

| 53                                      | MSC    | MSC             | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd,AWB | Multiply and Subtract from Accumulator            | 1             | 1                             | OA,OB,OAE<br>SA,SB,SAE   |

| 54                                      | MUL    | MUL.SS          | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)       | 1             | 1                             | None                     |

|                                         |        | MUL.SS          | Wb,Ws,Acc                   | Accumulator = signed(Wb) * signed(Ws)             | 1             | 1                             | None                     |

|                                         |        | MUL.SU          | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(Ws)     | 1             | 1                             | None                     |

|                                         |        | MUL.SU          | Wb,Ws,Acc                   | Accumulator = signed(Wb) *<br>unsigned(Ws)        | 1             | 1                             | None                     |

|                                         |        | MUL.SU          | Wb,#lit5,Acc                | Accumulator = signed(Wb) * unsigned(lit5)         | 1             | 1                             | None                     |

|                                         |        | MUL.US          | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) *<br>signed(Ws)     | 1             | 1                             | None                     |

|                                         |        | MUL.US          | Wb,Ws,Acc                   | Accumulator = unsigned(Wb) * signed(Ws)           | 1             | 1                             | None                     |

|                                         |        | MUL.UU          | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1                             | None                     |

|                                         |        | MUL.UU          | Wb,#lit5,Acc                | Accumulator = unsigned(Wb) *<br>unsigned(lit5)    | 1             | 1                             | None                     |

|                                         |        | MUL.UU          | Wb,Ws,Acc                   | Accumulator = unsigned(Wb) *<br>unsigned(Ws)      | 1             | 1                             | None                     |

|                                         |        | MULW.SS         | Wb,Ws,Wnd                   | Wnd = signed(Wb) * signed(Ws)                     | 1             | 1                             | None                     |

|                                         |        | MULW.SU         | Wb,Ws,Wnd                   | Wnd = signed(Wb) * unsigned(Ws)                   | 1             | 1                             | None                     |

|                                         |        | MULW.US         | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * signed(Ws)                   | 1             | 1                             | None                     |

|                                         |        | MULW.UU         | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * unsigned(Ws)                 | 1             | 1                             | None                     |

|                                         |        | MUL.SU          | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1             | 1                             | None                     |

|                                         |        | MUL.SU          | Wb,#lit5,Wnd                | Wnd = signed(Wb) * unsigned(lit5)                 | 1             | 1                             | None                     |

|                                         |        | MUL.UU          | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1                             | None                     |

|                                         |        | MUL.UU          | Wb,#lit5,Wnd                | Wnd = unsigned(Wb) * unsigned(lit5)               | 1             | 1                             | None                     |

|                                         |        | MUL             | f                           | W3:W2 = f * WREG                                  | 1             | 1                             | None                     |

## TABLE 24-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

## 26.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33EPXXGS50X family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXGS50X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                | 40°C to +125°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                            | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 3.0V^{(3)}$  | -0.3V to +5.5V       |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(3)}$    | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                   |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                |                      |

| Maximum current sunk by all ports <sup>(2)</sup>                              | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those, or any other conditions above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 26-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

| DC CHARACTERISTICS                 |     |                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |            |                                                                                                                                                 |  |

|------------------------------------|-----|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. Symbol Characteristic |     | Min.                                    | Тур. <sup>(1)</sup>                                                                                                                                                                                                                                                                   | Max. | Units | Conditions |                                                                                                                                                 |  |

|                                    | lı∟ | Input Leakage Current <sup>(2,3)</sup>  |                                                                                                                                                                                                                                                                                       |      |       |            |                                                                                                                                                 |  |

| DI50                               |     | I/O Pins 5V Tolerant <sup>(4)</sup>     | -1                                                                                                                                                                                                                                                                                    | —    | +1    | μA         | $Vss \le VPIN \le VDD,$ pin at high-impedance                                                                                                   |  |

| DI51                               |     | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1                                                                                                                                                                                                                                                                                    | —    | +1    | μA         | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ pin \text{ at high-impedance}, \\ -40^\circ C \leq TA \leq +85^\circ C \end{array}$ |  |

| DI51a                              |     | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1    | μA         | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                   |  |

| DI51b                              |     | I/O Pins Not 5V Tolerant <sup>(4)</sup> | -1                                                                                                                                                                                                                                                                                    | —    | +1    | μA         | $Vss \le VPIN \le VDD,$<br>pin at high-impedance,<br>-40°C \le TA ≤ +125°C                                                                      |  |