Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K × 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXGS50X Digital Signal Controller (DSC) devices.

dsPIC33EPXXGS50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

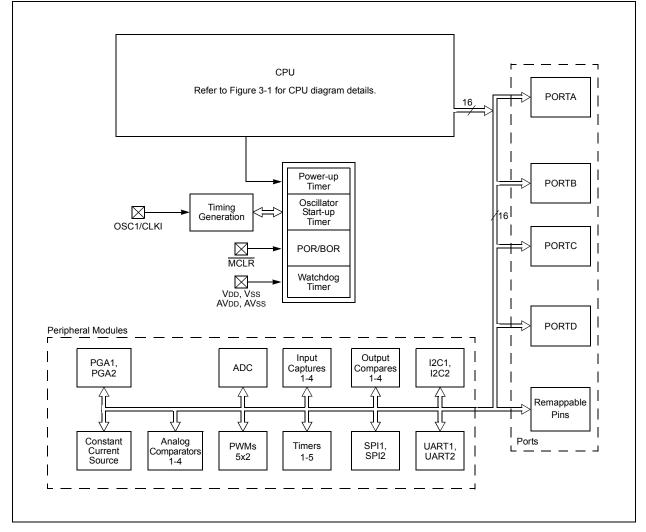

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: dsPIC33EPXXGS50X FAMILY BLOCK DIAGRAM

| Pin Name <sup>(1)</sup>                                  | Pin<br>Type | Buffer<br>Type | PPS        | Description                                                                 |

|----------------------------------------------------------|-------------|----------------|------------|-----------------------------------------------------------------------------|

| SCL1                                                     | I/O         | ST             | No         | Synchronous serial clock input/output for I2C1.                             |

| SDA1                                                     | I/O         | ST             | No         | Synchronous serial data input/output for I2C1.                              |

| ASCL1                                                    | I/O         | ST             | No         | Alternate synchronous serial clock input/output for I2C1.                   |

| ASDA1                                                    | I/O         | ST             | No         | Alternate synchronous serial data input/output for I2C1.                    |

| SCL2                                                     | I/O         | ST             | No         | Synchronous serial clock input/output for I2C2.                             |

| SDA2                                                     | I/O         | ST             | No         | Synchronous serial data input/output for I2C2.                              |

| ASCL2                                                    | I/O         | ST             | No         | Alternate synchronous serial clock input/output for I2C2.                   |

| ASDA2                                                    | I/O         | ST             | No         | Alternate synchronous serial data input/output for I2C2.                    |

| TMS                                                      | I           | ST             | No         | JTAG Test mode select pin.                                                  |

| TCK                                                      | I           | ST             | No         | JTAG test clock input pin.                                                  |

| TDI                                                      | I           | ST             | No         | JTAG test data input pin.                                                   |

| TDO                                                      | 0           |                | No         | JTAG test data output pin.                                                  |

| FLT1-FLT8                                                | Ι           | ST             | Yes        | PWM Fault Inputs 1 through 8.                                               |

| FLT9-FLT12                                               | I           | ST             | No         | PWM Fault Inputs 9 through 12.                                              |

| FLT31                                                    |             | ST             | No         | PWM Fault Input 31 (Class B Fault).                                         |

| PWM1L-PWM3L                                              | 0           | _              | No         | PWM Low Outputs 1 through 3.                                                |

| PWM1H-PWM3H                                              | 0           | _              | No         | PWM High Outputs 1 through 3.                                               |

| PWM4L-PWM5L <sup>(2)</sup><br>PWM4H-PWM5H <sup>(2)</sup> | 0           | _              | Yes        | PWM Low Outputs 4 and 5.                                                    |

| SYNCI1, SYNCI2                                           | 0           | —<br>ST        | Yes<br>Yes | PWM High Outputs 4 and 5.                                                   |

| SYNCO1, SYNCO2                                           | 0           | 51             | Yes        | PWM Synchronization Inputs 1 and 2.<br>PWM Synchronization Outputs 1 and 2. |

| CMP1A-CMP4A                                              |             | Analog         | No         | Comparator Channels 1 through 4 A input.                                    |

| CMP1B-CMP4B                                              |             | Analog         | No         | Comparator Channels 1 through 4 B input.                                    |

| CMP1C-CMP4C                                              | i           | Analog         | No         | Comparator Channels 1 through 4 C input.                                    |

| CMP1D-CMP4D                                              | i           | Analog         | No         | Comparator Channels 1 through 4 D input.                                    |

| DACOUT1, DACOUT2                                         | 0           |                | No         | DAC Output Voltages 1 and 2.                                                |

| EXTREF1, EXTREF2                                         | Ι           | Analog         | No         | External Voltage Reference Inputs 1 and 2 for the reference DACs.           |

| ISRC1-ISRC4                                              | 0           | Analog         | No         | Constant-Current Outputs 1 through 4.                                       |

| PGA1P1-PGA1P4                                            | Ι           | Analog         | No         | PGA1 Positive Inputs 1 through 4.                                           |

| PGA1N1-PGA1N3                                            | I           | Analog         | No         | PGA1 Negative Inputs 1 through 3.                                           |

| PGA2P1-PGA2P4                                            | I           | Analog         | No         | PGA2 Positive Inputs 1 through 4.                                           |

| PGA2N1-PGA2N3                                            | I           | Analog         | No         | PGA2 Negative Inputs 1 through 3.                                           |

| ADTRG31                                                  | Ι           | ST             | No         | External ADC trigger source.                                                |

| PGED1                                                    | I/O         | ST             | No         | Data I/O pin for Programming/Debugging Communication Channel 1.             |

| PGEC1                                                    | Ι           | ST             | No         | Clock input pin for Programming/Debugging Communication Channel 1.          |

| PGED2                                                    | I/O         | ST             | No         | Data I/O pin for Programming/Debugging Communication Channel 2.             |

| PGEC2                                                    | Ι           | ST             | No         | Clock input pin for Programming/Debugging Communication Channel 2.          |

| PGED3                                                    | I/O         | ST             | No         | Data I/O pin for Programming/Debugging Communication Channel 3.             |

| PGEC3                                                    | I           | ST             | No         | Clock input pin for Programming/Debugging Communication Channel 3.          |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------|

|------------|-------------------------------------|

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PowerO = OutputI = InputTTL = TTL input buffer

1: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

2: These pins are dedicated on 64-pin devices.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "Multi-Tool Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

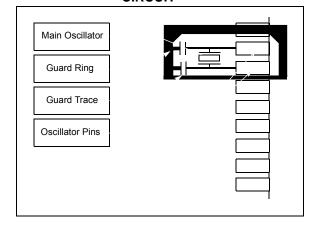

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### 3.7 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R/W-0                | R/W-0                                                                                                             | R/W-0                                                      | R/W-0             | R/C-0                              | R/C-0     | R-0             | R/W-0              |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------|------------------------------------|-----------|-----------------|--------------------|--|--|

| OA                   | OB                                                                                                                | SA <sup>(3)</sup>                                          | SB <sup>(3)</sup> | OAB                                | SAB       | DA              | DC                 |  |  |

| bit 15               |                                                                                                                   |                                                            |                   |                                    |           |                 | bit 8              |  |  |

| R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup>                                                                                              | R/W-0 <sup>(2)</sup>                                       | R-0               | R/W-0                              | R/W-0     | R/W-0           | R/W-0              |  |  |

| IPL2 <sup>(1)</sup>  | IPL1 <sup>(1)</sup>                                                                                               | IPL0 <sup>(1)</sup>                                        | RA                | N                                  | OV        | Z               | C                  |  |  |

| bit 7                |                                                                                                                   |                                                            |                   |                                    |           | _               | bit 0              |  |  |

|                      |                                                                                                                   |                                                            |                   |                                    |           |                 |                    |  |  |

| Legend:              |                                                                                                                   | C = Clearable                                              | bit               |                                    |           |                 |                    |  |  |

| R = Readable bit     |                                                                                                                   | W = Writable                                               | bit               | U = Unimplemented bit, read as '0' |           |                 |                    |  |  |

| -n = Value at        | POR                                                                                                               | '1'= Bit is set                                            |                   | '0' = Bit is cle                   | ared      | x = Bit is unkr | x = Bit is unknown |  |  |

| bit 15               | 1 = Accumula                                                                                                      | ator A Overflow<br>ator A has overf<br>ator A has not o    | lowed             |                                    |           |                 |                    |  |  |

| bit 14               | OB: Accumulator B Overflow Status bit<br>1 = Accumulator B has overflowed<br>0 = Accumulator B has not overflowed |                                                            |                   |                                    |           |                 |                    |  |  |

| bit 13               | 1 = Accumula                                                                                                      | ator A Saturatio<br>ator A is saturat<br>ator A is not sat | ed or has bee     |                                    | some time |                 |                    |  |  |

- 1 = Accumulator B is saturated or has been saturated at some time

- 0 = Accumulator B is not saturated

- bit 11 OAB: OA || OB Combined Accumulator Overflow Status bit

- 1 = Accumulators A or B have overflowed

- 0 = Neither Accumulators A or B have overflowed

- bit 10 SAB: SA || SB Combined Accumulator 'Sticky' Status bit

- 1 = Accumulators A or B are saturated or have been saturated at some time

- 0 = Neither Accumulator A or B are saturated

- bit 9 DA: DO Loop Active bit

- 1 = DO loop in progress

- 0 = DO loop not in progress

- bit 8 DC: MCU ALU Half Carry/Borrow bit

- 1 = A carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- 0 = No carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **2:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

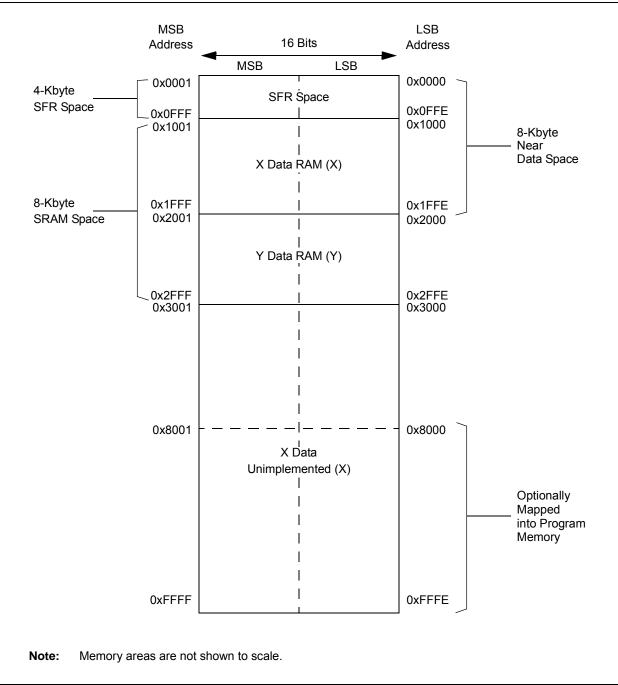

#### FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

## TABLE 4-20: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SFR<br>Name | Addr. | Bit 15     | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|------------|----------|----------|----------|----------|----------|----------|----------|------------|--------|--------|--------|---------|--------|--------|--------|---------------|

| RPINR0      | 06A0  | INT1R<7:0> |          |          |          |          |          | _        | _        | _          | _      | —      | _      |         |        | 0000   |        |               |

| RPINR1      | 06A2  | _          | _        | _        | _        | _        | _        | _        | _        |            |        |        | INT2   | R<7:0>  |        |        |        | 0000          |

| RPINR2      | 06A4  |            |          |          | T1CKF    | R<7:0>   |          |          |          | _          | _      | _      | _      | _       | _      | —      | _      | 0000          |

| RPINR3      | 06A6  | T3CKR7     | T3CKR6   | T3CKR5   | T3CKR4   | T3CKR3   | T3CKR2   | T3CKR1   | T3CKR0   | T2CKR7     | T2CKR6 | T2CKR5 | T2CKR4 | T2CKR3  | T2CKR2 | T2CKR1 | T2CKR0 | 0000          |

| RPINR7      | 06AE  | IC2R7      | IC2R6    | IC2R5    | IC2R4    | IC2R3    | IC2R2    | IC2R1    | IC2R0    | IC1R7      | IC1R6  | IC1R5  | IC1R4  | IC1R3   | IC1R2  | IC1R1  | IC1R0  | 0000          |

| RPINR8      | 06B0  | IC4R7      | IC4R6    | IC4R5    | IC4R4    | IC4R3    | IC4R2    | IC4R1    | IC4R0    | IC3R7      | IC3R6  | IC3R5  | IC3R4  | IC3R3   | IC3R2  | IC3R1  | IC3R0  | 0000          |

| RPINR11     | 06B6  | _          | _        | _        | _        | _        | _        | _        | _        | OCFAR<7:0> |        |        |        |         | 0000   |        |        |               |

| RPINR12     | 06B8  | FLT2R7     | FLT2R6   | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | FLT1R7     | FLT1R6 | FLT1R5 | FLT1R4 | FLT1R3  | FLT1R2 | FLT1R1 | FLT1R0 | 0000          |

| RPINR13     | 06BA  | FLT4R7     | FLT4R6   | FLT4R5   | FLT4R4   | FLT4R3   | FLT4R2   | FLT4R1   | FLT4R0   | FLT3R7     | FLT3R6 | FLT3R5 | FLT3R4 | FLT3R3  | FLT3R2 | FLT3R1 | FLT3R0 | 0000          |

| RPINR18     | 06C4  | U1CTSR7    | U1CTSR6  | U1CTSR5  | U1CTSR4  | U1CTSR3  | U1CTSR2  | U1CTSR1  | U1CTS0   | U1RXR7     | U1RXR6 | U1RXR5 | U1RXR4 | U1RXR3  | U1RXR2 | U1RXR1 | U1RXR0 | 0000          |

| RPINR19     | 06C6  | U2CTSR7    | U2CTSR6  | U2CTSR5  | U2CTSR4  | U2CTSR3  | U2CTSR2  | U2CTSR1  | U2CTSR0  | U2RXR7     | U2RXR6 | U2RXR5 | U2RXR4 | U2RXR3  | U2RXR2 | U2RXR1 | U2RXR0 | 0000          |

| RPINR20     | 06C8  | SCK1INR7   | SCK1INR6 | SCK1INR5 | SCK1INR4 | SCK1INR3 | SCK1INR2 | SCK1INR1 | SCK1INR0 | SDI1R7     | SDI1R6 | SDI1R5 | SDI1R4 | SDI1R3  | SDI1R2 | SDI1R1 | SDI1R0 | 0000          |

| RPINR21     | 06CA  | _          | _        | _        | _        | _        | _        | _        | _        |            |        |        | SS1F   | R<7:0>  |        |        |        | 0000          |

| RPINR22     | 06CC  | SCK2INR7   | SCK2INR6 | SCK2INR5 | SCK2INR4 | SCK2INR3 | SCK2INR2 | SCK2INR1 | SCK2INR0 | SDI2R7     | SDI2R6 | SDI2R5 | SDI2R4 | SDI2R3  | SDI2R2 | SDI2R1 | SDI2R0 | 0000          |

| RPINR23     | 06CE  | _          | _        | _        | _        | _        | _        | _        | _        |            |        |        | SS2F   | R<7:0>  |        |        |        | 0000          |

| RPINR37     | 06EA  |            |          |          | SYNCI    | R<7:0>   |          |          |          | _          | —      | —      | _      | —       | —      | —      | _      | 0000          |

| RPINR38     | 06EC  | _          | —        | —        | _        | —        | —        | _        | —        |            |        |        | SYNC   | 2R<7:0> |        |        |        | 0000          |

| RPINR42     | 06F4  | FLT6R7     | FLT6R6   | FLT6R5   | FLT6R4   | FLT6R3   | FLT6R2   | FLT6R1   | FLT6R0   | FLT5R7     | FLT5R6 | FLT5R5 | FLT5R4 | FLT5R3  | FLT5R2 | FLT5R1 | FLT5R0 | 0000          |

| RPINR43     | 06F6  | FLT8R7     | FLT8R6   | FLT8R5   | FLT8R4   | FLT8R3   | FLT8R2   | FLT8R1   | FLT8R0   | FLT7R7     | FLT7R6 | FLT7R5 | FLT7R4 | FLT7R3  | FLT7R2 | FLT7R1 | FLT7R0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

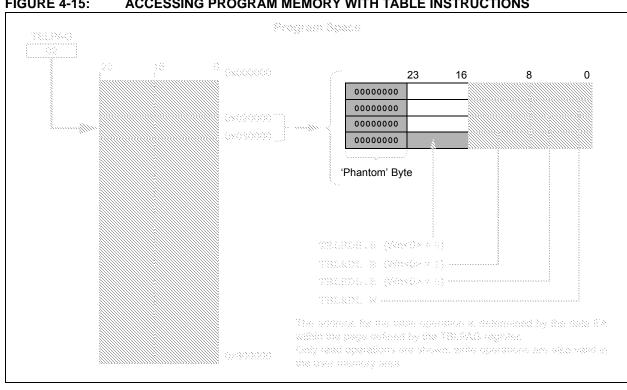

#### DATA ACCESS FROM PROGRAM 4.9.1 MEMORY USING TABLE **INSTRUCTIONS**

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### **FIGURE 4-15:** ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0          | U-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0  |

|--------------|-----|-----|-----|------|------|------|------|

| —            | —   | —   | —   | ILR3 | ILR2 | ILR1 | ILR0 |

| bit 15 bit 8 |     |     |     |      |      |      |      |

| R-0     |

|---------|---------|---------|---------|---------|---------|---------|---------|

| VECNUM7 | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7   | •       |         |         |         |         | ·       | bit 0   |

| Legend:       |                                                      |                                                                |                       |                    |  |  |  |  |  |  |

|---------------|------------------------------------------------------|----------------------------------------------------------------|-----------------------|--------------------|--|--|--|--|--|--|

| R = Readabl   | e bit                                                | W = Writable bit                                               | U = Unimplemented bit | read as '0'        |  |  |  |  |  |  |

| -n = Value at | POR                                                  | '1' = Bit is set                                               | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |  |

| bit 15-12     | Unimple                                              | mented: Read as '0'                                            |                       |                    |  |  |  |  |  |  |

| bit 11-8      | ILR<3:0>                                             | New CPU Interrupt Priority                                     | Level bits            |                    |  |  |  |  |  |  |

|               |                                                      | PU Interrupt Priority Level is                                 |                       |                    |  |  |  |  |  |  |

|               | •                                                    |                                                                |                       |                    |  |  |  |  |  |  |

|               | •                                                    |                                                                |                       |                    |  |  |  |  |  |  |

|               | •                                                    | •                                                              |                       |                    |  |  |  |  |  |  |

|               | 0001 = CPU Interrupt Priority Level is 1             |                                                                |                       |                    |  |  |  |  |  |  |

|               | 0000 = CPU Interrupt Priority Level is 0             |                                                                |                       |                    |  |  |  |  |  |  |

| bit 7-0       | VECNUM<7:0>: Vector Number of Pending Interrupt bits |                                                                |                       |                    |  |  |  |  |  |  |

|               | 1111111                                              | 1 = 255, Reserved; do not u                                    | se                    |                    |  |  |  |  |  |  |

|               | •                                                    |                                                                |                       |                    |  |  |  |  |  |  |

|               | •                                                    |                                                                |                       |                    |  |  |  |  |  |  |

|               | •                                                    |                                                                |                       |                    |  |  |  |  |  |  |

|               |                                                      | 1 = 9, IC1 – Input Capture 1<br>0 = 8, INT0 – External Interr  | upt 0                 |                    |  |  |  |  |  |  |

|               |                                                      | 10 = 8, in 10 – External inter-<br>1 = 7, Reserved; do not use | •                     |                    |  |  |  |  |  |  |

|               |                                                      | 0 = 6, Generic soft error trap                                 |                       |                    |  |  |  |  |  |  |

|               |                                                      | 1 = 5, Reserved; do not use                                    |                       |                    |  |  |  |  |  |  |

|               |                                                      | 0 = 4, Math error trap                                         |                       |                    |  |  |  |  |  |  |

|               | 0000001                                              | 1 = 3, Stack error trap                                        |                       |                    |  |  |  |  |  |  |

|               | 0000001                                              | 0 = 2, Generic hard trap                                       |                       |                    |  |  |  |  |  |  |

|               |                                                      | 1 = 1, Address error trap                                      |                       |                    |  |  |  |  |  |  |

|               | 0000000                                              | 0 = 0, Oscillator fail trap                                    |                       |                    |  |  |  |  |  |  |

# 12.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1. T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 12-2.

### 12.1 Timer Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R-0, HSC             |                                           | R-0, HSC                                 | R/W-0                   | R/W-0              | R/W-0                  | R/W-0                | R/W-0               |

|----------------------|-------------------------------------------|------------------------------------------|-------------------------|--------------------|------------------------|----------------------|---------------------|

| FLTSTAT <sup>(</sup> | <sup>1)</sup> CLSTAT <sup>(1)</sup>       | TRGSTAT                                  | FLTIEN                  | CLIEN              | TRGIEN                 | ITB <sup>(3)</sup>   | MDCS <sup>(3)</sup> |

| bit 15               |                                           |                                          |                         | •                  | •                      | •                    | bit 8               |

| R/W-0                | R/W-0                                     | U-0                                      | U-0                     | R/W-0              | R/W-0                  | R/W-0                | R/W-0               |

|                      |                                           | 0-0                                      | 0-0                     | 1                  | CAM <sup>(2,3,4)</sup> | XPRES <sup>(5)</sup> |                     |

| DTC1<br>bit 7        | DTC0                                      | _                                        |                         | MTBS               | CAM <sup>2,0,1</sup>   | XPRES <sup>(0)</sup> | IUE<br>bit (        |

|                      |                                           |                                          |                         |                    |                        |                      | Dit (               |

| Legend:              |                                           | HSC = Hardw                              | are Settable/C          | learable bit       |                        |                      |                     |

| R = Reada            | ble bit                                   | W = Writable I                           | oit                     | U = Unimplei       | mented bit, read       | l as '0'             |                     |

| -n = Value           | at POR                                    | '1' = Bit is set                         |                         | '0' = Bit is cle   | ared                   | x = Bit is unkr      | nown                |

|                      |                                           |                                          | (4)                     |                    |                        |                      |                     |

| bit 15               |                                           | ult Interrupt Sta                        |                         |                    |                        |                      |                     |

|                      |                                           | rupt is pending                          |                         |                    |                        |                      |                     |

|                      |                                           | nterrupt is pend<br>ared by setting      |                         |                    |                        |                      |                     |

| bit 14               |                                           | ent-Limit Interr                         |                         | )                  |                        |                      |                     |

|                      |                                           | nit interrupt is p                       | •                       |                    |                        |                      |                     |

|                      |                                           | t-limit interrupt                        |                         |                    |                        |                      |                     |

|                      | This bit is clea                          | ared by setting                          | CLIEN = 0.              |                    |                        |                      |                     |

| bit 13               | TRGSTAT: Tri                              | igger Interrupt S                        | Status bit              |                    |                        |                      |                     |

|                      |                                           | errupt is pendi                          |                         |                    |                        |                      |                     |

|                      |                                           | interrupt is per<br>ared by setting      |                         |                    |                        |                      |                     |

| bit 12               | FLTIEN: Fault                             | t Interrupt Enab                         | ole bit                 |                    |                        |                      |                     |

|                      |                                           | rupt is enabled<br>rupt is disabled      |                         | STAT bit is clea   | ired                   |                      |                     |

| bit 11               | CLIEN: Curre                              | nt-Limit Interru                         | pt Enable bit           |                    |                        |                      |                     |

|                      |                                           | nit interrupt is e<br>nit interrupt is c |                         | ne CLSTAT bit      | is cleared             |                      |                     |

| bit 10               | TRGIEN: Trig                              | ger Interrupt Er                         | nable bit               |                    |                        |                      |                     |

|                      |                                           | event generates                          |                         |                    | AT bit is cleared      |                      |                     |

| bit 9                | ITB: Independ                             | lent Time Base                           | Mode bit <sup>(3)</sup> |                    |                        |                      |                     |

|                      |                                           |                                          |                         | ne time base p     | eriod for this PV      | VMx generator        |                     |

|                      | 0 = PTPER re                              | gister provides                          | timing for this         | PWMx genera        | ator                   | ·                    |                     |

| bit 8                | MDCS: Maste                               | er Duty Cycle R                          | egister Select          | bit <sup>(3)</sup> |                        |                      |                     |

|                      | 1 = MDC regis                             | ster provides du                         | uty cycle inforr        | nation for this    | PWMx generate          | or                   |                     |

|                      | 0 = PDCx and                              | I SDCx register                          | s provide duty          | cycle informa      | tion for this PW       | Mx generator         |                     |

| Note 1:              | Software must cle                         | ar the interrupt                         | status here a           | nd in the corre    | sponding IFSx I        | pit in the interru   | pt controller.      |

|                      | The Independent<br>CAM bit is ignored     |                                          | de (ITB = 1) m          | ust be enabled     | I to use Center-       | Aligned mode.        | If ITB = 0, the     |

| 3:                   | These bits should                         | not be change                            | d after the PW          | /Mx is enabled     | by setting PTE         | N = 1 (PTCON         | <15>).              |

|                      | Center-Aligned m                          | -                                        |                         |                    |                        | -                    | -                   |

|                      | registers. The higl<br>the fastest clock. |                                          |                         |                    |                        |                      |                     |

|                      | ine lastest clock.                        |                                          |                         |                    |                        |                      |                     |

### **REGISTER 15-12: PWMCONX: PWMx CONTROL REGISTER (x = 1 to 5)**

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripherals or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The dsPIC33EPXXGS50X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical.

| Note: | In this section, the SPI modules are        |

|-------|---------------------------------------------|

|       | referred to together as SPIx, or separately |

|       | as SPI1 and SPI2. Special Function          |

|       | Registers follow a similar notation. For    |

|       | example, SPIxCON refers to the control      |

|       | register for the SPI1 and SPI2 modules.     |

The SPIx module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration.

The SPIx serial interface consists of four pins, as follows:

- · SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-Pin mode, SSx is not used. In 2-Pin mode, neither SDOx nor SSx is used.

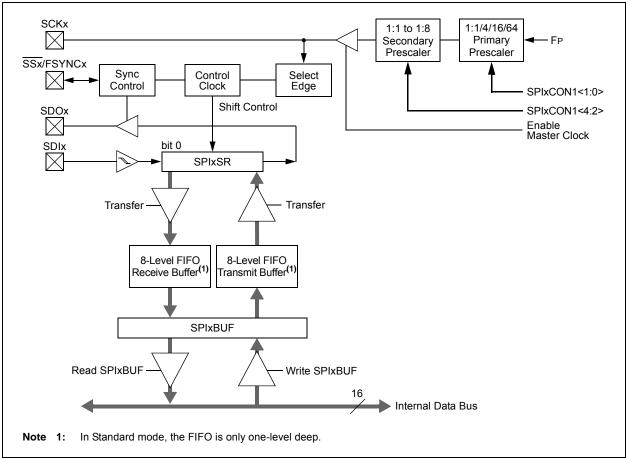

Figure 16-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

#### FIGURE 16-1: SPIX MODULE BLOCK DIAGRAM

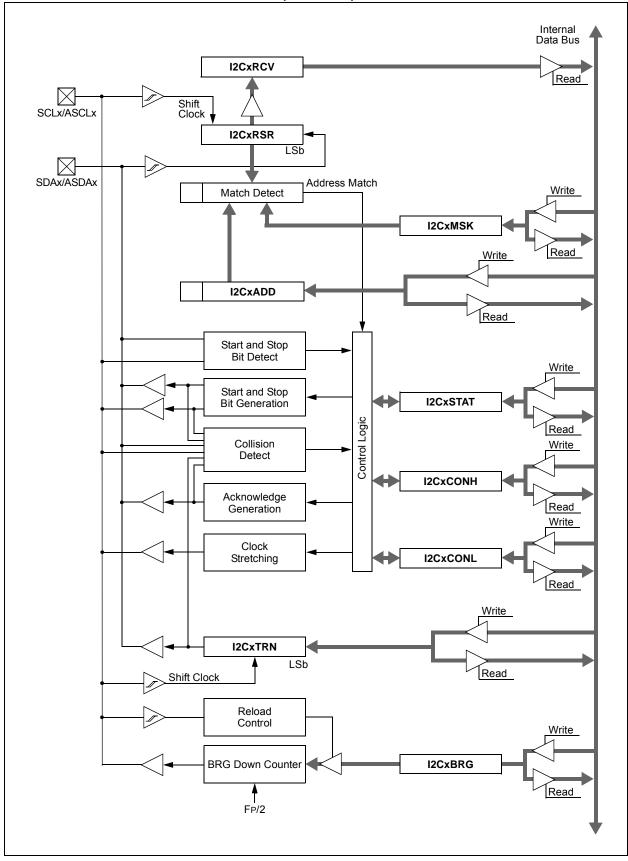

FIGURE 17-1: I2Cx BLOCK DIAGRAM (x = 1 OR 2)

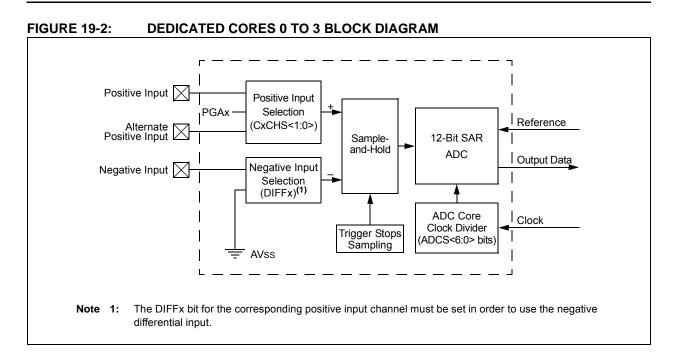

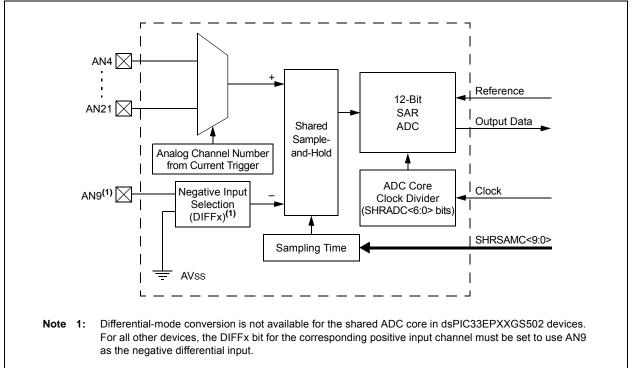

### FIGURE 19-3: SHARED CORE BLOCK DIAGRAM

### REGISTER 19-15: ADEIEL: ADC EARLY INTERRUPT ENABLE REGISTER LOW

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|----------|-------|-------|-------|--------|-------|-------|-------|

|          |       |       | EIEN  | <15:8> |       |       |       |

| bit 15   |       |       |       |        |       |       | bit 8 |

|          |       |       |       |        |       |       |       |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|          |       |       | EIEN  | <7:0>  |       |       |       |

| bit 7    |       |       |       |        |       |       | bit 0 |

| <u> </u> |       |       |       |        |       |       |       |

| Legend:  |       |       |       |        |       |       |       |

| Logona.           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

bit 15-0 EIEN<15:0>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

### REGISTER 19-16: ADEIEH: ADC EARLY INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|

| —     | —   |       | EIEN<21:16> |       |       |       |       |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 EIEN<21:16>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

# 22.3 Current Source Control Register

#### REGISTER 22-1: ISRCCON: CONSTANT-CURRENT SOURCE CONTROL REGISTER

| R/W-0                 | U-0                                                                                       | U-0                                                                                                                                                                                                                                                                                               | U-0                 | U-0              | R/W-0            | R/W-0           | R/W-0    |  |

|-----------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|------------------|-----------------|----------|--|

| ISRCEN                |                                                                                           |                                                                                                                                                                                                                                                                                                   | —                   | —                | OUTSEL2          | OUTSEL1         | OUTSEL0  |  |

| bit 15                |                                                                                           |                                                                                                                                                                                                                                                                                                   |                     |                  |                  | •<br>•          | bit 8    |  |

| U-0                   | U-0                                                                                       | R/W-0                                                                                                                                                                                                                                                                                             | R/W-0               | R/W-0            | R/W-0            | R/W-0           | R/W-0    |  |

| 0-0                   | 0-0                                                                                       | ISRCCAL5                                                                                                                                                                                                                                                                                          | ISRCCAL4            | ISRCCAL3         | ISRCCAL2         | ISRCCAL1        | ISRCCAL0 |  |

| <br>bit 7             |                                                                                           |                                                                                                                                                                                                                                                                                                   |                     |                  |                  |                 |          |  |

|                       |                                                                                           |                                                                                                                                                                                                                                                                                                   |                     |                  |                  |                 | bit C    |  |

| Legend:               |                                                                                           |                                                                                                                                                                                                                                                                                                   |                     |                  |                  |                 |          |  |

| R = Readabl           | le bit                                                                                    | W = Writable                                                                                                                                                                                                                                                                                      | bit                 | U = Unimpler     | nented bit, read | d as '0'        |          |  |

| -n = Value at         | t POR                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                                                                  |                     | '0' = Bit is cle | ared             | x = Bit is unkr | nown     |  |

|                       | •                                                                                         | led: Read as a local solution: Output Con                                                                                                                                                                                                                                                         |                     | Select bits      |                  |                 |          |  |

| bit 14-11<br>bit 10-8 | 0 = Current s<br>Unimplemen<br>OUTSEL<2:0<br>111 = Reserv<br>110 = Reserv<br>101 = Reserv | ved<br>ved                                                                                                                                                                                                                                                                                        | o'<br>stant-Current | Select bits      |                  |                 |          |  |

|                       | 011 = Input p<br>010 = Input p<br>001 = Input p                                           | in, ISRC3 (AN<br>in, ISRC2 (AN<br>in, ISRC1 (AN<br>put is selected                                                                                                                                                                                                                                | 5)<br>6)            |                  |                  |                 |          |  |

| bit 7-6               | Unimplemen                                                                                | ted: Read as '                                                                                                                                                                                                                                                                                    | 0'                  |                  |                  |                 |          |  |

| bit 5-0               | The calibratio module is ena                                                              | SRCCAL<5:0>: Constant-Current Source Calibration bits<br>The calibration value must be copied from Flash address, 0x800E78, into these bits before the<br>nodule is enabled. Refer to the calibration data address table (Table 23-3) in Section 23.0 "Special<br>Features" for more information. |                     |                  |                  |                 |          |  |

| Bit Field    | Description                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| FNOSC<2:0>   | Oscillator Selection bits                                                                                                       |

|              | 111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)                                                                             |

|              | 110 = Fast RC Oscillator with Divide-by-16                                                                                      |

|              | 101 = Low-Power RC Oscillator (LPRC)                                                                                            |

|              | 100 = Reserved; do not use                                                                                                      |

|              | 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)<br>010 = Primary Oscillator (XT, HS, EC)                         |

|              | 001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)                                                              |

|              | 000 = Fast RC Oscillator (FRC)                                                                                                  |

| FCKSM<1:0>   | Clock Switching Mode bits                                                                                                       |

|              | 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled                                                           |

|              | 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled                                                            |

|              | 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                             |

| IOL1WAY      | Peripheral Pin Select Configuration bit                                                                                         |

|              | 1 = Allows only one reconfiguration                                                                                             |

|              | 0 = Allows multiple reconfigurations                                                                                            |

| OSCIOFNC     | OSC2 Pin Function bit (except in XT and HS modes)                                                                               |

|              | 1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                   |

| POSCMD<1:0>  | Primary Oscillator Mode Select bits                                                                                             |

|              | 11 = Primary Oscillator is disabled                                                                                             |

|              | 10 = HS Crystal Oscillator mode                                                                                                 |

|              | 01 = XT Crystal Oscillator mode                                                                                                 |

|              | 00 = EC (External Clock) mode                                                                                                   |

| WDTEN<1:0>   | Watchdog Timer Enable bits                                                                                                      |

|              | 11 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the                                         |

|              | SWDTEN bit in the RCON register will have no effect)                                                                            |

|              | 10 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register) |

|              | 01 = Watchdog Timer is enabled only while device is active and is disabled while in Sleep                                       |

|              | mode; software control is disabled in this mode                                                                                 |

|              | 00 = Watchdog Timer and SWDTEN bit are disabled                                                                                 |

| WINDIS       | Watchdog Timer Window Enable bit                                                                                                |

|              | 1 = Watchdog Timer in Non-Window mode                                                                                           |

|              | 0 = Watchdog Timer in Window mode                                                                                               |

| PLLKEN       | PLL Lock Enable bit                                                                                                             |

|              | 1 = PLL lock is enabled                                                                                                         |

|              | 0 = PLL lock is disabled                                                                                                        |

| WDTPRE       | Watchdog Timer Prescaler bit                                                                                                    |

|              | 1 = 1:128<br>0 = 1:32                                                                                                           |

|              |                                                                                                                                 |

| WDTPOST<3:0> | Watchdog Timer Postscaler bits                                                                                                  |

|              | 1111 = 1:32,768<br>1110 = 1:16,384                                                                                              |

|              | •                                                                                                                               |

|              | •                                                                                                                               |

|              | •                                                                                                                               |

|              | 0001 = 1:2                                                                                                                      |

|              | 0000 = 1:1                                                                                                                      |

#### TABLE 23-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

### 26.1 DC Characteristics

#### TABLE 26-1: OPERATING MIPS vs. VOLTAGE

| Characteristic | VDD Range                   | Temperature Range | Maximum MIPS            |  |  |

|----------------|-----------------------------|-------------------|-------------------------|--|--|

| Gharacteristic | (in Volts)                  | (in °C)           | dsPIC33EPXXGS50X Family |  |  |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +85°C    | 70                      |  |  |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +125°C   | 60                      |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, PGAs and comparators) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 26-13 for the minimum and maximum BOR values.

#### TABLE 26-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min. | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  | —           | +85  | °C   |

| Extended Temperature Devices                                                                |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  | —           | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | I    | Pint + Pi/c | )    | W    |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                           | Pdmax  | (    | TJ — TA)/θJ | IA   | W    |

#### TABLE 26-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                      | Symbol | Тур. | Max. | Unit | Notes |

|-----------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-Pin TQFP 10x10x1 mm  | θJA    | 49.0 |      | °C/W | 1     |

| Package Thermal Resistance, 48-Pin TQFP 7x7x1.0 mm  | θJA    | 63.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN 8x8 mm       | θJA    | 29.0 | -    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP 10x10x1 mm  | θJA    | 50.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S 6x6x0.9 mm | θJA    | 30.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin UQFN 6x6x0.5 mm  | θJA    | 26.0 | -    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC 7.50 mm     | θJA    | 70.0 |      | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

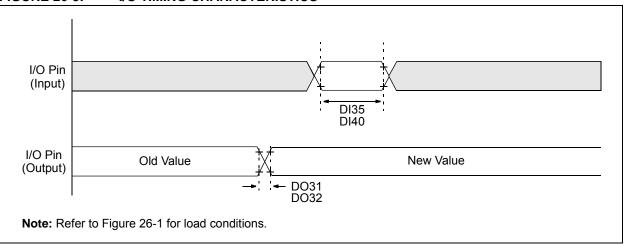

#### TABLE 26-22: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |            |

|--------------------|--------|-----------------------------------|-------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol | nbol Characteristic               |                                                       | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DO31               | TioR   | Port Output Rise Time             | _                                                     | 5                   | 10   | ns    |            |

| DO32               | TIOF   | Port Output Fall Time             | _                                                     | 5                   | 10   | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                    | _                   | _    | ns    |            |

| DI40               | Trbp   | CNx High or Low Time (input)      | 2                                                     |                     | _    | Тсү   |            |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

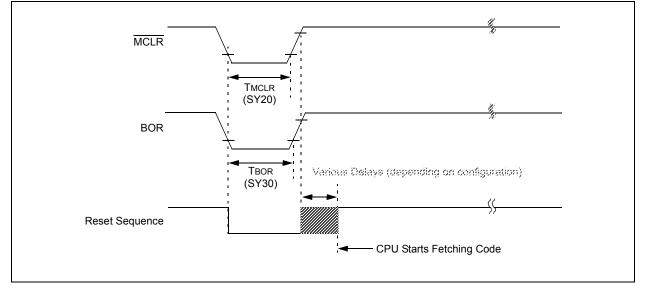

### FIGURE 26-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units            |          |          | S    |  |  |

|-------------------------|------------------|----------|----------|------|--|--|

| Dimensior               | Dimension Limits |          |          | MAX  |  |  |

| Number of Pins          | Ν                |          | 28       | -    |  |  |

| Pitch                   | е                |          | 0.65 BSC |      |  |  |

| Overall Height          | Α                | 0.80     | 0.90     | 1.00 |  |  |

| Standoff                | A1               | 0.00     | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3               | 0.20 REF |          |      |  |  |

| Overall Width           | Е                |          | 6.00 BSC |      |  |  |

| Exposed Pad Width       | E2               | 3.65     | 3.70     | 4.70 |  |  |

| Overall Length          | D                |          | 6.00 BSC |      |  |  |

| Exposed Pad Length      | D2               | 3.65     | 3.70     | 4.70 |  |  |

| Terminal Width          | b                | 0.23     | 0.30     | 0.35 |  |  |

| Terminal Length         | L                | 0.30     | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed Pad | К                | 0.20     | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2

NOTES: