Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

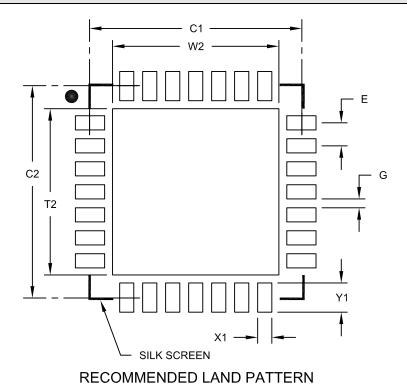

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs504-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "Multi-Tool Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

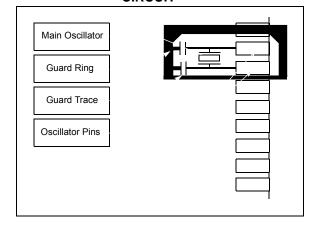

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

**CORCON: CORE CONTROL REGISTER**

REGISTER 3-2:

| R/W-0           | U-0                                                                         | R/W-0                              | R/W-0                             | R/W-0                | R-0             | R-0             | R-0   |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------|------------------------------------|-----------------------------------|----------------------|-----------------|-----------------|-------|--|--|--|--|

| VAR             |                                                                             | US1                                | US0                               | EDT <sup>(1)</sup>   | DL2             | DL1             | DL0   |  |  |  |  |

| bit 15          |                                                                             |                                    |                                   |                      |                 |                 | bit   |  |  |  |  |

| R/W-0           | R/W-0                                                                       | R/W-1                              | R/W-0                             | R/C-0                | R-0             | R/W-0           | R/W-0 |  |  |  |  |

| SATA            | SATB                                                                        | SATDW                              | ACCSAT                            | IPL3 <sup>(2)</sup>  | SFA             | RND             | IF    |  |  |  |  |

| bit 7           | OAID                                                                        | OAIDW                              | ACCOAL                            | 11 2011              | UIA             | THE             | bit   |  |  |  |  |

| Legend:         |                                                                             | C = Clearable                      | - hit                             |                      |                 |                 |       |  |  |  |  |

| R = Readable    | bit                                                                         | W = Writable                       |                                   | U = Unimpler         | mented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value at F |                                                                             | '1' = Bit is set                   |                                   | '0' = Bit is cle     |                 | x = Bit is unkn | iown  |  |  |  |  |

|                 |                                                                             | 1 - Dit 13 301                     | •                                 |                      | arcu            |                 | lowin |  |  |  |  |

| bit 15          |                                                                             | •                                  | ocessing Later                    |                      |                 |                 |       |  |  |  |  |

|                 |                                                                             | • •                                | essing is enab<br>sing is enabled |                      |                 |                 |       |  |  |  |  |

| bit 14          | Unimplemen                                                                  | ted: Read as '                     | 0'                                |                      |                 |                 |       |  |  |  |  |

| bit 13-12       | -                                                                           |                                    | igned/Signed                      | Control bits         |                 |                 |       |  |  |  |  |

|                 | 11 = Reserve                                                                |                                    | 0 0                               |                      |                 |                 |       |  |  |  |  |

|                 | 10 = DSP engine multiplies are mixed-sign                                   |                                    |                                   |                      |                 |                 |       |  |  |  |  |

|                 |                                                                             | gine multiplies<br>gine multiplies |                                   |                      |                 |                 |       |  |  |  |  |

| bit 11          | EDT: Early DO Loop Termination Control bit <sup>(1)</sup>                   |                                    |                                   |                      |                 |                 |       |  |  |  |  |

|                 | 1 = Terminate<br>0 = No effect                                              | es executing Do                    | o loop at the e                   | nd of current lo     | oop iteration   |                 |       |  |  |  |  |

| bit 10-8        | DL<2:0>: DO Loop Nesting Level Status bits                                  |                                    |                                   |                      |                 |                 |       |  |  |  |  |

|                 | 111 <b>= 7</b> do <b>lo</b>                                                 | ops are active                     |                                   |                      |                 |                 |       |  |  |  |  |

|                 | •                                                                           |                                    |                                   |                      |                 |                 |       |  |  |  |  |

|                 | •                                                                           |                                    |                                   |                      |                 |                 |       |  |  |  |  |

|                 | 001 = 1 DO lo                                                               | op is active<br>ops are active     |                                   |                      |                 |                 |       |  |  |  |  |

| bit 7           |                                                                             | •                                  |                                   |                      |                 |                 |       |  |  |  |  |

|                 | SATA: ACCA Saturation Enable bit<br>1 = Accumulator A saturation is enabled |                                    |                                   |                      |                 |                 |       |  |  |  |  |

|                 |                                                                             | itor A saturatio                   |                                   |                      |                 |                 |       |  |  |  |  |

| bit 6           | SATB: ACCB                                                                  | Saturation En                      | able bit                          |                      |                 |                 |       |  |  |  |  |

|                 |                                                                             | itor B saturatio                   |                                   |                      |                 |                 |       |  |  |  |  |

| bit 5           | SATDW: Data                                                                 | a Space Write                      | from DSP Eng                      | ine Saturation       | Enable bit      |                 |       |  |  |  |  |

|                 | 1 = Data Spac                                                               | ce write satura                    | tion is enabled                   | l                    |                 |                 |       |  |  |  |  |

| bit 4           | -                                                                           |                                    | ration Mode S                     |                      |                 |                 |       |  |  |  |  |

|                 |                                                                             | ration (super s<br>ration (normal  |                                   |                      |                 |                 |       |  |  |  |  |

| L:1 0           |                                                                             | •                                  | Level Status b                    | <sub>oit 3</sub> (2) |                 |                 |       |  |  |  |  |

| bit 3           |                                                                             | contraped monity                   |                                   |                      |                 |                 |       |  |  |  |  |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# **REGISTER 6-1:** RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ul><li>1 = Device has been in Idle mode</li><li>0 = Device has not been in Idle mode</li></ul>                         |

| bit 1 | BOR: Brown-out Reset Flag bit                                                                                           |

|       | <ul><li>1 = A Brown-out Reset has occurred</li><li>0 = A Brown-out Reset has not occurred</li></ul>                     |

| bit 0 | POR: Power-on Reset Flag bit                                                                                            |

|       | <ul><li>1 = A Power-on Reset has occurred</li><li>0 = A Power-on Reset has not occurred</li></ul>                       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

### TABLE 7-1: INTERRUPT VECTOR DETAILS

|                                      | Vector | IRQ       |                     | Inte     | errupt Bit Lo | cation      |

|--------------------------------------|--------|-----------|---------------------|----------|---------------|-------------|

| Interrupt Source                     | #      | #         | IVT Address         | Flag     | Enable        | Priority    |

|                                      | Hi     | ghest Nat | ural Order Priority | •        |               |             |

| INT0 – External Interrupt 0          | 8      | 0         | 0x000014            | IFS0<0>  | IEC0<0>       | IPC0<2:0>   |

| IC1 – Input Capture 1                | 9      | 1         | 0x000016            | IFS0<1>  | IEC0<1>       | IPC0<6:4>   |

| OC1 – Output Compare 1               | 10     | 2         | 0x000018            | IFS0<2>  | IEC0<2>       | IPC0<10:8>  |

| T1 – Timer1                          | 11     | 3         | 0x00001A            | IFS0<3>  | IEC0<3>       | IPC0<14:12> |

| Reserved                             | 12     | 4         | 0x00001C            | _        |               | _           |

| IC2 – Input Capture 2                | 13     | 5         | 0x00001E            | IFS0<5>  | IEC0<5>       | IPC1<6:4>   |

| OC2 – Output Compare 2               | 14     | 6         | 0x000020            | IFS0<6>  | IEC0<6>       | IPC1<10:8>  |

| T2 – Timer2                          | 15     | 7         | 0x000022            | IFS0<7>  | IEC0<7>       | IPC1<14:12> |

| T3 – Timer3                          | 16     | 8         | 0x000024            | IFS0<8>  | IEC0<8>       | IPC2<2:0>   |

| SPI1E – SPI1 Error                   | 17     | 9         | 0x000026            | IFS0<9>  | IEC0<9>       | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done            | 18     | 10        | 0x000028            | IFS0<10> | IEC0<10>      | IPC2<10:8>  |

| U1RX – UART1 Receiver                | 19     | 11        | 0x00002A            | IFS0<11> | IEC0<11>      | IPC2<14:12> |

| U1TX – UART1 Transmitter             | 20     | 12        | 0x00002C            | IFS0<12> | IEC0<12>      | IPC3<2:0>   |

| ADC – ADC Global Convert Done        | 21     | 13        | 0x00002E            | IFS0<13> | IEC0<13>      | IPC3<6:4>   |

| Reserved                             | 22     | 14        | 0x000030            | _        | _             | _           |

| NVM – NVM Write Complete             | 23     | 15        | 0x000032            | IFS0<15> | IEC0<15>      | IPC3<14:12> |

| SI2C1 – I2C1 Slave Event             | 24     | 16        | 0x000034            | IFS1<0>  | IEC1<0>       | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event            | 25     | 17        | 0x000036            | IFS1<1>  | IEC1<1>       | IPC4<6:4>   |

| CMP1 – Analog Comparator 1 Interrupt | 26     | 18        | 0x000038            | IFS1<2>  | IEC1<2>       | IPC4<10:8>  |

| CN – Input Change Interrupt          | 27     | 19        | 0x00003A            | IFS1<3>  | IEC1<3>       | IPC4<14:12> |

| INT1 – External Interrupt 1          | 28     | 20        | 0x00003C            | IFS1<4>  | IEC1<4>       | IPC5<2:0>   |

| Reserved                             | 29-32  | 21-24     | 0x00003E-0x000044   | _        | _             | _           |

| OC3 – Output Compare 3               | 33     | 25        | 0x000046            | IFS1<9>  | IEC1<9>       | IPC6<6:4>   |

| OC4 – Output Compare 4               | 34     | 26        | 0x000048            | IFS1<10> | IEC1<10>      | IPC6<10:8>  |

| T4 – Timer4                          | 35     | 27        | 0x00004A            | IFS1<11> | IEC1<11>      | IPC6<14:12> |

| T5 – Timer5                          | 36     | 28        | 0x00004C            | IFS1<12> | IEC1<12>      | IPC7<2:0>   |

| INT2 – External Interrupt 2          | 37     | 29        | 0x00004E            | IFS1<13> | IEC1<13>      | IPC7<6:4>   |

| U2RX – UART2 Receiver                | 38     | 30        | 0x000050            | IFS1<14> | IEC1<14>      | IPC7<10:8>  |

| U2TX – UART2 Transmitter             | 39     | 31        | 0x000052            | IFS1<15> | IEC1<15>      | IPC7<14:12> |

| SPI2E – SPI2 Error                   | 40     | 32        | 0x000054            | IFS2<0>  | IEC2<0>       | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done            | 41     | 33        | 0x000056            | IFS2<1>  | IEC2<1>       | IPC8<6:4>   |

| Reserved                             | 42-44  | 34-36     | 0x000058-0x00005C   | —        | _             | _           |

| IC3 – Input Capture 3                | 45     | 37        | 0x00005E            | IFS2<5>  | IEC2<5>       | IPC9<6:4>   |

| IC4 – Input Capture 4                | 46     | 38        | 0x000060            | IFS2<6>  | IEC2<6>       | IPC9<10:8>  |

| Reserved                             | 47-56  | 39-48     | 0x000062-0x000074   | _        | _             | _           |

| SI2C2 – I2C2 Slave Event             | 57     | 49        | 0x000076            | IFS3<1>  | IEC3<1>       | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event            | 58     | 50        | 0x000078            | IFS3<2>  | IEC3<2>       | IPC12<10:8> |

| Reserved                             | 59-61  | 51-53     | 0x00007A-0x00007E   | _        | _             | _           |

| INT4 – External Interrupt 4          | 62     | 54        | 0x000080            | IFS3<6>  | IEC3<6>       | IPC13<10:8> |

| Reserved                             | 63-64  | 55-54     | 0x000082-0x000084   | —        |               | _           |

| PSEM – PWM Special Event Match       | 65     | 57        | 0x000086            | IFS3<9>  | IEC3<9>       | IPC14<6:4>  |

| Reserved                             | 66-72  | 58-64     | 0x000088-0x000094   | —        |               | _           |

| U1E – UART1 Error Interrupt          | 73     | 65        | 0x000096            | IFS4<1>  | IEC4<1>       | IPC16<6:4>  |

| U2E – UART2 Error Interrupt          | 74     | 66        | 0x000098            | IFS4<2>  | IEC4<2>       | IPC16<10:8> |

| Reserved                             | 75-80  | 67-72     | 0x00009A-0x0000A4   | —        |               | _           |

#### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| R/W-0           | U-0                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| ROON            |                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                           | ROSEL                                                                                                                                                                                                | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15          |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       | bit 8                 |  |  |  |

| U-0             | U-0                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                  | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

| _               | _                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                    |                       | —                     | —                     | _                     |  |  |  |

| bit 7           |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       | bit C                 |  |  |  |

| Legend:         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

| R = Readable    | bit                                                                                                                                                                                                          | W = Writable b                                                                                                                                                                                                                                                                                                                                   | bit                                                                                                                                                                                                  | U = Unimplem          | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at F |                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                      | '0' = Bit is clea     |                       | x = Bit is unkr       | nown                  |  |  |  |

|                 |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

| bit 15          | 1 = Reference                                                                                                                                                                                                | ence Oscillator<br>e oscillator outp<br>e oscillator outp                                                                                                                                                                                                                                                                                        | ut is enabled of                                                                                                                                                                                     |                       | 2)                    |                       |                       |  |  |  |

| bit 14          | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                    |                       |                       |                       |                       |  |  |  |

| bit 13          | ROSSLP: Re                                                                                                                                                                                                   | ference Oscillat                                                                                                                                                                                                                                                                                                                                 | or Run in Slee                                                                                                                                                                                       | ep bit                |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                              | e oscillator outp<br>e oscillator outp                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

| bit 12          | ROSEL: Refe                                                                                                                                                                                                  | OSEL: Reference Oscillator Source Select bit                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                              | crystal is used ock is used as                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

| bit 11-8        | •                                                                                                                                                                                                            | Reference Osc                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

|                 | 1110 = Refer<br>1101 = Refer<br>1100 = Refer<br>1011 = Refer<br>1010 = Refer<br>1000 = Refer<br>0111 = Refer<br>0110 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer | ence clock divic<br>ence clock divic | led by 16,384<br>led by 8,192<br>led by 4,096<br>led by 2,048<br>led by 1,024<br>led by 512<br>led by 512<br>led by 256<br>led by 128<br>led by 64<br>led by 32<br>led by 16<br>led by 8<br>led by 4 |                       |                       |                       |                       |  |  |  |

| bit 7-0         | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                    |                       |                       |                       |                       |  |  |  |

|                 | •                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                       |                       |                       |                       |  |  |  |

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

### 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control x register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 26-11 for the maximum VIH specification for each pin.

### 10.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP, as shown in Example 10-1.

## **10.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the ICN functionality of each I/O port. The CNENx registers contain the ICN interrupt enable control bits for each of the input pins. Setting any of these bits enables an ICN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source, or sink source, connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on Input Change Notification pins should always be disabled when the port pin is configured as a digital output.

#### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

| R/W-0           | R/W-0                                  | R/W-0                                                                                           | R/W-0              | R/W-0                | R/W-0            | R/W-0              | R/W-0  |

|-----------------|----------------------------------------|-------------------------------------------------------------------------------------------------|--------------------|----------------------|------------------|--------------------|--------|

| T1CKR7          | T1CKR6                                 | T1CKR5                                                                                          | T1CKR4             | T1CKR3               | T1CKR2           | T1CKR1             | T1CKR0 |

| bit 15          |                                        |                                                                                                 |                    |                      |                  |                    | bit 8  |

|                 |                                        |                                                                                                 |                    |                      |                  |                    |        |

| U-0             | U-0                                    | U-0                                                                                             | U-0                | U-0                  | U-0              | U-0                | U-0    |

| —               | —                                      | —                                                                                               | —                  | —                    | -                | —                  | —      |

| bit 7           |                                        |                                                                                                 |                    |                      |                  | •                  | bit 0  |

|                 |                                        |                                                                                                 |                    |                      |                  |                    |        |

| Legend:         |                                        |                                                                                                 |                    |                      |                  |                    |        |

| R = Readable    | bit                                    | W = Writable                                                                                    | bit                | U = Unimpler         | nented bit, read | as '0'             |        |

| -n = Value at P | OR                                     | '1' = Bit is set                                                                                |                    | '0' = Bit is cleared |                  | x = Bit is unknown |        |

| bit 15-8        | 10110101 =<br>10110100 =<br>00000001 = | : Assign Timer'<br>Input tied to RF<br>Input tied to RF<br>Input tied to RF<br>Input tied to Vs | 2181<br>2180<br>21 | ck (T1CK) to t       | he Correspondi   | ng RPn Pin bits    | 5      |

#### REGISTER 10-3: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2

bit 7-0 Unimplemented: Read as '0'

### REGISTER 10-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| OCFAR7 | OCFAR6 | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 OCFAR<7:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180

00000001 = Input tied to RP1 00000000 = Input tied to Vss

| R/W-0           | R/W-0                                            | R/W-0                                                                                         | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|---------|

| U1CTSR7         | U1CTSR6                                          | U1CTSR5                                                                                       | U1CTSR4          | U1CTSR3          | U1CTSR2          | U1CTSR1         | U1CTSR0 |

| bit 15          |                                                  |                                                                                               | ·                |                  |                  |                 | bit 8   |

|                 |                                                  |                                                                                               |                  |                  |                  |                 |         |

| R/W-0           | R/W-0                                            | R/W-0                                                                                         | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| U1RXR7          | U1RXR6                                           | U1RXR5                                                                                        | U1RXR4           | U1RXR3           | U1RXR2           | U1RXR1          | U1RXR0  |

| bit 7           |                                                  |                                                                                               |                  |                  |                  |                 | bit 0   |

| <u> </u>        |                                                  |                                                                                               |                  |                  |                  |                 |         |

| Legend:         |                                                  |                                                                                               |                  |                  |                  |                 |         |

| R = Readable    |                                                  | W = Writable                                                                                  |                  | •                | nented bit, read |                 |         |

| -n = Value at F | POR                                              | '1' = Bit is set                                                                              |                  | '0' = Bit is cle | ared             | x = Bit is unkr | iown    |

| bit 7-0         | 10110100 =<br>•<br>•<br>00000001 =<br>00000000 = | Input tied to RF<br>Input tied to RF<br>Input tied to RF<br>Input tied to Vs<br>: Assign UART | 2180<br>21<br>35 | 1RX) to the Co   | rresponding RF   | n Pin bits      |         |

### REGISTER 10-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

### REGISTER 10-14: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0         | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0            | R/W-0            | R/W-0              | R/W-0    |

|---------------|------------------------------------|------------------------------------------------------------------------------|--------------|------------------|------------------|--------------------|----------|

| SCK2INR7      | SCK2INR6                           | SCK2INR5                                                                     | SCK2INR4     | SCK2INR3         | SCK2INR2         | SCK2INR1           | SCK2INR0 |

| bit 15        |                                    |                                                                              |              |                  |                  |                    | bit 8    |

| R/W-0         | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0            | R/W-0            | R/W-0              | R/W-0    |

| SDI2R7        | SDI2R6                             | SDI2R5                                                                       | SDI2R4       | SDI2R3           | SDI2R2           | SDI2R1             | SDI2R0   |

| bit 7         |                                    |                                                                              |              |                  |                  |                    | bit (    |

| Legend:       |                                    |                                                                              |              |                  |                  |                    |          |

| R = Readable  | bit                                | W = Writable                                                                 | bit          | U = Unimpler     | nented bit, read | l as '0'           |          |

| -n = Value at | POR                                | '1' = Bit is set                                                             |              | '0' = Bit is cle | ared             | x = Bit is unknown |          |

|               | 10110100 =<br>•<br>•<br>00000001 = | Input tied to Rf<br>Input tied to Rf<br>Input tied to Rf<br>Input tied to Vs | 2180<br>21   |                  |                  |                    |          |

| bit 7-0       | 10110101 =                         | Input tied to RF<br>Input tied to RF                                         | 2181<br>2180 | 12) to the Corre | esponding RPn    | Pin bits           |          |

#### REGISTER 10-36: RPOR16: PERIPHERAL PIN SELECT OUTPUT REGISTER 16

| U-0             | U-0    | R/W-0            | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|--------|------------------|---------|------------------|------------------|-----------------|---------|

| —               | _      | RP177R5          | RP177R4 | RP177R3          | RP177R2          | RP177R1         | RP177R0 |

| bit 15          | -<br>- |                  |         |                  |                  | •               | bit 8   |

| U-0             | U-0    | R/W-0            | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| _               | _      | RP176R5          | RP176R4 | RP176R3          | RP176R2          | RP176R1         | RP176R0 |

| bit 7           |        |                  |         |                  |                  |                 | bit C   |

| Legend:         |        |                  |         |                  |                  |                 |         |

| R = Readable    | bit    | W = Writable     | bit     | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value at I | POR    | '1' = Bit is set |         | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 13-8 | RP177R<5:0>: Peripheral Output Function is Assigned to RP177 Output Pin bits |

|----------|------------------------------------------------------------------------------|

|          | (see Table 10-2 for peripheral function numbers)                             |

| bit 7-6  | Unimplemented: Read as '0'                                                   |

| bit 5-0  | RP176R<5:0>: Peripheral Output Function is Assigned to RP176 Output Pin bits |

# (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-37: RPOR17: PERIPHERAL PIN SELECT OUTPUT REGISTER 17

| U-0                           | U-0 | R/W-0                         | R/W-0            | R/W-0                              | R/W-0                | R/W-0              | R/W-0              |  |  |

|-------------------------------|-----|-------------------------------|------------------|------------------------------------|----------------------|--------------------|--------------------|--|--|

| —                             | —   | RP179R5                       | RP179R4          | RP179R3                            | RP179R2              | RP179R1            | RP179R0            |  |  |

| bit 15                        |     |                               |                  |                                    |                      |                    | bit 8              |  |  |

| <b></b>                       |     |                               |                  |                                    |                      |                    |                    |  |  |

| U-0                           | U-0 | R/W-0                         | R/W-0            | R/W-0                              | R/W-0                | R/W-0              | R/W-0              |  |  |

| —                             | —   | RP178R5                       | RP178R4          | RP178R3                            | RP178R2              | RP178R1            | RP178R0            |  |  |

| bit 7                         |     |                               |                  |                                    |                      |                    | bit 0              |  |  |

|                               |     |                               |                  |                                    |                      |                    |                    |  |  |

| Legend:                       |     |                               |                  |                                    |                      |                    |                    |  |  |

| R = Readable bit W = Writable |     |                               | bit              | U = Unimplemented bit, read as '0' |                      |                    |                    |  |  |

| -n = Value at POR '1'         |     | '1' = Bit is set              | '1' = Bit is set |                                    | '0' = Bit is cleared |                    | x = Bit is unknown |  |  |

| -n = Value at POR             |     | Value at POR '1' = Bit is set |                  | '0' = Bit is cle                   | eared                | x = Bit is unknown |                    |  |  |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 10-2 for peripheral function numbers)

### REGISTER 17-1: I2CxCONL: I2Cx CONTROL REGISTER LOW (CONTINUED)

| bit 6 | STREN: SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Used in conjunction with the SCLREL bit.                                                                                                               |

|       | <ul> <li>1 = Enables software or receives clock stretching</li> <li>0 = Disables software or receives clock stretching</li> </ul>                      |

| 54 C  | C C                                                                                                                                                    |

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                       |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge                                    |

|       | 0 = Sends ACK during Acknowledge                                                                                                                       |

| bit 4 | ACKEN: Acknowledge Sequence Enable bit                                                                                                                 |

|       | (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                          |

|       | 1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit; hardware is clear at the end of the master Acknowledge sequence |

|       | 0 = Acknowledge sequence is not in progress                                                                                                            |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                            |

|       | 1 = Enables Receive mode for I <sup>2</sup> C; hardware is clear at the end of the eighth bit of the master receive data byte                          |

|       | 0 = Receive sequence is not in progress                                                                                                                |

| bit 2 | PEN: Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                             |

|       | 1 = Initiates Stop condition on SDAx and SCLx pins; hardware is clear at the end of the master Stop sequence                                           |

|       | 0 = Stop condition is not in progress                                                                                                                  |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                           |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins; hardware is clear at the end of the master Repeated Start sequence                       |

|       | 0 = Repeated Start condition is not in progress                                                                                                        |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                            |

|       | 1 = Initiates Start condition on SDAx and SCLx pins; hardware is clear at the end of the master Start sequence                                         |

0 = Start condition is not in progress

### REGISTER 20-1: CMPxCON: COMPARATOR x CONTROL REGISTER (CONTINUED)

| bit 5 | EXTREF: Enable External Reference bit                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = External source provides reference to DACx (maximum DAC voltage is determined by the external<br/>voltage source)</li> </ul>                                 |

|       | 0 = AVDD provides reference to DACx (maximum DAC voltage is AVDD)                                                                                                         |

| bit 4 | HYSPOL: Comparator Hysteresis Polarity Select bit                                                                                                                         |

|       | <ul> <li>1 = Hysteresis is applied to the falling edge of the comparator output</li> <li>0 = Hysteresis is applied to the rising edge of the comparator output</li> </ul> |

| bit 3 | CMPSTAT: Comparator Current State bit                                                                                                                                     |

|       | Reflects the current output state of Comparator x, including the setting of the CMPPOL bit.                                                                               |

| bit 2 | ALTINP: Alternate Input Select bit                                                                                                                                        |

|       | 1 = INSEL<1:0> bits select alternate inputs                                                                                                                               |

|       | 0 = INSEL<1:0> bits select comparator inputs                                                                                                                              |

| bit 1 | CMPPOL: Comparator Output Polarity Control bit                                                                                                                            |

|       | 1 = Output is inverted                                                                                                                                                    |

|       | 0 = Output is non-inverted                                                                                                                                                |

| bit 0 | RANGE: DACx Output Voltage Range Select bit                                                                                                                               |

|       | 1 = AVDD is the maximum DACx output voltage                                                                                                                               |

|       | 0 = Unimplemented, do not use                                                                                                                                             |

|       |                                                                                                                                                                           |

**Note 1:** DACOUTx can be associated only with a single comparator at any given time. The software must ensure that multiple comparators do not enable the DACx output by setting their respective DACOE bit.

# 22.3 Current Source Control Register

#### REGISTER 22-1: ISRCCON: CONSTANT-CURRENT SOURCE CONTROL REGISTER

| R/W-0                 | U-0                                                                                       | U-0                                                                                                                                                                                                                                                                                                                                                             | U-0                 | U-0              | R/W-0            | R/W-0           | R/W-0    |  |  |

|-----------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|------------------|-----------------|----------|--|--|

| ISRCEN                |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                 | —                   | —                | OUTSEL2          | OUTSEL1         | OUTSEL0  |  |  |

| bit 15                |                                                                                           | •                                                                                                                                                                                                                                                                                                                                                               | •                   | •                |                  |                 | bit 8    |  |  |

| U-0                   | U-0                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                           | R/W-0               | R/W-0            | R/W-0            | R/W-0           | R/W-0    |  |  |

| 0-0                   | 0-0                                                                                       | ISRCCAL5                                                                                                                                                                                                                                                                                                                                                        | ISRCCAL4            | ISRCCAL3         | ISRCCAL2         | ISRCCAL1        | ISRCCAL0 |  |  |

| <br>bit 7             |                                                                                           | ISRCCALS                                                                                                                                                                                                                                                                                                                                                        | ISRUUAL4            | ISRUUALS         | ISRCCALZ         | ISRCCALT        | bit (    |  |  |

|                       |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                 |                     |                  |                  |                 | DILC     |  |  |

| Legend:               |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                 |                     |                  |                  |                 |          |  |  |

| R = Readabl           | le bit                                                                                    | W = Writable                                                                                                                                                                                                                                                                                                                                                    | bit                 | U = Unimpler     | nented bit, read | d as '0'        |          |  |  |

| -n = Value at         | t POR                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                |                     | '0' = Bit is cle | ared             | x = Bit is unkr | nown     |  |  |

|                       | •                                                                                         | >: Output Con                                                                                                                                                                                                                                                                                                                                                   |                     | Select bits      |                  |                 |          |  |  |

| bit 14-11<br>bit 10-8 | 0 = Current s<br>Unimplemen<br>OUTSEL<2:0<br>111 = Reserv<br>110 = Reserv<br>101 = Reserv | ved<br>ved                                                                                                                                                                                                                                                                                                                                                      | o'<br>stant-Current | Select bits      |                  |                 |          |  |  |

|                       | 011 = Input p<br>010 = Input p<br>001 = Input p                                           | in, ISRC3 (AN<br>in, ISRC2 (AN<br>in, ISRC1 (AN<br>put is selected                                                                                                                                                                                                                                                                                              | 5)<br>6)            |                  |                  |                 |          |  |  |

| bit 7-6               | Unimplemen                                                                                | ted: Read as '                                                                                                                                                                                                                                                                                                                                                  | 0'                  |                  |                  |                 |          |  |  |

| bit 5-0               | The calibratio module is ena                                                              | <ul> <li>Jnimplemented: Read as '0'</li> <li>SRCCAL&lt;5:0&gt;: Constant-Current Source Calibration bits</li> <li>The calibration value must be copied from Flash address, 0x800E78, into these bits before the nodule is enabled. Refer to the calibration data address table (Table 23-3) in Section 23.0 "Special Features" for more information.</li> </ul> |                     |                  |                  |                 |          |  |  |

# TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier Working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                        |

| Wm*Wn | Multiplicand and Multiplier Working register pair for DSP instructions $\in$ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                       |