Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs504-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

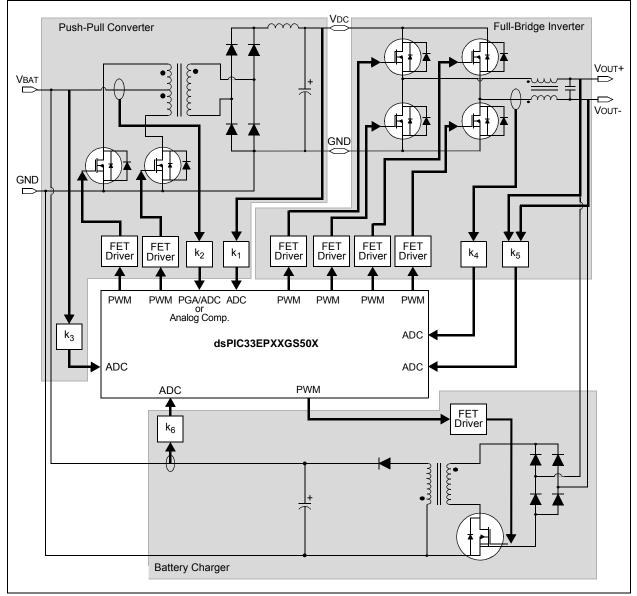

### FIGURE 2-6: OFF-LINE UPS

#### **TABLE 4-3**: **INTERRUPT CONTROLLER REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15                   | Bit 14                   | Bit 13                   | Bit 12                   | Bit 11                   | Bit 10                   | Bit 9                    | Bit 8                   | Bit 7                   | Bit 6    | Bit 5    | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0                    | All<br>Resets |

|-------------|-------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|-------------------------|-------------------------|----------|----------|-----------|-----------|-----------|-----------|--------------------------|---------------|

| IFS0        | 0800  | NVMIF                    | -                        | ADCIF                    | U1TXIF                   | U1RXIF                   | SPI1IF                   | SPI1EIF                  | T3IF                    | T2IF                    | OC2IF    | IC2IF    | -         | T1IF      | OC1IF     | IC1IF     | INTOIF                   | 0000          |

| IFS1        | 0802  | U2TXIF                   | U2RXIF                   | INT2IF                   | T5IF                     | T4IF                     | OC4IF                    | OC3IF                    | -                       | _                       | -        | -        | INT1IF    | CNIF      | AC1IF     | MI2C1IF   | SI2C1IF                  | 0000          |

| IFS2        | 0804  | _                        | -                        | _                        | _                        | _                        | _                        | —                        | -                       | _                       | IC4IF    | IC3IF    | -         | _         | _         | SPI2IF    | SPI2EIF                  | 0000          |

| IFS3        | 0806  | _                        | _                        | _                        | _                        | _                        | _                        | PSEMIF                   | _                       | _                       | INT4IF   | _        | _         | _         | MI2C2IF   | SI2C2IF   | -                        | 0000          |

| IFS4        | 0808  | -                        | -                        | -                        | -                        | -                        | -                        | PSESIF                   | -                       | -                       | -        | -        | -         | -         | U2EIF     | U1EIF     | -                        | 0000          |

| IFS5        | 080A  | PWM2IF                   | PWM1IF                   | _                        | _                        | _                        | _                        | _                        | _                       |                         | _        | _        | _         | _         | -         | -         | -                        | 0000          |

| IFS6        | 080C  | ADCAN1IF                 | ADCAN0IF                 | —                        | _                        | _                        | _                        | AC4IF                    | AC3IF                   | AC2IF                   |          | _        | _         | _         | PWM5IF    | PWM4IF    | PWM3IF                   | 0000          |

| IFS7        | 080E  | -                        | -                        | -                        | -                        | -                        | -                        | -                        | -                       | -                       | -        | ADCAN7IF | ADCAN6IF  | ADCAN5IF  | ADCAN4IF  | ADCAN3IF  | ADCAN2IF                 | 0000          |

| IFS8        | 0810  | JTAGIF                   | ICDIF                    | -                        | -                        | -                        | -                        | -                        | -                       | -                       | -        | -        | -         | -         | -         | -         | -                        | 0000          |

| IFS9        | 0812  | ADCAN16IF <sup>(1)</sup> | ADCAN15IF <sup>(1)</sup> | ADCAN14IF <sup>(2)</sup> | ADCAN13IF(1)             | ADCAN12IF <sup>(2)</sup> | ADCAN11IF <sup>(2)</sup> | ADCAN10IF <sup>(2)</sup> | ADCAN9IF <sup>(2)</sup> | ADCAN8IF <sup>(2)</sup> | _        | _        | _         | _         | -         | -         | -                        | 0000          |

| IFS10       | 0814  | -                        | I2C2BCIF                 | I2C1BCIF                 | -                        | -                        | _                        | -                        | -                       | _                       | -        | -        | ADCAN21IF | ADCAN20IF | ADCAN19IF | ADCAN18IF | ADCAN17IF <sup>(2)</sup> | 0000          |

| IFS11       | 0816  | _                        | -                        | _                        | _                        | _                        | _                        | _                        | -                       | _                       | _        | _        | ADFLTR1IF | ADFLTR0IF | ADCMP1IF  | ADCMP0IF  | -                        | 0000          |

| IEC0        | 0820  | NVMIE                    | -                        | ADCIE                    | U1TXIE                   | U1RXIE                   | SPI1IE                   | SPI1EIE                  | T3IE                    | T2IE                    | OC2IE    | IC2IE    | -         | T1IE      | OC1IE     | IC1IE     | INTOIE                   | 0000          |

| IEC1        | 0822  | U2TXIE                   | U2RXIE                   | INT2IE                   | T5IE                     | T4IE                     | OC4IE                    | OC3IE                    | -                       | _                       | _        | -        | INT1IE    | CNIE      | AC1IF     | MI2C1IE   | SI2C1IE                  | 0000          |

| IEC2        | 0824  | _                        | _                        | _                        | _                        | _                        | _                        | _                        | _                       | _                       | IC4IE    | IC3IE    | -         | _         | _         | SPI2IE    | SPI2EIE                  | 0000          |

| IEC3        | 0826  | _                        | _                        | _                        | _                        | _                        | _                        | PSEMIE                   | _                       | _                       | INT4IE   | _        | -         | _         | MI2C2IE   | SI2C2IE   | -                        | 0000          |

| IEC4        | 0828  | _                        | _                        | _                        | -                        | _                        | _                        | PSESIE                   | -                       | _                       | _        | _        | -         | -         | U2EIE     | U1EIE     | -                        | 0000          |

| IEC5        | 082A  | PWM2IE                   | PWM1IE                   | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC6        | 082C  | ADCAN1IE                 | ADCAN0IE                 | _                        | _                        | _                        | _                        | AC4IE                    | AC3IE                   | AC2IE                   | _        | _        | -         | _         | PWM5IE    | PWM4IE    | PWM3IE                   | 0000          |

| IEC7        | 082E  | _                        | _                        | _                        | -                        | _                        | _                        | _                        | -                       | _                       | _        | ADCAN7IE | ADCAN6IE  | ADCAN5IE  | ADCAN4IE  | ADCAN3IE  | ADCAN2IE                 | 0000          |

| IEC8        | 0830  | JTAGIE                   | ICDIE                    | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC9        | 0832  | ADCAN16IE <sup>(1)</sup> | ADCAN15IE <sup>(1)</sup> | ADCAN14IE <sup>(2)</sup> | ADCAN13IE <sup>(1)</sup> | ADCAN12IE <sup>(2)</sup> | ADCAN11IE <sup>(2)</sup> | ADCAN10IE <sup>(2)</sup> | ADCAN9IE <sup>(2)</sup> | ADCAN8IE <sup>(2)</sup> | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC10       | 0834  | _                        | I2C2BCIE                 | I2C1BCIE                 | -                        | _                        | _                        | _                        | -                       | _                       | _        | _        | ADCAN21IE | ADCAN20IE | ADCAN19IE | ADCAN18IE | ADCAN17IE <sup>(2)</sup> | 0000          |

| IEC11       | 0836  | _                        | _                        | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | ADFLTR1IE | ADFLTR0IE | ADCMP1IE  | ADCMP0IE  | -                        | 0000          |

| IPC0        | 0840  | _                        | T1IP2                    | T1IP1                    | T1IP0                    | _                        | OC1IP2                   | OC1IP1                   | OC1IP0                  | _                       | IC1IP2   | IC1IP1   | IC1IP0    | -         | INT0IP2   | INT0IP1   | INT0IP0                  | 4444          |

| IPC1        | 0842  | -                        | T2IP2                    | T2IP1                    | T2IP0                    | -                        | OC2IP2                   | OC2IP1                   | OC2IP0                  | _                       | IC2IP2   | IC2IP1   | IC2IP0    | -         | -         | -         | -                        | 4440          |

| IPC2        | 0844  | _                        | U1RXIP2                  | U1RXIP1                  | U1RXIP0                  | _                        | SPI1IP2                  | SPI1IP1                  | SPI1IP0                 | _                       | SPI1EIP2 | SPI1EIP1 | SPI1EIP0  | -         | T3IP2     | T3IP1     | T3IP0                    | 4444          |

| IPC3        | 0846  | _                        | NVMIP2                   | NVMIP1                   | NVMIP0                   | _                        | _                        | _                        | _                       | _                       | ADCIP2   | ADCIP1   | ADCIP0    | -         | U1TXIP2   | U1TXIP1   | U1TXIP0                  | 4044          |

| IPC4        | 0848  | _                        | CNIP2                    | CNIP1                    | CNIP0                    | _                        | AC1IP2                   | AC1IP1                   | AC1IP0                  | _                       | MI2C1IP2 | MI2C1IP1 | MI2C1IP0  | -         | SI2C1IP2  | SI2C1IP1  | SI2C1IP0                 | 4444          |

| IPC5        | 084A  | _                        | -                        | _                        | -                        | _                        | -                        | -                        | -                       | _                       | —        | -        | -         | -         | INT1IP2   | INT1IP1   | INT1IP0                  | 0004          |

| IPC6        | 084C  | _                        | T4IP2                    | T4IP1                    | T4IP0                    | _                        | OC4IP2                   | OC4IP1                   | OC4IP0                  | _                       | OC3IP2   | OC3IP1   | OC3IP0    | -         | -         | -         | -                        | 4440          |

| IPC7        | 084E  | _                        | U2TXIP2                  | U2TXIP1                  | U2TXIP0                  | _                        | U2RXIP2                  | U2RXIP1                  | U2RXIP0                 | _                       | INT2IP2  | INT2IP1  | INT2IP0   | _         | T5IP2     | T5IP1     | T5IP0                    | 4444          |

| IPC8        | 0850  | _                        | -                        | _                        | -                        | _                        | _                        | -                        | -                       | _                       | SPI2IP2  | SPI2IP1  | SPI2IP0   | -         | SPI2EIP2  | SPI2EIP1  | SPI2EIP0                 | 0044          |

| IPC9        | 0852  | _                        | _                        | _                        | _                        | _                        | IC4IP2                   | IC4IP1                   | IC4IP0                  | _                       | IC3IP2   | IC3IP1   | IC3IP0    | _         | _         | _         | _                        | 0440          |

Legend:

Note 1:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal. Only available on dsPIC33EPXXGS506 devices. Only available on dsPIC33EPXXGS504/505 and dsPIC33EPXXGS506 devices.

2:

### 4.6.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions, and the DSP accumulator class of instructions, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

**Note:** For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

- **Note:** Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.6.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.6.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-------|-------|-------|-----|-----|-------|

| VAR    | —   | US1   | US0   | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |       |       |       |     |     | bit 8 |

|        |     |       |       |       |     |     |       |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-----|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7 |       |       |        |                     |     |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

- 1 = Variable exception processing is enabled

- 0 = Fixed exception processing is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 10-24: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0           | U-0        | R/W-0                             | R/W-0  | R/W-0                              | R/W-0         | R/W-0              | R/W-0  |  |  |

|---------------|------------|-----------------------------------|--------|------------------------------------|---------------|--------------------|--------|--|--|

|               | —          | RP41R5                            | RP41R4 | RP41R3                             | RP41R2        | RP41R1             | RP41R0 |  |  |

| bit 15        | •          |                                   |        |                                    |               |                    | bit 8  |  |  |

|               |            |                                   |        |                                    |               |                    |        |  |  |

| U-0           | U-0        | R/W-0                             | R/W-0  | R/W-0                              | R/W-0         | R/W-0              | R/W-0  |  |  |

| —             | —          | RP40R5                            | RP40R4 | RP40R3                             | RP40R2        | RP40R1             | RP40R0 |  |  |

| bit 7         |            |                                   |        |                                    |               |                    | bit 0  |  |  |

|               |            |                                   |        |                                    |               |                    |        |  |  |

| Legend:       |            |                                   |        |                                    |               |                    |        |  |  |

| R = Readable  | e bit      | W = Writable                      | bit    | U = Unimplemented bit, read as '0' |               |                    |        |  |  |

| -n = Value at | POR        | '1' = Bit is set                  |        | '0' = Bit is cle                   | ared          | x = Bit is unknown |        |  |  |

|               |            |                                   |        |                                    |               |                    |        |  |  |

| bit 15-14     | Unimplemen | ted: Read as '                    | 0'     |                                    |               |                    |        |  |  |

| bit 13-8      |            | Peripheral Ou<br>-2 for periphera | •      | 0                                  | RP41 Output F | Pin bits           |        |  |  |

| bit 7.6       | Unimplomon | Unimplemented, Deed ee '0'        |        |                                    |               |                    |        |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-25: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0               | U-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0              | R/W-0  |

|-------------------|-----|------------------|--------|------------------|------------------|--------------------|--------|

| —                 | —   | RP43R5           | RP43R4 | RP43R3           | RP43R2           | RP43R1             | RP43R0 |

| bit 15            |     |                  |        |                  |                  |                    | bit 8  |

|                   |     |                  |        |                  |                  |                    |        |

| U-0               | U-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0              | R/W-0  |

| —                 |     | RP42R5           | RP42R4 | RP42R3           | RP42R2           | RP42R1             | RP42R0 |

| bit 7             |     |                  |        |                  |                  |                    | bit 0  |

|                   |     |                  |        |                  |                  |                    |        |

| Legend:           |     |                  |        |                  |                  |                    |        |

| R = Readable b    | bit | W = Writable     | bit    | U = Unimpler     | mented bit, read | d as '0'           |        |

| -n = Value at POR |     | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unknown |        |

bit 13-8 **RP43R<5:0>:** Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP42R<5:0>:** Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 10-2 for peripheral function numbers)

### **REGISTER 15-16:** SPHASEx: PWMx SECONDARY PHASE-SHIFT REGISTER (x = 1 to 5)<sup>(1,2)</sup>

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0              | R/W-0 |  |

|-------------------|-------|------------------|-------|-------------------|-------|--------------------|-------|--|

|                   |       |                  | SPHAS | SEx<15:8>         |       |                    |       |  |

| bit 15            |       |                  |       |                   |       |                    | bit 8 |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0              | R/W-0 |  |

|                   |       |                  | SPHA  | SEx<7:0>          |       |                    |       |  |

| bit 7             |       |                  |       |                   |       |                    | bit 0 |  |

| Legend:           |       |                  |       |                   |       |                    |       |  |

| R = Readable bit  |       | W = Writable bit |       | U = Unimplen      |       |                    |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is clea | ared  | x = Bit is unknown |       |  |

bit 15-0 **SPHASEx<15:0>:** Secondary Phase Offset for PWMxL Output Pin bits (used in Independent PWM mode only)

- **Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); SPHASEx<15:0> = Not used

- True Independent Output mode (IOCONx<11:10> = 11), PHASEx<15:0> = Phase-shift value for PWMxL only

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); SPHASEx<15:0> = Not used

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxL only

- When the PHASEx/SPHASEx registers provide the local period, the valid range of values is 0x0010-0xFFF8

| REGISTER 16-2: | SPIxCON1: SPIx CONTROL REGISTER 1 |

|----------------|-----------------------------------|

|----------------|-----------------------------------|

| U-0                 | U-0                                                                        | U-0                                                                                                                                                                                             | R/W-0                  | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |  |  |  |  |  |

|---------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|-----------------------------------------|----------------------|----------------------|--|--|--|--|--|

| _                   | —                                                                          | _                                                                                                                                                                                               | DISSCK                 | DISSDO               | MODE16                                  | SMP                  | CKE <sup>(1)</sup>   |  |  |  |  |  |

| bit 15              |                                                                            | ·                                                                                                                                                                                               |                        |                      |                                         |                      | bit                  |  |  |  |  |  |

| R/W-0               | R/W-0                                                                      | R/W-0                                                                                                                                                                                           | R/W-0                  | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |  |  |  |  |  |

| SSEN <sup>(2)</sup> |                                                                            | MSTEN                                                                                                                                                                                           | SPRE2 <sup>(3)</sup>   | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup>                    | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |  |  |

| bit 7               | ora                                                                        | moren                                                                                                                                                                                           | 011122                 | 011121               | 011120                                  |                      | bit                  |  |  |  |  |  |

|                     |                                                                            |                                                                                                                                                                                                 |                        |                      |                                         |                      |                      |  |  |  |  |  |

| Legend:             |                                                                            |                                                                                                                                                                                                 |                        |                      |                                         |                      |                      |  |  |  |  |  |

| R = Readable        | e bit                                                                      | W = Writable                                                                                                                                                                                    | bit                    | U = Unimpler         | mented bit, read                        | d as '0'             |                      |  |  |  |  |  |

| -n = Value at       | POR                                                                        | '1' = Bit is se                                                                                                                                                                                 | t                      | '0' = Bit is cle     | ared                                    | x = Bit is unkr      | nown                 |  |  |  |  |  |

|                     |                                                                            |                                                                                                                                                                                                 |                        |                      |                                         |                      |                      |  |  |  |  |  |

| bit 15-13           | -                                                                          | nted: Read as                                                                                                                                                                                   |                        |                      |                                         |                      |                      |  |  |  |  |  |

| bit 12              |                                                                            | able SCKx Pin                                                                                                                                                                                   | •                      |                      | <i>'</i> )                              |                      |                      |  |  |  |  |  |

|                     |                                                                            | SPIx clock is di                                                                                                                                                                                | •                      | ctions as I/O        |                                         |                      |                      |  |  |  |  |  |

| bit 11              | 0 = Internal SPIx clock is enabled<br>DISSDO: Disable SDOx Pin bit         |                                                                                                                                                                                                 |                        |                      |                                         |                      |                      |  |  |  |  |  |

|                     |                                                                            | 1 = SDOx pin is not used by the module; pin functions as I/O                                                                                                                                    |                        |                      |                                         |                      |                      |  |  |  |  |  |

|                     |                                                                            | n is controlled b                                                                                                                                                                               |                        |                      |                                         |                      |                      |  |  |  |  |  |

| bit 10              | MODE16: Word/Byte Communication Select bit                                 |                                                                                                                                                                                                 |                        |                      |                                         |                      |                      |  |  |  |  |  |

|                     |                                                                            | <ul> <li>1 = Communication is word-wide (16 bits)</li> <li>1 = Communication is byte-wide (8 bits)</li> </ul>                                                                                   |                        |                      |                                         |                      |                      |  |  |  |  |  |

|                     |                                                                            | -                                                                                                                                                                                               |                        |                      |                                         |                      |                      |  |  |  |  |  |

| bit 9               |                                                                            | ata Input Sam                                                                                                                                                                                   | ole Phase bit          |                      |                                         |                      |                      |  |  |  |  |  |

|                     | Master Mode                                                                |                                                                                                                                                                                                 | the end of da          | ta output time       |                                         |                      |                      |  |  |  |  |  |

|                     |                                                                            | <ul> <li>I = Input data is sampled at the end of data output time</li> <li>Input data is sampled at the middle of data output time</li> </ul>                                                   |                        |                      |                                         |                      |                      |  |  |  |  |  |

|                     | <u>Slave Mode:</u><br>SMP must be cleared when SPIx is used in Slave mode. |                                                                                                                                                                                                 |                        |                      |                                         |                      |                      |  |  |  |  |  |

| bit 8               | CKE: SPIx C                                                                | lock Edge Sele                                                                                                                                                                                  | ect bit <sup>(1)</sup> |                      |                                         |                      |                      |  |  |  |  |  |

|                     |                                                                            |                                                                                                                                                                                                 |                        |                      | clock state to lo<br>ock state to activ |                      |                      |  |  |  |  |  |

| bit 7               |                                                                            | <ul> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)</li> <li>SSEN: Slave Select Enable bit (Slave mode)<sup>(2)</sup></li> </ul> |                        |                      |                                         |                      |                      |  |  |  |  |  |

|                     |                                                                            | s used for Slav                                                                                                                                                                                 |                        | is controlled h      | by port function                        |                      |                      |  |  |  |  |  |

| bit 6               | -                                                                          | Polarity Select                                                                                                                                                                                 | -                      |                      |                                         |                      |                      |  |  |  |  |  |

|                     | 1 = Idle state                                                             | for clock is a h                                                                                                                                                                                | nigh level; activ      |                      |                                         |                      |                      |  |  |  |  |  |

| bit 5               |                                                                            | ster Mode Enal                                                                                                                                                                                  |                        |                      |                                         |                      |                      |  |  |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                               | node                                                                                                                                                                                            |                        |                      |                                         |                      |                      |  |  |  |  |  |

| Note 1: Th          | e CKE bit is not                                                           |                                                                                                                                                                                                 | d SPI modes. I         | Program this bi      | t to '0' for Fram                       | ed SPI modes (       | FRMEN =              |  |  |  |  |  |

| 0. Th               |                                                                            |                                                                                                                                                                                                 |                        |                      |                                         |                      |                      |  |  |  |  |  |

- **2:** This bit must be cleared when FRMEN = 1.

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

#### REGISTER 17-3: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC     | R-0, HSC                    | R-0, HSC                         | U-0            | U-0                           | R/C-0, HS                    | R-0, HSC                          | R-0, HSC             |

|--------------|-----------------------------|----------------------------------|----------------|-------------------------------|------------------------------|-----------------------------------|----------------------|

| ACKSTAT      | TRSTAT                      | ACKTIM                           | 0-0            |                               | BCL                          | GCSTAT                            | ADD10                |

| bit 15       | IRSIAI                      | ACKTIW                           | _              | —                             | BCL                          | GCSTAT                            |                      |

| DIL 15       |                             |                                  |                |                               |                              |                                   | bit 8                |

| R/C-0, HS    | R/C-0, HS                   | R-0, HSC                         | R/C-0, HSC     | R/C-0, HSC                    | R-0, HSC                     | R-0, HSC                          | R-0, HSC             |

| IWCOL        | I2COV                       | D_A                              | Р              | S                             | R_W                          | RBF                               | TBF                  |

| bit 7        |                             |                                  | •              |                               | •                            |                                   | bit 0                |

|              |                             |                                  |                |                               |                              |                                   |                      |

| Legend:      |                             | C = Clearab                      | le bit         | HS = Hardware                 | e Settable bit               | HSC = Hardware Se                 | ttable/Clearable bit |

| R = Readab   | ole bit                     | W = Writable                     | e bit          | '0' = Bit is clear            | red                          | x = Bit is unknown                |                      |

| -n = Value a | it POR                      | '1' = Bit is se                  | et             | U = Unimplem                  | ented bit, read              | as '0'                            |                      |

|              |                             |                                  |                |                               | 120                          | P I.I. I                          |                      |

| bit 15       |                             | -                                | -              | nen operating a               | s I <sup>2</sup> C master, a | pplicable to master tra           | insmit operation)    |

|              |                             | was received<br>as received f    |                |                               |                              |                                   |                      |

|              |                             |                                  |                | f a slave Ackno               | wledge.                      |                                   |                      |

| bit 14       | TRSTAT: T                   | ransmit Statu                    | s bit (when o  | perating as I <sup>2</sup> C  | C master, appli              | cable to master trans             | mit operation)       |

|              |                             | transmit is in                   | · • ·          | ,                             |                              |                                   |                      |

|              |                             | transmit is no                   |                |                               | on Hardwara                  | is clear at the end of sl         | lavo Acknowlodgo     |

| bit 13       |                             |                                  |                | bit (I <sup>2</sup> C Slave r |                              |                                   | lave Acknowledge.    |

| DIC 15       |                             | •                                |                | ence, set on th               | • ·                          | lae of SCL x                      |                      |

|              |                             |                                  | • .            | cleared on the                | •                            | •                                 |                      |

| bit 12-11    | Unimpleme                   | ented: Read                      | <b>as</b> '0'  |                               |                              |                                   |                      |

| bit 10       | BCL: Maste                  | er Bus Collisi                   | on Detect bit  |                               |                              |                                   |                      |

|              |                             |                                  |                | d during a mas                | ter operation                |                                   |                      |

|              |                             | collision dete<br>s set at detec |                | collision                     |                              |                                   |                      |

| bit 9        |                             | Seneral Call S                   |                | comsion.                      |                              |                                   |                      |

| bit o        |                             | l call address                   |                | ed                            |                              |                                   |                      |

|              | 0 = Genera                  | I call address                   | s was not rec  | eived                         |                              |                                   |                      |

|              |                             |                                  |                | nes the general               | call address.                | Hardware is clear at S            | Stop detection.      |

| bit 8        |                             | -Bit Address                     |                |                               |                              |                                   |                      |

|              |                             | ddress was i<br>ddress was i     |                |                               |                              |                                   |                      |

|              |                             |                                  |                | 2nd byte of th                | e matched 10                 | -bit address. Hardwa              | re is clear at Stop  |

|              | detection.                  |                                  |                | -                             |                              |                                   |                      |

| bit 7        |                             | Cx Write Coll                    |                |                               |                              |                                   |                      |

|              |                             |                                  | o the I2CxTF   | RN register faile             | ed because the               | e I <sup>2</sup> C module is busy |                      |

|              | 0 = No colli<br>Hardware is |                                  | ccurrence of   | a write to I2Cx               | TRN while bus                | sy (cleared by softwar            | e).                  |

| bit 6        |                             | x Receive O                      |                |                               |                              | , ( <b>,</b>                      | - /                  |

|              | 1 = A byte v                | was received                     | -              |                               | r was still hold             | ing the previous byte             |                      |

|              | 0 = No over<br>Hardware is  |                                  | tempt to tran  | sfer I2CxRSR f                | o I2CxRCV (c                 | leared by software).              |                      |

| bit 5        |                             | Address bit (                    | -              |                               |                              |                                   |                      |

|              |                             | es that the la                   |                | • ·                           |                              |                                   |                      |

|              | 0 = Indicate                | es that the las                  | st byte receiv | ed was a devic                |                              |                                   |                      |

|              | Hardware is                 | s clear at a d                   | evice addres   | s match. Hardw                | vare is set by               | reception of a slave b            | yte.                 |

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                           |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                    |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                   |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                               |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                             |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                              |

|       | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                           |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                         |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                              |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                           |

Note 1: Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual" for information on enabling the UARTx module for transmit operation.

### 19.0 HIGH-SPEED, 12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33EPXXGS50X devices have a high-speed, 12-bit Analog-to-Digital Converter (ADC) that features a low conversion latency, high resolution and oversampling capabilities to improve performance in AC/DC, DC/DC power converters.

### **19.1 Features Overview**

The High Speed, 12-Bit Multiple SARs Analog-to-Digital Converter (ADC) includes the following features:

- Five ADC Cores: Four Dedicated Cores and One Shared (Common) Core

- User-Configurable Resolution of up to 12 Bits for each Core

- Up to 3.25 Msps Conversion Rate per Channel at 12-Bit Resolution

- Low-Latency Conversion

- Up to 22 Analog Input Channels, with a Separate 16-Bit Conversion Result Register for each Input

- Conversion Result can be Formatted as Unsigned or Signed Data, on a per Channel Basis, for All Channels

- Single-Ended and Pseudodifferential Conversions are available on All ADC Cores

- Simultaneous Sampling of up to 5 Analog Inputs

- Channel Scan Capability

- Multiple Conversion Trigger Options for each Core, including:

- PWM1 through PWM5 (primary and secondary triggers, and current-limit event trigger)

- PWM Special Event Trigger

- Timer1/Timer2 period match

- Output Compare 1 and event trigger

- External pin trigger event (ADTRG31)

- Software trigger

- Two Integrated Digital Comparators with Dedicated Interrupts:

- Multiple comparison options

- Assignable to specific analog inputs

- Two Oversampling Filters with Dedicated Interrupts:

- Provide increased resolution

- Assignable to a specific analog input

The module consists of five independent SAR ADC cores. Simplified block diagrams of the Multiple SARs 12-Bit ADC are shown in Figure 19-1, Figure 19-2 and Figure 19-3.

The analog inputs (channels) are connected through multiplexers and switches to the Sample-and-Hold (S&H) circuit of each ADC core. The core uses the channel information (the output format, the measurement mode and the input number) to process the analog sample. When conversion is complete, the result is stored in the result buffer for the specific analog input, and passed to the digital filter and digital comparator if they were configured to use data from this particular channel.

The ADC module can sample up to five inputs at a time (four inputs from the dedicated SAR cores and one from the shared SAR core). If multiple ADC inputs request conversion on the shared core, the module will convert them in a sequential manner, starting with the lowest order input.

The ADC provides each analog input the ability to specify its own trigger source. This capability allows the ADC to sample and convert analog inputs that are associated with PWM generators operating on independent time bases.

| U-0                   | U-0       | U-0                                   | U-0            | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-----------------------|-----------|---------------------------------------|----------------|----------------------------|-----------------|-----------------|-----------------|

| —                     | —         | —                                     |                | SYNCTRG3                   | SYNCTRG2        | SYNCTRG1        | SYNCTRGO        |

| bit 15                |           |                                       |                |                            |                 |                 | bit 8           |

| U-0                   | U-0       | U-0                                   | U-0            | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

| _                     | _         |                                       | _              | SAMC3EN                    | SAMC2EN         | SAMC1EN         | SAMCOEN         |

| oit 7                 |           |                                       |                |                            |                 |                 | bit (           |

| _egend:               |           |                                       |                |                            |                 |                 |                 |

| -egend.<br>R = Readab | le hit    | W = Writable                          | hit            | II = I Inimplem            | ented bit, read | l as 'N'        |                 |

| n = Value a           |           | '1' = Bit is set                      |                | 0' = Bit is clea           |                 | x = Bit is unkr | own             |

|                       |           |                                       |                |                            |                 |                 |                 |

| oit 15-12             | Unimpleme | ented: Read as '                      | 0'             |                            |                 |                 |                 |

| pit 11                | SYNCTRG3  | : Dedicated AD                        | C Core 3 Trigg | ger Synchronizat           | ion bit         |                 |                 |

|                       |           |                                       |                | core source cloc           | k (TCORESRC)    |                 |                 |

|                       |           | C core triggers a                     | -              |                            |                 |                 |                 |

| bit 10                |           |                                       |                | ger Synchronizat           |                 |                 |                 |

|                       |           | ers are synchror<br>C core triggers a |                | core source cloc<br>onized | K (ICORESRC)    |                 |                 |

| oit 9                 |           |                                       | -              | ger Synchronizat           | ion bit         |                 |                 |

|                       |           |                                       |                | core source cloc           |                 |                 |                 |

|                       |           | C core triggers a                     |                |                            | . ,             |                 |                 |

| oit 8                 | SYNCTRG   | : Dedicated AD                        | C Core 0 Trigg | ger Synchronizat           | ion bit         |                 |                 |

|                       |           | ers are synchror<br>C core triggers a |                | core source cloc<br>onized | k (TCORESRC)    |                 |                 |

| oit 7-4               |           | ented: Read as '                      | -              |                            |                 |                 |                 |

| oit 3                 | SAMC3EN:  | Dedicated ADC                         | Core 3 Conve   | ersion Delay Ena           | ble bit         |                 |                 |

|                       |           |                                       |                | elayed and the             |                 | continue samp   | ling during the |

|                       |           |                                       |                | s in the ADCORE            |                 |                 | -4              |

|                       |           | gger, the sampli<br>re clock cycle    | ng will be sto | pped immediatel            | y and the conv  | version will be | started on the  |

| oit 2                 | SAMC2EN:  | Dedicated ADC                         | Core 2 Conve   | ersion Delay Ena           | ble bit         |                 |                 |

|                       |           |                                       |                | elayed and the A           |                 | continue samp   | ling during the |

|                       |           |                                       |                | s in the ADCORE            |                 | eraion will be  | atartad an the  |

|                       |           | re clock cycle                        | ng will be sto | pped immediatel            | y and the com   |                 | started on the  |

| oit 1                 |           | -                                     | Core 1 Conve   | ersion Delay Ena           | ble bit         |                 |                 |

|                       |           |                                       |                | elayed and the A           |                 | continue samp   | ling during the |

|                       |           |                                       |                | s in the ADCORE            |                 |                 |                 |

|                       |           | gger, the sampli<br>re clock cycle    | ng will be sto | pped immediatel            | y and the conv  | version will be | started on the  |

| oit O                 |           | -                                     | Core 0 Conve   | ersion Delay Ena           | ble bit         |                 |                 |

|                       |           |                                       |                | elayed and the A           |                 | continue samp   | ling during the |

|                       |           |                                       |                | s in the ADCORE            |                 | -               | -               |

|                       |           |                                       |                | pped immediatel            |                 |                 |                 |

| DIFF7       SIGN7       DIFF6       SIGN6       DIFF5       SIGN5       DIFF4       SIGN         bit 15 |        |       |       |       |       |       |       |       |

|---------------------------------------------------------------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|-------|

| bit 15<br>R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>DIFF3 SIGN3 DIFF2 SIGN2 DIFF1 SIGN1 DIFF0 SIGN   | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0DIFF3SIGN3DIFF2SIGN2DIFF1SIGN1DIFF0SIGN                                   | DIFF7  | SIGN7 | DIFF6 | SIGN6 | DIFF5 | SIGN5 | DIFF4 | SIGN4 |

| DIFF3 SIGN3 DIFF2 SIGN2 DIFF1 SIGN1 DIFF0 SIGN                                                          | bit 15 |       | •     | •     | •     | •     |       | bit 8 |

| DIFF3 SIGN3 DIFF2 SIGN2 DIFF1 SIGN1 DIFF0 SIGN                                                          |        |       |       |       |       |       |       |       |

|                                                                                                         | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| bit 7                                                                                                   | DIFF3  | SIGN3 | DIFF2 | SIGN2 | DIFF1 | SIGN1 | DIFF0 | SIGN0 |

|                                                                                                         | bit 7  |       | •     | •     | •     | •     | •     | bit 0 |

|                                                                                                         |        |       |       |       |       |       |       |       |

#### REGISTER 19-19: ADMOD0L: ADC INPUT MODE CONTROL REGISTER 0 LOW

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1(odd) **DIFF<7:0>:** Differential-Mode for Corresponding Analog Inputs bits

1 = Channel is differential

- 0 = Channel is single-ended

- bit 14-0 (even) **SIGN<7:0>:** Output Data Sign for Corresponding Analog Inputs bits

- 1 = Channel output data is signed

- 0 = Channel output data is unsigned

#### REGISTER 19-20: ADMOD0H: ADC INPUT MODE CONTROL REGISTER 0 HIGH

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| DIFF15 | SIGN15 | DIFF14 | SIGN14 | DIFF13 | SIGN13 | DIFF12 | SIGN12 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|--------|-------|-------|-------|-------|

| DIFF11 | SIGN11 | DIFF10 | SIGN10 | DIFF9 | SIGN9 | DIFF8 | SIGN8 |

| bit 7  |        |        |        |       |       |       | bit 0 |

| Legend:           |                                                                      |                      |                    |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-1(odd) DIFF<15:8>: Differential-Mode for Corresponding Analog Inputs bits

- 1 = Channel is differential

- 0 = Channel is single-ended

bit 14-0 (even) SIGN<15:8>: Output Data Sign for Corresponding Analog Inputs bits

- 1 = Channel output data is signed

- 0 = Channel output data is unsigned

#### REGISTER 19-27: ADTRIGXH: ADC CHANNEL TRIGGER x SELECTION REGISTER HIGH (x = 0 to 5)

| U-0    | U-0 | U-0 | R/W-0             | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-----|-------------------|-------|-------|-------|-------|--|--|

|        | _   | _   | TRGSRC(4x+3)<4:0> |       |       |       |       |  |  |

| bit 15 |     |     |                   |       |       |       | bit 8 |  |  |

|        |     |     |                   |       |       |       |       |  |  |

| U-0    | U-0 | U-0 | R/W-0             | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|        | _   | _   | TRGSRC(4x+2)<4:0> |       |       |       |       |  |  |

| bit 7  |     |     |                   |       |       |       | bit 0 |  |  |

### Legend:

| •                 |                  |                               |                    |  |

|-------------------|------------------|-------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as '0'             |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |  |

#### bit 15-13 Unimplemented: Read as '0'

bit 12-8 TRGSRC(4x+3)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

| TRGSRC(4x+3)<4:0>: Ingger Source Selection T  |

|-----------------------------------------------|

| 11111 = ADTRG31                               |

| 11110 = Reserved                              |

| 11101 = Reserved                              |

| 11100 = PWM Generator 5 current-limit trigger |

| 11011 = PWM Generator 4 current-limit trigger |

| 11010 = PWM Generator 3 current-limit trigger |

| 11001 = PWM Generator 2 current-limit trigger |

| 11000 = PWM Generator 1 current-limit trigger |

| 10111 = Output Compare 2 trigger              |

| 10110 = Output Compare 1 trigger              |

| 10101 = Reserved                              |

| 10100 = Reserved                              |

| 10011 = PWM Generator 5 secondary trigger     |

| 10010 = PWM Generator 4 secondary trigger     |

| 10001 = PWM Generator 3 secondary trigger     |

| 10000 = PWM Generator 2 secondary trigger     |

| 01111 = PWM Generator 1 secondary trigger     |

| 01110 = PWM secondary Special Event Trigger   |

| 01101 = Timer2 period match                   |

| 01100 = Timer1 period match                   |

| 01011 = Reserved                              |

| 01010 = Reserved                              |

| 01001 = PWM Generator 5 primary trigger       |

| 01000 = PWM Generator 4 primary trigger       |

| 00111 = PWM Generator 3 primary trigger       |

| 00110 = PWM Generator 2 primary trigger       |

| 00101 = PWM Generator 1 primary trigger       |

| 00100 = PWM Special Event Trigger             |

| 00011 = Reserved                              |

| 00010 = Level software trigger                |

| 00001 = Common software trigger               |

| 00000 = No trigger is enabled                 |

| Unimplemented: Read as '0'                    |

|                                               |

bit 7-5

### 23.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXGS50X family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

- Brown-out Reset (BOR)

### 23.1 Configuration Bits

In dsPIC33EPXXGS50X family devices, the Configuration Words are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the end of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 23-1 with detailed descriptions in Table 23-2. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration Shadow registers during device Resets.

For devices operating in Dual Partition modes, the BSEQx bits (FBTSEQ<11:0>) determine which panel is the Active Partition at start-up and the Configuration Words from that panel are loaded into the Configuration Shadow registers.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Words for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled. Program code executing out of configuration space will cause a device Reset.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration Words.

### TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|