Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

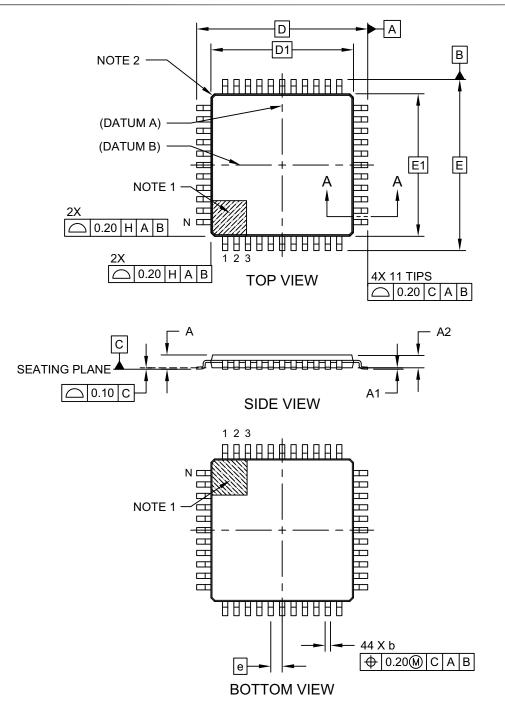

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs504t-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.5.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible, regardless of the contents of the Data Space Page register. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space in combination with DSRPAG = 0x00. Consequently, DSRPAG is initialized to 0x001 at Reset.

- Note 1: DSRPAG should not be used to access Page 0. An EDS access with DSRPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSRPAG in software has no effect.

The remaining PSV pages are only accessible using the DSRPAG register in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

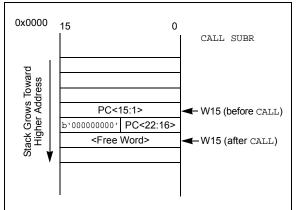

### 4.5.3 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP), and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXGS50X devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-11 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes). When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-11. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

### FIGURE 4-11: CALL STACK FRAME

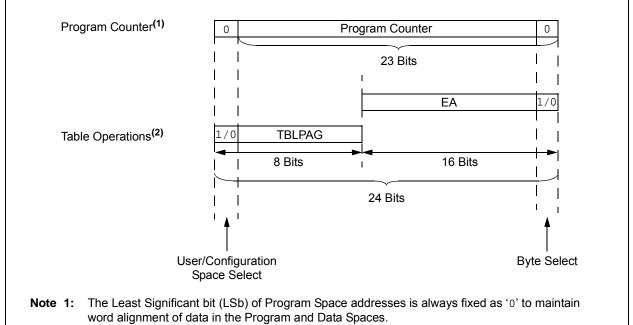

## 4.9 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXGS50X family architecture uses a 24-bit wide Program Space (PS) and a 16-bit wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXGS50X family devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## TABLE 4-40: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Type                            | Access        | Program Space Address |             |                     |               |     |  |

|----------------------------------------|---------------|-----------------------|-------------|---------------------|---------------|-----|--|

|                                        | Space         | <23>                  | <22:16>     | <15>                | <14:1>        | <0> |  |

| Instruction Access<br>(Code Execution) | User          | 0 PC<22:1> 0          |             |                     |               | 0   |  |

|                                        |               |                       | 0xxx xxxx x | xxx xxx             | x xxxx xxx0   |     |  |

| TBLRD/TBLWT<br>(Byte/Word Read/Write)  | User          | TB                    | LPAG<7:0>   |                     | Data EA<15:0> |     |  |

|                                        |               | 0                     | xxx xxxx    | XXXX                |               | xx  |  |

|                                        | Configuration | TBLPAG<7:0>           |             | Data EA<15:0>       |               |     |  |

|                                        |               | 1                     | xxx xxxx    | xxxx xxxx xxxx xxxx |               |     |  |

#### FIGURE 4-14: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

**2:** Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

#### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| R/SO-0(    | <sup>1)</sup> R/W-0 <sup>(1)</sup>      | R/W-0 <sup>(1)</sup>                                                                                            | R/W-0                            | R/C-0                             | R-0                     | R/W-0                   | R/C-0                   |

|------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------|-------------------------|-------------------------|-------------------------|

| WR         | WREN                                    | WRERR                                                                                                           | NVMSIDL <sup>(2)</sup>           | SFTSWP <sup>(6)</sup>             | P2ACTIV <sup>(6)</sup>  | RPDF                    | URERR                   |

| bit 15     |                                         |                                                                                                                 |                                  |                                   |                         |                         | bit 8                   |

|            |                                         |                                                                                                                 |                                  |                                   |                         |                         |                         |

| U-0        | U-0                                     | U-0                                                                                                             | U-0                              | R/W-0 <sup>(1)</sup>              | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    |

| _          | —                                       | —                                                                                                               | —                                | NVMOP3 <sup>(3,4)</sup>           | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4)</sup> |

| bit 7      |                                         |                                                                                                                 |                                  |                                   |                         |                         | bit 0                   |

|            |                                         |                                                                                                                 |                                  |                                   |                         |                         |                         |

| Legend:    |                                         | C = Clearab                                                                                                     | le bit                           | SO = Settable                     | Only bit                |                         |                         |

| R = Reada  | able bit                                | W = Writable                                                                                                    | e bit                            | U = Unimplem                      | ented bit, read a       | as '0'                  |                         |

| -n = Value | at POR                                  | '1' = Bit is se                                                                                                 | et                               | '0' = Bit is clea                 | red                     | x = Bit is unkn         | own                     |

|            |                                         |                                                                                                                 |                                  |                                   |                         |                         |                         |

| bit 15     | WR: Write Co                            |                                                                                                                 |                                  |                                   |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  |                                   | on; the operation       | on is self-timed        | and the bit is          |

|            |                                         |                                                                                                                 |                                  | tion is complete ete and inactive |                         |                         |                         |

| bit 14     | WREN: Write                             | -                                                                                                               | -                                |                                   | -                       |                         |                         |

|            |                                         |                                                                                                                 | m/erase operat                   | ions                              |                         |                         |                         |

|            |                                         |                                                                                                                 | /erase operation                 |                                   |                         |                         |                         |

| bit 13     |                                         |                                                                                                                 | Error Flag bit <sup>(1</sup>     |                                   |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  | ce attempt, or te                 | rmination has o         | ccurred (bit is se      | et automatically        |

|            | •                                       | et attempt of the second se |                                  | pleted normally                   | ,                       |                         |                         |

| bit 12     |                                         |                                                                                                                 | le Control bit <sup>(2)</sup>    |                                   |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  | ndby mode dur                     | ing Idle mode           |                         |                         |

|            |                                         | • •                                                                                                             | or is active duri                | •                                 | 0                       |                         |                         |

| bit 11     | SFTSWP: Pa                              | artition Soft Sv                                                                                                | vap Status bit <sup>(€</sup>     | 5)                                |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  |                                   | e BOOTSWP inst          |                         |                         |

|            |                                         |                                                                                                                 | artition swap us<br>sed on FBTSE |                                   | P instruction or        | a device Reset          | will determine          |

| bit 10     | P2ACTIV: Pa                             |                                                                                                                 |                                  | C .                               |                         |                         |                         |

|            |                                         |                                                                                                                 | apped into the a                 | active region                     |                         |                         |                         |

|            |                                         |                                                                                                                 | apped into the a                 | •                                 |                         |                         |                         |

| bit 9      | RPDF: Row F                             | Programming                                                                                                     | Data Format b                    | it                                |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  | npressed forma                    |                         |                         |                         |

|            | 0 = Row data                            | a to be stored                                                                                                  | in RAM in und                    | ompressed forr                    | nat                     |                         |                         |

| Note 1:    | These bits can on                       | ly be reset or                                                                                                  | a POR.                           |                                   |                         |                         |                         |

| 2:         | If this bit is set, po                  |                                                                                                                 |                                  |                                   | DLE) and upon e         | exiting Idle mod        | e, there is a           |

| •          | delay (TVREG) bef                       |                                                                                                                 | -                                | -                                 |                         |                         |                         |

|            | All other combinat                      |                                                                                                                 |                                  | •                                 |                         | ana ara in prag         | ~~~~                    |

| 4:<br>5:   | Execution of the I<br>Two adjacent wor  |                                                                                                                 | -                                | -                                 | -                       |                         |                         |

| 5.<br>6:   | Only available on                       |                                                                                                                 | -                                |                                   | -                       | -                       |                         |

| 0.         | this bit is reserved                    |                                                                                                                 |                                  |                                   |                         |                         |                         |

| 7:         | The specific Boot                       |                                                                                                                 |                                  | of the program                    | med data:               |                         |                         |

|            | 11 = Single Partitio                    |                                                                                                                 |                                  |                                   |                         |                         |                         |

|            | 10 = Dual Partitio<br>01 = Protected Du |                                                                                                                 |                                  |                                   |                         |                         |                         |

|            | 00 = Reserved                           |                                                                                                                 |                                  |                                   |                         |                         |                         |

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS7000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXGS50X family CPU.

The interrupt controller has the following features:

- Six processor exceptions and software traps

- · Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

- Alternate Interrupt Vector Table (AIVT) for debug support

## 7.1 Interrupt Vector Table

The dsPIC33EPXXGS50X family Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to 246 sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-2, is available only when the Boot Segment is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least 2 pages to enable the AIVT.

Note: Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXGS50X family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| R/W-1         | R/W-0       | R/W-0                                                            | U-0            | U-0              | U-0              | U-0             | R/W-0  |  |  |  |

|---------------|-------------|------------------------------------------------------------------|----------------|------------------|------------------|-----------------|--------|--|--|--|

| GIE           | DISI        | SWTRAP                                                           | _              | _                | _                |                 | AIVTEN |  |  |  |

| bit 15        |             |                                                                  |                |                  |                  |                 | bit    |  |  |  |

|               |             |                                                                  |                |                  |                  |                 |        |  |  |  |

| U-0           | U-0         | U-0                                                              | R/W-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|               |             | —                                                                | INT4EP         |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |

| bit 7         |             |                                                                  |                |                  |                  |                 | bit    |  |  |  |

| Legend:       |             |                                                                  |                |                  |                  |                 |        |  |  |  |

| R = Readable  | e bit       | W = Writable                                                     | bit            | U = Unimple      | mented bit, read | l as '0'        |        |  |  |  |

| -n = Value at | POR         | '1' = Bit is set                                                 |                | '0' = Bit is cle | eared            | x = Bit is unki | nown   |  |  |  |

|               |             |                                                                  |                |                  |                  |                 |        |  |  |  |

| bit 15        | GIE: Global | Interrupt Enable                                                 | e bit          |                  |                  |                 |        |  |  |  |

|               |             | ts and associate                                                 |                |                  |                  |                 |        |  |  |  |

|               |             | ts are disabled, I                                               | •              | till enabled     |                  |                 |        |  |  |  |

| bit 14        |             | Instruction Statu                                                |                |                  |                  |                 |        |  |  |  |

|               |             | struction is active<br>struction is not a                        |                |                  |                  |                 |        |  |  |  |

| bit 13        |             |                                                                  |                |                  |                  |                 |        |  |  |  |

| DIL 15        |             | SWTRAP: Software Trap Status bit<br>1 = Software trap is enabled |                |                  |                  |                 |        |  |  |  |

|               |             | e trap is disabled                                               |                |                  |                  |                 |        |  |  |  |

| bit 12-9      | Unimpleme   | ented: Read as '                                                 | 0'             |                  |                  |                 |        |  |  |  |

| bit 8         | AIVTEN: Al  | ternate Interrupt                                                | Vector Table E | Enable           |                  |                 |        |  |  |  |

|               |             | ternate Interrupt                                                |                |                  |                  |                 |        |  |  |  |

|               |             | andard Interrupt                                                 |                |                  |                  |                 |        |  |  |  |

| bit 7-5       | -           | ented: Read as '                                                 |                |                  |                  |                 |        |  |  |  |

| bit 4         |             | ternal Interrupt 4                                               | -              | Polarity Selec   | ct bit           |                 |        |  |  |  |

|               | •           | t on negative edg<br>t on positive edg                           | •              |                  |                  |                 |        |  |  |  |

| bit 3         | -           | ented: Read as '                                                 |                |                  |                  |                 |        |  |  |  |

| bit 2         | -           | ternal Interrupt 2                                               |                | Polarity Selec   | rt hit           |                 |        |  |  |  |

| SIL 2         |             | t on negative ed                                                 | 0              |                  |                  |                 |        |  |  |  |

|               |             | t on positive edg                                                |                |                  |                  |                 |        |  |  |  |

| bit 1         | INT1EP: Ex  | ternal Interrupt 1                                               | Edge Detect    | Polarity Selec   | ct bit           |                 |        |  |  |  |

|               |             | t on negative ed                                                 |                |                  |                  |                 |        |  |  |  |

|               | •           | t on positive edg                                                |                |                  |                  |                 |        |  |  |  |

| bit 0         |             | ternal Interrupt (                                               | -              | Polarity Selec   | ct bit           |                 |        |  |  |  |

|               |             | t on negative edg                                                |                |                  |                  |                 |        |  |  |  |

|               | 0 = memup   | t on positive edg                                                | e              |                  |                  |                 |        |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

## 10.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 26-11 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 26.0 "Electrical Characteristics" of this data sheet. For example:

Vон = 2.4v @ Iон = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 27.0 "DC and AC Device Characteristics Graphs"** for additional information.

### REGISTER 10-14: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0            | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0            | R/W-0            | R/W-0              | R/W-0    |

|------------------|------------------------------------|------------------------------------------------------------------------------|--------------|------------------|------------------|--------------------|----------|

| SCK2INR7         | SCK2INR6                           | SCK2INR5                                                                     | SCK2INR4     | SCK2INR3         | SCK2INR2         | SCK2INR1           | SCK2INR0 |

| bit 15           |                                    |                                                                              |              |                  |                  |                    | bit 8    |

| R/W-0            | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0            | R/W-0            | R/W-0              | R/W-0    |

| SDI2R7           | SDI2R6                             | SDI2R5                                                                       | SDI2R4       | SDI2R3           | SDI2R2           | SDI2R1             | SDI2R0   |

| bit 7            |                                    |                                                                              |              |                  |                  |                    | bit (    |

| Legend:          |                                    |                                                                              |              |                  |                  |                    |          |

| R = Readable bit |                                    | W = Writable                                                                 | bit          | U = Unimpler     | nented bit, read | l as '0'           |          |

| -n = Value at    | POR                                | '1' = Bit is set                                                             |              | '0' = Bit is cle | ared             | x = Bit is unknown |          |

|                  | 10110100 =<br>•<br>•<br>00000001 = | Input tied to Rf<br>Input tied to Rf<br>Input tied to Rf<br>Input tied to Vs | 2180<br>21   |                  |                  |                    |          |

| bit 7-0          | 10110101 =                         | Input tied to RF<br>Input tied to RF                                         | 2181<br>2180 | 12) to the Corre | esponding RPn    | Pin bits           |          |

# 12.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1. T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 12-2.

## 12.1 Timer Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| <b>REGISTER 12-2:</b> | TyCON: ( | (TIMER3 AND TIMER | 5) CONTROL REGISTER |

|-----------------------|----------|-------------------|---------------------|

|-----------------------|----------|-------------------|---------------------|

| TON <sup>(1)</sup> |                               | R/W-0                        | U-0                     | U-0                          | U-0             | U-0                  | U-0            |

|--------------------|-------------------------------|------------------------------|-------------------------|------------------------------|-----------------|----------------------|----------------|

| TON                |                               | TSIDL <sup>(2)</sup>         | —                       | _                            | _               | _                    | _              |

| bit 15             |                               |                              |                         |                              |                 |                      | bit            |

| U-0                | R/W-0                         | R/W-0                        | R/W-0                   | U-0                          | U-0             | R/W-0                | U-0            |

| _                  | TGATE <sup>(1)</sup>          | TCKPS1 <sup>(1)</sup>        | TCKPS0 <sup>(1)</sup>   | _                            | _               | TCS <sup>(1,3)</sup> | _              |

| bit 7              |                               |                              |                         |                              |                 |                      | bit            |

| Legend:            |                               |                              |                         |                              |                 |                      |                |

| R = Readable       | hit                           | W = Writable                 | hit                     | =   Inimpler                 | mented bit, rea | ad as 'O'            |                |

| -n = Value at I    |                               | '1' = Bit is set             |                         | '0' = Bit is cle             |                 | x = Bit is unkno     | מעאר           |

|                    | FOR                           | I - DILISSEL                 |                         |                              | aleu            |                      | 50011          |

| bit 15             | TON: Timery                   | On bit <sup>(1)</sup>        |                         |                              |                 |                      |                |

|                    | 1 = Starts 16-                | •                            |                         |                              |                 |                      |                |

|                    | 0 = Stops 16-                 | bit Timery                   |                         |                              |                 |                      |                |

| bit 14             | •                             | ted: Read as '               |                         |                              |                 |                      |                |

| bit 13             | TSIDL: Timer                  | y Stop in Idle M             | lode bit <sup>(2)</sup> |                              |                 |                      |                |

|                    |                               | ues module op                |                         |                              | dle mode        |                      |                |

|                    |                               | s module opera               |                         | ode                          |                 |                      |                |

| bit 12-7           | -                             | ted: Read as '               |                         | (4)                          |                 |                      |                |

| bit 6              |                               | ery Gated Time               | Accumulation            | Enable bit <sup>(1)</sup>    |                 |                      |                |

|                    | When TCS =<br>This bit is ign |                              |                         |                              |                 |                      |                |

|                    | When TCS =                    |                              |                         |                              |                 |                      |                |

|                    |                               | <u>o.</u><br>le accumulatior | n is enabled            |                              |                 |                      |                |

|                    |                               | e accumulation               |                         |                              |                 |                      |                |

| bit 5-4            | TCKPS<1:0>                    | : Timery Input               | Clock Prescal           | e Select bits <sup>(1)</sup> | 1               |                      |                |

|                    | 11 <b>= 1:256</b>             |                              |                         |                              |                 |                      |                |

|                    | 10 <b>= 1:64</b>              |                              |                         |                              |                 |                      |                |

|                    | 01 = 1:8<br>00 = 1:1          |                              |                         |                              |                 |                      |                |

| bit 3-2            |                               | ted: Read as '               | ı'                      |                              |                 |                      |                |

| bit 1              | -                             | Clock Source S               |                         |                              |                 |                      |                |

|                    |                               | clock is from pir            |                         | e risina edae)               |                 |                      |                |

|                    | 0 = Internal c                |                              |                         | c rising cage)               |                 |                      |                |

| bit 0              |                               | ted: Read as '               | )'                      |                              |                 |                      |                |

|                    |                               |                              |                         | 1), these bits               | have no effec   | t on Timery operat   | tion; all time |

|                    | ictions are set th            | •                            |                         | 1) in the Time-              | v Control rogi  | ster (TxCON<3>),     |                |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all devices. See the "Pin Diagrams" section for the available pins.

#### **REGISTER 15-20:** IOCONX: PWMx I/O CONTROL REGISTER (x = 1 to 5) (CONTINUED)

| bit 3-2 | CLDAT<1:0>: State for PWMxH and PWMxL Pins if CLMOD is Enabled bits <sup>(2)</sup>                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | IFLTMOD (FCLCONx<15>) = 0: Normal Fault Mode:                                                                                                                                                                    |

|         | If current limit is active, then CLDAT1 provides the state for the PWMxH pin.                                                                                                                                    |

|         | If current limit is active, then CLDAT0 provides the state for the PWMxL pin.                                                                                                                                    |

|         | IFLTMOD (FCLCONx<15>) = 1: Independent Fault Mode:                                                                                                                                                               |

|         | CLDAT<1:0> bits are ignored.                                                                                                                                                                                     |

| bit 1   | SWAP: SWAP PWMxH and PWMxL Pins bit                                                                                                                                                                              |

|         | <ul> <li>1 = PWMxH output signal is connected to the PWMxL pins; PWMxL output signal is connected to the<br/>PWMxH pins</li> </ul>                                                                               |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                                                                                                                     |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                                                                                                                       |

|         | <ul> <li>1 = Output overrides via the OVRDAT&lt;1:0&gt; bits are synchronized to the PWMx time base</li> <li>0 = Output overrides via the OVRDAT&lt;1:0&gt; bits occur on the next CPU clock boundary</li> </ul> |

|         |                                                                                                                                                                                                                  |

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: State represents the active/inactive state of the PWMx depending on the POLH and POLL bits settings.

#### **REGISTER 15-21:** TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 5)

| R/W-0           | R/W-0                             | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|-----------------|-----------------------------------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

|                 |                                   |                  | TRGC                               | MP<12:5>             |       |                    |       |

| bit 15          |                                   |                  |                                    |                      |       |                    | bit 8 |

| R/W-0           | R/W-0                             | R/W-0            | R/W-0                              | R/W-0                | U-0   | U-0                | U-0   |

|                 |                                   | TRGCMP<4:0>      | >                                  |                      | _     | _                  | _     |

| bit 7           |                                   |                  |                                    |                      | ·     |                    | bit 0 |

| Legend:         |                                   |                  |                                    |                      |       |                    |       |

| R = Readable    | R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at F | POR                               | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

bit 15-3 **TRGCMP<12:0>:** Trigger Compare Value bits When the primary PWMx functions in the local time base, this register contains the compare values that can trigger the ADC module.

bit 2-0 Unimplemented: Read as '0'

#### R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 **HRPDIS HRDDIS** \_\_\_\_ BLANKSEL3 BLANKSEL2 BLANKSEL1 **BLANKSEL0** \_ bit 15 bit 8 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 CHOPSEL3 CHOPSEL2 CHOPSEL1 CHOPSEL0 CHOPHEN CHOPLEN bit 7 bit 0 Leaend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 HRPDIS: High-Resolution PWMx Period Disable bit 1 = High-resolution PWMx period is disabled to reduce power consumption 0 = High-resolution PWMx period is enabled bit 14 HRDDIS: High-Resolution PWMx Duty Cycle Disable bit 1 = High-resolution PWMx duty cycle is disabled to reduce power consumption 0 = High-resolution PWMx duty cycle is enabled bit 13-12 Unimplemented: Read as '0' bit 11-8 BLANKSEL<3:0>: PWMx State Blank Source Select bits The selected state blank signal will block the current-limit and/or Fault input signals (if enabled via the BCH and BCL bits in the LEBCONx register). 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM5H is selected as the state blank source 0100 = PWM4H is selected as the state blank source 0011 = PWM3H is selected as the state blank source 0010 = PWM2H is selected as the state blank source 0001 = PWM1H is selected as the state blank source 0000 = No state blanking bit 7-6 Unimplemented: Read as '0' bit 5-2 CHOPSEL<3:0>: PWMx Chop Clock Source Select bits The selected signal will enable and disable (chop) the selected PWMx outputs. 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM5H is selected as the chop clock source 0100 = PWM4H is selected as the chop clock source 0011 = PWM3H is selected as the chop clock source 0010 = PWM2H is selected as the chop clock source 0001 = PWM1H is selected as the chop clock source 0000 = Chop clock generator is selected as the chop clock source bit 1 **CHOPHEN:** PWMxH Output Chopping Enable bit 1 = PWMxH chopping function is enabled 0 = PWMxH chopping function is disabled bit 0 CHOPLEN: PWMxL Output Chopping Enable bit 1 = PWMxL chopping function is enabled 0 = PWMxL chopping function is disabled

**REGISTER 15-26:** AUXCONx: PWMx AUXILIARY CONTROL REGISTER (x = 1 to 5)

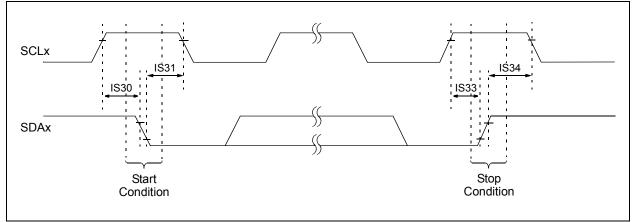

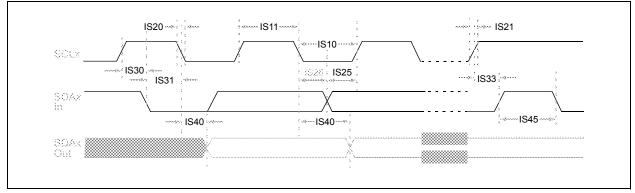

# 17.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70000195) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family of devices contains two Inter-Integrated Circuit (I $^2$ C) modules: I2C1 and I2C2.

The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx/ASCLx pin is clock

- · The SDAx/ASDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C Interface Supporting Both Master and Slave modes of Operation

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing

- I<sup>2</sup>C Port allows Bidirectional Transfers between Master and Slaves

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control)

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates accordingly

- System Management Bus (SMBus) Support

- Alternate I<sup>2</sup>C Pin Mapping (ASCLx/ASDAx)

# 17.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 17.1.1 KEY RESOURCES

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

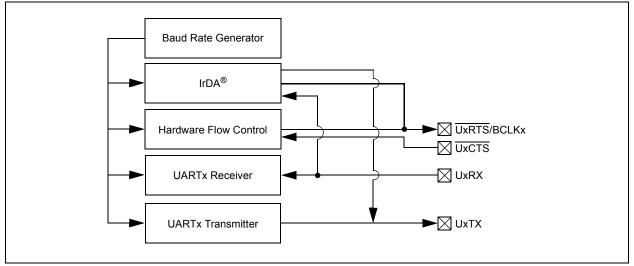

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXGS50X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps in 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps in 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit Mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 18-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 18-1: UARTX SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 19-15: ADEIEL: ADC EARLY INTERRUPT ENABLE REGISTER LOW

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|----------|-------|-------|-------|--------|-------|-------|-------|

|          |       |       | EIEN  | <15:8> |       |       |       |

| bit 15   |       |       |       |        |       |       | bit 8 |

|          |       |       |       |        |       |       |       |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|          |       |       | EIEN  | <7:0>  |       |       |       |

| bit 7    |       |       |       |        |       |       | bit 0 |

| <u> </u> |       |       |       |        |       |       |       |

| Legend:  |       |       |       |        |       |       |       |

| Logona.           |                  |                       |                                    |  |

|-------------------|------------------|-----------------------|------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |

bit 15-0 EIEN<15:0>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

### REGISTER 19-16: ADEIEH: ADC EARLY INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | EIEN< | 21:16> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 EIEN<21:16>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter is changed as a result of the instruction, or a PSV or table read is performed. In these cases, the execution takes multiple instruction cycles,

Slit6

Wb

Wd

Wdo

Wm,Wn

with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the "16-bit MCU and DSC Programmer's Reference Manual' (DS70157).

| #textMeans literal defined by "text"(text)Means "content of text"[text]Means "the location addressed by text" $\{\}$ Optional field or operation $a \in \{b, c, d\}$ a is selected from the set of values b, c, d <n:m>Register bit field.bByte mode selection</n:m> |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [text]       Means "the location addressed by text"         {}       Optional field or operation         a ∈ {b, c, d}       a is selected from the set of values b, c, d <n:m>       Register bit field</n:m>                                                       |  |

|                                                                                                                                                                                                                                                                      |  |

| $a \in \{b, c, d\}$ a is selected from the set of values b, c, d $$ Register bit field                                                                                                                                                                               |  |

| <n:m> Register bit field</n:m>                                                                                                                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                      |  |

| .b Byte mode selection                                                                                                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                                      |  |

| .d Double-Word mode selection                                                                                                                                                                                                                                        |  |

| .S Shadow register select                                                                                                                                                                                                                                            |  |

| .w Word mode selection (default)                                                                                                                                                                                                                                     |  |

| Acc One of two accumulators {A, B}                                                                                                                                                                                                                                   |  |

| AWB Accumulator write-back destination address register $\in$ {W13, [W13]+ = 2}                                                                                                                                                                                      |  |

| bit4 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$                                                                                                                                                                                   |  |

| C, DC, N, OV, Z MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                                                                                                                                                                                 |  |

| Expr Absolute address, label or expression (resolved by the linker)                                                                                                                                                                                                  |  |

| f File register address $\in \{0x00000x1FFF\}$                                                                                                                                                                                                                       |  |

| lit1 1-bit unsigned literal $\in \{0,1\}$                                                                                                                                                                                                                            |  |

| lit4 4-bit unsigned literal $\in \{015\}$                                                                                                                                                                                                                            |  |

| lit5 5-bit unsigned literal $\in \{031\}$                                                                                                                                                                                                                            |  |

| lit8 8-bit unsigned literal $\in \{0255\}$                                                                                                                                                                                                                           |  |

| lit10 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode                                                                                                                                                                                     |  |

| lit14 14-bit unsigned literal $\in \{016384\}$                                                                                                                                                                                                                       |  |

| lit16 16-bit unsigned literal $\in \{065535\}$                                                                                                                                                                                                                       |  |

| lit23 23-bit unsigned literal $\in$ {08388608}; LSb must be '0'                                                                                                                                                                                                      |  |

| None Field does not require an entry, can be blank                                                                                                                                                                                                                   |  |

| OA, OB, SA, SB DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate                                                                                                                                                                           |  |

| PC Program Counter                                                                                                                                                                                                                                                   |  |

| Slit10         10-bit signed literal ∈ {-512511}                                                                                                                                                                                                                     |  |

| Slit16         16-bit signed literal ∈ {-3276832767}                                                                                                                                                                                                                 |  |

Destination W register ∈ { Wd, [Wd], [Wd++], [Wd--], [++Wd], [--Wd] }

{ Wnd, [Wnd], [Wnd++], [Wnd--], [++Wnd], [--Wnd], [Wnd+Wb] }

Dividend, Divisor Working register pair (direct addressing)

6-bit signed literal  $\in$  {-16...16}

Base W register  $\in$  {W0...W15}

Destination W register  $\in$

#### **TABLE 24-1:** SYMBOLS USED IN OPCODE DESCRIPTIONS

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------------------|---------------|-------------------------------|--------------------------|

| 55                 | NEG                  | NEG    | Acc             | Negate Accumulator                                | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG    | f               | $f = \overline{f} + 1$                            | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | NEG    | f,WREG          | WREG = $\overline{f}$ + 1                         | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1                             | C,DC,N,OV,Z              |

| 56                 | NOP                  | NOP    |                 | No Operation                                      | 1             | 1                             | None                     |

|                    |                      | NOPR   |                 | No Operation                                      | 1             | 1                             | None                     |

| 57                 | POP                  | POP    | f               | Pop f from Top-of-Stack (TOS)                     | 1             | 1                             | None                     |

|                    |                      | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1                             | None                     |