Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs504t-i-ml |

TABLE 4-15: SPI1 AND SPI2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9    | Bit 8       | Bit 7       | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | AII<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|---------|----------|-------------|-------------|-------------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT    | 0240  | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0     | SRMPT       | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242  | _      | 1      | _       | DISSCK | DISSDO | MODE16  | SMP      | CKE         | SSEN        | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2    | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _       | _        | -           | _           | _           | _      | 1      | -      | _      | FRMDLY | SPIBEN | 0000          |

| SPI1BUF     | 0248  |        |        |         |        |        |         | SPI1 Tra | nsmit and R | eceive Buff | er Register | ī      |        |        |        |        |        | 0000          |

| SPI2STAT    | 0260  | SPIEN  | _      | SPISIDL | _      | I      | SPIBEC2 | SPIBEC1  | SPIBEC0     | SRMPT       | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1    | 0262  | _      | 1      | _       | DISSCK | DISSDO | MODE16  | SMP      | CKE         | SSEN        | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2    | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | ı      | _       | -        | ı           | -           | _           | _      | _      | ı      | -      | FRMDLY | SPIBEN | 0000          |

| SPI2BUF     | 0268  |        | •      | •       |        |        | •       | SPI2 Tra | nsmit and R | eceive Buff | er Register | ī      | •      | •      |        |        | •      | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.6 Instruction Addressing Modes

The addressing modes shown in Table 4-38 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

## 4.6.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

## 4.6.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

**Note:** Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

TABLE 4-38: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

# 4.7.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note:

The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

## 4.8 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.8.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these situations are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

Note:

All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note:

Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED) **REGISTER 6-1:**

bit 3 SLEEP: Wake-up from Sleep Flag bit 1 = Device has been in Sleep mode 0 = Device has not been in Sleep mode bit 2 IDLE: Wake-up from Idle Flag bit 1 = Device has been in Idle mode 0 = Device has not been in Idle mode bit 1 BOR: Brown-out Reset Flag bit 1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

bit 0 POR: Power-on Reset Flag bit

1 = A Power-on Reset has occurred 0 = A Power-on Reset has not occurred

Note 1: All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

2: If the WDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

## REGISTER 10-4: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| T3CKR7 | T3CKR6 | T3CKR5 | T3CKR4 | T3CKR3 | T3CKR2 | T3CKR1 | T3CKR0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| T2CKR7 | T2CKR6 | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 T3CKR<7:0>: Assign Timer3 External Clock (T3CK) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181 10110100 = Input tied to RP180

•

•

•

0000001 = Input tied to RP1 0000000 = Input tied to Vss

bit 7-0 T2CKR<7:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181 10110100 = Input tied to RP180

•

•

00000001 = Input tied to RP1 00000000 = Input tied to Vss

## REGISTER 10-19: RPINR43: PERIPHERAL PIN SELECT INPUT REGISTER 43

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLT8R7 | FLT8R6 | FLT8R5 | FLT8R4 | FLT8R3 | FLT8R2 | FLT8R1 | FLT8R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLT7R7 | FLT7R6 | FLT7R5 | FLT7R4 | FLT7R3 | FLT7R2 | FLT7R1 | FLT7R0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 FLT8R<7:0>: Assign PWM Fault 8 (FLT8) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181 10110100 = Input tied to RP180

•

•

00000001 = Input tied to RP1 00000000 = Input tied to Vss

bit 7-0 FLT7R<7:0>: Assign PWM Fault 7 (FLT7) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181 10110100 = Input tied to RP180

•

•

00000001 = Input tied to RP1 00000000 = Input tied to Vss

## REGISTER 10-36: RPOR16: PERIPHERAL PIN SELECT OUTPUT REGISTER 16

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP177R<5:0>: Peripheral Output Function is Assigned to RP177 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP176R<5:0>: Peripheral Output Function is Assigned to RP176 Output Pin bits

(see Table 10-2 for peripheral function numbers)

## REGISTER 10-37: RPOR17: PERIPHERAL PIN SELECT OUTPUT REGISTER 17

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP179R<5:0>: Peripheral Output Function is Assigned to RP179 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP178R<5:0>: Peripheral Output Function is Assigned to RP178 Output Pin bits

(see Table 10-2 for peripheral function numbers)

## 11.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 11.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

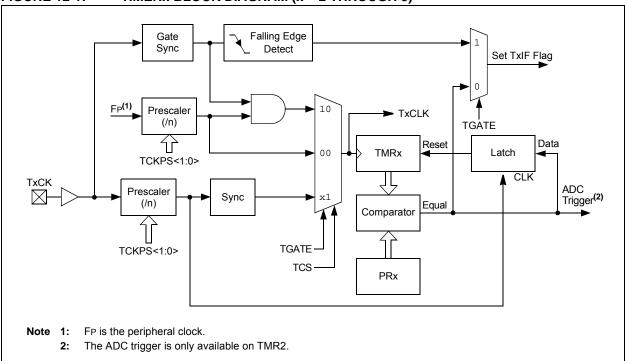

FIGURE 12-1: TIMERX BLOCK DIAGRAM (x = 2 THROUGH 5)

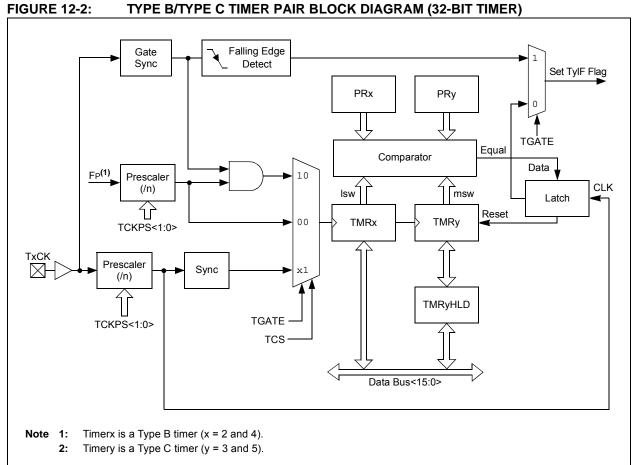

## FIGURE 40.0. THE DECREE OF THE DAID DIGGER OF AN 400 DIT TIMES

## REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

| R/W-0  | R/W-0  | R/W-0    | R/W-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|--------|----------|-------|-----|-----|-----|-------|

| FLTMD  | FLTOUT | FLTTRIEN | OCINV | _   |     |     | OC32  |

| bit 15 |        |          |       |     |     |     | bit 8 |

| R/W-0  | R/W-0, HS | R/W-0  | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-0    |

|--------|-----------|--------|----------|----------|----------|----------|----------|

| OCTRIG | TRIGSTAT  | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |           |        |          |          |          |          | bit 0    |

| Legend:           | HS = Hardware Settable bit |                             |                    |  |

|-------------------|----------------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15 FLTMD: Fault Mode Select bit

1 = Fault mode is maintained until the Fault source is removed; the corresponding OCFLTA bit is cleared in software and a new PWMx period starts

0 = Fault mode is maintained until the Fault source is removed and a new PWMx period starts

bit 14 FLTOUT: Fault Out bit

1 = PWMx output is driven high on a Fault

0 = PWMx output is driven low on a Fault

bit 13 FLTTRIEN: Fault Output State Select bit

1 = OCx pin is tri-stated on a Fault condition

0 = OCx pin I/O state is defined by the FLTOUT bit on a Fault condition

bit 12 OCINV: Output Compare x Invert bit

1 = OCx output is inverted

0 = OCx output is not inverted

bit 11-9 **Unimplemented:** Read as '0'

bit 8 OC32: Cascade Two OCx Modules Enable bit (32-bit operation)

1 = Cascade module operation is enabled

0 = Cascade module operation is disabled

bit 7 OCTRIG: Output Compare x Trigger/Sync Select bit

1 = Triggers OCx from the source designated by the SYNCSELx bits

0 = Synchronizes OCx with the source designated by the SYNCSELx bits

bit 6 TRIGSTAT: Timer Trigger Status bit

1 = Timer source has been triggered and is running

0 = Timer source has not been triggered and is being held clear

bit 5 OCTRIS: Output Compare x Output Pin Direction Select bit

1 = OCx is tri-stated

0 = OCx module drives the OCx pin

**Note 1:** Do not use the OCx module as its own synchronization or trigger source.

2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripherals or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola® SPI and SIOP interfaces.

The dsPIC33EPXXGS50X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical.

: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPIx module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration.

The SPIx serial interface consists of four pins, as follows:

- · SDIx: Serial Data Input

- · SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSX/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-Pin mode, SSx is not used. In 2-Pin mode, neither SDOx nor SSx is used.

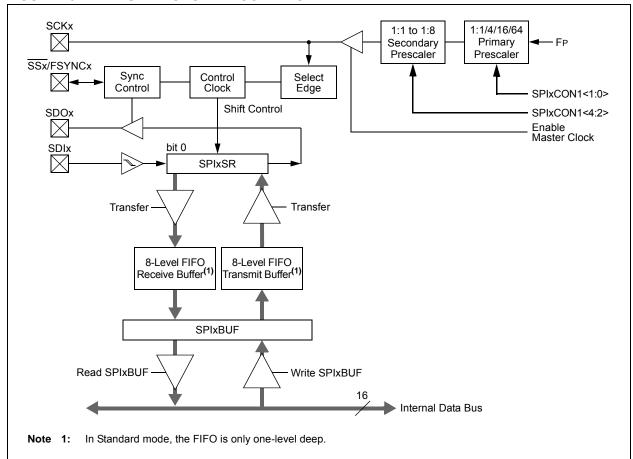

Figure 16-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

FIGURE 16-1: SPIX MODULE BLOCK DIAGRAM

## REGISTER 19-12: ADCOREXH: DEDICATED ADC CORE x CONTROL REGISTER HIGH (x = 0 to 3)(1)

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-1 | R/W-1 |

|--------|-----|-----|--------|--------|--------|-------|-------|

| _      | _   | _   | EISEL2 | EISEL1 | EISEL0 | RES1  | RES0  |

| bit 15 |     |     |        |        |        |       | bit 8 |

| U-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| _     | ADCS6 | ADCS5 | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set

'0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

Legend:

bit 12-10 EISEL<2:0>: ADC Core x Early Interrupt Time Selection bits

111 = Early interrupt is set and an interrupt is generated 8 TADCORE clocks prior to when the data is ready

110 = Early interrupt is set and an interrupt is generated 7 TADCORE clocks prior to when the data is ready

101 = Early interrupt is set and an interrupt is generated 6 TADCORE clocks prior to when the data is ready

100 = Early interrupt is set and an interrupt is generated 5 TADCORE clocks prior to when the data is ready

011 = Early interrupt is set and an interrupt is generated 4 TADCORE clocks prior to when the data is ready

010 = Early interrupt is set and an interrupt is generated 3 TADCORE clocks prior to when the data is ready

001 = Early interrupt is set and an interrupt is generated 2 TADCORE clocks prior to when the data is ready

000 = Early interrupt is set and an interrupt is generated 1 TADCORE clock prior to when the data is ready

bit 9-8 RES<1:0>: ADC Core x Resolution Selection bits

11 = 12-bit resolution

10 = 10-bit resolution

01 = 8-bit resolution

00 = 6-bit resolution

bit 7 Unimplemented: Read as '0'

bit 6-0 ADCS<6:0>: ADC Core x Input Clock Divider bits

> These bits determine the number of Source Clock Periods (TCORESRC) for one Core Clock Period (TADCORE).

1111111 = 254 Source Clock Periods

0000011 = 6 Source Clock Periods

0000010 = 4 Source Clock Periods

0000001 = 2 Source Clock Periods

0000000 = 2 Source Clock Periods

Note 1: For the 6-bit ADC core resolution (RES<1:0> = 00), the EISEL<2:0> bits settings, from '100' to '111', are not valid and should not be used. For the 8-bit ADC core resolution (RES<1:0> = 01), the EISEL<2:0> bits settings, '110' and '111', are not valid and should not be used.

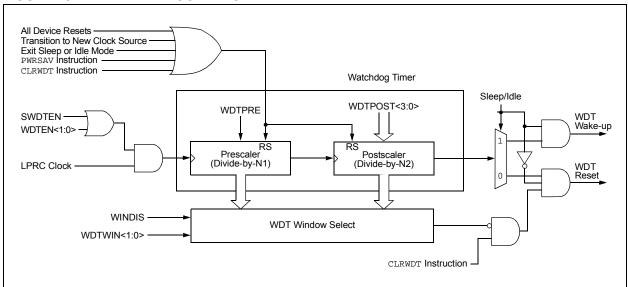

## 23.6 Watchdog Timer (WDT)

For dsPIC33EPXXGS50X family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

## 23.6.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Time-out Period (TWDT), as shown in Parameter SY12 in Table 26-23.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods, ranges from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

**Note:** The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

## 23.6.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) needs to be cleared in software after the device wakes up.

## 23.6.3 ENABLING WDT

The WDT is enabled or disabled by the WDTEN<1:0> Configuration bits in the FWDT Configuration register. When the WDTEN<1:0> Configuration bits have been programmed to '0b11', the WDT is always enabled.

The WDT can be optionally controlled in software when the WDTEN<1:0> Configuration bits have been programmed to '0b10'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disables the WDT during non-critical segments for maximum power savings.

The WDT Time-out flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

## 23.6.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<7>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

## FIGURE 23-2: WDT BLOCK DIAGRAM

## 24.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- Literal operations

- · DSP operations

- Control operations

Table 24-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 24-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- · The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- · The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

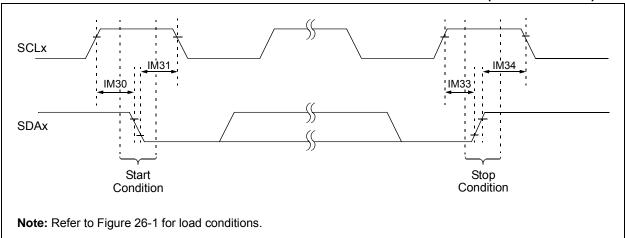

## FIGURE 26-19: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

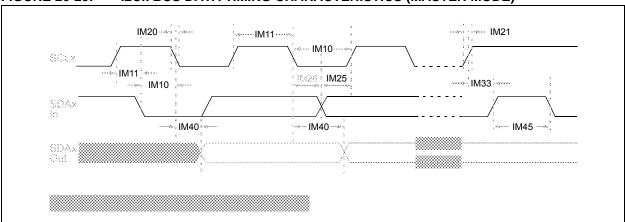

## FIGURE 26-20: I2Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | N        | <b>IILLIMETER</b> | S    |

|-------------------------|--------|----------|-------------------|------|

| Dimension               | Limits | MIN      | NOM               | MAX  |

| Number of Pins          | N      | 28       |                   |      |

| Pitch                   | е      | 0.65 BSC |                   |      |

| Overall Height          | Α      | 0.80     | 0.90              | 1.00 |

| Standoff                | A1     | 0.00     | 0.02              | 0.05 |

| Terminal Thickness      | A3     |          | 0.20 REF          |      |

| Overall Width           | Е      | 6.00 BSC |                   |      |

| Exposed Pad Width       | E2     | 3.65     | 3.70              | 4.70 |

| Overall Length          | D      | 6.00 BSC |                   |      |

| Exposed Pad Length      | D2     | 3.65     | 3.70              | 4.70 |

| Terminal Width          | р      | 0.23     | 0.30              | 0.35 |

| Terminal Length         | Ĺ      | 0.30     | 0.40              | 0.50 |

| Terminal-to-Exposed Pad | K      | 0.20     | -                 | _    |

## Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2

| CPU                                      |     | F                                            |        |

|------------------------------------------|-----|----------------------------------------------|--------|

| Addressing Modes                         | 21  | Filter Capacitor (CEFC) Specifications       | 305    |

| Clocking System Options                  | 105 | Flash Program Memory                         |        |

| Fast RC (FRC) Oscillator                 | 105 | and Table Instructions                       |        |

| FRC Oscillator with PLL (FRCPLL)         | 105 | Control Registers                            |        |

| FRC Oscillator with Postscaler           | 105 | Dual Partition Flash Configuration           |        |

| Low-Power RC (LPRC) Oscillator           | 105 | Operations                                   |        |

| Primary (XT, HS, EC) Oscillator          |     |                                              |        |

| Primary Oscillator with PLL              |     | Resources                                    |        |

| Control Registers                        |     | RTSP Operation                               |        |

| Data Space Addressing                    |     | Flexible Configuration                       | 277    |

| Instruction Set                          |     | G                                            |        |

| Registers                                |     | -                                            | 4.5    |

| Resources                                |     | Getting Started Guidelines                   |        |

| Customer Change Notification Service     |     | Connection Requirements                      |        |

| Customer Notification Service            |     | CPU Logic Filter Capacitor Connection (VCAP) |        |

| Customer Support                         |     | Decoupling Capacitors                        |        |

| Oustomer Support                         | 504 | External Oscillator Pins                     |        |

| D                                        |     | ICSP Pins                                    |        |

| Data Address Space                       | 37  | Master Clear (MCLR) Pin                      |        |

| Memory Map for dsPIC33EP16GS50X Devices  |     | Oscillator Value Conditions on Start-up      |        |

| Memory Map for dsPIC33EP32GS50X Devices  |     | Targeted Applications                        |        |

| Memory Map for dsPIC33EP64GS50X Devices  |     | Unused I/Os                                  | 18     |

| Near Data Space                          |     | н                                            |        |

|                                          |     |                                              |        |

| Organization, Alignment                  |     | High-Speed Analog Comparator                 |        |

| SFR Space                                |     | Applications                                 |        |

| Width                                    | 31  | Description                                  |        |

| Data Space                               | 00  | Digital-to-Analog Comparator (DAC)           | 265    |

| Extended X                               |     | Features Overview                            | 263    |

| Paged Data Memory Space (figure)         |     | Hysteresis                                   | 266    |

| Paged Memory Scheme                      | 66  | Pulse Stretcher and Digital Logic            | 265    |

| DC Characteristics                       |     | Resources                                    | 266    |

| Brown-out Reset (BOR)                    |     | High-Speed PWM                               |        |

| Constant-Current Source Specifications   |     | Description                                  | 181    |

| DACx Output (DACOUTx Pin) Specifications |     | Features                                     |        |

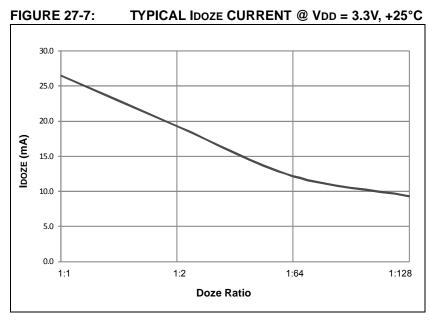

| Doze Current (IDOZE)                     | 309 | Resources                                    | 182    |

| I/O Pin Input Specifications             | 310 | Write-Protected Registers                    |        |

| I/O Pin Output Specifications            | 313 | High-Speed, 12-Bit Analog-to-Digital         |        |

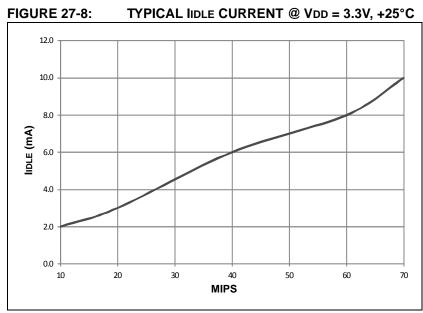

| Idle Current (IIDLE)                     | 307 | Converter (ADC)                              | 229    |

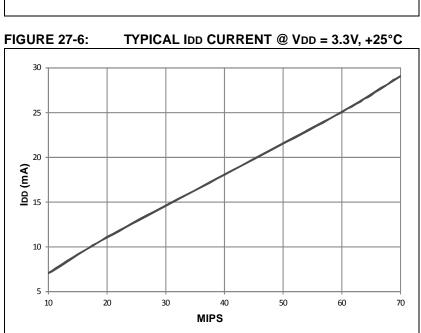

| Operating Current (IDD)                  | 306 | Control Registers                            |        |

| Operating MIPS vs. Voltage               | 304 | Features Overview                            |        |

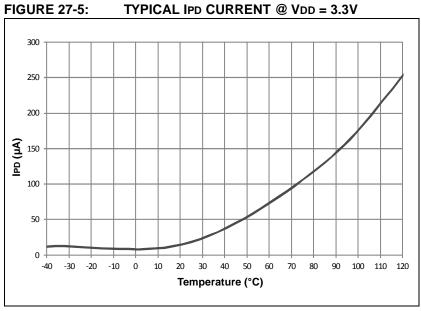

| Power-Down Current (IPD)                 |     | Resources                                    |        |

| Program Memory                           |     | Nesources                                    | 202    |

| Temperature and Voltage Specifications   |     | I                                            |        |

| Watchdog Timer Delta Current (△IWDT)     |     | I/O Ports                                    | 125    |

| DC/AC Characteristics                    |     | Configuring Analog/Digital Port Pins         |        |

| Graphs and Tables                        | 349 |                                              |        |

| Demo/Development Boards, Evaluation and  |     | Helpful Tips                                 |        |

| Starter Kits                             | 302 | Open-Drain Configuration                     |        |

| Development Support                      |     | Parallel I/O (PIO)                           |        |

| Device Calibration                       |     | Resources                                    |        |

| Addresses                                |     | Write/Read Timing                            |        |

|                                          |     | In-Circuit Debugger                          |        |

| and Identification                       | 203 | MPLAB ICD 3                                  |        |

| Device Programmer                        | 004 | PICkit 3 Programmer                          |        |

| MPLAB PM3                                |     | In-Circuit Emulation                         |        |

| Doze Mode                                |     | In-Circuit Serial Programming (ICSP)27       | 7, 287 |

| DSP Engine                               | 30  | Input Capture                                | 171    |

| E                                        |     | Control Registers                            | 172    |

|                                          |     | Resources                                    | 171    |

| Electrical Characteristics               |     | Input Change Notification (ICN)              | 126    |

| AC                                       | 315 | . ,                                          |        |

| Equations                                |     |                                              |        |

| Device Operating Frequency               | 105 |                                              |        |

| FPLLO Calculation                        |     |                                              |        |

| Fvco Calculation                         | 105 |                                              |        |

| Errata                                   | 10  |                                              |        |

|                                          |     |                                              |        |

## Worldwide Sales and Service

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614

Fax: 678-957-9614

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323

Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC

Tel: 919-844-7510

New York, NY

Tel: 631-435-6000

San Jose, CA

Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto

Tel: 905-695-1980 Fax: 905-695-2078

## ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511

Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou

Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Fax: 886-2-2508-0102 **Thailand - Bangkok**

Tel: 66-2-694-1351 Fax: 66-2-694-1350

## EUROPE

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Ecnos

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud

Tel: 33-1-30-60-70-00

Germany - Garching

Tel: 49-8931-9700 **Germany - Haan**

Tel: 49-2129-3766400

Germany - Heilbronn

Tel: 49-7131-67-3636

Germany - Karlsruhe

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611

Fax: 39-0331-466781

Italy - Padova

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim

Tel: 47-7289-7561

Poland - Warsaw

Tel: 48-22-3325737

Romania - Bucharest

Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90

Fax: 34-91-708-08-91

Sweden - Gothenberg

Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

UK - Wokingham

Tel: 44-118-921-5800 Fax: 44-118-921-5820